Sinterconnects: All-Copper Top-Side Interconnects Based on Copper Sinter Paste for Power Module Packaging

Abstract

:1. Introduction

2. Materials and Methods

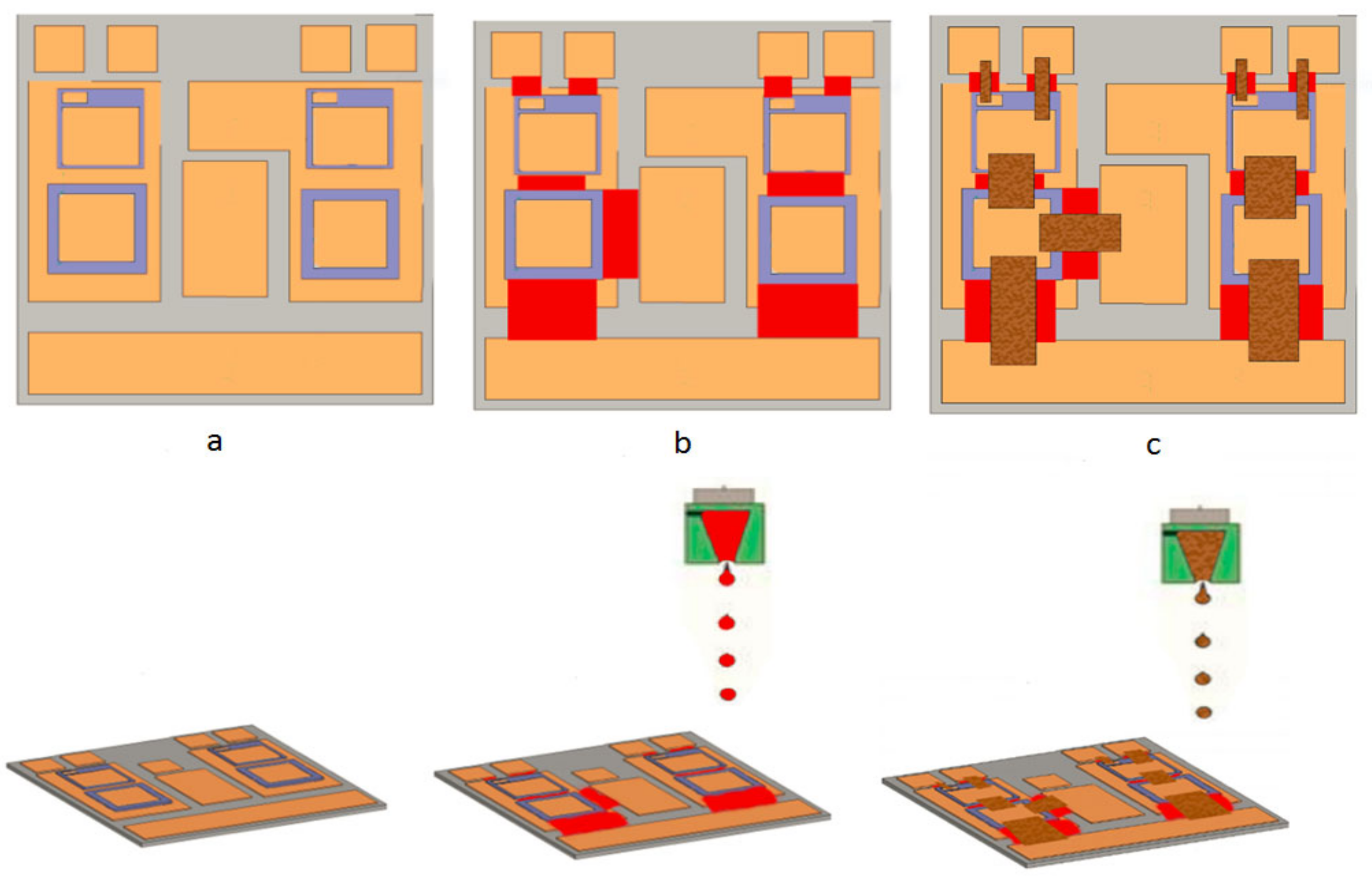

2.1. Fabrication of Top-Side Interconnects

2.1.1. Structure A–Thick, Al Wire Bond Interconnections

2.1.2. Structure B–Printed Cu-Sinter Pasted Interconnection

2.1.3. Structure C–Printed Cu Clip-Attach Interconnection

2.2. Post-Fabrication Inspection and Measurement

2.3. FEM Simulations

2.3.1. Electrical Simulations

2.3.2. Thermal Simulation

3. Results and Discussion

3.1. Characterization and Measurements

3.2. Electrical and Thermal Simulation Results of the Sinterconnects at High Current Regimes

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Hermanns, K.; Peng, Y.; Mantooth, A. The Increasing Role of Design Automation in Power Electronics: Gathering What Is Needed. IEEE Power Electron. Mag. 2020, 7, 46–50. [Google Scholar] [CrossRef]

- Broughton, J.; Smet, V.; Tummala, R.R.; Joshi, Y.K. Review of Thermal Packaging Technologies for Automotive Power Electronics for Traction Purposes. J. Electron. Packag. 2018, 140. [Google Scholar] [CrossRef]

- Yang, S.; Bryant, A.; Mawby, P.; Xiang, D.; Ran, L.; Tavner, P. An Industry-Based Survey of Reliability in Power Electronic Converters. IEEE Trans. Ind. Appl. 2011, 47, 1441–1451. [Google Scholar] [CrossRef]

- Oh, H.; Han, B.; McCluskey, P.; Han, C.; Youn, B.D. Physics-of-Failure, Condition Monitoring, and Prognostics of Insulated Gate Bipolar Transistor Modules: A Review. IEEE Trans. Power Electron. 2015, 30, 2413–2426. [Google Scholar] [CrossRef]

- Liu, K.; Yang, J.; Luo, J.; Wang, L.; Huang, Q.; Chen, F. The characterization and application of chip topside bonding materials for power modules packaging: A review. J. Phys. Conf. Ser. 2020, 1605, 012168. [Google Scholar] [CrossRef]

- Seal, S.; Mantooth, H.A. High Performance Silicon Carbide Power Packaging—Past Trends, Present Practices, and Future Directions. Energies 2017, 10, 341. [Google Scholar] [CrossRef] [Green Version]

- Durand, C.; Klingler, M.; Coutellier, D.; Naceur, H. Power Cycling Reliability of Power Module: A Survey. IEEE Trans. Device Mater. Reliab. 2016, 16, 80–97. [Google Scholar] [CrossRef]

- Wirebondless Semiconductor Package. U.S. Patent US8304903B2, 14 June 2006.

- Wirebondless Module Package. U.S. Patent US5616886A, 5 June 1995.

- Wirebondless Wafer Level Package with Plated Bumps and Interconnects. U.S. Patent US20090289356A1, 23 May 2008.

- Weidner, K.; Kaspar, M.; Seliger, N. Planar interconnect technology for power module system integration. In Proceedings of the 2012 7th International Conference on Integrated Power Electronics Systems (CIPS), Nuremberg, Germany, 6–8 March 2012; pp. 1–5. [Google Scholar]

- Zhu, Q.; Forsyth, A.; Todd, R.; Mills, L. Thermal characterisation of a copper-clip-bonded IGBT module with double-sided cooling. In Proceedings of the 2017 23rd IEEE International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Amsterdam, The Netherlands, 27–29 September 2017; p. 1. [Google Scholar]

- Barbarini, E.; Troadec, C. Power Module Packaging: Market and Technology Trends. In Proceedings of the Additional Conferences (Device Packaging, HiTEC, HiTEN, & CICMT), Boston, MA, USA, 30 September–3 October 2019; Volume 2019, pp. 749–779. [Google Scholar]

- Lee, H.; Smet, V.; Tummala, R. A Review of SiC Power Module Packaging Technologies: Challenges, Advances, and Emerging Issues. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 8, 239–255. [Google Scholar] [CrossRef]

- Stockmeier, T.; Beckedahl, P.; Göbl, C.; Malzer, T. SKiN: Double side sintering technology for new packages. In Proceedings of the 2011 IEEE 23rd International Symposium on Power Semiconductor Devices and ICs, San Diego, CA, USA, 23–26 May 2011; pp. 324–327. [Google Scholar]

- Zhang, Z.; Chen, C.; Yang, Y.; Zhang, H.; Kim, D.; Sugahara, T.; Nagao, S.; Suganuma, K. Low-temperature and pressureless sinter joining of Cu with micron/submicron Ag particle paste in air. J. Alloy. Compd. 2019, 780, 435–442. [Google Scholar] [CrossRef]

- Jo, J.L.; Anai, K.; Yamauchi, S.; Sakaue, T. The Properties of Cu Sinter Paste for Pressure Sintering at Low Temperature. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 28–31 May 2019; pp. 76–80. [Google Scholar]

- Gao, Y.; Chen, C.; Nagao, S.; Suganuma, K.; Bahman, A.S.; Iannuzzo, F. Highly Reliable Package using Cu Particles Sinter Paste for Next Generation Power Devices. In Proceedings of the PCIM Europe 2019, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 7–9 May 2019; pp. 1–4. [Google Scholar]

- Bhogaraju, S.K.; Conti, F.; Schmid, M.; Meier, M.R.; Schweigart, H.; Elger, G. Development of sinter paste with surface modified copper alloy particles for die-attach bonding. In Proceedings of the CIPS 2020 11th International Conference on Integrated Power Electronics Systems, Berlin, Germany, 24–26 March 2020; pp. 1–6. [Google Scholar]

- Gao, Y.; Li, W.; Chen, C.; Zhang, H.; Jiu, J.; Li, C.-F.; Nagao, S.; Suganuma, K. Novel copper particle paste with self-reduction and self-protection characteristics for die attachment of power semiconductor under a nitrogen atmosphere. Mater. Des. 2018, 160, 1265–1272. [Google Scholar] [CrossRef]

- Wei, T.B.; Khor, L.; Long, L.H.; Jeng, L.L.; Hang, G.S. Universal copper clip packaging solution for power management IC. In Proceedings of the 2015 China Semiconductor Technology International Conference, Shanghai, China, 15–16 March 2015; pp. 1–3. [Google Scholar]

- Zhu, Y.; Chen, H.; Xue, K.; Li, M.; Wu, J. Thermal and reliability analysis of clip bonding package using high thermal conductivity adhesive. In Proceedings of the 2013 IEEE 15th Electronics Packaging Technology Conference (EPTC 2013), Singapore, 11–13 December 2013; pp. 259–263. [Google Scholar]

- Hwang, J.S. Solder Paste in Electronics Packaging: Technology and Applications in Surface Mount, Hybrid Circuits, and Component Assembly; Springer: Berlin, Germany, 2012. [Google Scholar]

- Lwin, K.K.; Tubillo, C.E.; Panumard, T.J.D.; Suthiwongsunthorn, N.; Sirinorakul, S. Copper Clip Package for high performance MOSFETs and its optimization. In Proceedings of the 2016 IEEE 18th Electronics Packaging Technology Conference (EPTC), Singapore, 30 November–3 December 2016; pp. 123–128. [Google Scholar]

- ANSYS Electronics Desktop. 2019. Available online: https://www.ansys.com/products/electronics/ansys-electronics-desktop (accessed on 7 January 2020).

- Jackson, J.D. Classical Electrodynamics; Wiley: New York, NY, USA, 1999; pp. 1925–2016. [Google Scholar]

- Jones, W.; March, N.H. Theoretical Solid State Physics; Courier Corporation: Chelmsford, MA, USA, 1985; Volume 35. [Google Scholar]

- Gnielinski, V.; Kabelac, S.; Kind, M.; Martin, H.; Mewes, D.; Schaber, K.; Stephan, P. VDI-Wärmeatlas; Springer: Berlin, Germany, 2006; pp. 978–983. [Google Scholar]

- Qian, C.; Gheitaghy, A.M.; Fan, J.J.; Tang, H.Y.; Sun, B.; Ye, H.Y.; Zhang, G.Q. Thermal Management on IGBT Power Electronic Devices and Modules. IEEE Access 2018, 6, 12868–12884. [Google Scholar] [CrossRef]

- Kraft, S.; Zischler, S.; Tham, N.; Schletz, A. B3. 3-Properties of a novel silver sintering die attach material for high temperature-high lifetime applications. Proc. Sens. 2013, 2013, 242–247. [Google Scholar]

- Siow, K.S.; Lin, Y.T. Identifying the development state of sintered silver (Ag) as a bonding material in the microelectronic packaging via a patent landscape study. J. Electron. Packag. 2016, 138, 020804. [Google Scholar] [CrossRef] [Green Version]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: Berlin, Germany, 2010. [Google Scholar]

- Singh, B.; Mehta, B. Relationship between nature of metal-oxide contacts and resistive switching properties of copper oxide thin film based devices. Thin Solid Films 2014, 569, 35–43. [Google Scholar] [CrossRef]

- Nair, M.; Guerrero, L.; Arenas, O.L.; Nair, P. Chemically deposited copper oxide thin films: Structural, optical and electrical characteristics. Appl. Surf. Sci. 1999, 150, 143–151. [Google Scholar] [CrossRef]

- Katsis, D.; Van Wyk, J. Void-induced thermal impedance in power semiconductor modules: Some transient temperature effects. IEEE Trans. Ind. Appl. 2003, 39, 1239–1246. [Google Scholar] [CrossRef]

- Polom, T.A.; Van Der Broeck, C.H.; De Doncker, R.W.; Lorenz, R.D. Exploiting Distinct Thermal Response Properties for Power Semiconductor Module Health Monitoring. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 1. [Google Scholar] [CrossRef]

| Material | Thermal Conductivity W/(m-K) |

|---|---|

| IGBT, diode: Si | 140 |

| DBC ceramic: Al2O3 | 36 |

| DBC: Cu | 400 |

| Cu paste interconnect | 40 (structure B), 100 (structure C) |

| Cu clip | 400 |

| Wires: Al | 200 |

| Encapsulant | 0.75 |

| Structure | |||

|---|---|---|---|

| A | B | C | [Unit] |

| 9.5 | 8.1 | 8.4 | [K/W] |

| 1 | 0.85 | 0.88 | [p.u.] |

| Max | Average | |

|---|---|---|

| Structure A | 108.8 | 104.6 |

| Structure B | 108.9 | 104.6 |

| Structure C | 104.5 | 100.0 |

| Structure C with double-side cooling * | 74.0 | 71.1 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Roshanghias, A.; Malago, P.; Kaczynski, J.; Polom, T.; Bardong, J.; Holzmann, D.; Malik, M.-H.; Ortner, M.; Hirschl, C.; Binder, A. Sinterconnects: All-Copper Top-Side Interconnects Based on Copper Sinter Paste for Power Module Packaging. Energies 2021, 14, 2176. https://doi.org/10.3390/en14082176

Roshanghias A, Malago P, Kaczynski J, Polom T, Bardong J, Holzmann D, Malik M-H, Ortner M, Hirschl C, Binder A. Sinterconnects: All-Copper Top-Side Interconnects Based on Copper Sinter Paste for Power Module Packaging. Energies. 2021; 14(8):2176. https://doi.org/10.3390/en14082176

Chicago/Turabian StyleRoshanghias, Ali, Perla Malago, Jaroslaw Kaczynski, Timothy Polom, Jochen Bardong, Dominik Holzmann, Muhammad-Hassan Malik, Michael Ortner, Christina Hirschl, and Alfred Binder. 2021. "Sinterconnects: All-Copper Top-Side Interconnects Based on Copper Sinter Paste for Power Module Packaging" Energies 14, no. 8: 2176. https://doi.org/10.3390/en14082176

APA StyleRoshanghias, A., Malago, P., Kaczynski, J., Polom, T., Bardong, J., Holzmann, D., Malik, M.-H., Ortner, M., Hirschl, C., & Binder, A. (2021). Sinterconnects: All-Copper Top-Side Interconnects Based on Copper Sinter Paste for Power Module Packaging. Energies, 14(8), 2176. https://doi.org/10.3390/en14082176