Abstract

The concept of the modular multilevel converter (MLC) has been raising interest in research in order to improve their performance and applicability. The potential of an MLC is enormous, with a great focus on medium- and high-voltage applications, such as solar photovoltaic and wind farms, electrified railway systems, or power distribution systems. This concept makes it possible to overcome the limitation of the semiconductors blocking voltages, presenting advantageous characteristics. However, the complexity of implementation and control presents added challenges. Thus, this paper aims to contribute with a critical and comparative analysis of the state-of-the-art aspects of this concept in order to maximize its potential. In this paper, different power electronics converter topologies that can be integrated into the MLC concept are presented, highlighting the advantages and disadvantages of each topology. Nevertheless, different modulation techniques used in an MLC are also presented and analyzed. Computational simulations of all the modulation techniques under analysis were developed, based on four cascaded full-bridge topologies. Considering the simulation results, a comparative analysis was possible to make regarding the symmetry of the synthesized waveforms, the harmonic content, and the power distribution in each submodule constituting the MLC.

1. Introduction

Multilevel converters (MLC) present themselves as the greatest innovation of recent years in the concept of power electronics converters [1]. The ability to synthesize the ladder output waveform as a function of the combination of the different direct current (DC) buses makes the MLC concept widely used in different power electronics applications. The greater the number of DC buses of the MLC, the greater the number of voltage levels that can be synthesized, and, consequently, the output waveform will approach a sinusoid [1]. The main points that characterize the concept of MLC and that differ from conventional two-level power converters topologies are as follows [1,2,3,4,5]:

- Easily extendable due to modular converter substructures. Modularity and expandability allow the creation of redundant operating states, improving system response in case of failures (more fault tolerant);

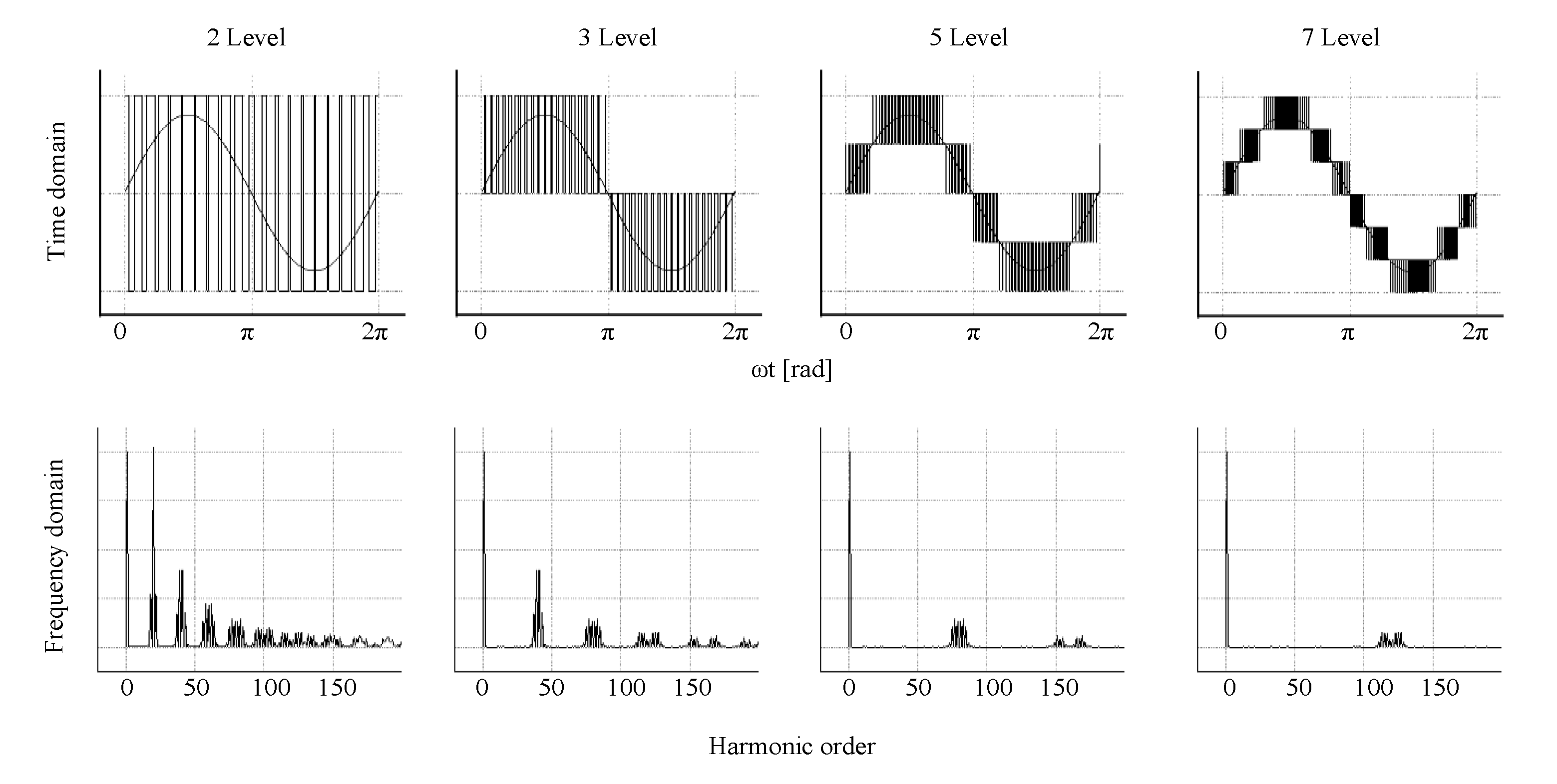

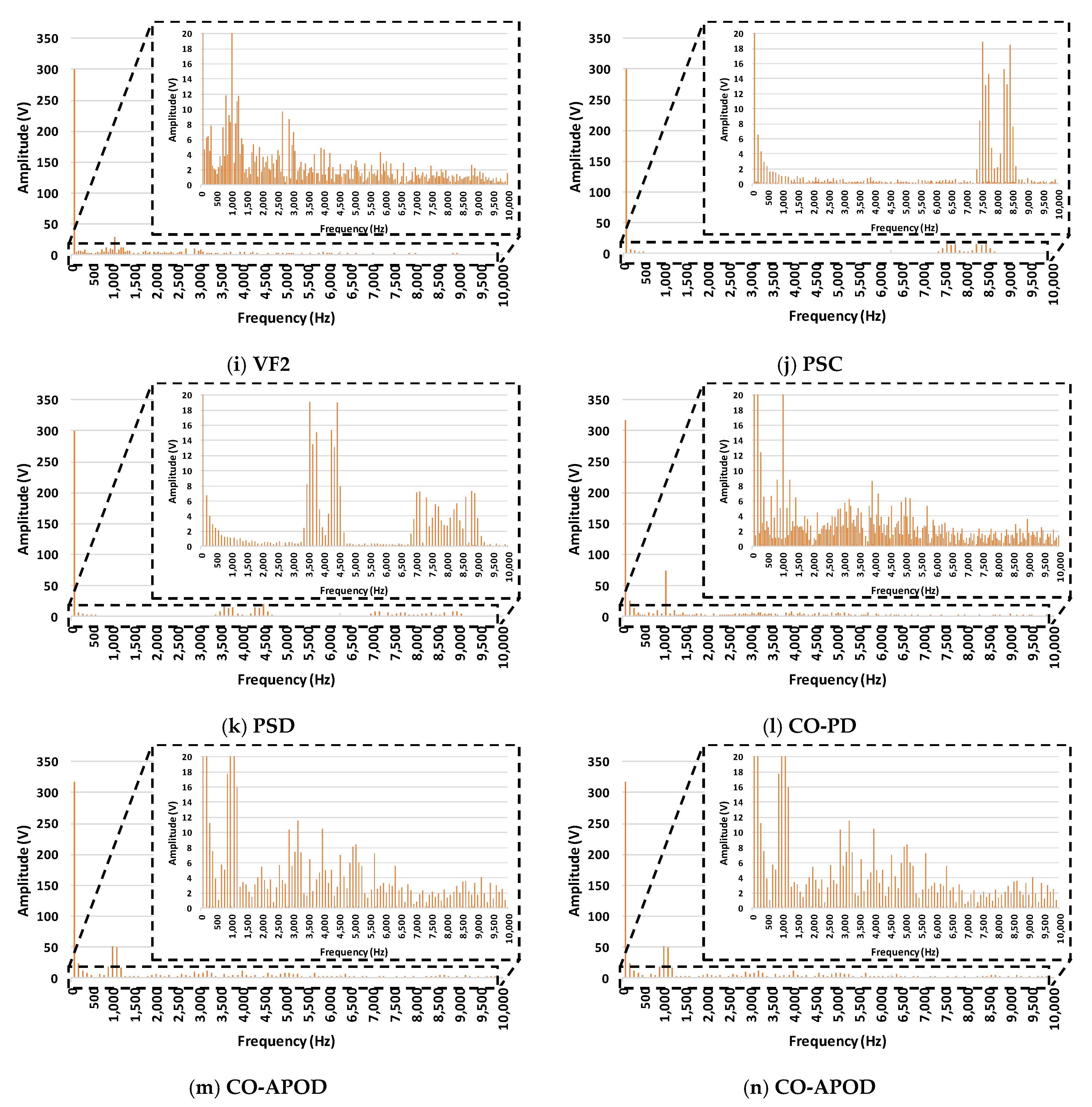

- Lower harmonic content and more concentrated in the fundamental component and at high frequencies. As illustrated in Figure 1: (i) the greater the number of levels, the more closely the output waveform resembles a sinusoid; (ii) the higher-frequency harmonic content allows for easier filtering;

Figure 1. Influence of the voltage levels that an MLC can produce on the harmonic spectrum.

Figure 1. Influence of the voltage levels that an MLC can produce on the harmonic spectrum. - Possibility of integrating less bulky passive filters, thus minimizing implementation costs and system losses, mainly copper and core losses in ferromagnetic elements;

- Possibility of reducing the voltage stress (dv/dt) of the power semiconductors. This feature enables the integration of more standard semiconductors with the higher commercially available stock and lower costs. Additionally, it allows for mitigating electromagnetic interference problems caused by high dv/dt values when switching semiconductors. Nevertheless, by reducing the dv/dt stress, it is also possible to reduce the galvanic isolation stress;

- Possibility of reducing switching frequencies, minimizing switching losses and semiconductor voltage stress;

- Simpler and faster maintenance service: just exchange the damaged submodule with a functional one;

- Enable the easy integration of renewable energy sources and energy storage systems.

All these features are very attractive, especially for high-voltage power distribution applications. An example of the integration of an MLC in high-voltage direct current (HVDC) systems can be seen in [5,6,7,8,9]. A distributed control of MLCs for HVDC application is proposed in [10], and fault conditions analyses can be found in [11,12,13]. Another major focus of MLC applications lies in solar photovoltaic [14,15,16,17,18,19,20,21,22] or wind farms onshore [23] and offshore [24,25,26,27]. The MLC can also interface with energy storage system (ESS) [28,29,30,31,32,33,34,35]. Regarding electric mobility, the MLC has great applicability in feeding railway electric systems [36] or operating as active power conditioner [37,38] to mitigate power quality problems in the railway system. Additionally, the MLC concept can be employed in electric vehicles for traction purposes [39,40] or to interface with an onboard ESS [41,42]. The MLC has also been implemented in marine propulsion [43,44]. The mentioned characteristics potentiated the integration of MLCs for active conditioners in order to mitigate power quality problems, acting as a static compensator [45,46,47,48,49,50] or distribution STATCOM (DSTATCOM) [51]. Emerging power electronics concepts, such as solid-state transformers, have also been exploring the potential of the MLC [52,53,54,55,56].

In [1] a comparative analysis, five submodule topologies capable of integrating an MLC solution are described, presenting conclusions regarding the allowed operating modes, number of semiconductors, and DC bus constitution. In [57], the authors present an analysis of different MLC topologies, highlighting the submodules: neutral-point-clamped (NPC), flying capacitor multilevel converter (FCMC), and cascaded full-bridge (CHB). Applicability of these topologies, as well as electrical magnitudes of some existing state-of-the-art prototypes developed, are presented.

Akagi in [58] explains the evolution of the modular multilevel converter (MMC) and modular multilevel cascaded converter (MMCC) concepts. The terminology adopted by Akagi was MMCC to portray modularity and the multilevel cascaded power electronics converters. Thus, the presented study depicts the analysis, classification, terminology and applications of different MMCC configurations, each cell being composed of a full- or half-bridge. Experimental results for a low-scale MMCC for an energy storage site and driver engine are presented, highlighting the good immunity of the system to electromagnetic interference.

The authors of [59] present the evolution of the topologies of the submodules that constitute an MMCC, highlighting the mathematical model of the system. Technical challenges and future trends are also presented. In [60] the authors pretended hybrid modular and multilevel solutions based on the combination of submodules of different topologies. An analysis of the evolution of the different cells is also presented. The authors of [61,62] present a study of the evolution of power electronics solutions for railway applications, highlighting the solutions implemented by different manufacturers where the submodules of the modular and multilevel systems are based on solid-state transformers. The evolution of the solutions shows a tendency for the submodules to share the same DC bus, with the output of each submodule being cascaded to the adjacent submodule. Prototypes of the power electronics converters and transformers used in different solutions are also presented and analyzed. Further studies can be found in [62,63,64], where different topologies, configurations, controls, and end applications for MMC are analyzed.

The main focus of the authors’ contribution in [65] lies essentially in the comparative study of different PWM techniques for the conventional MMC topology. In turn, a review of control techniques, as well as the working principle of an MMC, highlighting existing state-of-the-art techniques and future contributions, is presented in [66]. Applications of the MMC are also listed.

From the state-of-the-art review articles, some research gaps were found that this article aims to fill. From the study conducted, it was found that the review articles focus primarily on the conventional MMC topology, with each submodule consisting of either a half-bridge or full-bridge. There are other review studies but with other topologies, as well as review studies for cascaded solutions. The review of the applications is always limited to the studied topology. In turn, as far as the control algorithms are concerned, no complete study was found that implements all the modulation techniques in order to quantify the best solution. Thus, there exists a lack of analysis of the power imbalances between submodules, the harmonic distortion rate, and the harmonic content generated as a function of each PWM technique.

This paper aims to provide a critical, thorough and objective analysis of different power electronics converter topologies that can be integrated into modular and multilevel systems. Additionally, it is intended to contribute a comparative study of different modulation techniques to be implemented in MLC systems. It is expected that this study can serve as an implementation manual for different researchers, students, and engineers that have been developing work in this area, thus contributing a starting point for the development of new solutions. This paper is structured as follows: in Section 1, an introduction to the MLC concept is given, presenting the main advantages as well as applications of the MLC; in Section 2, an analysis of the MLC concept is performed, reviewing some power converters topologies that can be integrated into the MLC; Section 3 is dedicated to presenting PWM techniques to control MLCs; Section 4 presents a comparative analysis of the different PWM techniques in cascaded four full-bridge submodules; Section 5 presents the main conclusions of the review study.

2. Multilevel Converter

The DC–AC power converters, also known in the literature as inverters, are usually classified according to the constitution of the DC bus: voltage source inverter (VSI) or current source inverter (CSI). In general, the DC–AC power converters have as their main objective the synthetization of an AC component from a DC source, using fully controlled semiconductors. The AC output amplitude and frequency are adjusted from the implemented control algorithms. Regarding the power semiconductors, some examples of technologies can be (i) insulated-gate bipolar transistor—IGBT, (ii) metal-oxide-semiconductor field-effect transistor—MOSFET, (iii) insulated gate collector transistor—IGCT, etc. For the following analyses presented in this topic, the IGBT will be used as a power semiconductor due to its predominance in the implementation of these types of high-voltage and high-power applications.

In general, the DC–AC power converters have discrete values in their output, requiring precautions in their implementation in order to safeguard system integrity. That is, considering that the control of IGBTs is based on PWM techniques, the output waveform of the DC–AC power converter will have a resulting frequency equal to or multiple times the switching frequency of each IGBT. Although the output waveform is not sinusoidal, as desired, the frequency of the fundamental component is close to the desired one, as can be seen in Figure 1. This characteristic presents some requirements to be met, depending on the application.

VSIs have high discrete dv/dt output values. In order to smooth the waveform, the load needs to be inductive. Otherwise, with capacitive loads, current spikes would appear. This concludes the need to include an inductive filter between the output of the VSI and the load. In turn, CSIs have high discrete di/dt output values. Therefore, in order to smooth the output waveform, the CSI load should be capacitive. Otherwise, with inductive loads, voltage spikes would appear, thus concluding the need to include a capacitive filter between the output of the CSI and the load.

In order to integrate power electronics converters in high-voltage applications (for example, a VSI), it is necessary to increase the amplitude of the DC bus voltage. From a practical point of view, the DC bus voltage should be higher than the peak value of the power grid voltage. As a consequence of increasing the DC bus voltage, larger inductive filters will be required in order to mitigate the increase in dv/dt variations.

Considering the implementation of these types of solutions, it is also necessary to take into consideration the semiconductors available in the market. Aspects such as blocking voltages, switching frequencies, and stock quantities are important in industrial applications. However, semiconductors with high voltages and switching frequencies have limited stock, being more suited to specific applications of limited requirements, and are not very attractive either in research and development or in industry. In turn, semiconductors with medium voltages and switching frequencies present themselves as a mature and predominant technology in the market.

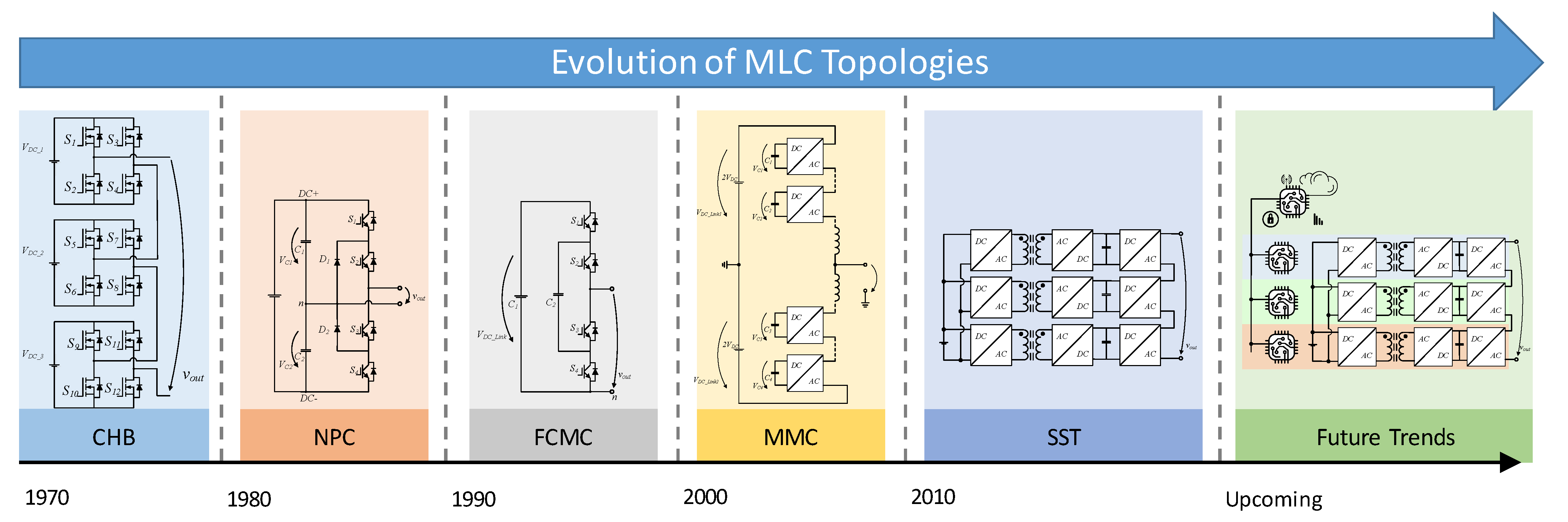

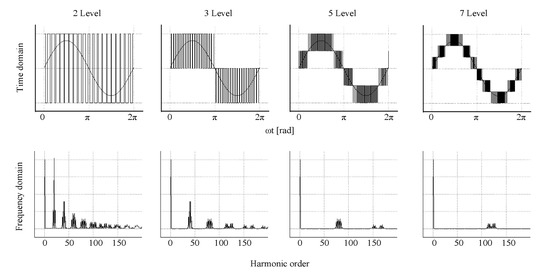

Figure 2 illustrates the evolution and emergence of new MLC topologies. The MLC concept emerged in the 1970s, invented and patented by William MacMurray, with the cascaded full-bridge configuration. The same inventor pioneered another approach, where the full-bridges were in parallel, sharing the same DC bus, with low-frequency cascaded transformers at the output of each submodule of the full-bridge [67,68]. The cascaded full-bridge topology has been matured, widely used by ABB (Oerlikon, Switzerland), featuring a modular and robust structure that is fault tolerant with the addition of bypass switches. The main disadvantages reside in the need for each submodule to require a DC-source. The cascaded transformer approach mitigates this problem, obtaining a single DC-source on the lower voltage DC-side. Although it allows a simpler DC bus balancing control algorithm, it requires special care in the sizing and control of the AC side in order to avoid the saturation of the transformers. In order to avoid an average value of the magnetic flux variation, it is recommended that the system start at 90° or to 270°, taking into account an application of AC. Thus, the flux density integral from the instant of 90° to 270° has a similar symmetrical value to the integral from 270° to 90°, obtaining a null value at each period [69]. Otherwise, the flux density would have an average value, which could saturate the ferromagnetic core. This is especially important for ferromagnetic cores that are not laminated and have low flux density values.

Figure 2.

Evolution and emergence of new MLC topologies.

In 1980, the NPC topology was presented and patented by Baker [70]. NPC topology attracted researchers, becoming best known when, in 1981, Akira Nabae and Hirofumi Akagi presented and experimentally proved its mode of operation [71].

A “multilevel high-voltage chopper” in the literature best known as FCMC topology, was introduced by Meynard and Foch in 1992 [72].

The modular multilevel converter (MMC) topology, emerging in the new millennium, is a major driver in power electronics for high-voltage and high-power applications. This concept can be implemented with submodules based on topologies such as half-bridge [73], full-bridge [73], NPC [74], T-type NPC (TNPC) [74], or FCMC [75]. Despite all the previously mentioned advantages concerning the MLC concept, MMC presents some added challenges, such as [8]

- The sizing of the inductive and capacitive elements: The inductor must be sized in order to decouple the DC component from the AC, as well as to minimize the short-circuiting of the DC bus;

- The pre-charging process of the capacitors: Whenever the MMC is initialized, the capacitors are discharged, requiring a pre-charging mechanism in order to minimize the inrush current;

- DC bus regulation: The DC bus must be constantly regulated to a reference voltage in order to allow the correct operation of the MMC, thus requiring several sensors and signal-conditioning circuits. The imbalance of DC bus voltages between the different submodules causes the emergence of circulating currents, requiring algorithms and mechanisms in order to mitigate this problem;

- The ripple in the DC bus: The harmonic spectrum of the DC bus voltage of each submodule will be concentrated in the fundamental frequency and in the second-order harmonic. Knowing that the voltage ripple is inversely proportional to the frequency of the fundamental component, this effect is more severe in variable speed applications, namely at start-up and at low motor rotating speeds. As such, capacitors with higher capacity are required, inflating implementation costs;

- Circulating currents: This effect does not affect the AC component of the output voltage and current. However, it increases the root mean square (RMS) and peak value of the arm current, consequently increasing the converter losses and the DC bus ripple;

- Fault-tolerance: The MMC is usually implemented with redundant submodules, ready to enter into operation in case of faults. One of the challenges is the decoupling of a damaged submodule and consequent coupling of an operational one, in a dynamic way, without the emergence of inrush currents. Another challenge is the development of protection mechanisms, namely circuit breakers, capable of shutting down the system in the event of a failure, which is especially important in HVDC applications.

In general, it was possible to notice that the development of modular and multilevel power electronics solutions presents an added challenge, mainly in high-voltage and high-power systems. The development of these systems requires a fully coordinated team: highlighting teams of engineers dedicated to the digital control system and implementation of algorithms in microcontrollers; teams dedicated to the development of simulation models; teams dedicated to the development of power electronics converters, semiconductors, transformers, and other magnetic components; a team dedicated to electromagnetic compatibility and signal isolation; mechanical teams for the development of the modular structure and heatsinking; and Computer-Aided Design (CAD) engineers for both the mechanical and electrical systems, such as printed circuit boards (PCB), among others. The development of this system is multidisciplinary, with complex development and validation tasks.

One of the future trends concerning the MLC concept is the cascading of different power converter topologies capable of synthesizing five or more output voltage levels [3]. Different configurations for the MMC using a solid state transformer (SST) can be seen in [61,63,76,77].

System modularity and expandability presented new challenges, particularly in control systems. Knowing that microcontrollers have a limited number of input and output peripherals, the expandability of the system also became limited. One solution would be to integrate a Field Programmable Gate Array (FPGA), since it has a large number of configurable input and output peripherals. However, the system would have to be oversized, or it would lose modularity [76]. In order to mitigate this disadvantage, decentralizing the control has been proposed [78,79,80,81,82]. As a future trend, each submodule would have its own microcontroller, the slaves, and there would be a communication channel with a central unit, the master. This way, the master would be responsible for managing and configuring the different submodules, distributing the tasks to each of them. Therefore, and for correct operation, the communication must be fast, not susceptible to interference, synchronized, and robust in case of failures. Possible contributions include the development of algorithms for plot management, configuration, and control of each submodule. The hardware is equally important, requiring a balanced solution between parallel communication (fast but with a larger number of connections) and serial communication (longer time but fewer connections).

As the system expands, more voltage sensors, more current sensors, more communication, and more monitoring peripherals are needed. As such, and in order to make a simpler, more compact, and cheaper solution, the development of sensorless control algorithms becomes important and interesting [83].

In analyzing the submodules, the assiduous presence of capacitors in the DC bus becomes evident. It becomes important to minimize bulky and lifetime-limited capacitors by using balancing algorithms or appropriate modulation techniques in order to extend the lifetime of the components [83].

In the following subtopics, different topologies of MLC are analyzed. The solution is presented, highlighting the operating modes, as well as presenting some examples of developed practical systems and prototypes. The multilevel system can be achieved either by expanding the topology or by modularity, where more submodules of the same topologies are inserted in series. To highlight that, considering the DC bus, it is necessary to create a dead time for switching between states. The dimensioning of this dead time is crucial in order to avoid a short circuit of the voltage source in the VDC_Link, as well as to avoid potentially destructive operating states.

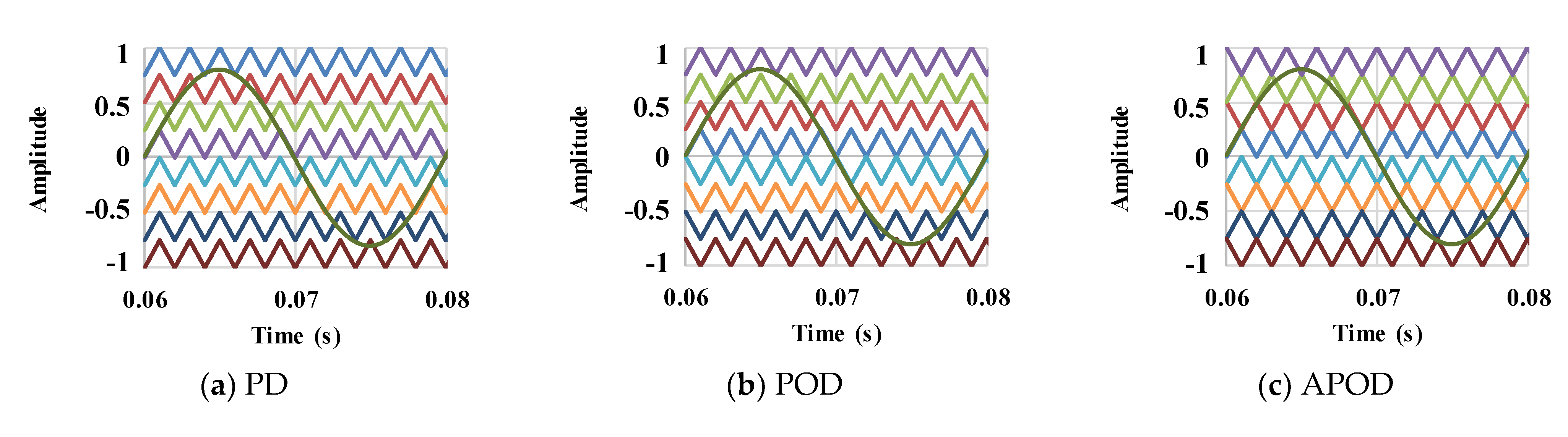

2.1. Half-Bridge Submodule

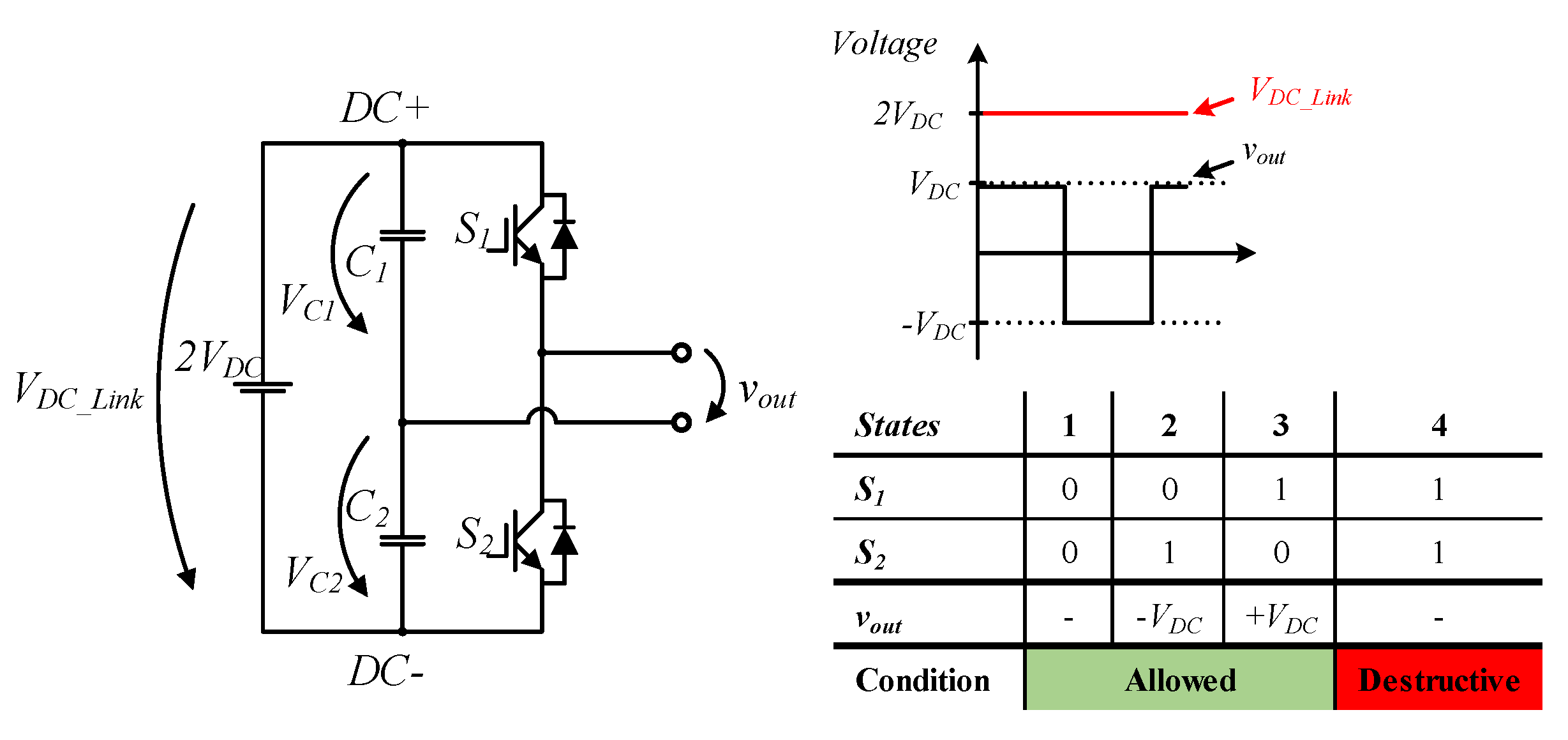

The half-bridge topology has great versatility, with two different approaches: one with the DC bus split and one with a single capacitor on the DC bus.

Regarding the split DC bus half-bridge topology, it has a simple structure, as shown in Figure 3. This topology features two capacitors on the DC bus and two IGBT devices connected in series. The midpoint of the capacitors is used as the reference potential for the output voltage, vout, of the converter [73]. As a consequence, to be able to generate an output voltage with a value of VDC_Link, the DC bus will need to have twice the voltage. Thus, each capacitor that makes up the DC bus will have a voltage equal to VDC_Link. Figure 3 shows the allowed states of operation of the topology.

Figure 3.

Half-bridge with split DC bus topology and operation principle.

In analyzing the literature, it was possible to verify that this topology is not used as a submodule in solutions such as MMC. However, it was possible to verify the integration of this topology together with other power electronics, presenting a hybrid multilevel solution. A five-level hybrid solution is presented in [84], where two half-bridge submodules are cascaded with a full-bridge. Another three-phase hybrid solution is presented in [85], where, for each phase of the electrical system, there are three cascaded half-bridge submodules, two with common DC bus, and one with split DC bus. Although not popular in multilevel applications as single submodule topology, this topology is widely used as an integral part of one of the stages of an SST [86,87,88].

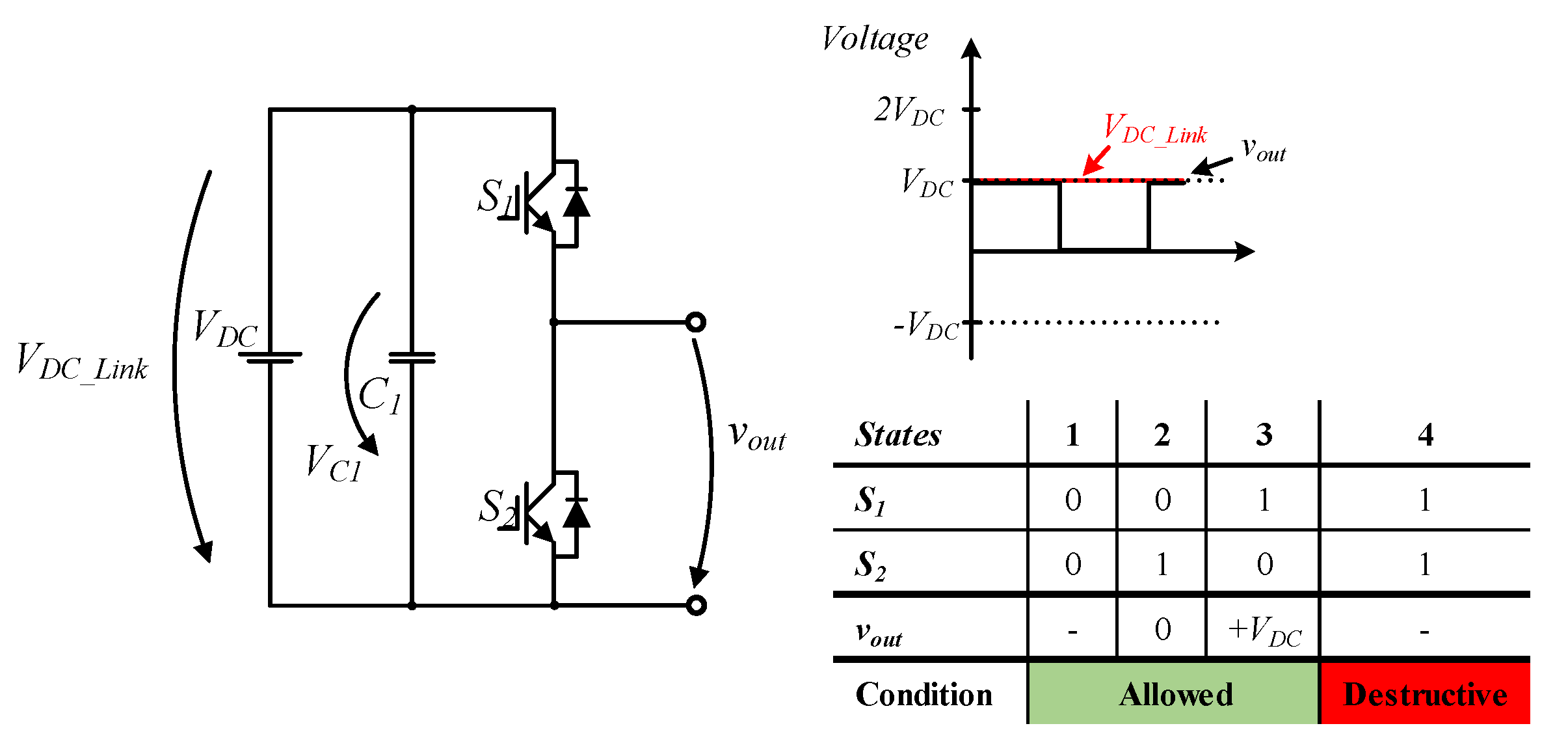

In turn, as far as the half-bridge topology with single DC bus is concerned, it features a single capacitor on the DC bus and two IGBT devices. As a consequence, it only allows two levels of output operation, as represented in Figure 4, always operating with a DC component [73]. This topology is commonly referred to as “chopper cells” [89]. In order to interface with AC applications, this topology needs an auxiliary submodule in order to create a symmetrical state. Thus, it is possible to identify two arms: an upper one responsible for synthesizing the positive semi-cycle and a lower one responsible for synthesizing the negative semi-cycle. The more levels of operation, the more submodules needed. Note that each submodule only allows operation in two quadrants: positive voltage and bidirectional current. However, its simplicity in terms of hardware is quite attractive for the constitution of MMC solutions.

Figure 4.

Half-bridge with single DC bus topology and operation principle.

A hybrid solution is presented in [42], in which they use different cascaded half-bridge submodules. The output is connected to a full-bridge power converter responsible for unipolar modulation. This system is replicated for each phase of the electrical system. Another hybrid solution, for the MMC concept, is presented in [7], where they use a combination of half-bridges with full-bridges. in analyzing the state of the art, it is in the MMC concept that this half-bridge submodule is widely used [38,45,90].

An example of an MMC using 48 half-bridge cells with a 3 kV DC bus and 550 kW output power can be found in [91]. Among several functionalities, the system’s decentralization with redundant operating mechanisms should be highlighted. Considering the complexity of the system, it is important to highlight that this prototype was developed by 26 researchers. The mathematical model of an MMC, as well as some diagram control algorithms, can be found in [77].

2.2. Full-Bridge Submodule

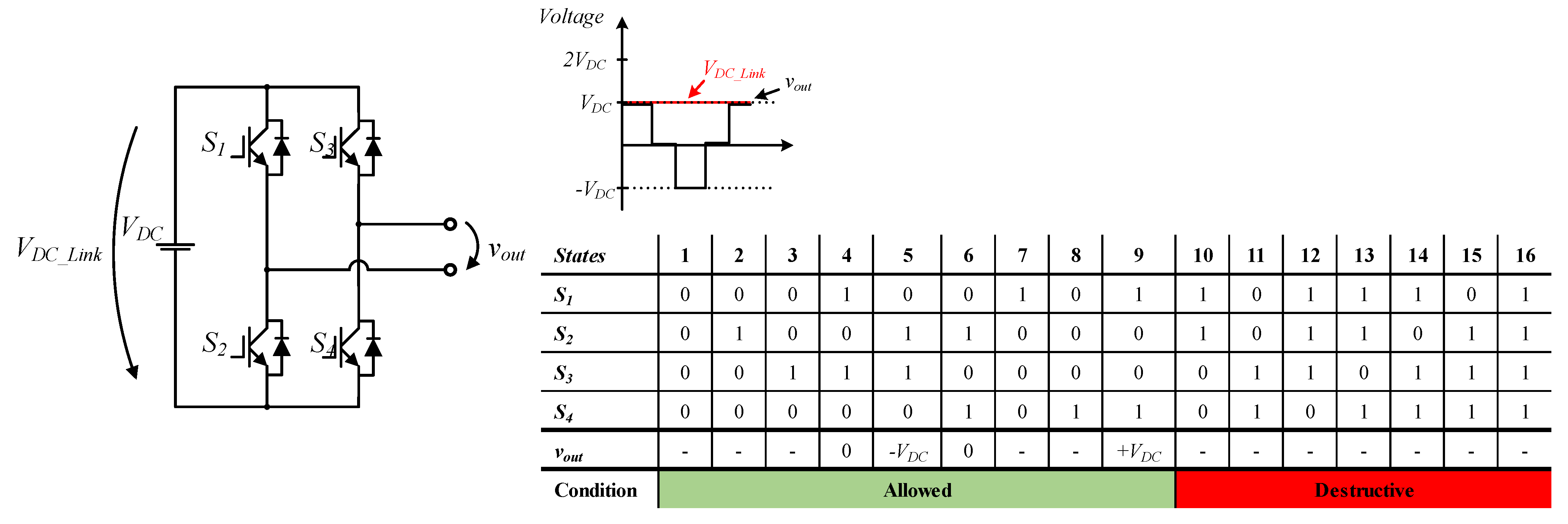

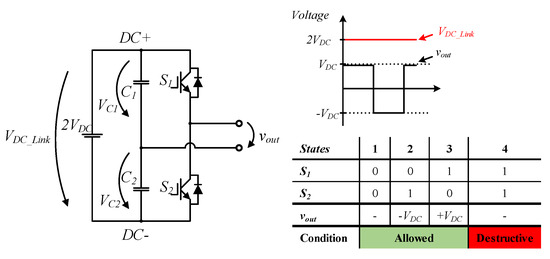

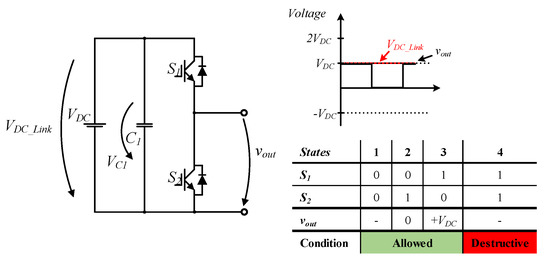

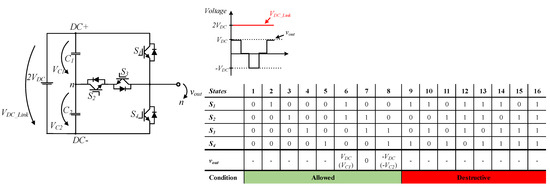

The full-bridge topology consists of four IGBT devices and a DC bus. This power converter topology features two IGBT arms, with each arm consisting of two more IGBTs. The output terminals of the power converter are connected to the midpoint of each arm. This configuration characterizes the converter commonly known as the “H-bridge” [73].

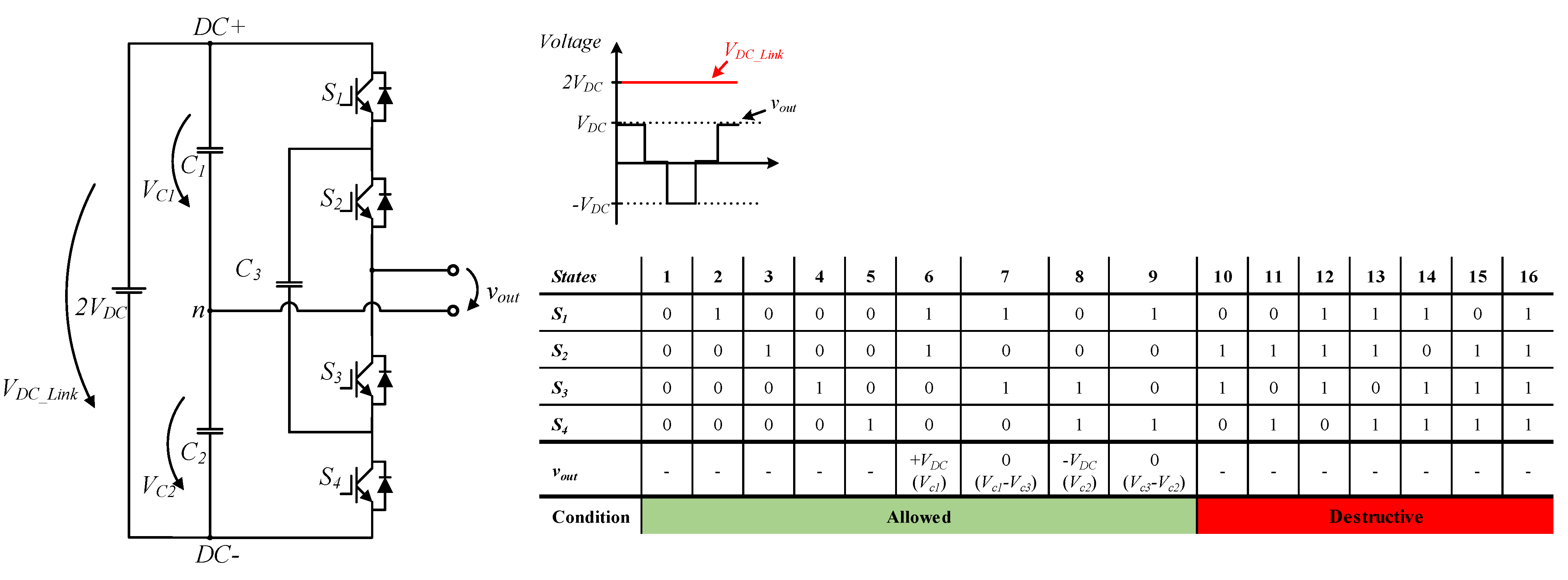

Regarding the operating modes, it should be noted that if the DC bus is a voltage source, the IGBTs that make up each arm should be driven complementarily in order to avoid a short circuit to the DC bus. For this purpose, creating a dead-time for the IGBT devices of the same arm is recommended. In turn, if the DC bus is constituted by a current source, a path for the current must always be maintained. As such, it is necessary to create an overlap time of the semiconductors of the same arm [92]. The operating modes considering a DC voltage source on the DC bus are shown in the Figure 5.

Figure 5.

Full-bridge topology and operation principle.

As far as control is concerned, with the unipolar modulation technique, it is possible to obtain a resulting output frequency of twice the value of the IGBT switching frequency. This is due to the configuration of two arms in parallel. This characteristic enables the integration of less bulky and cheaper passive filters. Nevertheless, this topology allows for operation in four quadrants, as well as generating bipolar signals. However, in case of failure of an IGBT, the submodule is totally inoperable [1].

Regarding the practical implementation, it is possible to identify the existence of different semiconductors referenced to the same potential, which enhances the implementation of simpler and cheaper driver circuits. Nevertheless, this topology is able to generate an output signal with amplitude equal to that of the DC bus. However, during the operating states, there will always be two semiconductors in conduction, presenting an output voltage slightly lower than the DC bus voltage due to the value of the direct voltage of the IGBT.

One of the most common approaches used in multilevel systems with the full-bridge is to cascade different submodules [27,93]. The larger the number of submodules, the higher the output voltage levels and hence the synthesis of a closer to sinusoidal output waveform. Using different voltage levels at each DC bus allows the creation of more voltage levels, consequently decreasing redundant states of operation [39]. In [4], the valid switch states and redundant stages for a five-level cascaded full-bridge are presented. The implementation of the space vector modulation technique (SVM) is the most recommended since it allows the logical combination of each IGBT to be determined in order to generate the desired state. However, the DC buses of each submodule are floating, requiring isolated sources for each, inflating the cost and complexity of implementation [27]. Solutions to mitigate this disadvantage have been developed, such as the use of a single DC-source in one of the submodules, using the redundant states to load the DC buses of each submodule in cascade [94]. SST emerges as an interesting concept that, in addition to allowing the creation of isolated sources for each DC bus, also allows for bidirectional power [61,95].

Another approach consists of connecting different full-bridges in parallel, adding an isolating transformer at the output of each full-bridge. Each submodule shares the same DC bus, with multiple IGBT devices referenced to the same potential, and the secondary side of each transformer is connected in series with the transformer of the adjacent submodule [96,97]. Combining the different transformer ratios of each transformer again allows for a greater number of generated voltage levels by foregoing redundant states [98,99]. In [77], the switching pattern obtained considering an MMCC composed by four full-bridge submodules with four transformers with different turns ratios is presented. However, it should be mentioned that this approach causes an imbalance in the operating powers of each submodule. According to [16], the submodule with a lower switching frequency contributes 80% of the total power transferred. The lower the switching frequency of each submodule, the higher the power. Regarding the power transformers, special attention needs to be paid to their sizing, as well as the instant to start the control.

These approaches have enhanced the study and implementation of innovative solutions, such as solid-state transformers. In [52], it is possible to verify an example of SST application. Each submodule is composed of a dual active bridge (DAB), following a full-bridge. The primary side of each submodule is connected to a single low voltage DC bus, and the outputs of each submodule are connected in series with the adjacent submodule. Among other features, the following advantages can be highlighted: connection of different submodules to a single DC bus, which allows simplification of the control of the DC bus; integration of the phase-shift technique for power transfer in the high-frequency isolating transformer, minimizing the probability of saturating the ferromagnetic core since the flux density cancels out every two switching cycles; a higher power density in the transformer.

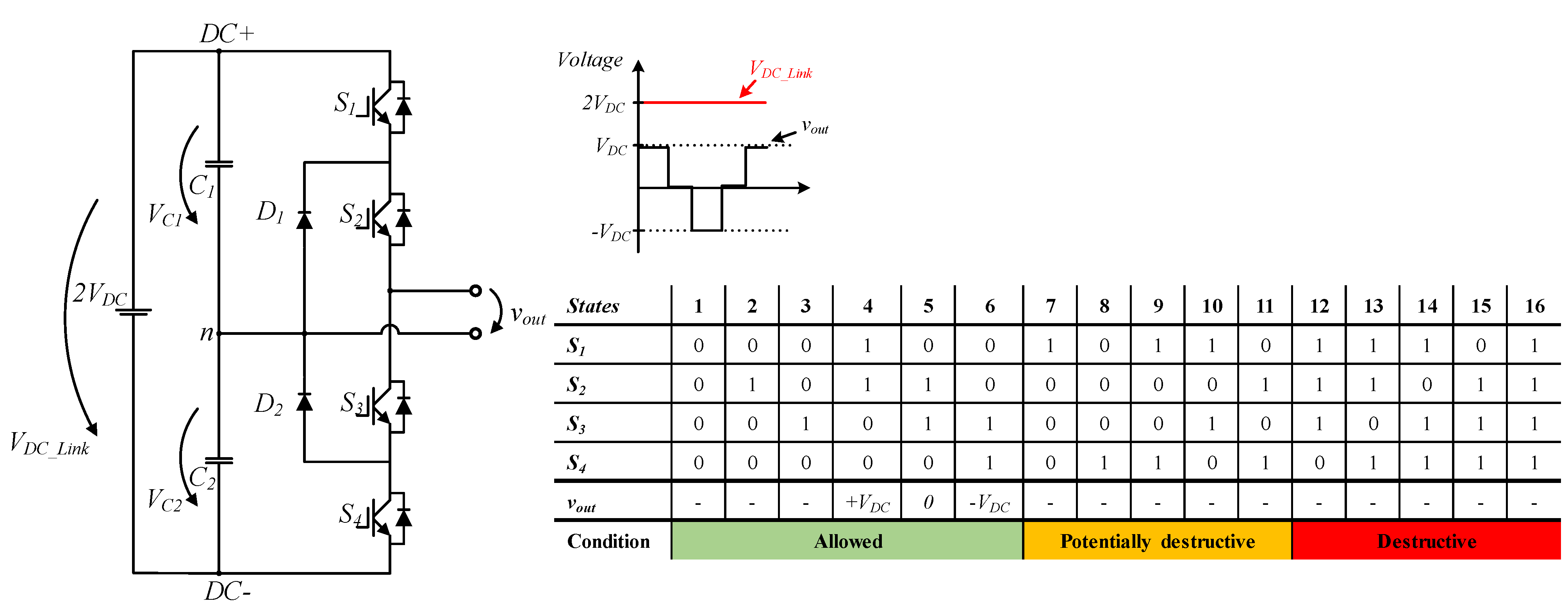

2.3. Neutral Point Clamped Submodule

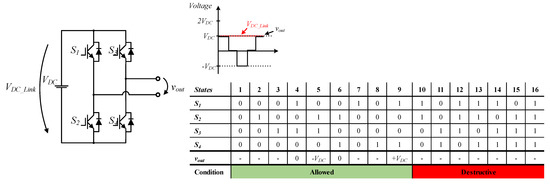

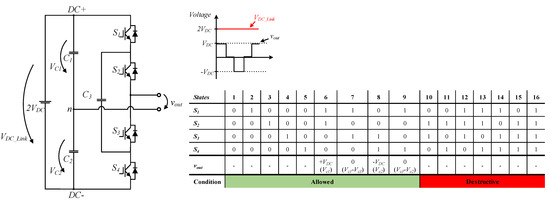

The NPC power converter consists of two arms, as illustrated in the Figure 6. One of the arms, for energy storage and decoupling purposes, consists of two capacitors connected in series, with the midpoint used as the reference potential. In turn, the other arm consists of four IGBT devices connected in series, with the midpoint used as the output terminal [74].

Figure 6.

Conventional NPC topology and operation principle.

The IGBT devices located in the upper part of the arm (S1 and S2) must be activated in a complementary way to the IGBT devices located in the lower part (S3 and S4). In this way, a short circuit to the DC bus is avoided. Depending on the modulation technique implemented, bipolar or unipolar, this topology presents the versatility to generate two or three output voltage levels [4,89].

This topology is expandable, requiring the addition of more semiconductors and capacitors. In [74,100], it is possible to find other variations of this topology, namely in its expandability to more levels. Control algorithms and applications are also presented. However, the more levels, the more diverse the current paths of the converter, with short and long paths to charge the DC bus. Due to this difference in impedances, even with similar semiconductors, this topology has as a major disadvantage the imbalance of the DC bus voltages. Nevertheless, the modulation technique adopted can intensify voltage imbalances. In order to mitigate this problem, different solutions have been explored: active control, active auxiliary circuits, and passive auxiliary circuits. A solution based on active control presents a greater complexity of implementation, requiring a microcontroller with greater processing capacity. In turn, active auxiliary circuits require additional hardware, essentially increasing complexity and cost. Finally, passive auxiliary circuits are characterized by increased system losses, decreasing the efficiency of the converter. This topology only has redundant states of operation between phases (phase–phase) of the power grid and not in the same phase power line. As such, if redundancy is an imposed feature, this NPC is only viable in three-phase applications, where, for example, a six-level NPC can obtain 216 redundant states [101]. The lower the modulation index, the higher the redundant states are [4]. Another variant of the NPC topology used as a submodule can be found in the Figure 7.

Figure 7.

Submodule NPC topology for cascaded applications and operation principle.

A cascaded MLC based on NPC cells was presented by M. Carpanet et al. in [102]. A novel hybrid MLC based on NPC cells cascaded with half-bridge chopper cells for three phase applications was presented in [103]. An SST solution composed by a multilevel DAB converter was proposed in [104], where a three-level NPC was adopted to be used on the high-voltage side.

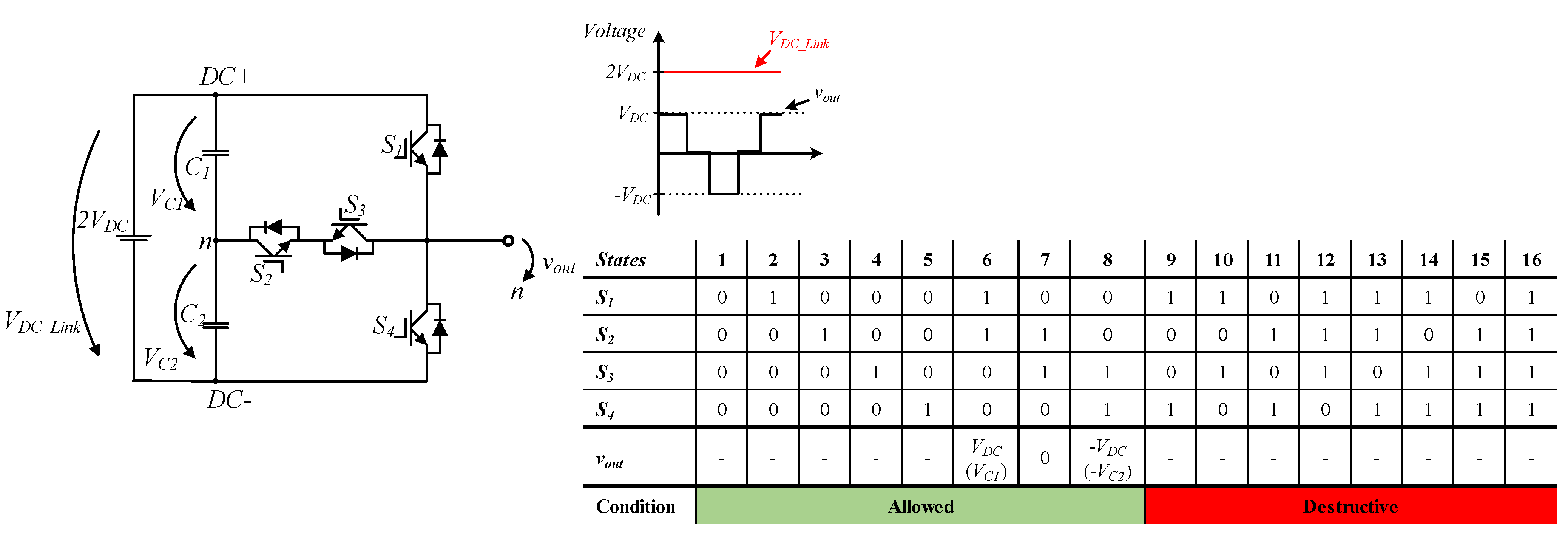

2.4. T-Type Neutral Point Clamping Submodule

The T-type NPC (TNPC) topology has a structure similar to the half-bridge topology with a split DC bus, with the addition of a bidirectional switch between the midpoints of the DC bus and the IGBT arm, as illustrated in Figure 8. The bidirectional switch consists of two IGBT devices connected in anti-series. This configuration is also referred to in the literature as a neutral point pilot (NPP) [59,89].

Figure 8.

T-NPC topology and operation principle.

The design of three-level T-NPC for high speed motor drives using 150 kVA silicon-carbide (SiC) MOSFET was presented in [105]. An MMC solution based on a new four-level T-NPC topology cell was presented in [106].

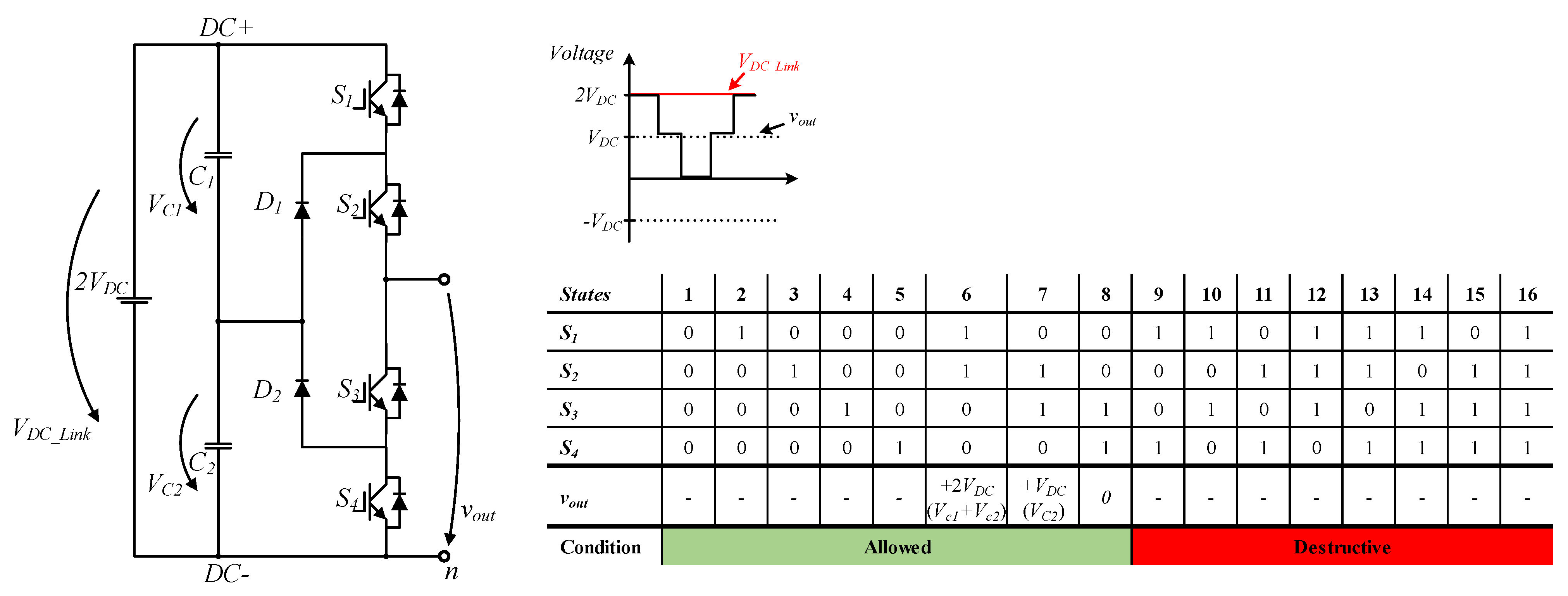

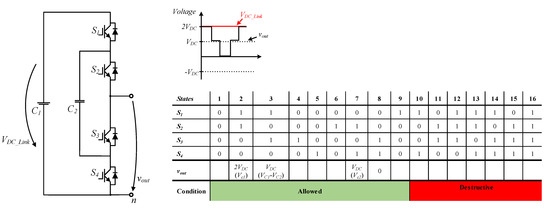

2.5. Flying Capacitor Multilevel Converter Submodule

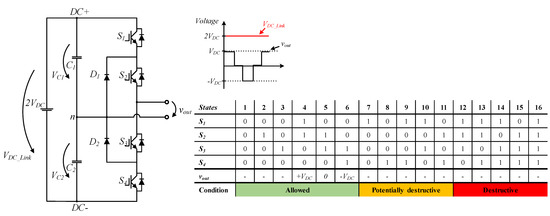

The FCMC topology has a similar structure to the NPC, with the diodes being replaced by a capacitor, as shown in Figure 9. Consequently, the center-located IGBT devices cannot be driven simultaneously in order to avoid short-circuiting the flying capacitor, C3. In order to ensure proper operation of the topology, the voltage of the floating capacitor must be similar to the voltage of each capacitor in the DC bus [100]. Regarding the power semiconductors, these must have a blocking voltage higher than the voltage of each set of capacitors of the DC bus [72].

Figure 9.

FCMC topology and operation principle.

In analyzing the schematic of the topology presented in Figure 9, it is possible to see the predominance of capacitive elements. As such, the topology is susceptible to inrush currents at the startup instant [74]. The implementation of auxiliary pre-charge circuits is recommended in order to minimize this disadvantage. A simple solution is to include resistors between the DC-source and the capacitors during the pre-charge process. As soon as the voltage in the capacitors reaches a minimum operating value, a switch is activated to bypass the resistors. This way, the converter can operate in steady-state without the losses associated with the resistors. In [100], it is possible to find other variations of this topology, namely in its expandability to more levels. Control algorithms and applications are also presented.

The capacitors are the main energy storing element in this topology, playing an important role for the correct operation of the system. The system performance is directly related to the voltage ripple in the capacitors that, consequently, will influence the energy stored in the capacitors. By increasing the switching frequency, it will be possible to decrease the capacity of the capacitors. However, electromagnetic compatibility problems will be intensified. Nevertheless, special care must be taken when choosing the technology of the capacitors, with electrolytic capacitors having a higher capacity despite a poor frequency response when compared to other technologies, such as film capacitors. What is also important is the lifetime of the capacitors, which is low, as well as the space occupied. Comparing the floating capacitor topology with the NPC, it can be concluded that the diodes have a smaller volume than the capacitors.

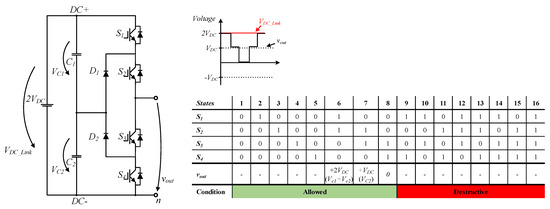

The Figure 10 shows the electrical scheme of the FCMC topology as a submodule presented by Meynard and Foch in 1992 [72]. It should be mentioned that semiconductors S3 and S4 must be activated in a complementary way with semiconductors S1 and S2, respectively. Some potentially destructive operating states could be reached if the control signals are not correctly configured, namely in the state where only S1 is active. From an operating point of view, the DC bus has twice the voltage of capacitor C2. As such, there is a redundant state in which voltage VC2 can be created with S1 = S3 at off and S1 = S2 at on (vout = VC2) or else S1 = S3 at on and S2 = S4 at off (vout = VC1 − VC2) [8]. The redundancy of states, with the expandability of the system, presents itself as an advantage in order to allow different states to charge or discharge a given capacitor [107]. An explanation of the operation modes of this submodule topology can be found in [8,100]. In [4] is presented the switch stage for a six-level FCMC, where it is useful to select a specific capacitor to charge or discharge during the switching pattern. By increasing the number of levels of the FCMC, more redundant states are obtained for different levels [4].

Figure 10.

Conventional submodule NPC topology for cascaded applications and operation principle.

The concept of floating capacitors was used in a project presented for the Google/IEEE Little Box Challenge in [108]. The authors developed an ultra-compact seven-level 2 kW FCMC, with a 450 V DC bus for 240 VAC networks, with a power density of 13.2 W/cm3 and an efficiency of 97.4%. Cascaded FCMC submodules are used to create a seven-level stair waveform, followed by a full-bridge converter so that it is possible to generate a sinusoidal output waveform with a mean value of zero.

2.6. Submodule Topologies Comparison

As analyzed so far, the different topologies have different functionalities, characteristics, and requirements for their correct operation. In this topic, a comparative analysis of the different topologies is performed, some of the characteristics being patent in Table 1. It should be noted that the comparative analysis is carried out from the implementation point of view. That is, the variables are adjusted in order to meet a requirement, such as in the case of the DC bus: the voltage was adjusted so that the power converter could generate an output voltage of VDC.

Table 1.

Comparative table of submodule topologies.

In analyzing Table 1, it is possible to conclude that the greater the number of IGBT devices making up the topology, the greater the number of output voltage levels one can synthesize. An example of this is the half-bridge topology that, with two IGBT devices, can only generate two voltage levels. In contrast, the remaining topologies, with four IGBT devices, can synthesize three levels.

With respect to the DC bus, it can be concluded that topologies with a split DC bus, need the DC bus voltage to be twice the value of the desired output voltage. Nevertheless, splitting the DC bus needs additional sensors and signal conditioning circuits, inflating the cost and complexity of implementation. Nevertheless, regarding the half bridge submodule with a single DC bus, it should be noted that for AC applications an additional module is required. Thus, depending on the number of output voltage levels desired, module replication is required: with one arm responsible for the positive half-cycle and another arm responsible for the negative half-cycle. The duplication of components, namely in voltage sensors, signal conditioning circuits, and capacitors, requires more complex control algorithms, as well as a larger initial investment.

From a practical point of view, two characteristics of the full-bridge topology can be highlighted. The first is the existence of IGBT devices referenced to the same power. If the implementation approach involves associating different submodules in parallel with cascaded transformers, it would be possible to implement simple, robust, and cheaper driver circuits. On the other hand, the full-bridge topology is the only one that features arms with IGBT devices in parallel. This feature allows for obtaining the resulting output frequencies higher than the switching frequency. As such, it is possible to reduce the passive filters and consequently reduce weight, volume, costs, and losses in both the copper and core of the inductive components.

In Table 2, it is possible to identify different approaches for implementing modular and multilevel power electronics solutions for different end applications. The topologies of power electronics converters presented are the topologies that prevail in the final equipment, and there may be different configurations of connections.

Table 2.

Examples of MLC applications.

In turn, Table 3 shows a more detailed analysis from the point of view of implementation and functionalities of different MLCs on the market and developed prototypes. It is possible to compare different powers, input and output voltages, switching frequencies, and the number of levels of the implemented systems. The information presented is based on the information obtained in the study of each article.

Table 3.

Examples of MLC solutions and prototypes developed.

With this study, it is possible to verify that, regardless of the topology used for the MLC solution, the final application presents high power and voltage. However, the higher the system interface voltage level, the greater the number of submodules. However, there are medium-voltage, high-power applications that have a smaller number of output levels, e.g., applications, such as motor speed control, with IGCT as the power semiconductor of choice. It should be noted that in the solutions presented, despite some difficulty in finding this information in all the articles studied, the prevailing PWM technique is the PSC. Finally, it should be noted that the switching frequencies range from a few hundred Hz to a few kHz.

3. Fault Tolerance Applied on MLC and Gate-Driver Circuits

With the increase in the number of MLC operating levels and, consequently, the number of semiconductors and passive components, namely the capacitors, the probability of failure increases. According to [184], there are three zones that relate the probability of failure of an electronic component to its lifetime, whether measured in hours or number of cycles. The first zone is indicated as “infant mortality” or “debug period”, and its fault probability is high, as in the third zone, indicated as “wearout period”. The intermediate zone is characterized by the operation of the system after the debugging period, thus being classified as “constant failure rate” or “useful life period”. Knowing that the third zone indicates the end of the period of the entire system, and total replacement of the system is recommended, the first two are characterized by sporadic and unpredicted failures. Considering that the complexity and cost of an MLC increase with the number of levels, it is required that this system present robustness and fault tolerance. Thus, a continuous operation of the system is intended. In this way, in case of failure of any component or submodule, another operating state would be used in order to allow the continuity of system operation. This process requires four steps: fault detection, fault protection, fault clearing, and fault recovery [185].

In analyzing the bibliography, there is a constant study on the contribution of solutions and control techniques in order to increase the fault tolerance and viability of the MLC, including the use of redundant operating states, the use of redundant submodules, the use of auxiliary circuits and redundant material, and an upgrade on the control algorithms.

Redundancy mechanisms in case of failure are usually classified as “hot reserve” or “cold reserve” [186,187]. In the case of hot reserve, only one bypass is performed to the failure submodule, keeping the system in operation [188]. In turn, in the case of cold reserve, the failed submodule is replaced by a redundant submodule [189]. In this way, it is possible to predict that the hot reserve mechanism causes an asymmetric operation of the converter, as well as increasing energy losses. The increase in the rated operating conditions can lead to an increase in the operating temperature of the submodule, making it more susceptible to failures (25% of failures are caused by thermal fatigue [190]). In turn, the cold reserve mechanism presents as a major challenge the existence of mechanisms with galvanic isolation in order to preload the reserve submodules, in order to minimize transients and the impact on the performance of the control algorithms [191].

Regarding semiconductor failures, namely fully controlled ones, they can fail and remain in open or closed circuits (33% of failures are related to semiconductors [190]). In the event of a failure with the semiconductor in an open circuit (18% of failure cases [190]), it can either occur due to semiconductor burnout or loss of the control signal [190]. In this situation, the MLC may continue to function based on redundant states. There must be multiple redundant operating states for each operating level, or voltage levels will be lost. If it is not possible to obtain redundant states for all voltage levels, another mechanism is recommended. Different open circuit semiconductor failure detection techniques can be found, such as using the clustering algorithm or an algorithm based on a calculated capacitance [192]; using the MLC behavior observation method [193,194,195]; using the method based on the Sliding Mode Observer [196]; using the Luenberger Observer method [197]; using the Kalman filter [194]; or using the Fourier transform to detect a failure in an FCMC [198]. In turn, in case the failure causes a short circuit to the semiconductor (15% of failure cases [190]), a bypass mechanism is necessary in order to remove the failed submodule. This mechanism is also used in case of failure of passive elements. The inoperable submodule will remain in the system until the next scheduled maintenance. The bypass mechanism uses vacuum valves for quick disconnection of the submodule and is used in Siemens and Alstom MMC systems [5]. There are fault detection circuits with a quick response to over-voltages [199]. In [200], a method based on the behavior of the IGBT gate voltage is presented in which it detects the operation failure in less than 10 us, whether the failure is in a short circuit or open circuit. A voltage balancing strategy is presented in [201], which uses a voltage sensorless prediction method to locate the faulty submodule. Results obtained in “hardware in the loop” state that in 35.4 ms, the system can determine an open-circuit fault and in 3.2 ms a closed-circuit fault. After detecting the fault, the system isolates the faulty submodules and then recalculates the new system operating variables in order to suppress the missing submodule.

After the failure is detected, the system can continue operating with or without the addition of redundant submodules. In the case of redundant submodules, they can be connected to the system, using fast DC breaker mechanisms [202]. Another breaker circuit is presented in [203] for DC faults in MMC applications. The authors of [204] present a fault-tolerant solution based on spare submodules for topologies with cascaded full bridges in three-phase systems.

On the other hand, control techniques can be used in order to maintain the incorruptibility of the system without the need to add more submodules. One of the techniques is to keep the average bus voltage of each submodule constant (Method 1) or keep the average bus voltage of the entire system constant (Method 2) [5,205]. With Method 1, the remaining healthy submodules should be able to detect and compensate for the failure of the damaged submodule by adjusting the modulation index. With this technique, the operating voltages of each submodule are respected, although there may be overmodulation. More failures may occur as long as it is possible to obtain an output voltage of the MLC higher than the peak voltage of the electrical network, the modulation index being readjusted [5,205]. In turn, with Method 2, by keeping the average voltage of the entire system constant, it is necessary for each submodule to compensate for the failure by increasing the average voltages of the DC bus of each submodule. This method requires each submodule to be oversized in terms of operating voltages. That is, the nominal voltages of the capacitors and the blocking voltages of the semiconductors must be oversized, and this compensation may be limited with the increase in the number of faults [5,205]. A comparative study of these two methods is presented in [205]. A review of IGBT fault diagnosis methods and protection mechanisms for VSIs is presented in [206]. The determination of the energy stored in the capacitors for different methods of operation can be found in [5,191].

Considering that electrolytic capacitors have a limited lifetime, one of the malfunctions can occur on the DC bus. In this case, a quick response to mitigate the failure and provide a solution is necessary for the continued operation of the system. A DC bus short circuit fault determination method is presented in [207], obtaining a 1 ms response. Considering the propagation time of the signal over 200 km, the mechanism ensures that the protection is activated after 2 ms. Simple and inexpensive mechanisms for momentary DC bus failures have also been studied and proposed [12]. Auxiliary supplies to preload and minimize transients for a start-up is a costly but critical factor. Strategies using power loops in order to transfer power from neighboring submodules to the faulty cell are proposed in [208]; the system is based on an MMCC with hybrid energy storage systems (battery and supercapacitor).

Regarding the gate-drive circuits, the control of the semiconductor devices that make up the MLC solutions is presented as a crucial topic of analysis for the correct functioning of the entire system. The variation of the reference potentials can cause circulating currents, affecting the performance of the driver circuit. The increase in levels is reflected in the increased need for a highly reliable driver circuit. Nevertheless, as switching frequencies increase, semiconductor devices are subject to greater dv/dt stress, reaching values of 100 kV/µs in the case of the SiC MOSFET, imposing the requirement of low capacities between the input and the output of the driver [209]. Moreover, dv/dt stress can shorten the lifetime of electrical insulation, eventually breaking down and damaging the semiconductor. For the correct implementation of a circuit driver, three premises are necessary: (i) high electrical isolation, (ii) low coupling capacity, (iii) optimized driver circuit footprint layout [209]. However, it is impossible to provide a solution with the best of the three requirements; it is necessary to find a tradeoff solution, depending on the final application. Knowing the common mode current is directly proportional to the insulation capacity and to the dv/dt [209], the MLC solutions allow for assisting in the mitigation of the dv/dt. Other mechanisms can be implemented, some of which are presented below.

In [210], the authors analyze the effects of four different layout architectures for the gate driver circuits in order to minimize common-mode currents and, thus, minimize electromagnetic interference. A solution based on isolated sources with an optimized PCB layout to be integrated into a half-bridge submodule with overvoltage protection mechanisms was implemented in [38].

Taking into account that the use of isolated DC–DC sources for each driver circuit makes the solution more expensive, bulky, and energy inefficient; the authors of [211] present five driver methods applied in FCMCs based on bootstrap in order to mitigate these problems. Among the implemented methods, the following can be enumerated: (i) bootstrap at deadtime, more suitable for the gallium nitride (GaN) power switch; (ii) cascaded bootstrap with the low-dropout regulator, despite its simplicity, needs a high-voltage power supply; (iii) double charge pump, presents a low-efficiency solution; (iv) synchronous bootstrap, can reduce the voltage drop across the bootstrap diode but can be critical in applications with extreme duty cycles; (v) gate driver charge pump, features high efficiency. A smart gate driver is presented by [212], where bidirectional and fast communication channels are used, thus allowing a modular implementation and expansion of the driver system. A similar approach was implemented in an MMC in [213]. Another modular gate driver circuit used in an NPC is presented in [214] and analyzed in [215].

A driver circuit with short circuit protection at 5 µs, coupling capacitance of 1.2 pF, and tested for voltages up to 6 kV can be found in [209]. An analysis of different gate driver power supply techniques is presented in [216], mentioning wireless power transfer techniques for a single driver or multiple drivers, a conventional self-powering integrable cell, and a resonant and snubber capacitor. Solutions for the gate drive to mitigate the common modo noise [217] or resonant circuits [218] and equipped with optical fiber for the gate control signals can also be found. Other driver systems can be found in [219,220].

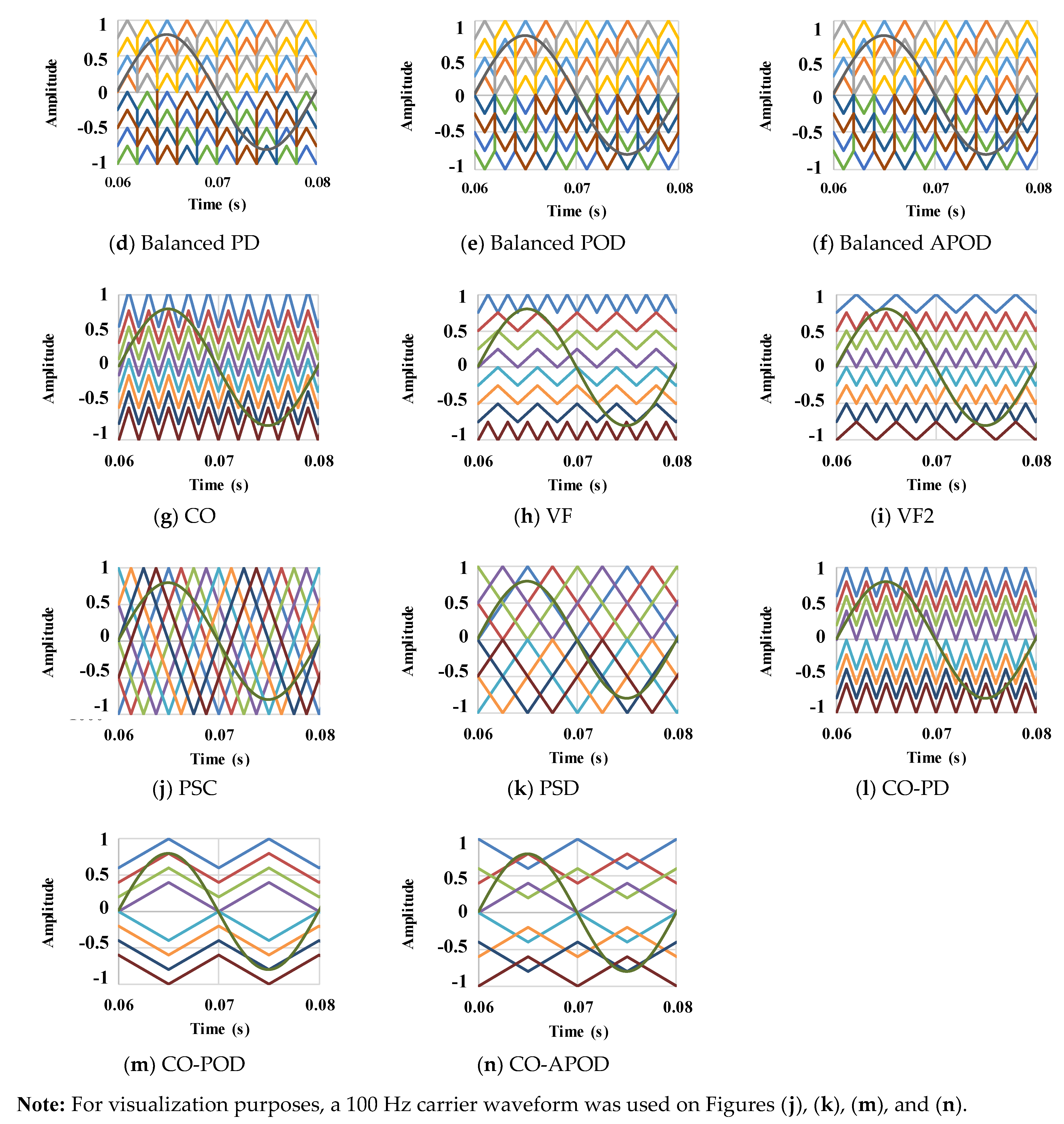

4. PWM Techniques Applied on MLC

In this section, different PWM modulation techniques applied in MLCs are presented and analyzed. These PWM techniques can be replicated with any MLC topology, requiring the correct configuration and sequence of PWM signals. It should be mentioned that there are PWM techniques that emerged in order to respond to some disadvantages of existing PWM techniques, not invalidating their implementation for other topologies for study and comparative analysis. Nevertheless, these techniques can be replicated for three-phase systems, where the correct configuration and phase delay adjustment of the carrier waveforms must be carried out for each phase of the three-phase power grid. A comparative study of the performance of different PWM techniques in the cascaded full-bridge topology is also presented.

4.1. Level-Shift PWM Technique

Level-shift PWM techniques were initially proposed for controlling MLCs with different IGBT devices in series, such as NPC or FCMCs. However, when these techniques were implemented in cascaded topologies, they created power imbalances between the different submodules. The unbalanced operation gives rise to the injection of harmonic content into the power grid and circulates currents between submodules [65]. In order to mitigate these problems, different approaches have been proposed, with some of them analyzed below.

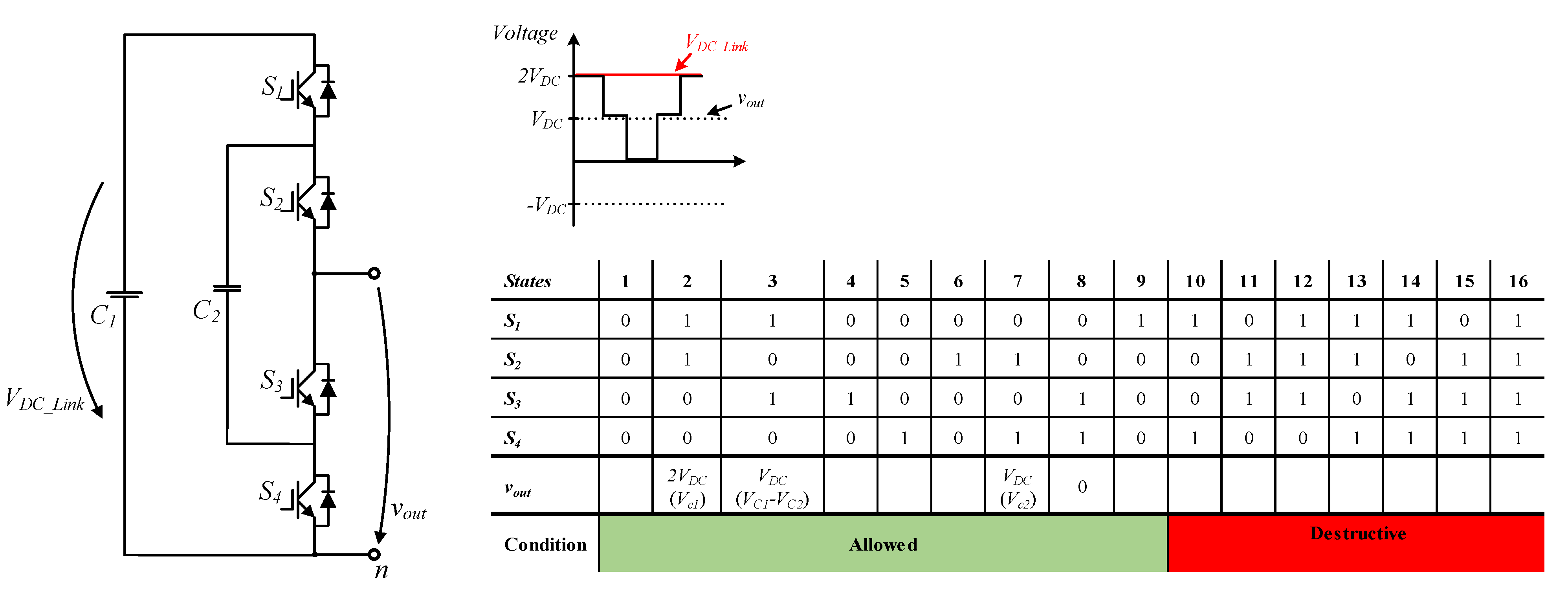

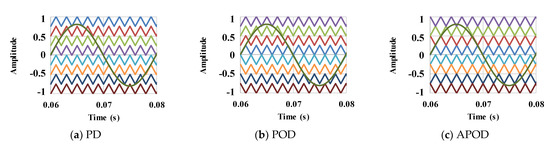

The simplest modulation techniques concerning level shift can be listed as follows: phase disposition (PD), phase opposition disposition (POD), and alternate phase opposition disposition (APOD). These techniques have in common the vertical arrangement of different carrier waves. The carrier waves have the same amplitude and frequency, but their average value (offset) varies.

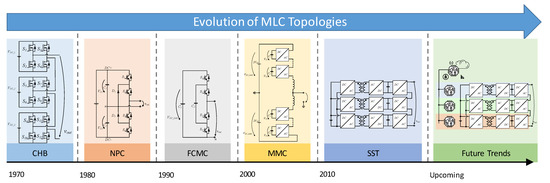

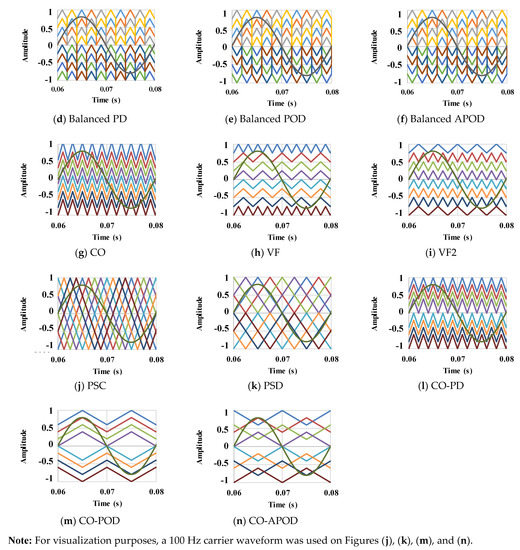

Regarding the PD technique, the carrier waves are synchronized with the same phase angle, as represented in the Figure 11a. In turn, the POD technique presents carrier waves with symmetry to the zero-reference axis. That is, the positive value carrier waves are synchronized with a phase angle of 0°, while the negative value carrier waves are synchronized with a phase angle of 180°, as illustrated in Figure 11b. Finally, for the APOD technique, all carrier waveforms are 180° lagged alternately, as shown in Figure 11c. Note that, due to the alternating arrangement in the carrier waveforms, the modulation presents symmetry in relation to the zero-reference axis. In the following three figures is represented an approach in order to mitigate the previously mentioned imbalance problems, which are balanced PD in Figure 11a, balanced POD in Figure 11b, and balanced APOD in Figure 11c. This approach consists of varying the average value of the carrier waves at each switching period [221]. This permutation technique can be integrated with any level shifting technique. In this way, in short periods of time, it is possible to balance the contribution of each module in the synthesized waveform. Note that the permutation must be performed along all levels, and not only to the adjacent levels. Otherwise, with the greater the number of levels, and if the permutation is performed only on adjacent modules, the imbalance will be still evident.

Figure 11.

Illustration of the carrier and modulation wave forms for different PWM techniques: (a) PD, (b) POD, (c) APOD, (d) Balanced PD, (e) Balanced POD, (f) Balanced APOD, (g) CO, (h) VF, (i) VF2, (j) PSC, (k) PSD, (l) CO-PD, (m) CO-POD, (n) CO-APOD.

Carrier overlapping (CO) appears as another group of techniques that, as the name implies, consists of overlapping the carrier waves. The carrier waves have the same frequency, angle, and amplitude, varying the average value. The amplitude value of each carrier wave can be defined by the ratio of twice the maximum peak-to-peak value of the carrier wave spectrum by the number of carrier waves, N, needed, plus one, as represented in Equation (1). That is, analyzing the example shown in Figure 11g, if the maximum value is 2000 and eight carrier waves are needed, the amplitude value should be 444. In turn, the overlap value represents half of the amplitude, it being 222 in the exemplified case.

Due to the overlap of the carrier waves, the modulating wave intersects more often with the carrier waves, minimizing the dispersion of the harmonic content. Thus, with the correct sizing of the modulation index, it is possible to obtain an improvement in system performance when compared to other modulation techniques. The study presented in [101] aids in calculating the better modulation index for MLCs. In the case of the NPC converter with three levels, this characteristic is evident for a modulation index below 70%. In turn, for an index higher than 80%, the harmonic content is similar. Despite the existence of this modulation technique in the literature, there is no scientific content describing its practical implementation.

In cascaded MLC applications, when the output voltage reaches maximum values, the bus voltages of the peripheral modules tend to oscillate [65]. By adopting a different switching frequency in these submodules, it is possible to minimize the voltage ripple in the capacitors, consequently improving the quality of the output waveform. The variable frequency (VF) PWM technique whose carrier waves from the peripheral submodules have higher frequencies is exemplified in Figure 11h.

In turn, in converters such as the NPC, the IGBT devices located at the periphery have a higher switching frequency than the internally located IGBT devices. Consequently, an analogous variable frequency 2 (VF2) approach is required in order to equalize the switching losses [65]. As such, the internal carrier waves have a higher frequency than the peripheral carrier waves, as exemplified in Figure 11i, making all the IGBT devices that make up the topology able to switch at similar frequencies. An experimental result of a five-level NPC using the VF2 can be found in [222].

In general, with the implementation of carrier waves with different frequencies, depending on each specific application, it is possible to reduce the output harmonic spectrum through harmonic cancellation.

4.2. Phase-Shift Carrier PWM Technique

The phase-shift carrier (PSC) PWM technique is one of the most widely used in power electronics applications. One of the reasons lies in its easy implementation, with digital signal controllers (DSC) with their own registers for phase angle control and synchronization with other carrier waves. The carrier waves of the PSC PWM technique share the same amplitude, frequency, and mean value. The carrier waves have a phase angle between them of 2π/n, as represented in Figure 11j. Knowing that n represents the number of arms and that in an MLC consisting of four cascaded full-bridge, there are right semiconductor arms, the carrier waves would be 45° lagged between them.

By analyzing Figure 11j, it is possible to predict that the modulating wave will intercept the carrier waves more often. As such, each submodule will contribute to the generation of the output waveform in a more similar way. That is, each submodule will exhibit similar operating powers and outputs. In cascaded applications, the voltage ripple of the buses will be similar. These characteristics enhance the concept of modularity. However, the PSC technique is not suitable for topologies such as NPC since it has a lower sensitivity and effectiveness to DC bus voltage ripples when compared to the VF technique [65].

4.3. Hybrid Carrier PWM Technique

Hybrid techniques consist of the fusion of different techniques, enhancing the most advantageous characteristics of each one. Some examples of combinations are phase-shift disposition (PSD), carrier overlapping disposition (COD), carrier overlapping phase disposition (CO-PD), carrier overlapping opposition disposition (CO-POD), and carrier overlap-alternate phase opposition disposition (CO-APOD). It should be mentioned that the hybrid technique has the major restriction of synthesizing M odd output voltage levels [65].

Combining the PSC and PD techniques, the PSD technique capable of controlling an MLC with M output voltage levels can be obtained. By analyzing Figure 11k, it is possible to see the existence of (M-1)/2 carrier waves above the zero-reference line. These waves have the same amplitude, frequency, and average value but have different phase angles. The remaining (M-1)/2 carrier waves have a symmetric average value, being therefore below the zero-reference line. Consequently, it is possible to see that there is symmetry to the zero-reference axis. The harmonic content resulting from the PSD technique is concentrated in fc(M-1)/2, fc being the frequency of the carrier waveform. As such, it is simple to eliminate the harmonic content resulting from IGBT switching through passive filters tuned to this frequency. In [65], the authors state that in five-level NPC (5L-NPC) applications with a modulation index higher than 70%, this modulation technique presents lower switching losses compared to PD, POD, APOD, CO, PSC, and COD.

Combining the CO technique with the level shift techniques, the COD technique can be obtained. This technique always has two groups of (M-1)/2 carrier waves. Depending on the technique used for level shift, different arrangements can be obtained. The carrier waves have the same frequency and amplitude, with the average value imposed by the CO technique and the phase angle by the PD technique.

The combination of the PD and CO technique gives the CO-PD technique, where the carrier waves have the same amplitude, frequency and phase, but different average values, as exemplified in Figure 11l. In turn, combining the POD and CO techniques produces the CO-POD technique, where the carrier waves below the zero-reference axis are 180° out of phase with respect to the upper carrier waves, as can be seen in Figure 11m. Finally, combining the APOD and CO techniques produces the CO-APOD technique, as illustrated in Figure 11n.

Note that the y axis shown in Figure 11 represents the amplitude of the carrier and modulator waves. In practical implementation, the amplitude values of each wave should be adjusted according to the registers of the peripheral used as PWM. Nevertheless, the values must be shifted vertically in order to always obtain positive values. It should be mentioned that there are DSCs, such as those of the C2000 family from Texas Instruments, as dedicated registers for easy configuration of the carrier wave lags. However, the vertical displacement of the waves does not present the same ease, and sometimes, conditions are implemented in order to adapt the modulating wave to obtain effects similar to the vertical displacement of the carriers. A comparative and informative study on how to implement these modulation techniques in C language would be interesting and a strong contribution to the development of modular and multilevel power electronics solutions.

4.4. Other Modulation Techniques

Other modulation techniques can be found in the literature, namely square wave modulation. This technique is mostly used in MMC applications with SST, allowing for the minimization of the value of the capacitance of the DC bus capacitors [223], the reduction in the dv/dt stress of the semiconductors [224], the optimization of the transformer flux density [225], the minimization of core losses, and the maximization of energy transfer on the transformer [226].

Modular and multilevel solutions, such as the MMC and MMCC, are particularly adapted for high-voltage and high-power applications due to the aforementioned intrinsic characteristics. However, in order to achieve a minimum DC bus voltage, it is necessary to connect several submodules. The combination of different submodules with slight differences in capacitance values, parasitic impedances, PWM techniques used, and different IGBT conduction times leads to different capacitor charge and discharge patterns. Some PWM techniques can minimize this problem, but, ultimately, balancing algorithms are needed. Consequently, not only does the DC bus regulation algorithm increase in complexity, but more signal acquisition hardware is needed with the increase in the number of submodules. It should be mentioned that the increase in this complexity leads to a longer processing time in the centralized microcontroller. In order to increase the efficiency of the MMC and MMCC, it is necessary to correctly size the number of submodules and the modulation indices, as well as to implement the correct DC bus balancing algorithms.

Regarding the balancing algorithms, they use redundant states in order to combine the output synthesized level of the MMC with the balancing of the capacitors’ voltages. The alternation of the operating states of the submodules in order to balance the capacitors voltages is one of the most-used solutions in MMCs and MMCCs. The performance of a balancing algorithm for a STATCOM composed of seven cascaded full-bridge converters for each phase of the power grid and with an unbalanced DC bus at the beginning is presented in [227].

In applications focused on very high voltage, with hundreds of submodules, the complexity and processing time can reduce the effectiveness of the control. On the other side, the voltage contribution of each submodule is relatively low. Then, the desired output voltage can be synthesized by adding up an appropriate number of submodules according to the phase angle of the reference voltage. This is the degree of freedom allowed in the development of sorting algorithms for the selection of the submodules to be in service in each time interval. Reference voltage level, submodule voltage, capacitor voltage balancing, etc. are parameters used by the sorting algorithms to select the submodules to be connected. As such, capacitor voltage prediction strategies of a half-bridge MMC [228] (saving 2/3 of the time compared to the commonly implemented quicksort algorithm for an arm with 100 submodules), the odd–even sorting technique implemented in FPGA [229] or a full-bridge MMC [230], techniques based on the grouping and sorting of MMCs [231] with decentralized control [232], the “Tortoise and the Hare” sorting method [233], a fundamental frequency with staircase modulation [234] or with a PSC [235] sorting algorithm for MMC, and a current sensorless sorting and selection algorithm [236] have been studied and implemented. Different balancing techniques were also studied in an MMC based on SST [237].

The SVM technique appears as another technique for controlling the semiconductors that make up the MLC. This technique consists of different sectors, which make up a switching state, and the algorithm will determine the sector that better eliminates the output operation error. In three-phase MLC applications, the number of redundant states increases substantially and is indicated for these systems. However, and despite the good characteristics for single-phase systems, namely determining the best operating status and keeping the DC bus regulated, there is still a gap in the contribution of this system. Contributions at the level of implementation in programming language and migration to a single-phase system depending on the chosen topology are necessary. Although the SVM technique is beyond the scope of this article, it is possible to find in the literature the SVM technique implemented in an MMC consisting of FCMC [238], a simplified SVM for a five-level MMC [239], an SVM implemented for a three-level NPC [240], and an approach for single-phase applications [241,242].

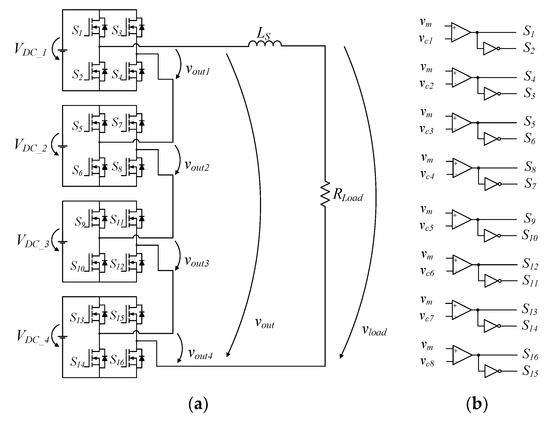

5. Simulation Results of PWM Techniques Applied on a Full-Bridge Cascade Converter

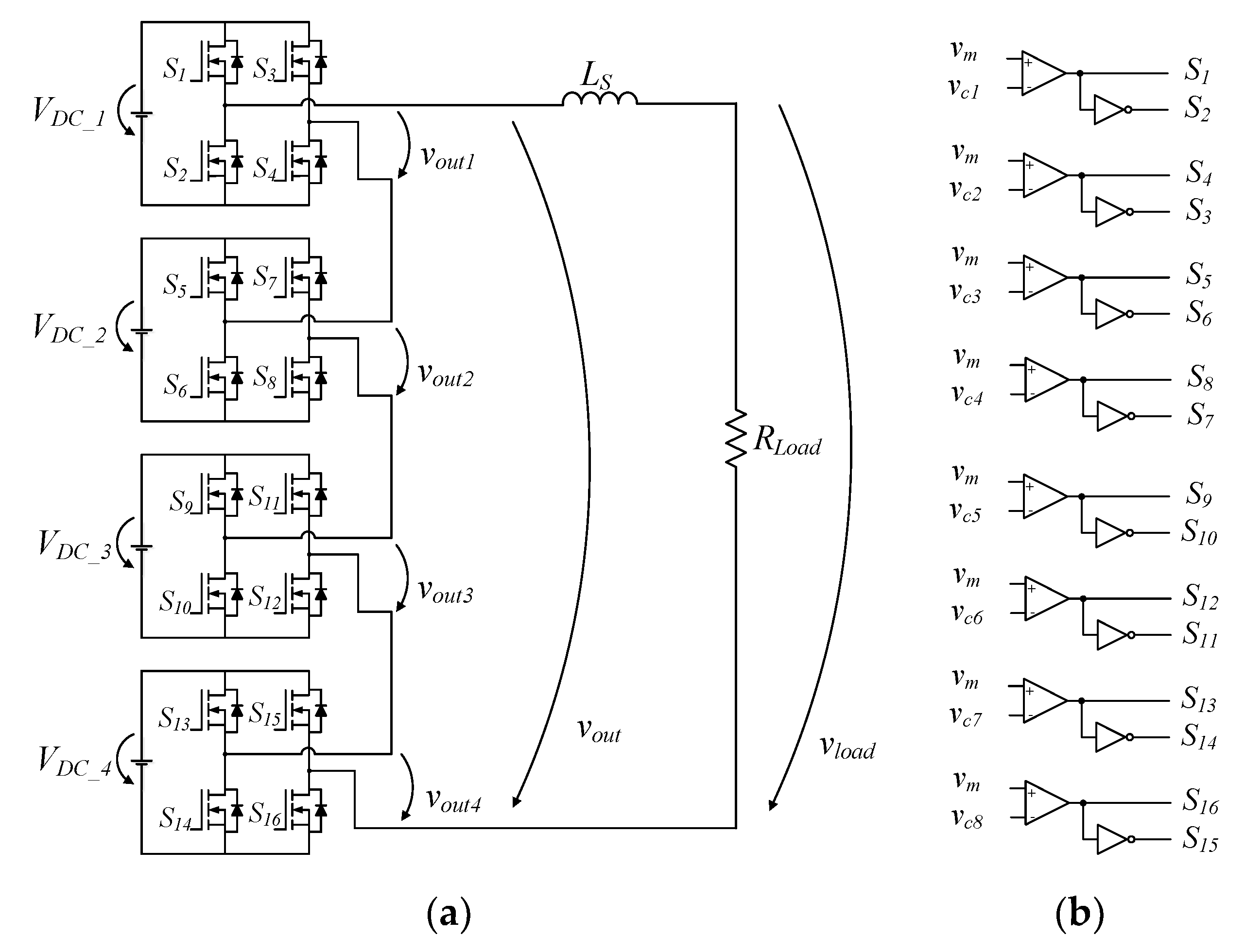

In this topic, a comparative analysis of different PWM modulation techniques based on computer simulations is performed. The simulation model was implemented in PSIM software, and the main parameters used are presented in Table 4. The Semikron IGBT with the reference SKM100GB12V was considered in order to obtain some real parameters for the IGBT model used in simulation. The MLC topology adopted was the cascaded four full-bridges submodules, being the electrical schematic shown in Figure 12a. A DC-source was connected to the DC bus of each submodule, keeping the bus voltage constant. The PWM signal sequence and logic are illustrated in Figure 12b. It should be mentioned that the modulation index and a current control algorithm should be adjusted for the final application. Some examples of control algorithms can be based on integral proportional, resonant proportional, and dead-beat predictive controls, among others [243,244]. The authors of [77] present the integration of some control methods in MLCs, namely positive and negative sequence detectors and current control, zero sequence current control, DC voltage equalization, circulating current compensation, and others.

Table 4.

Main simulation parameters.

Figure 12.

Electrical schematic of the (a) cascaded full-bridge and (b) PWM control circuit.

With this configuration of four submodules composed of full-bridges topology, it is possible to obtain 256 redundant states, with each voltage level having a limited number of states, as shown in Table 5. By analyzing Table 5, it is possible to verify that there is only one state to generate 4 VDC at the vout, when the four submodules are generating VDC. On the other hand, to generate 3 VDC, there are right states: when three of the submodules are generating VDC and a single submodule is generating 0. As there are two possibilities of generating 0 and four submodules, it is possible to obtain the right states. Continuing with the analysis, to generate 2 VDC, there are twenty-eight redundant states that are essentially divided into two conditions: (i) when three submodules generate 3 VDC and another submodule generates −VDC and (ii) when two submodules generate 2 VDC and the others are generating 0. Within these conditions, there are four combinations to generate 3 VDC − VDC and twenty-four combinations to generate 2 VDC + 0 + 0. In turn, to generate VDC, there are fifty-six states, which can be divided into two conditions: (i) two submodules to generate 2 VDC, one generating −VDC and the fourth submodule generating 0 and (ii) one submodule generating VDC and the remaining three submodules generating 0. Regarding the first condition, there are twelve possible combinations to generate 2 VDC − VDC + 0. Once there are two conditions to generate 0, the number of states is doubled, thus accounting for twenty-four states for 2 VDC − VDC + 0. In turn, for the VDC + 0 + 0 + 0 condition, there are thirty-two states. Finally, for the 0 state, it is possible to count fifty-four states, which can be divided into three conditions: (i) when two submodules generate 2 VDC and the remaining two submodules are generating −2 VDC; (ii) when a submodule is generating VDC, one submodule is generating −VDC, and the remaining two submodules are generating 0; and (iii) all submodules are generating 0. For the first condition, there are six possibilities for generating 2 VDC − 2 VDC. Regarding the second condition, there are twelve states to generate VDC − VDC + 0 + 0. As there are two possibilities of 0 VDC, the number of states is replicated to twenty-four. Regarding the last group, it is possible to count twenty-four states to generate the condition 0 + 0 + 0 + 0.

Table 5.

Redundant states for the cascaded four submodules full-bridge.

For negative values, the number of states is equal to the number of positive values, changing the condition to generate − VDC.

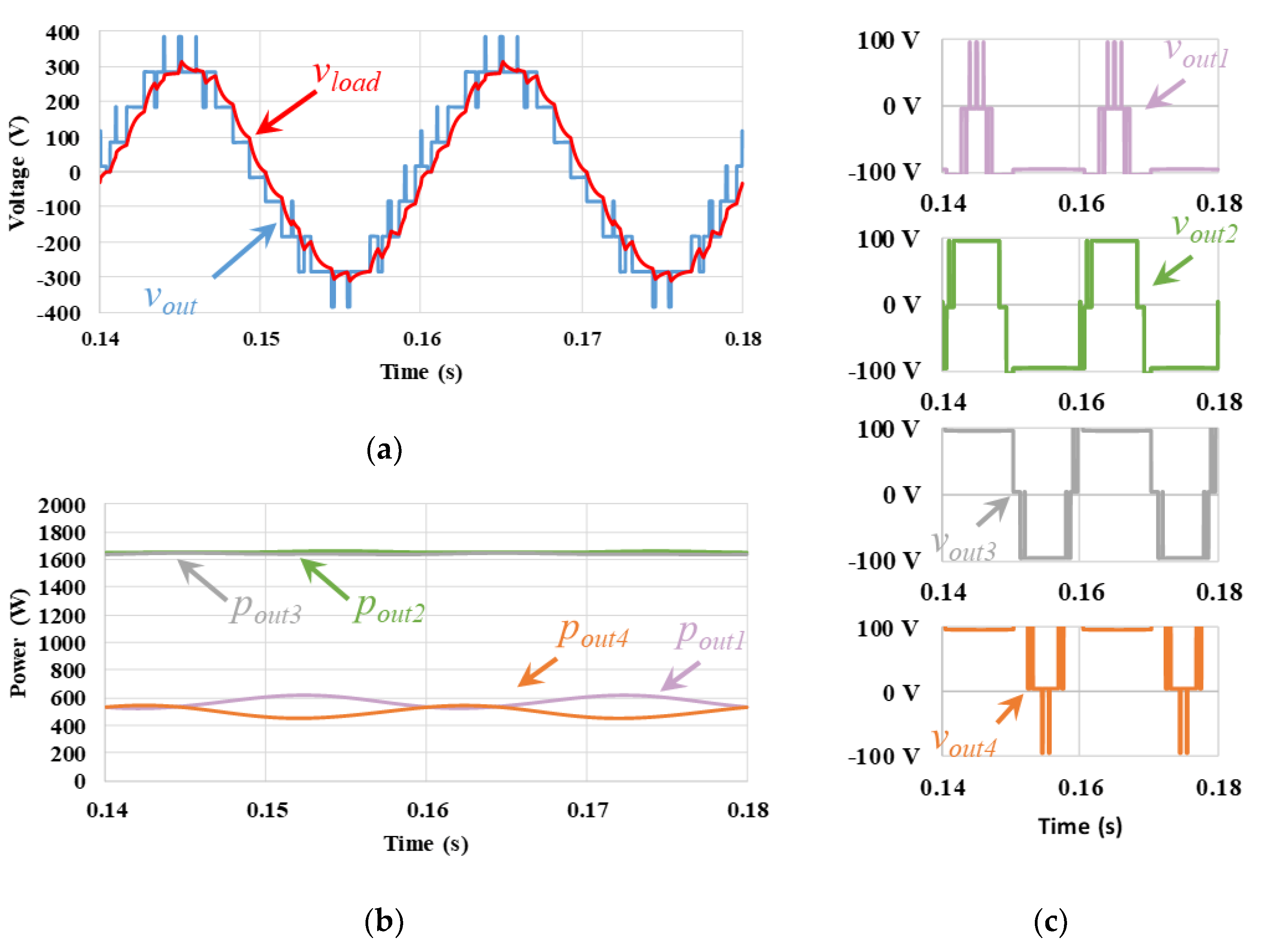

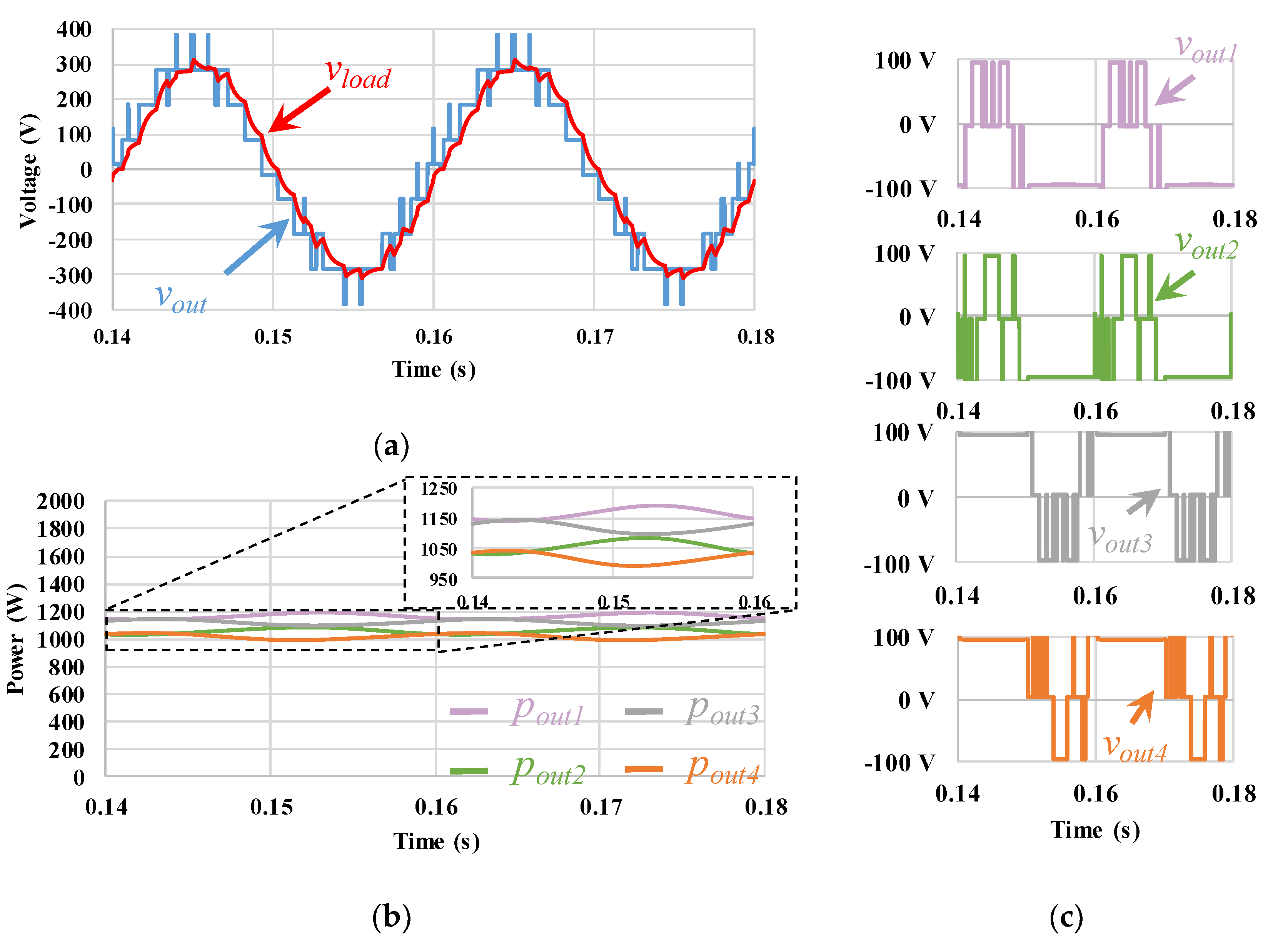

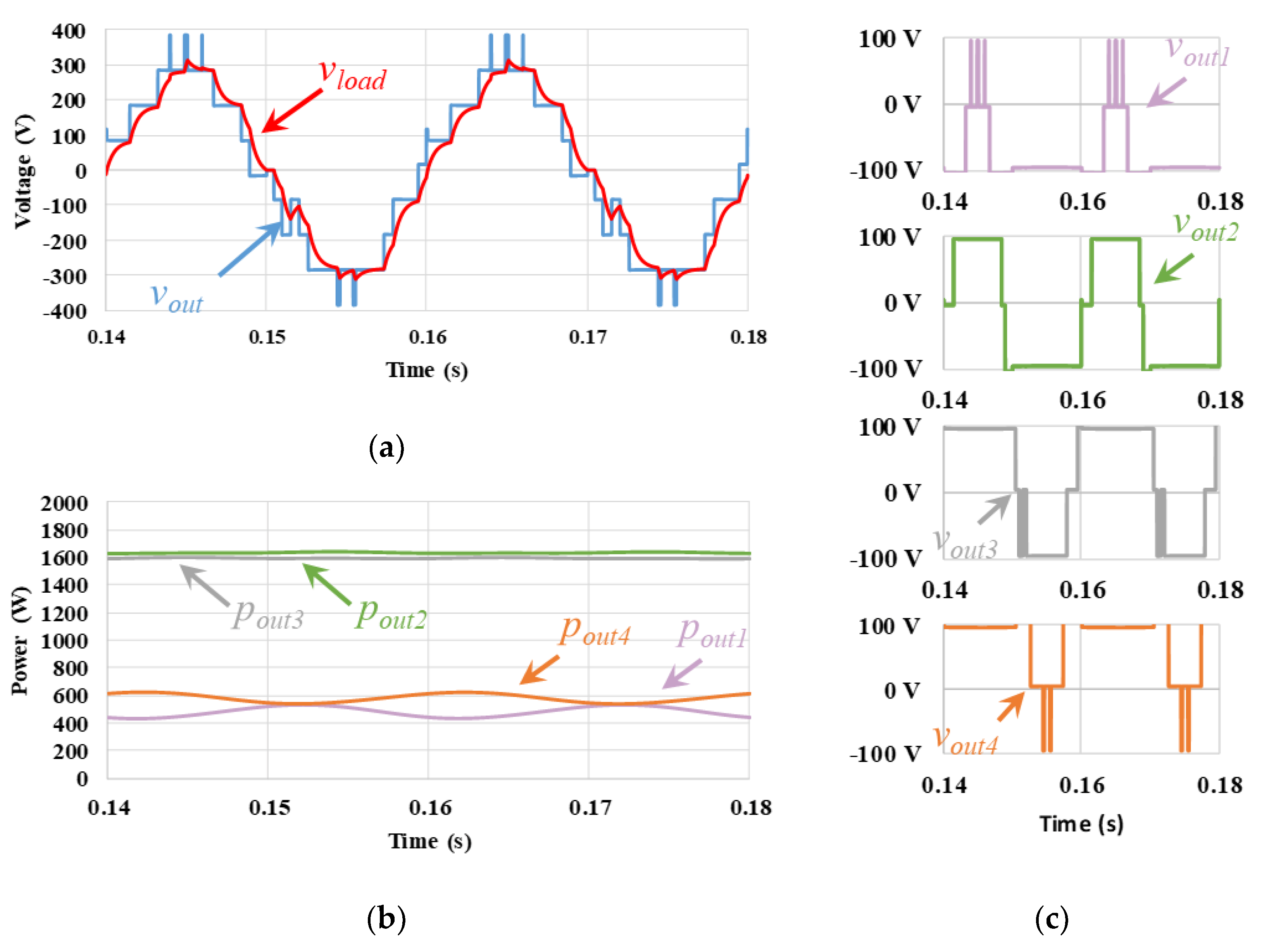

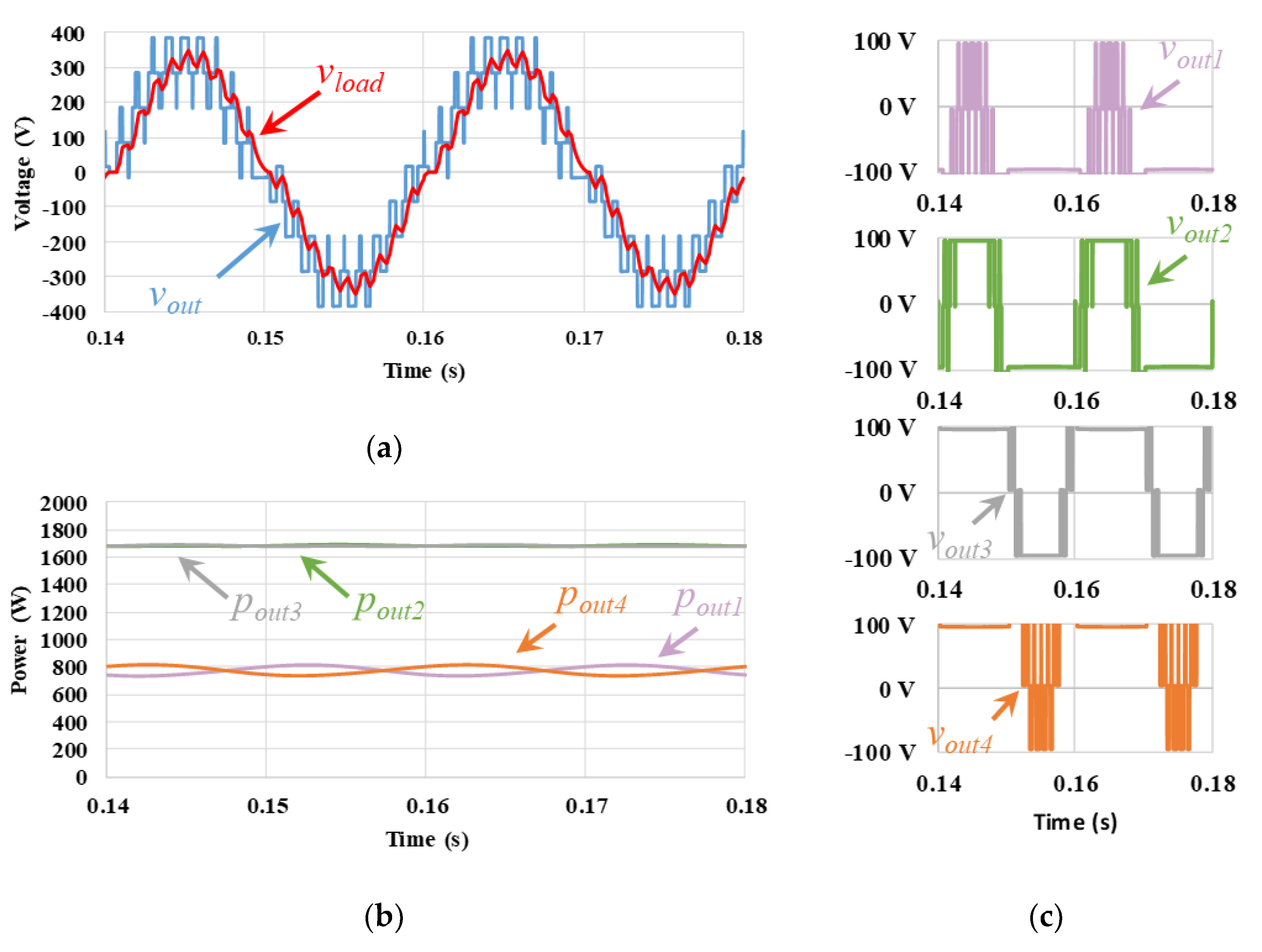

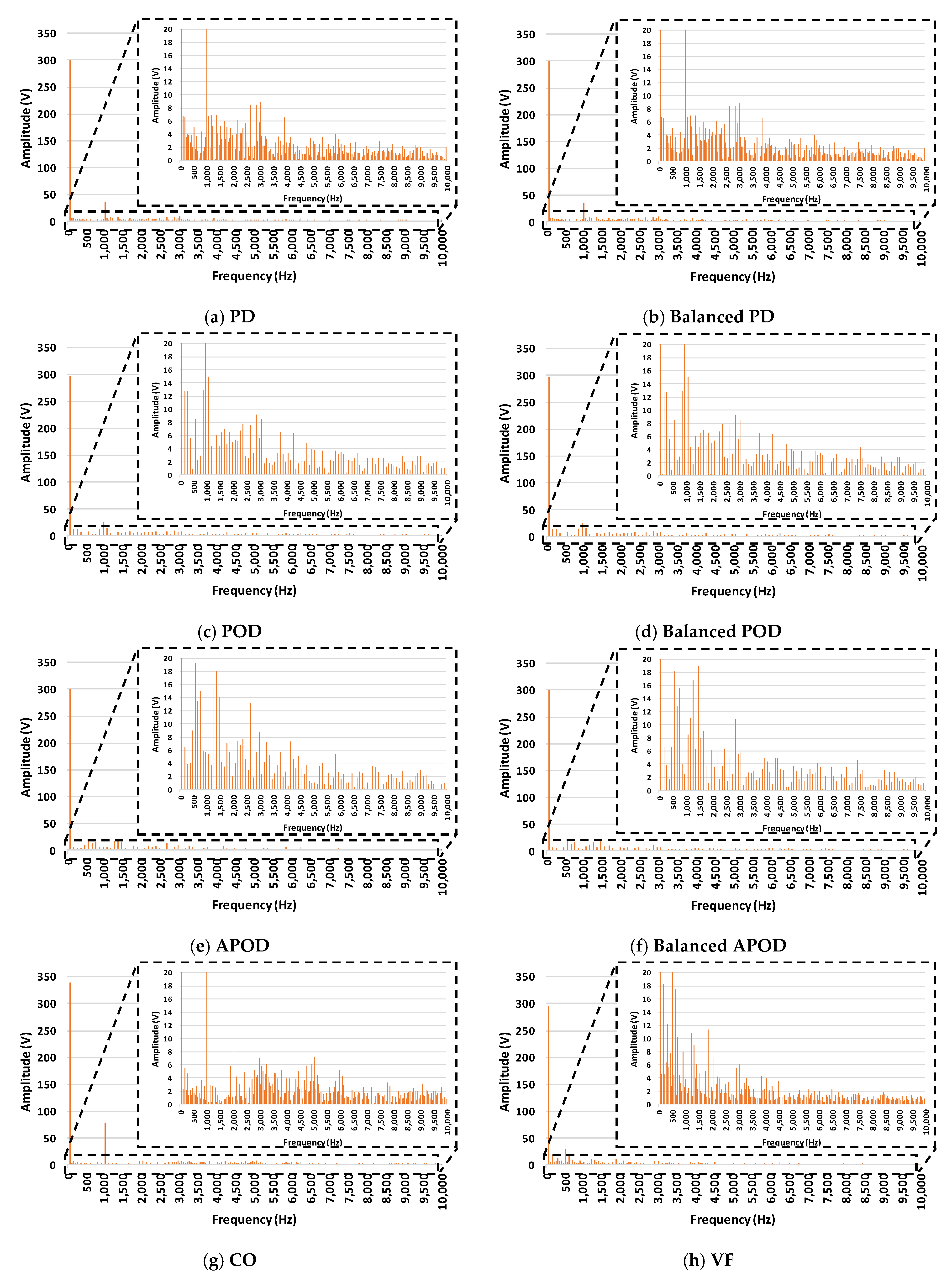

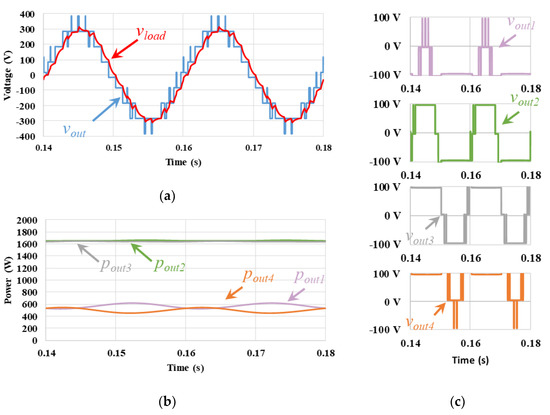

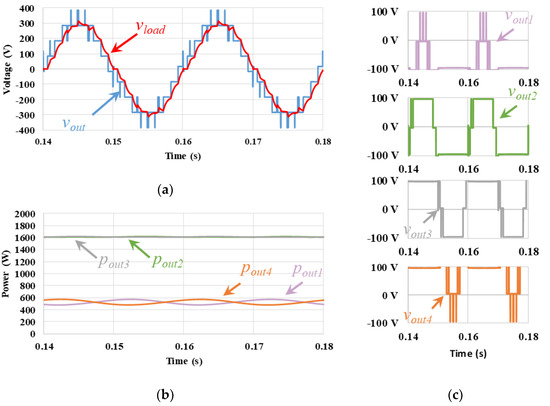

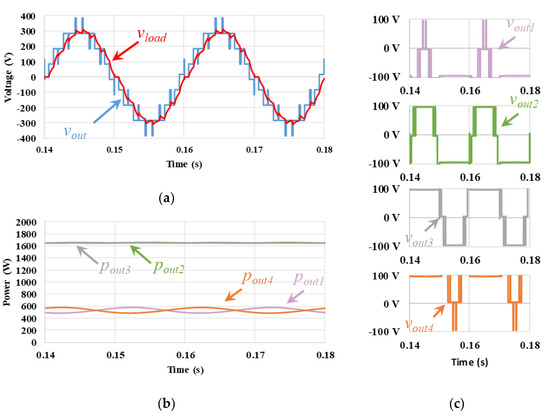

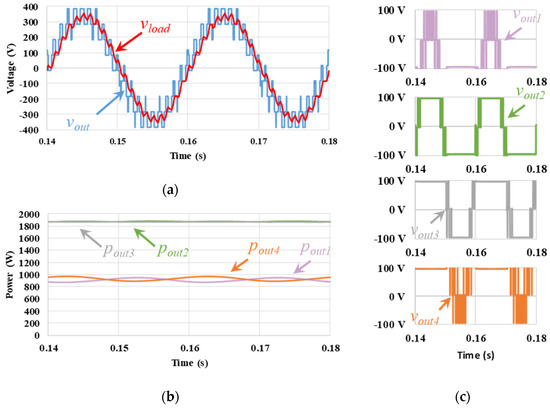

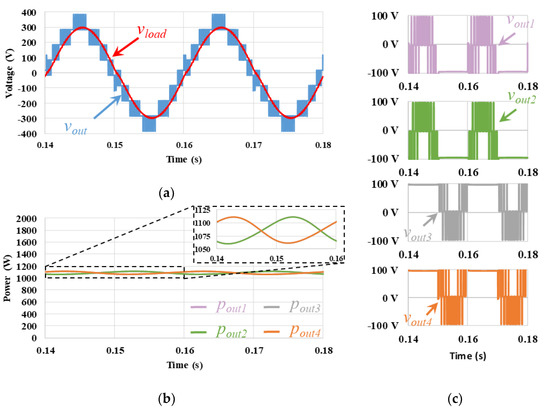

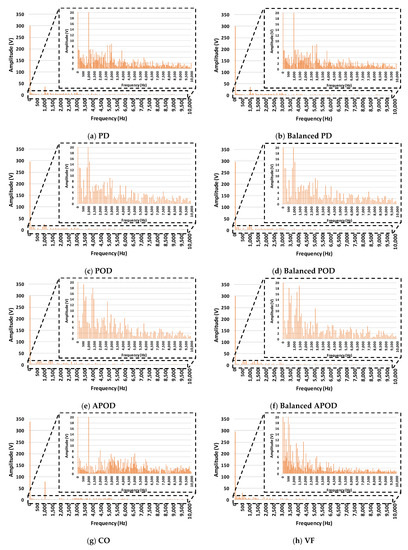

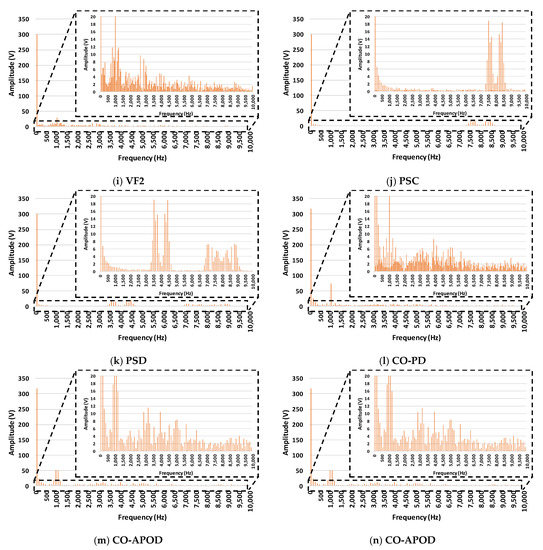

5.1. Basic Level-Shift PD, POD, and APOD PWM Techniques

The first PWM technique implemented for analysis was the PD, and the results are shown in Figure 13. In Figure 13a are illustrated the MLC output voltage waveform, vout, and the voltage waveform at load, vload. In analyzing the waveforms, it is possible to see that vout does not present symmetry in relation to the zero-reference axis. That is, the positive semi-cycle presents a waveform not symmetrical in relation to the negative semi-cycle. In Figure 13b are represented the power variations of each submodule over two cycles. It should be mentioned that the submodules have an oscillating power of 50 Hz, with a 180° delay with the complementary submodule. That is, pout3 is 180° lagged in relation to pout2, and pout4 is 180° lagged in relation to pout1. It should also be mentioned that, considering the pairs pout2 with pout3 and pout1 with pout4, they present slightly different average power values due to the asymmetry of the carrier waveforms. It is also possible to see the existence of submodules contributing with a power 3.3 times higher than other submodules. This fact is verified in Figure 13c, where each submodule presents a different pattern in the output voltage (vout1, vout2, vout3, and vout4). It should be noted that these differences in patterns cause each submodule to present different and unique powers.

Figure 13.

Simulation results of the PD PWM technique: (a) output voltage of the cascaded MLC, vout, and load voltage, vload; (b) output power on each submodule (pout1, pout2, pout3, pout4); (c) output voltage on each submodule (vout1, vout2, vout3, vout4).

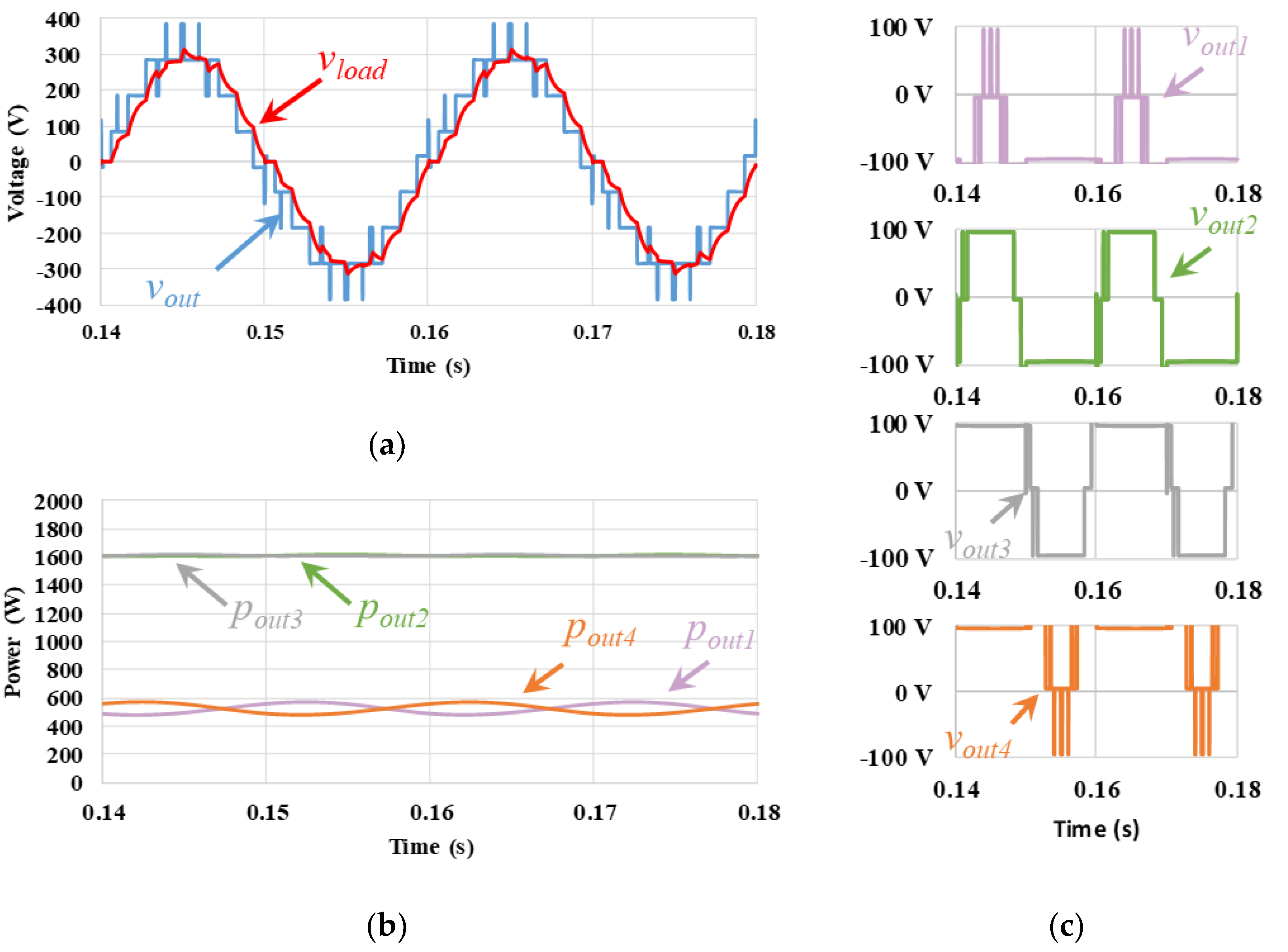

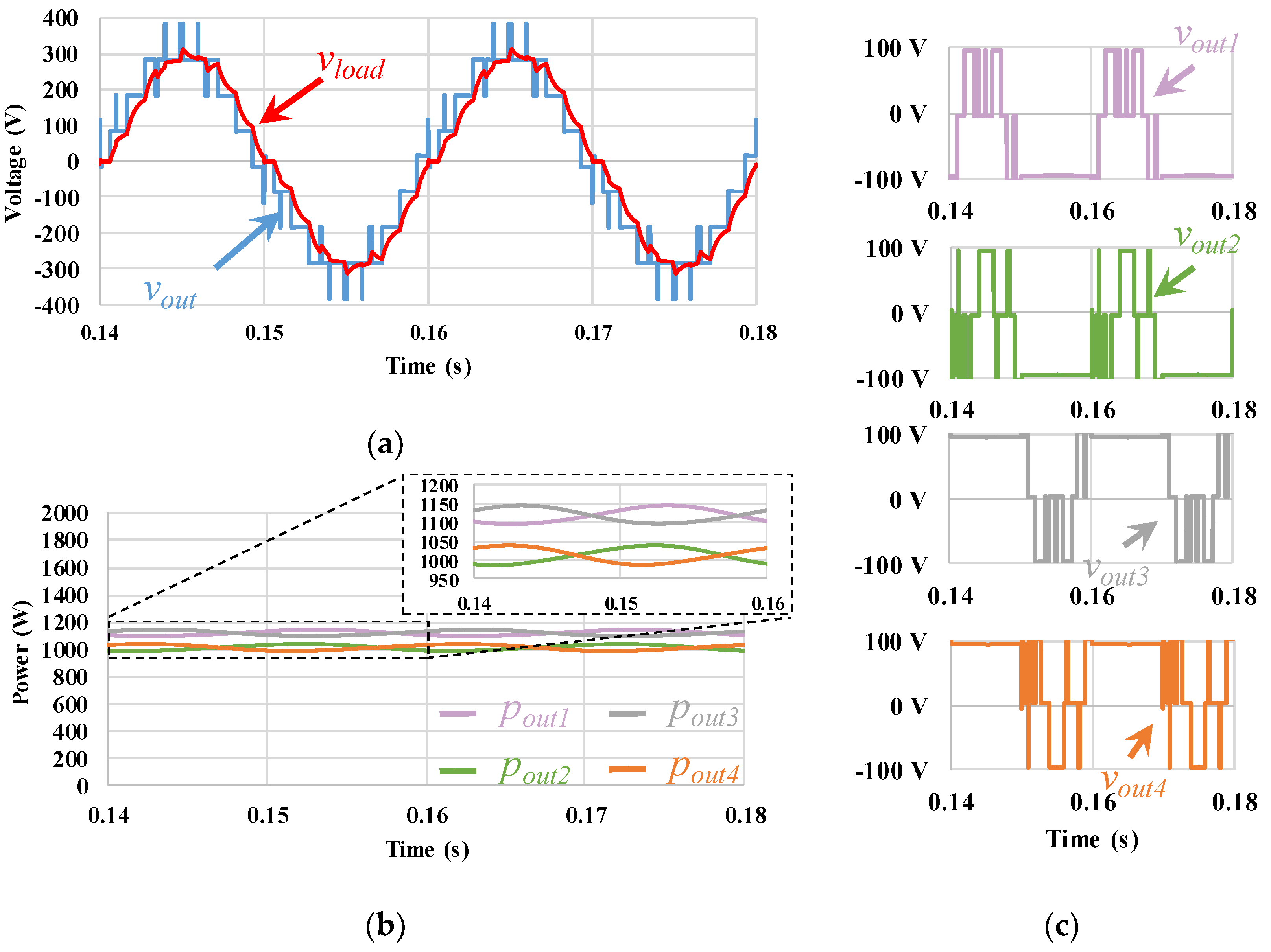

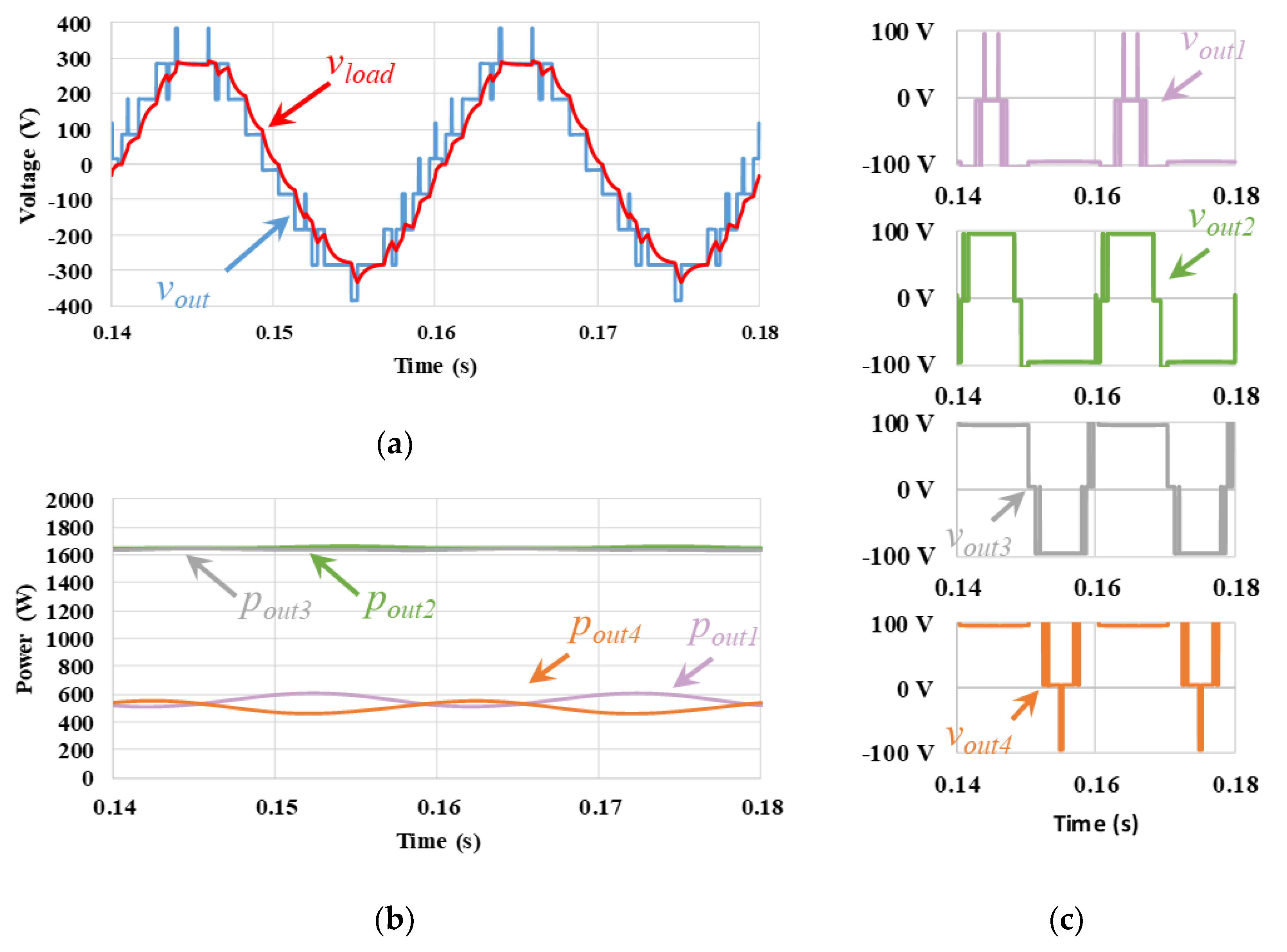

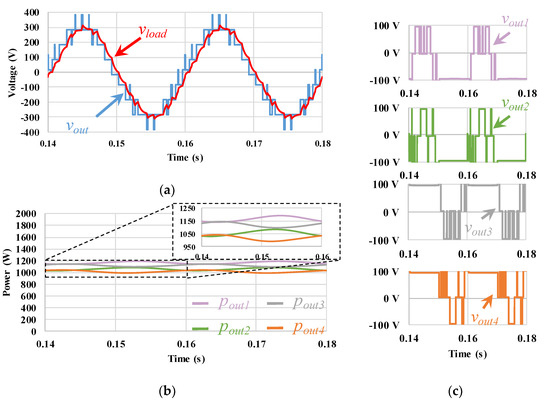

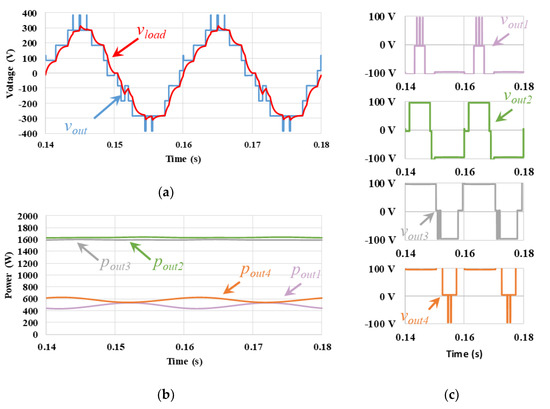

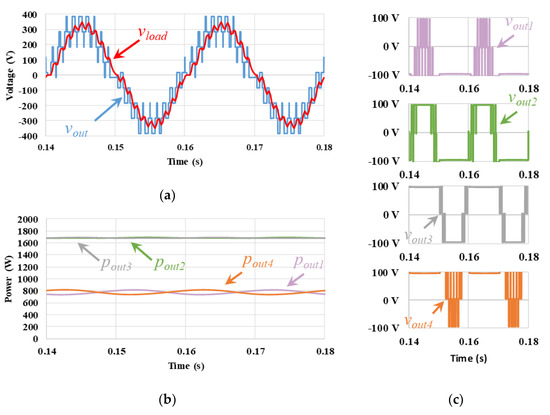

The next technique implemented was the POD, and the results are presented in the Figure 14. By analyzing the vout and vload waveforms in Figure 14a, it is possible to see that there is a symmetry with respect to the zero-reference axis. This fact is due to the symmetry of the carrier waveforms, as mentioned before. Figure 14b shows the power variation of each submodule over two cycles. It should be mentioned that the submodules have an oscillating power of 50 Hz, with a 180° delay with the complementary submodule. That is, pout3 is 180° lagged in relation to pout2, and pout4 is 180° lagged in relation to pout1. It should also be mentioned that the pairs pout2 with pout3 and pout1 with pout4 present similar average power values due to the asymmetry of the carrier waveforms. It is also possible to see that the power distribution among the different submodules is not uniform, with some submodules contributing 3.1 times more power. This fact is seen in Figure 14c with submodules having different output voltage patterns (vout1, vout2, vout3, and vout4). However, it should be mentioned that the symmetry of the carrier waves causes a parity in the system, and there is a complementary submodule with a similar voltage and power pattern. Despite this parity, the POD technique still has low modularity.

Figure 14.

Simulation results of the POD PWM technique: (a) output voltage of the cascaded MLC, vout, and load voltage, vload; (b) output power on each submodule (pout1, pout2, pout3, pout4); (c) output voltage on each submodule (vout1, vout2, vout3, vout4).

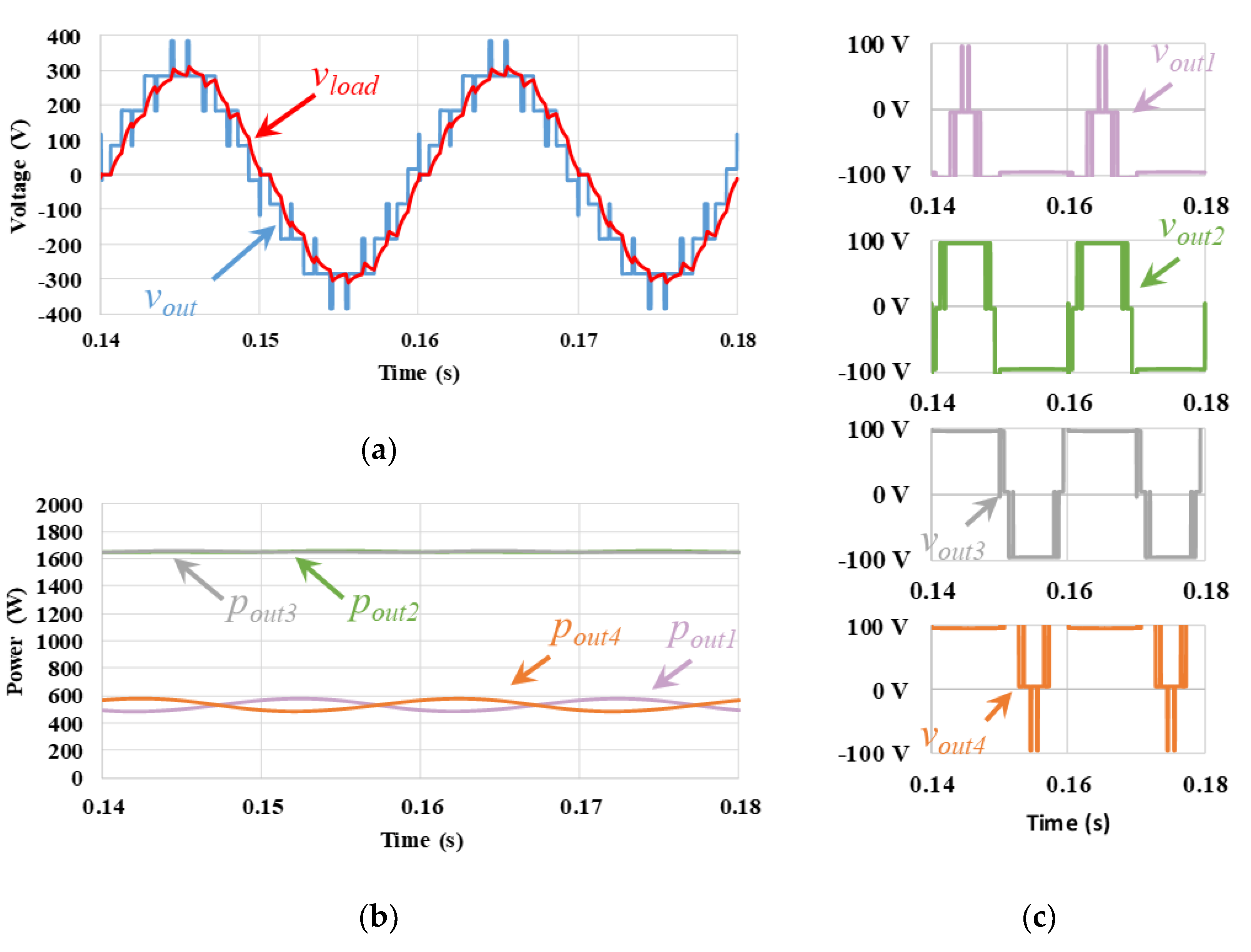

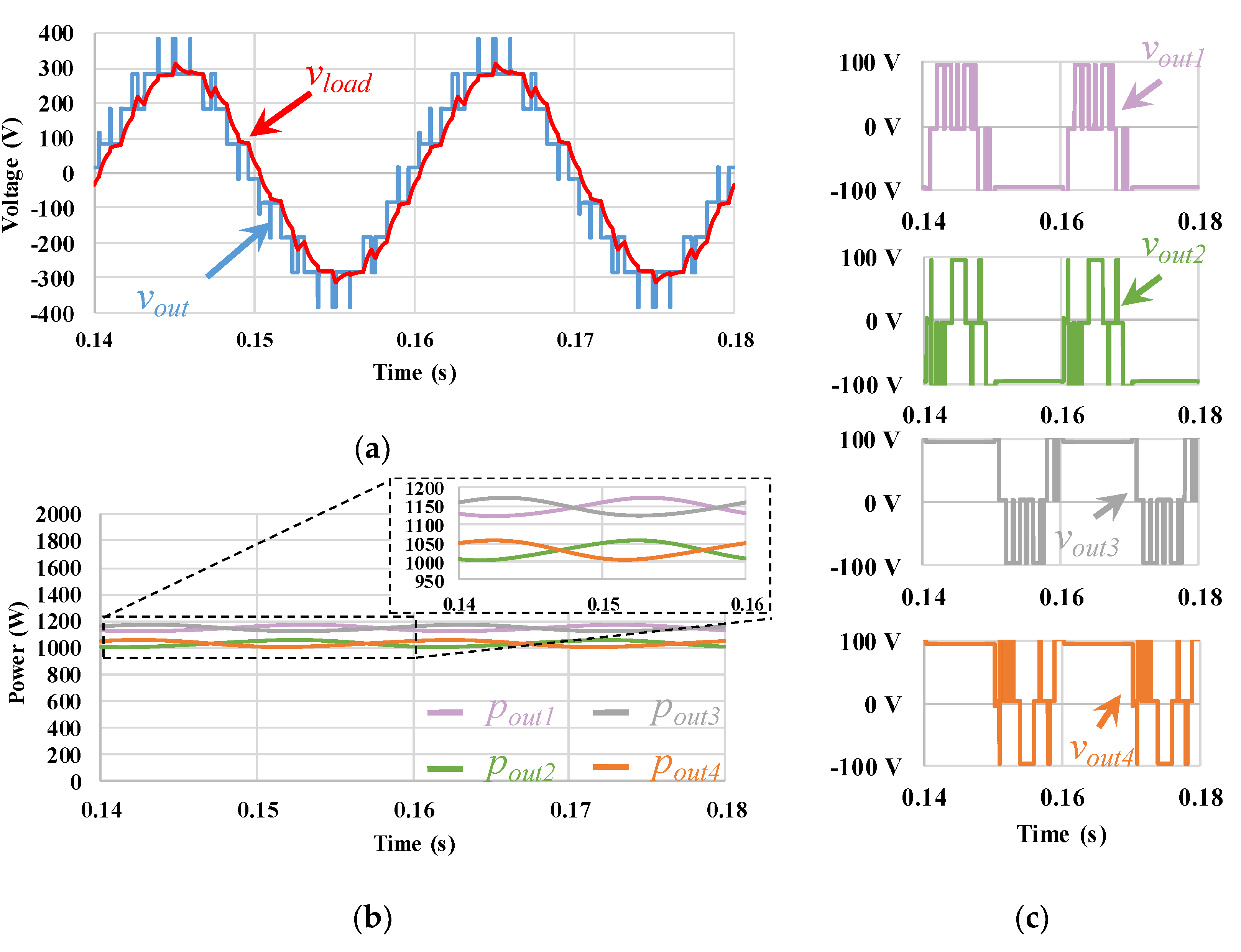

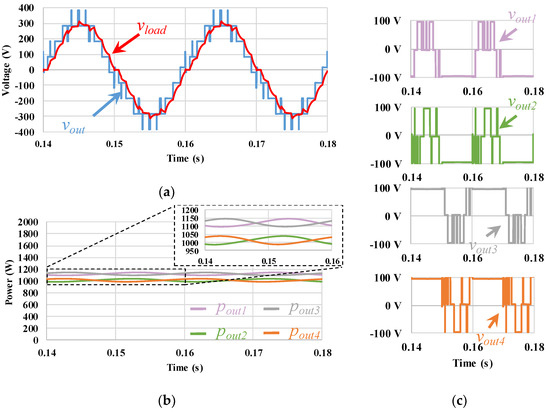

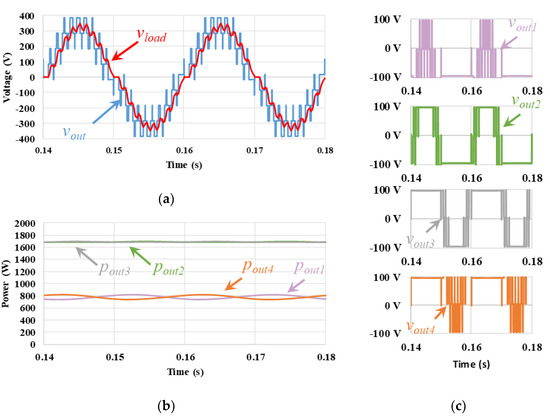

Regarding the APOD technique, the simulation results are shown in Figure 15. In Figure 15a are illustrated the vout and vload waveforms. Analyzing the waveforms, it is possible to see that vout presents symmetry in relation to the zero-reference axis. In Figure 15b is represented the variation of power in each submodule over two cycles. It should be mentioned that the submodules have an oscillating power of 50 Hz, with a 180° delay with the complementary submodule. That is, pout3 is 180° lagged in relation to pout2, and pout4 is 180° lagged in relation to pout1. It should also be mentioned that the pairs pout2 with pout3 and pout1 with pout4 present similar average power values due to the symmetry of the carrier waveforms. It is also possible to see that the power distribution for each submodule is not uniform, with some submodules contributing 3.1 times more power. Once again, this fact is verified with the analysis of Figure 15c, where each submodule presents a different pattern in the output voltage (vout1, vout2, vout3, and vout4).

Figure 15.

Simulation results of the APOD PWM technique: (a) output voltage of the cascaded MLC, vout, and load voltage, vload; (b) output power on each submodule (pout1, pout2, pout3, pout4); (c) output voltage on each submodule (vout1, vout2, vout3, vout4).

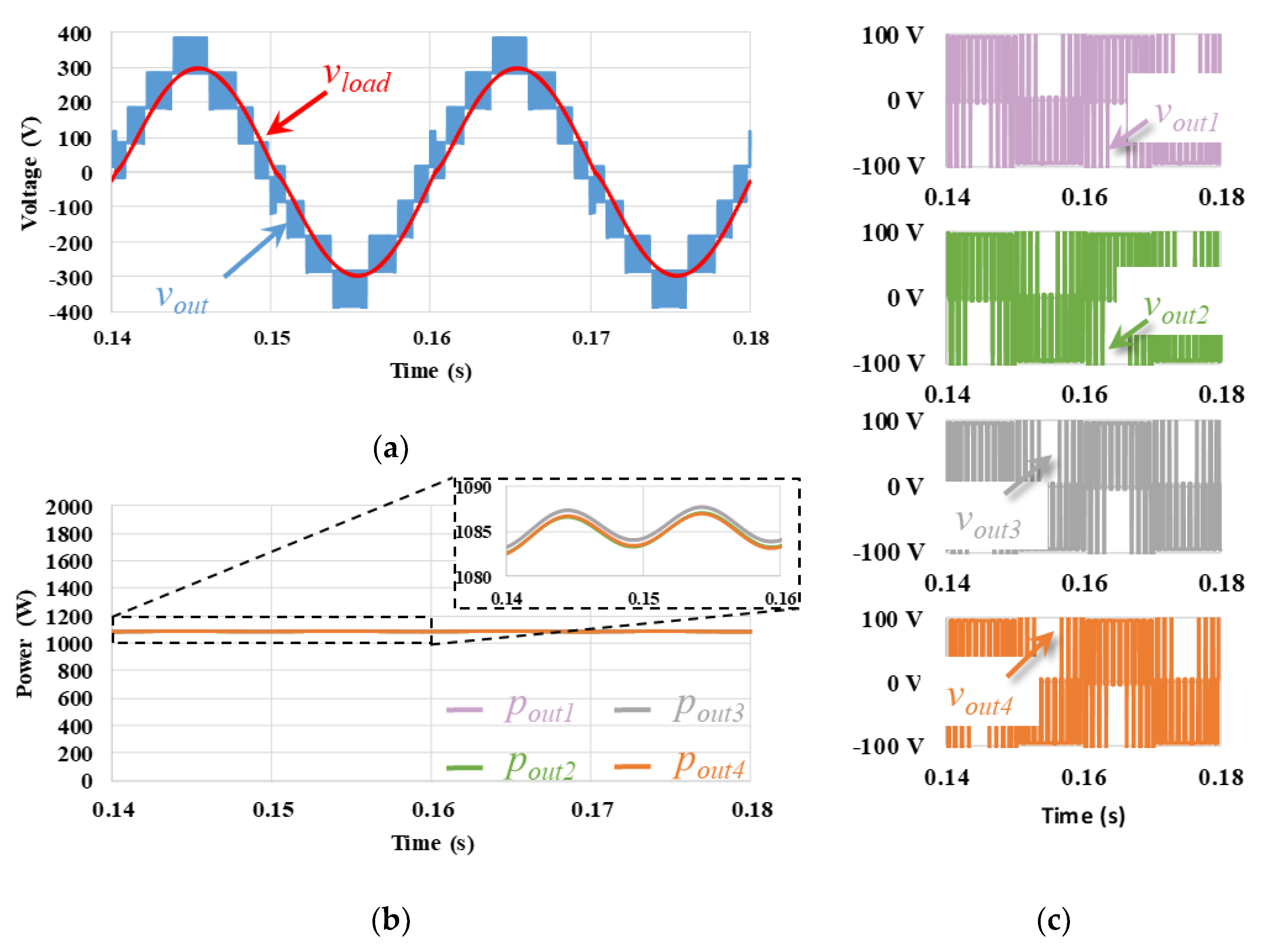

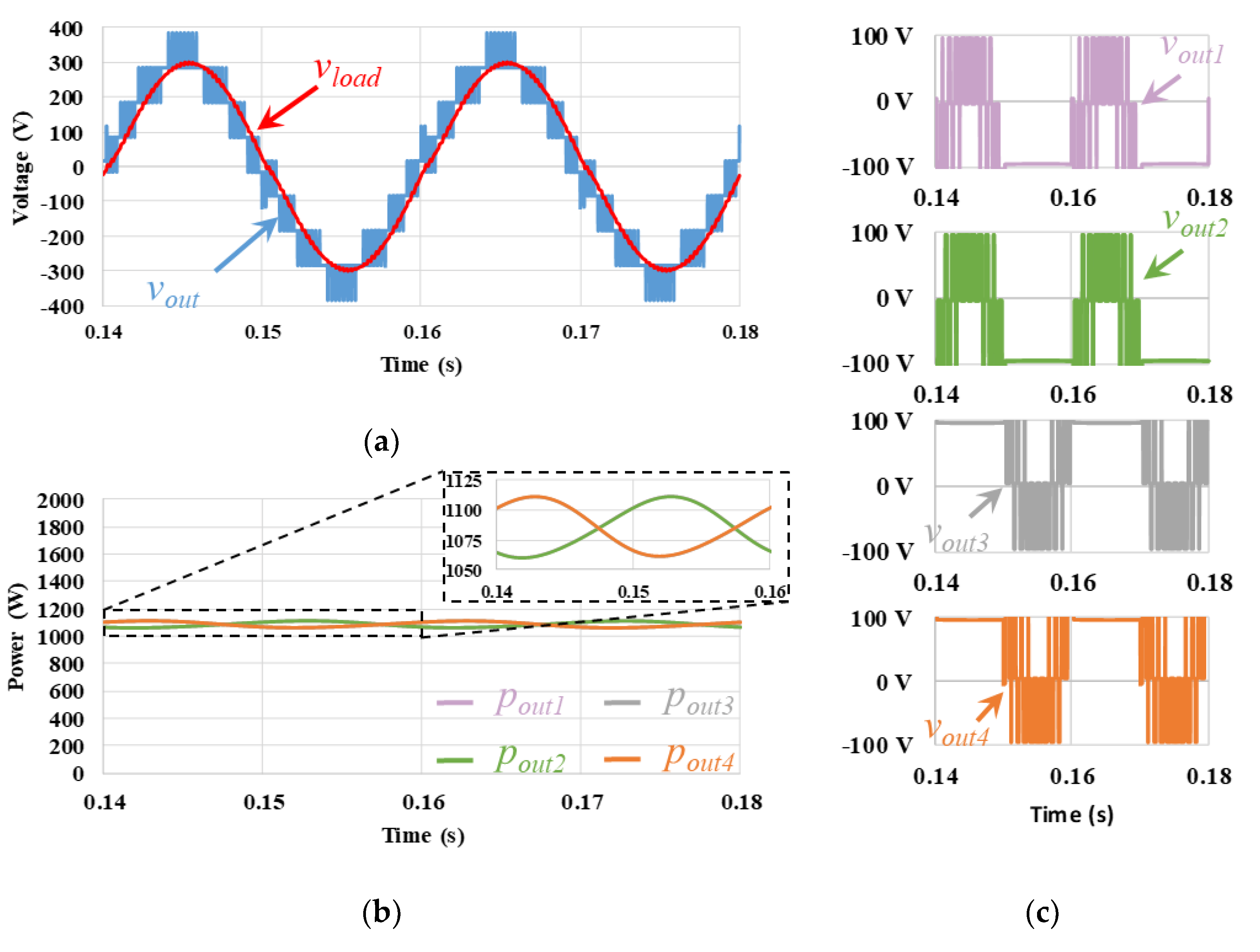

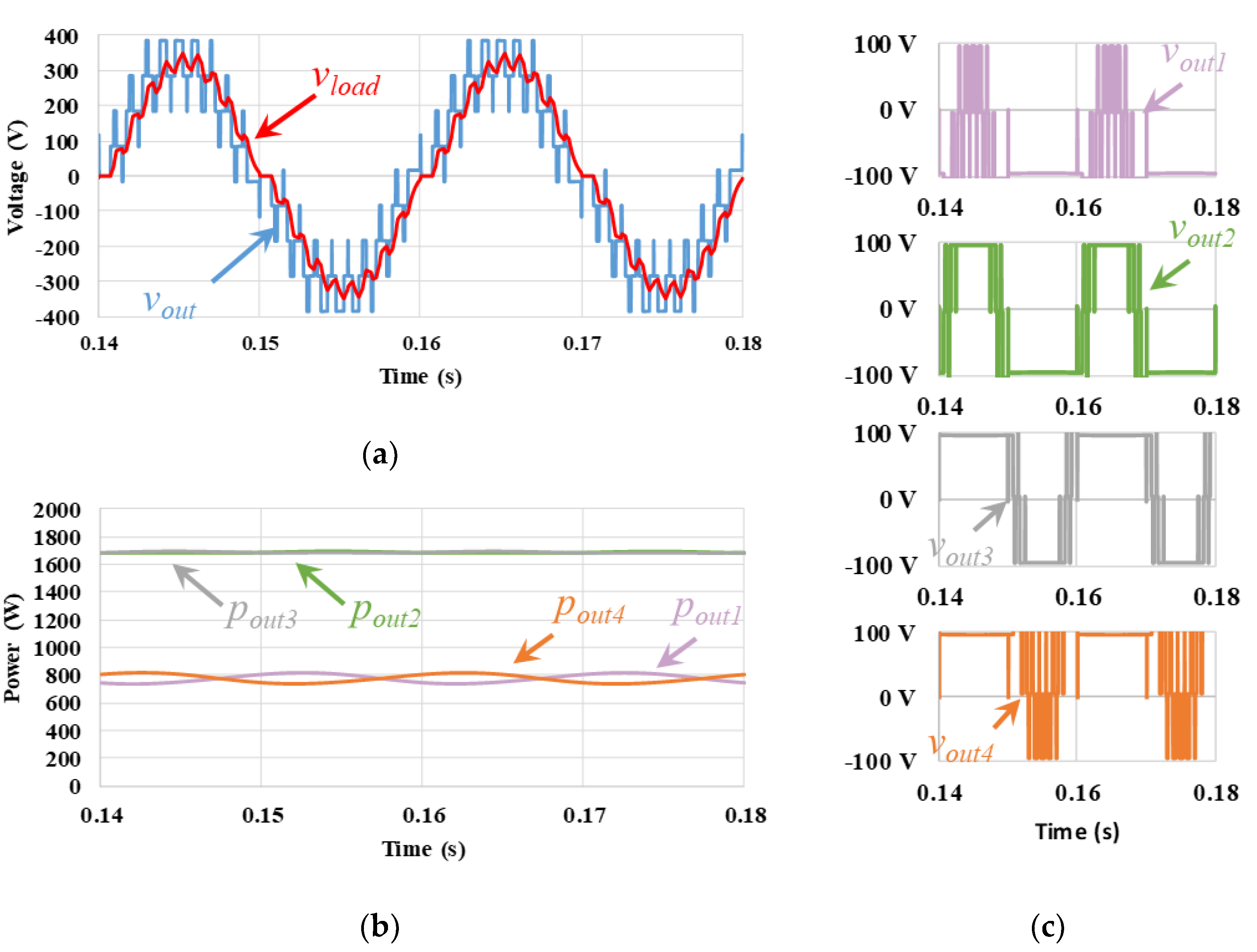

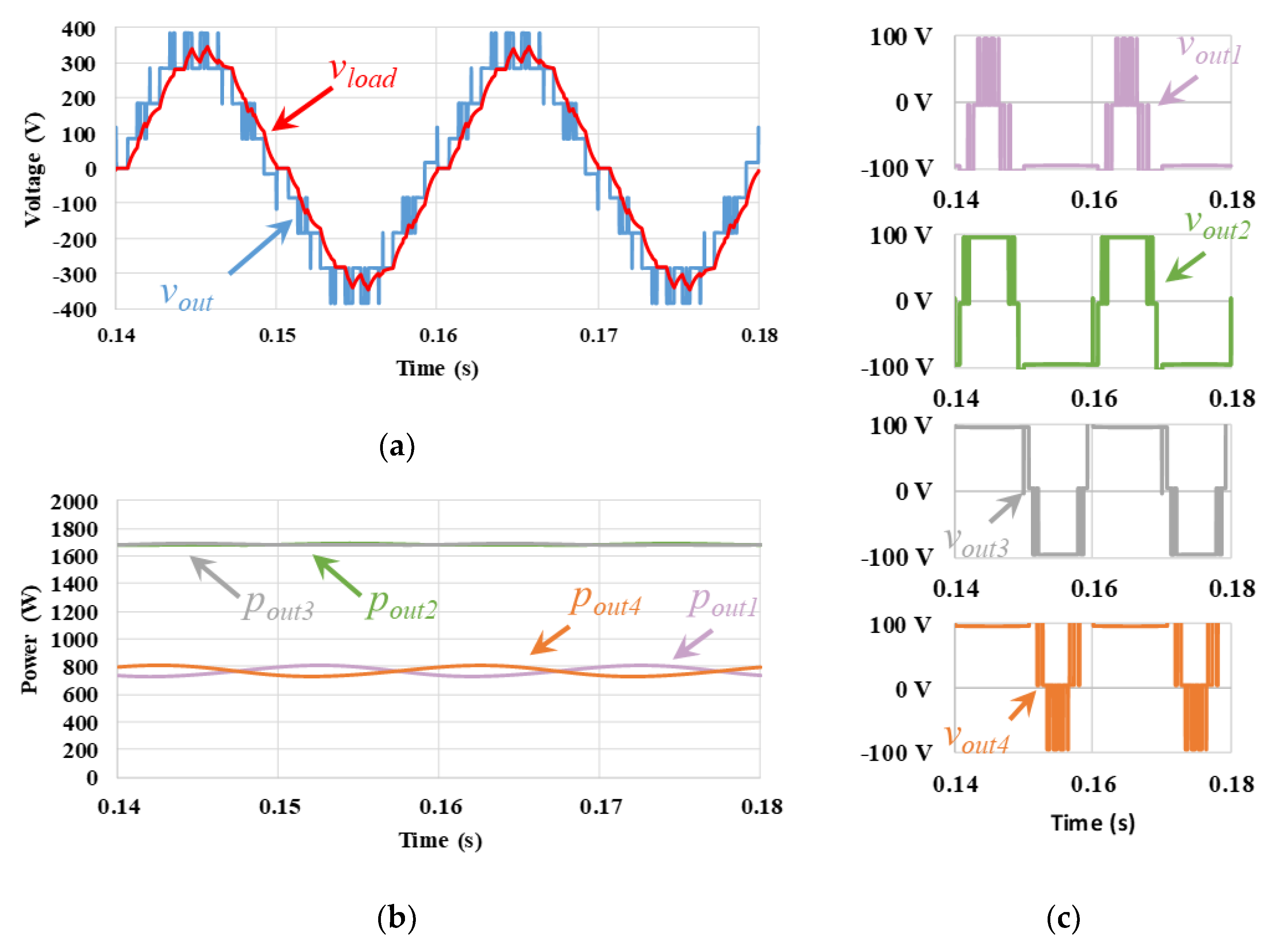

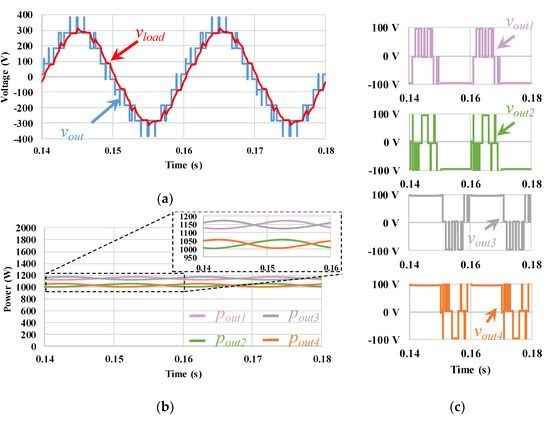

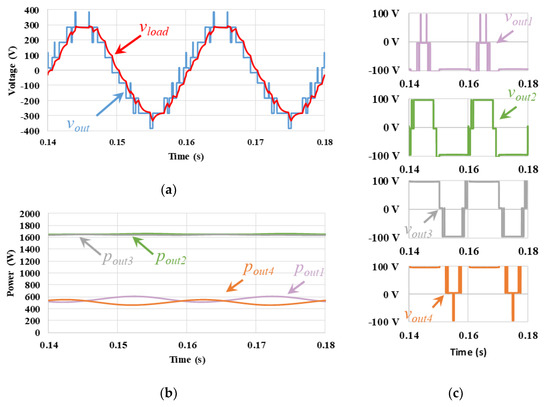

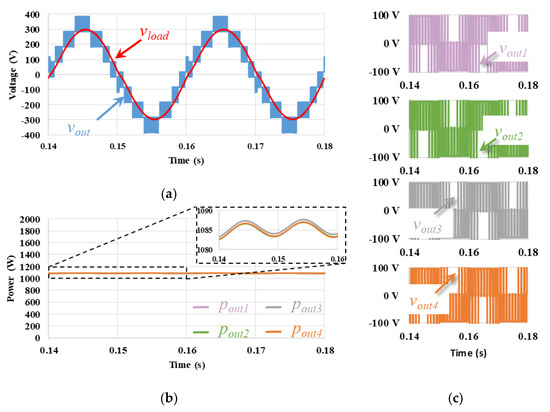

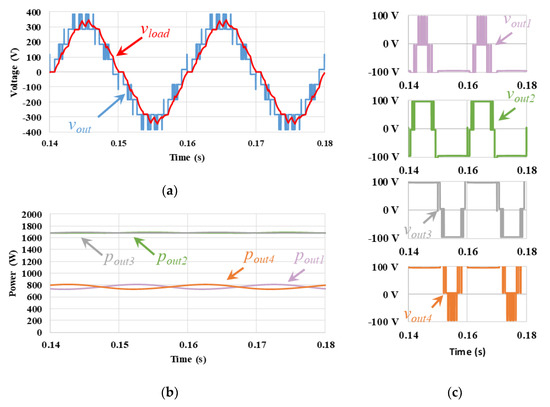

5.2. Power Balancing Level-Shift PD, POD, and APOD PWM Techniques

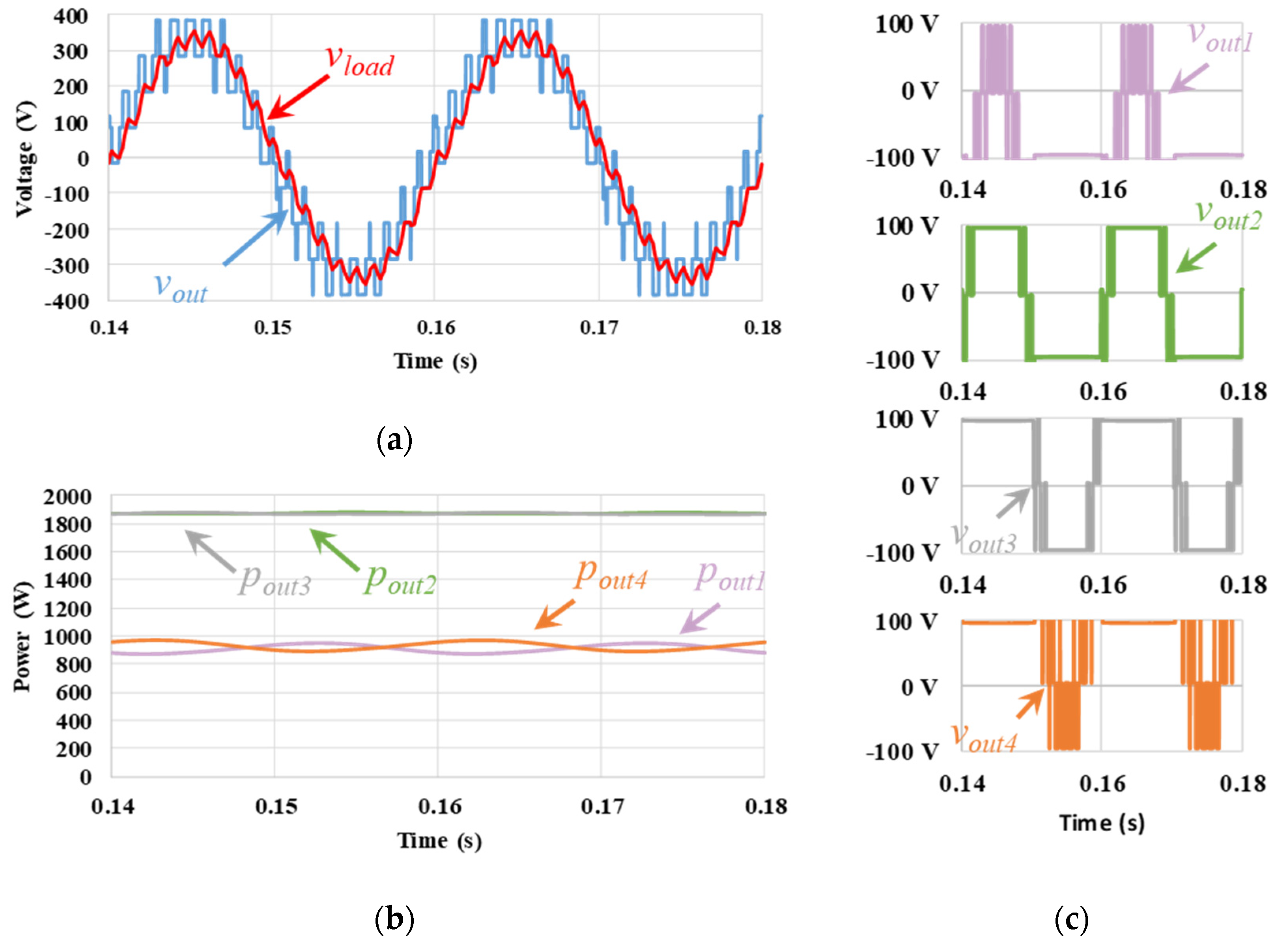

As far as the balancing techniques are concerned, the simulation results can be verified in the following figures: balanced PD in Figure 16, balanced POD in Figure 17, and balanced APOD in Figure 18. In analyzing the vout and vload waveforms, it is possible to verify that they present a greater symmetry resulting from the alternation of the carrier waves. In general, it was possible to minimize the power imbalances of each submodule. However, it should be mentioned that with the balanced PD technique (Figure 16b), each submodule presents a different average power value. In turn, with the balanced POD (Figure 17b) and balanced APOD (Figure 18b) techniques, the average power value is equal for each pair of modules. The alternation of carrier waves causes a higher number of intercepts to exist with the modulating wave for each submodule. As a result, the output voltages show a different pattern when compared to conventional unbalanced techniques: output voltages for balanced PD can be seen in Figure 16c; output voltages for balanced POD can be seen in Figure 17c; and output voltages for balanced APOD can be seen in Figure 18c.

Figure 16.