Second-Order Ripple Current Suppression Based on Virtual Impedance in the Application of Dynamic Voltage Restorer

Abstract

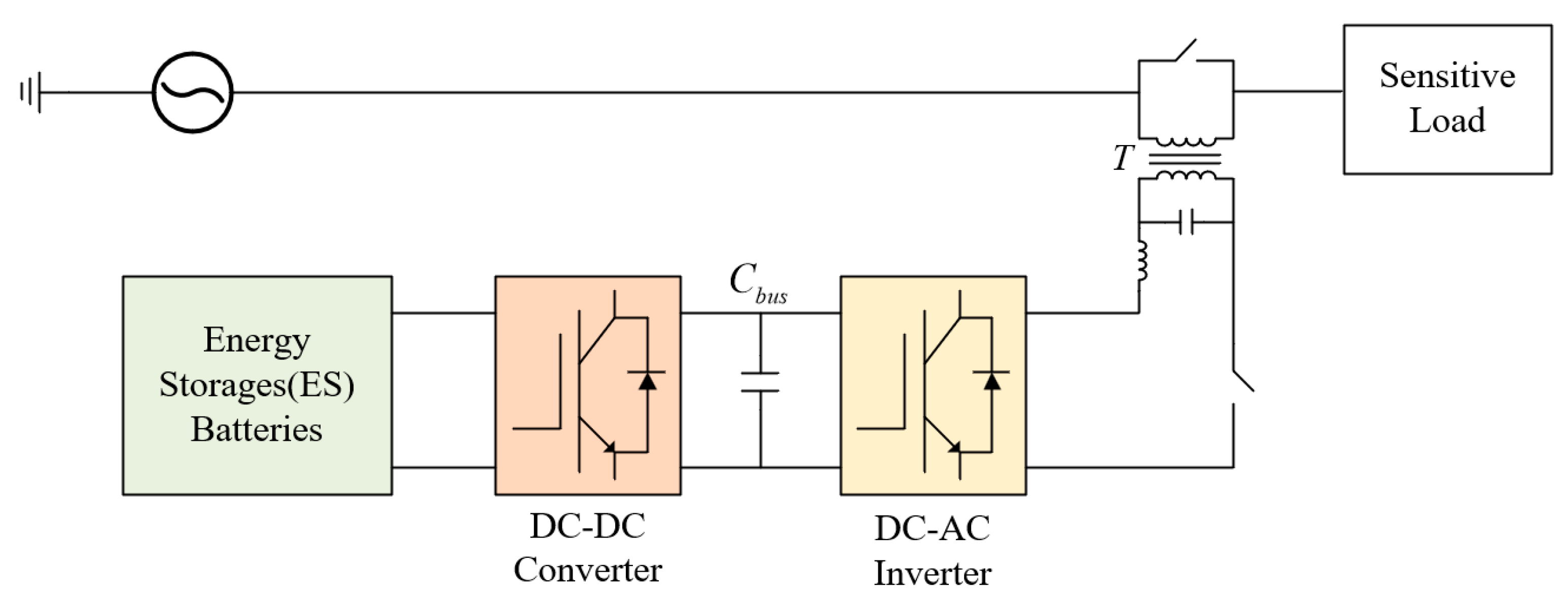

1. Introduction

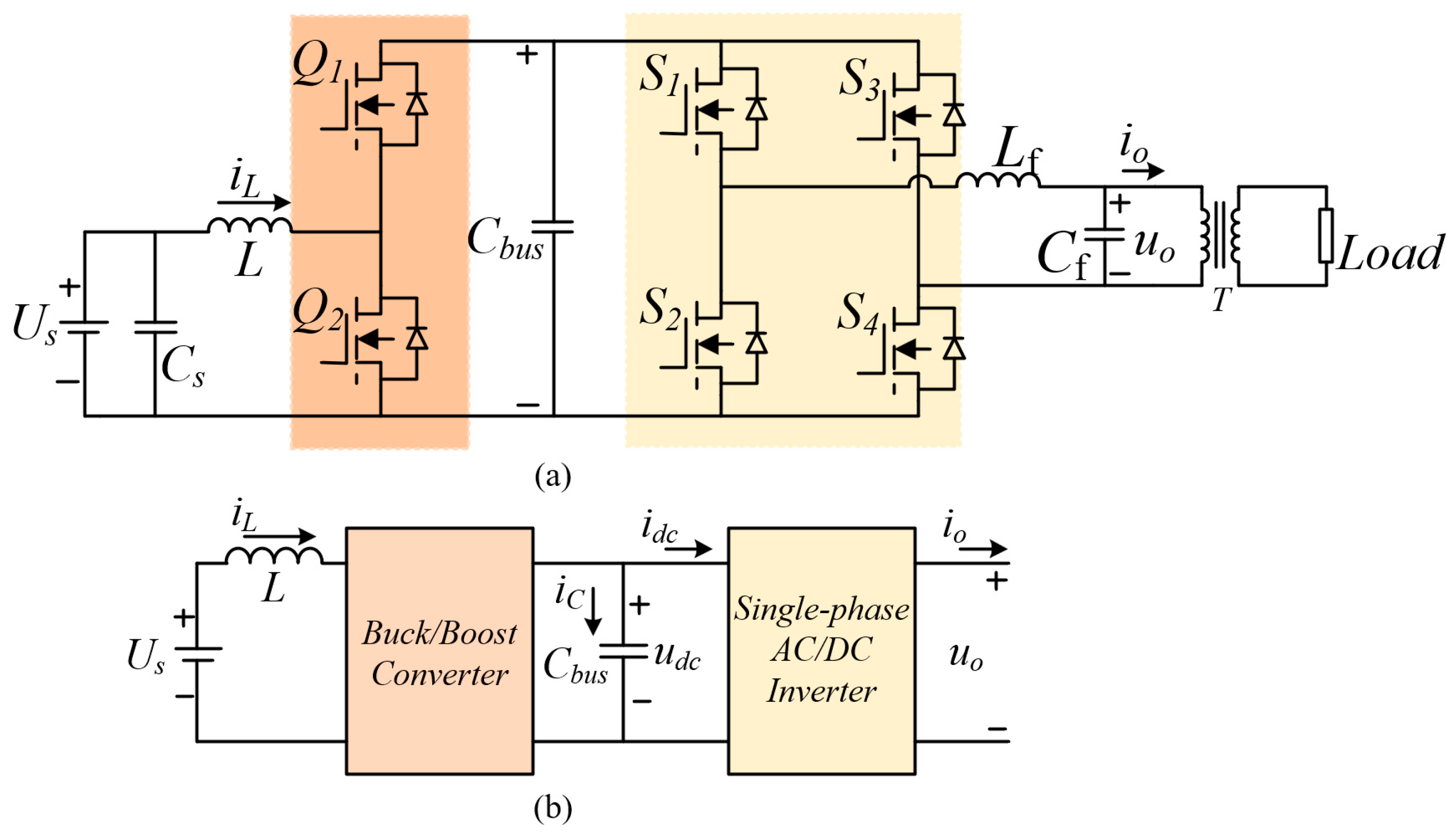

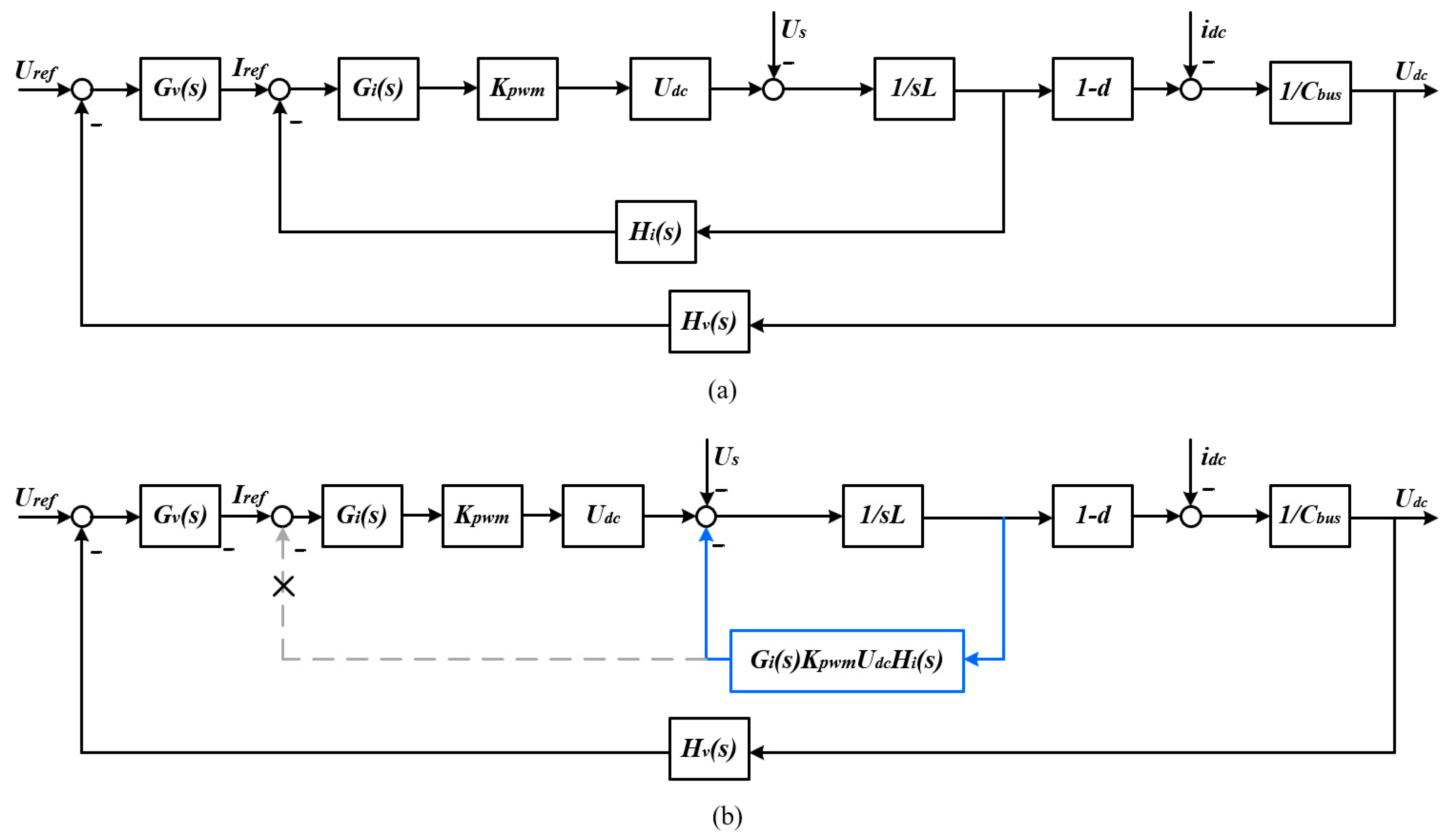

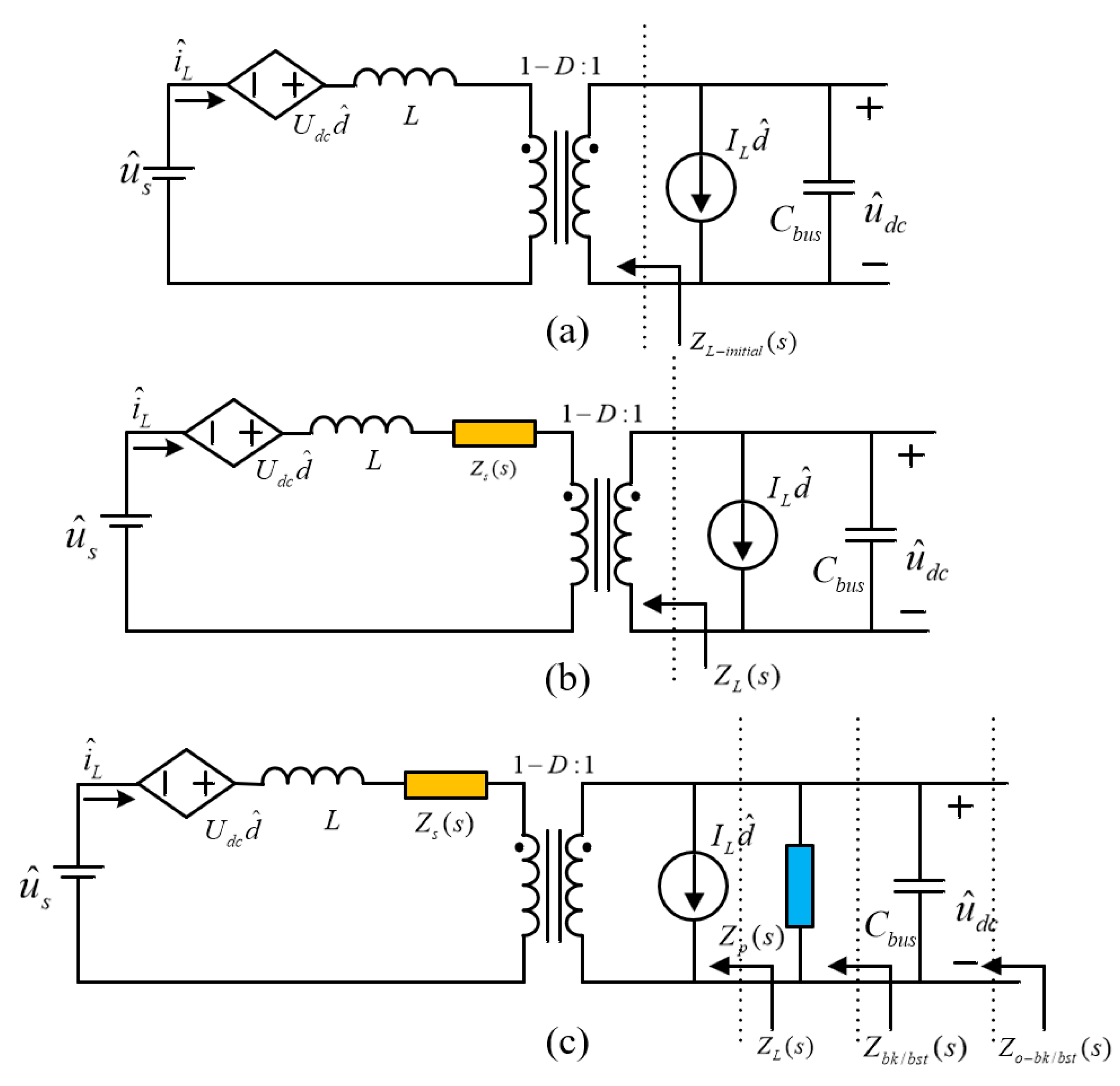

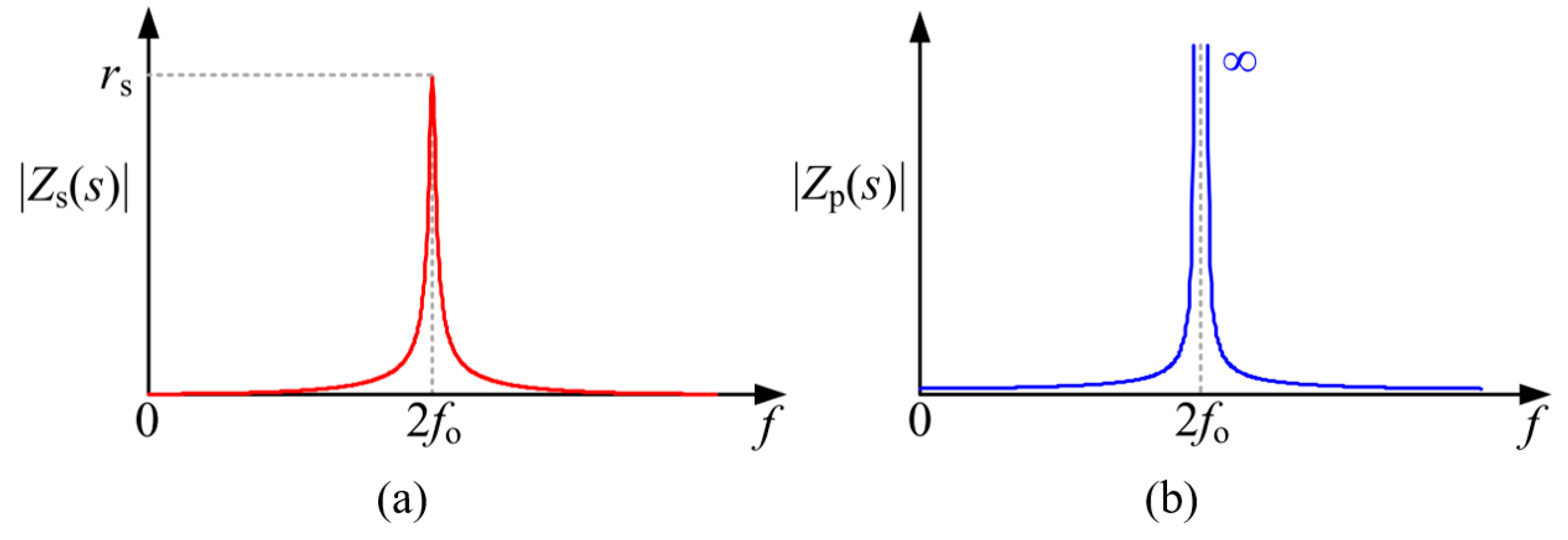

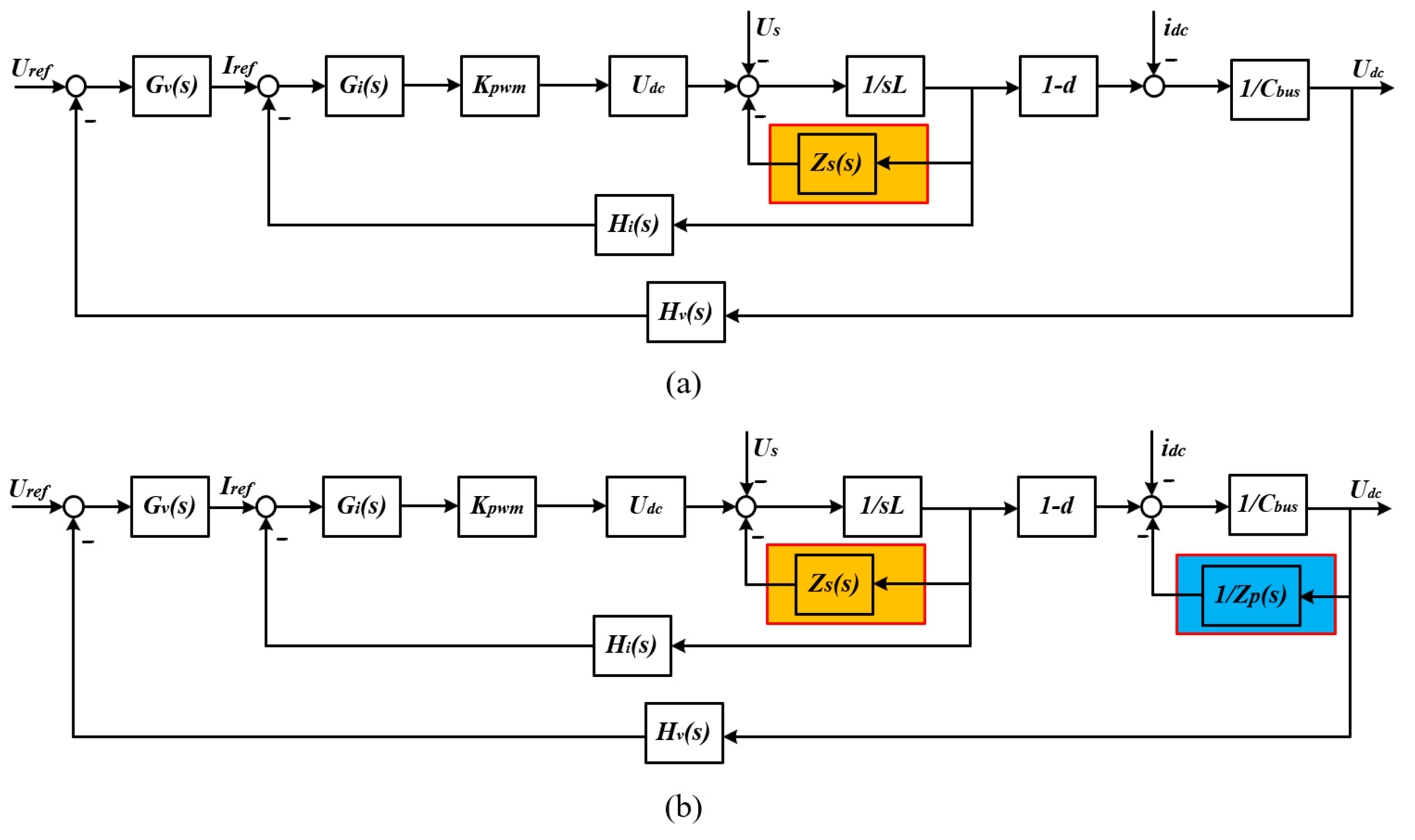

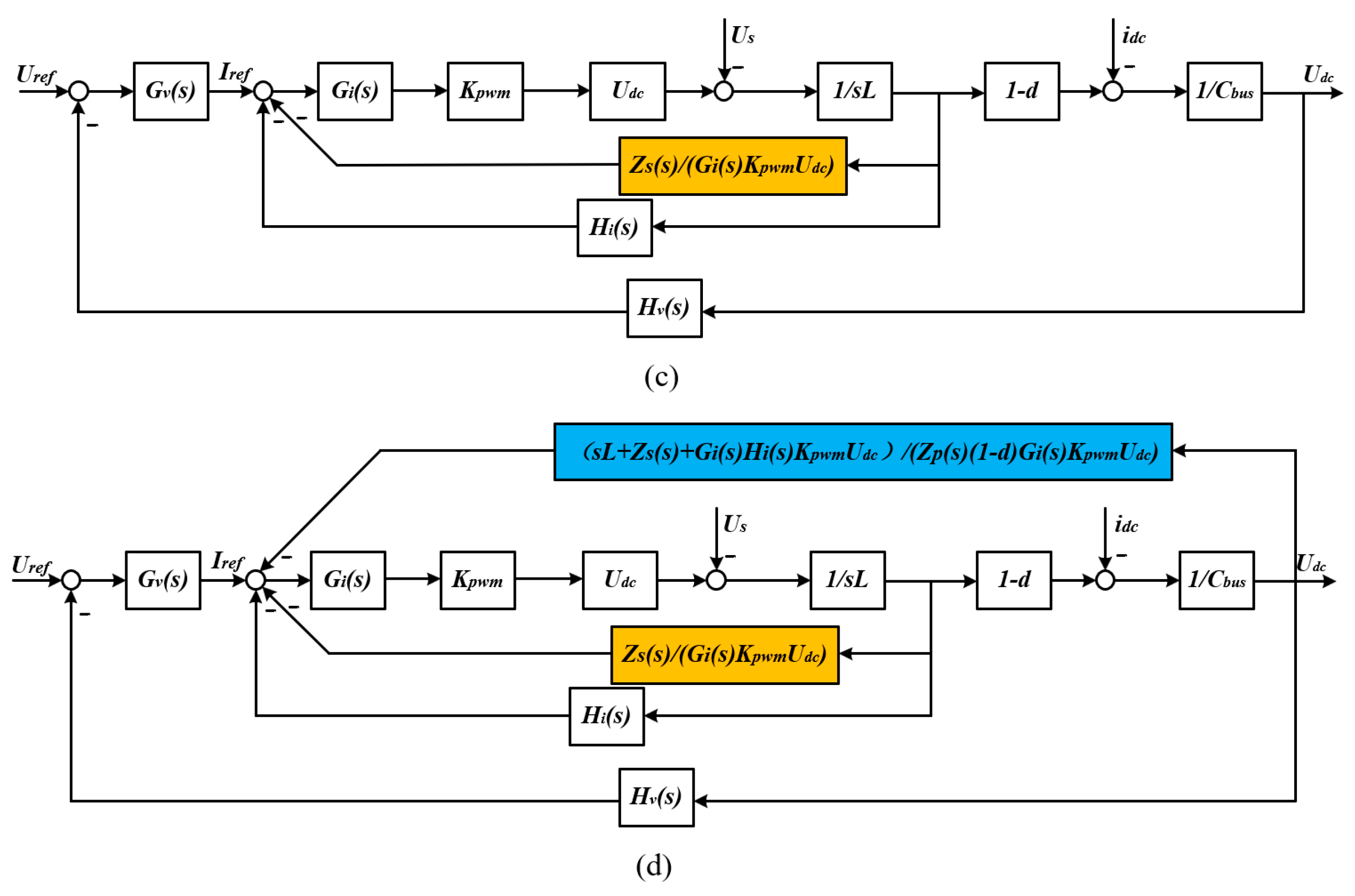

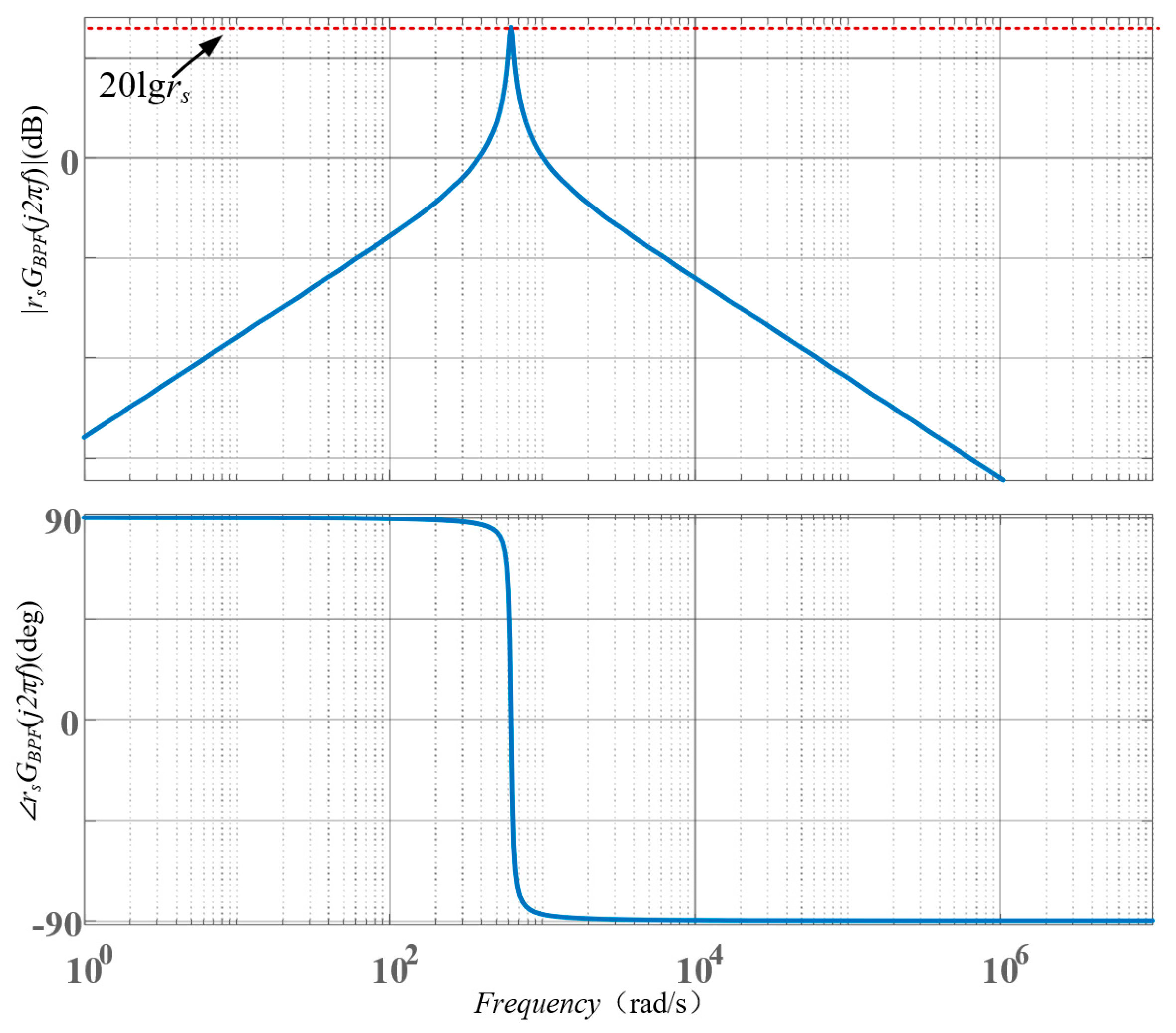

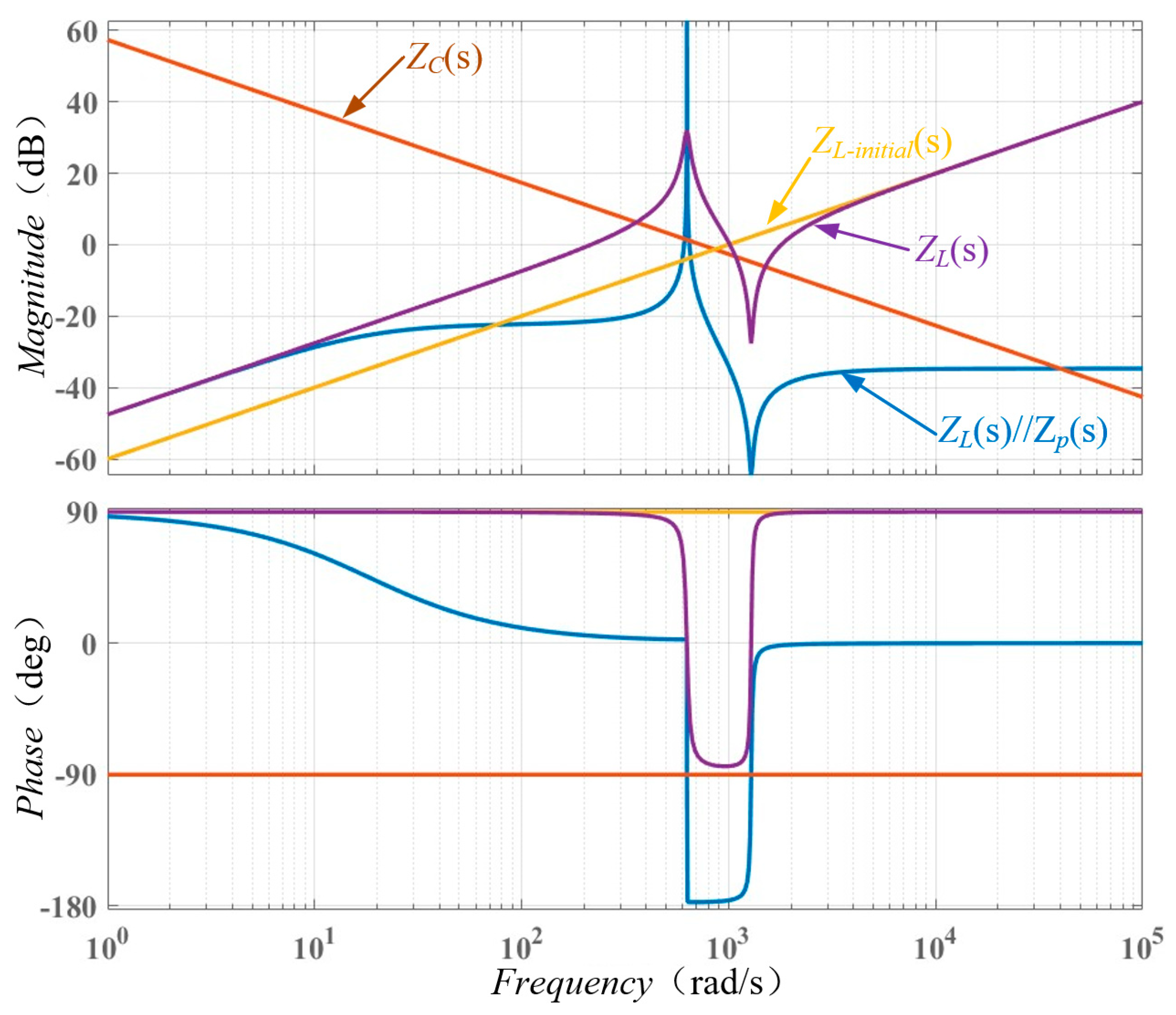

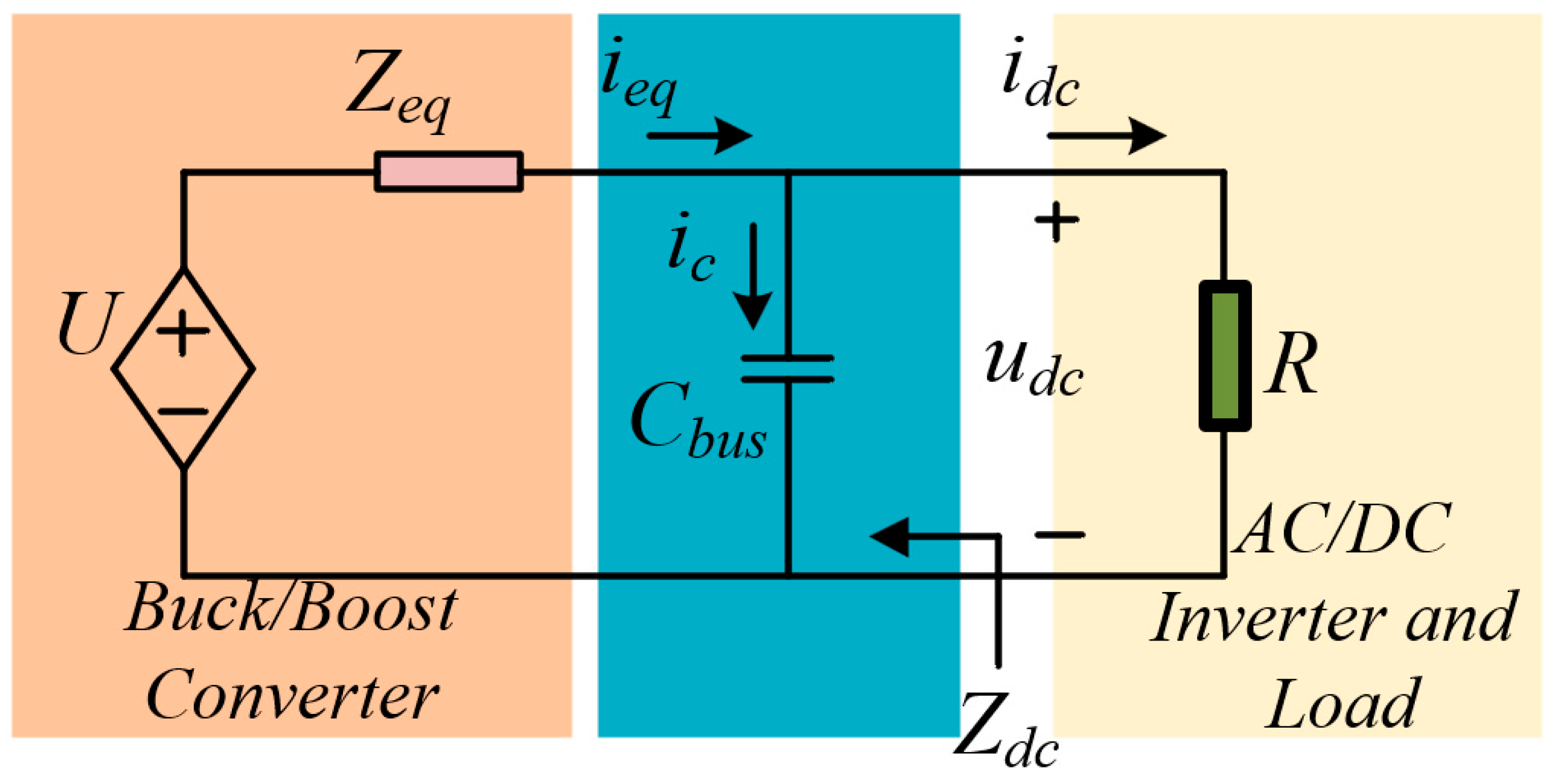

2. SRC Generation Mechanisms and Suppression Methods Based on Virtual Impedances

2.1. Generation and Propagation Mechanism of the SRCs

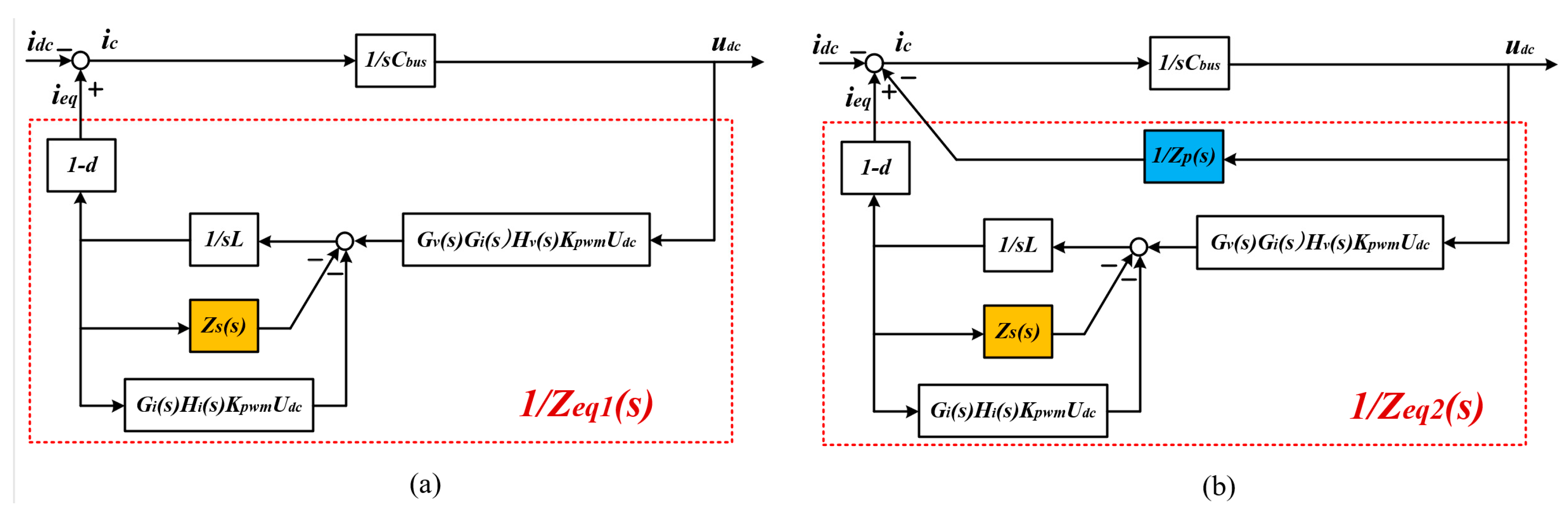

2.2. Suppression Method of SRCs Based on Virtual Impedance

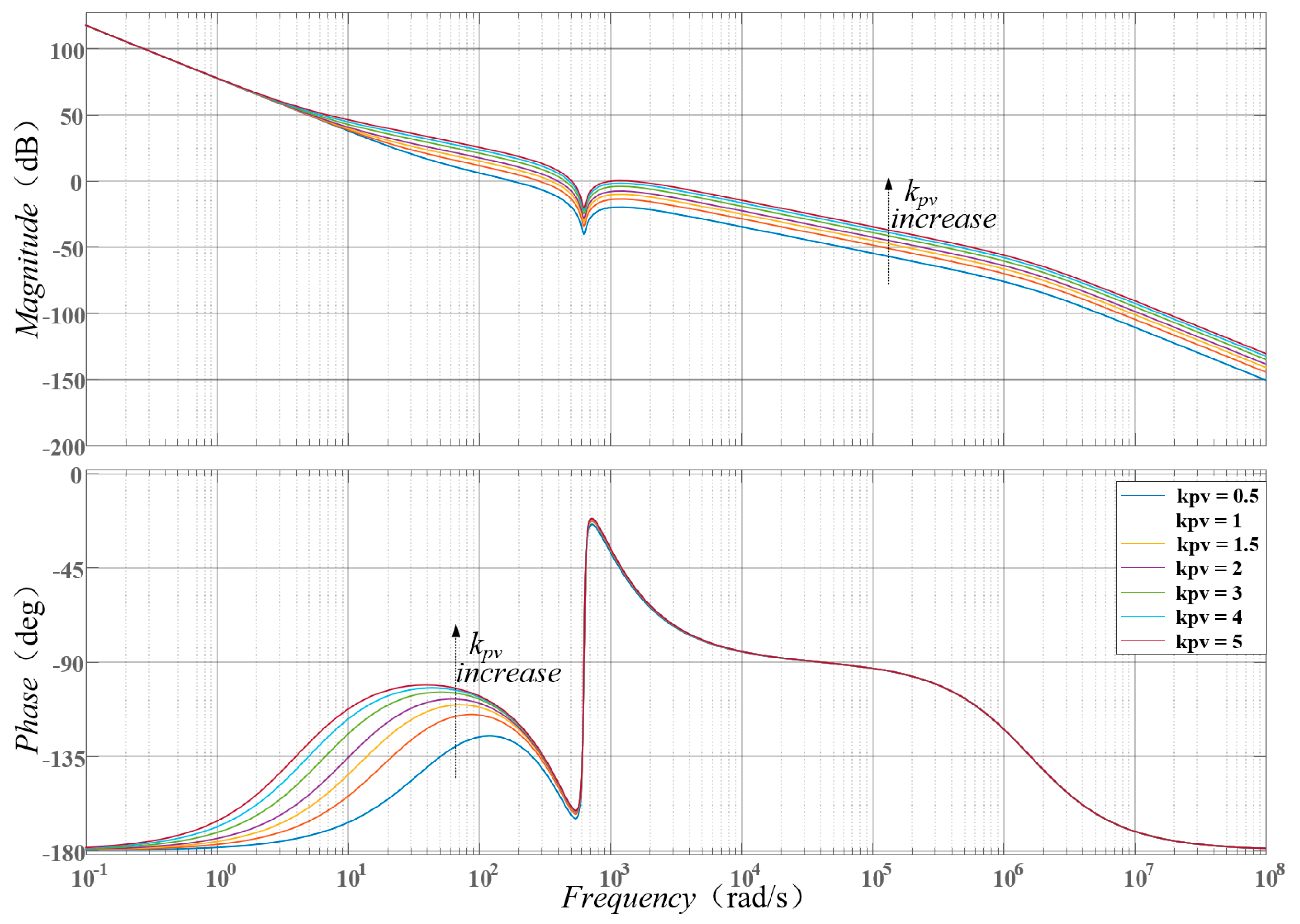

3. Virtual Impedance Selection and Parameter Design

4. Results Analysis

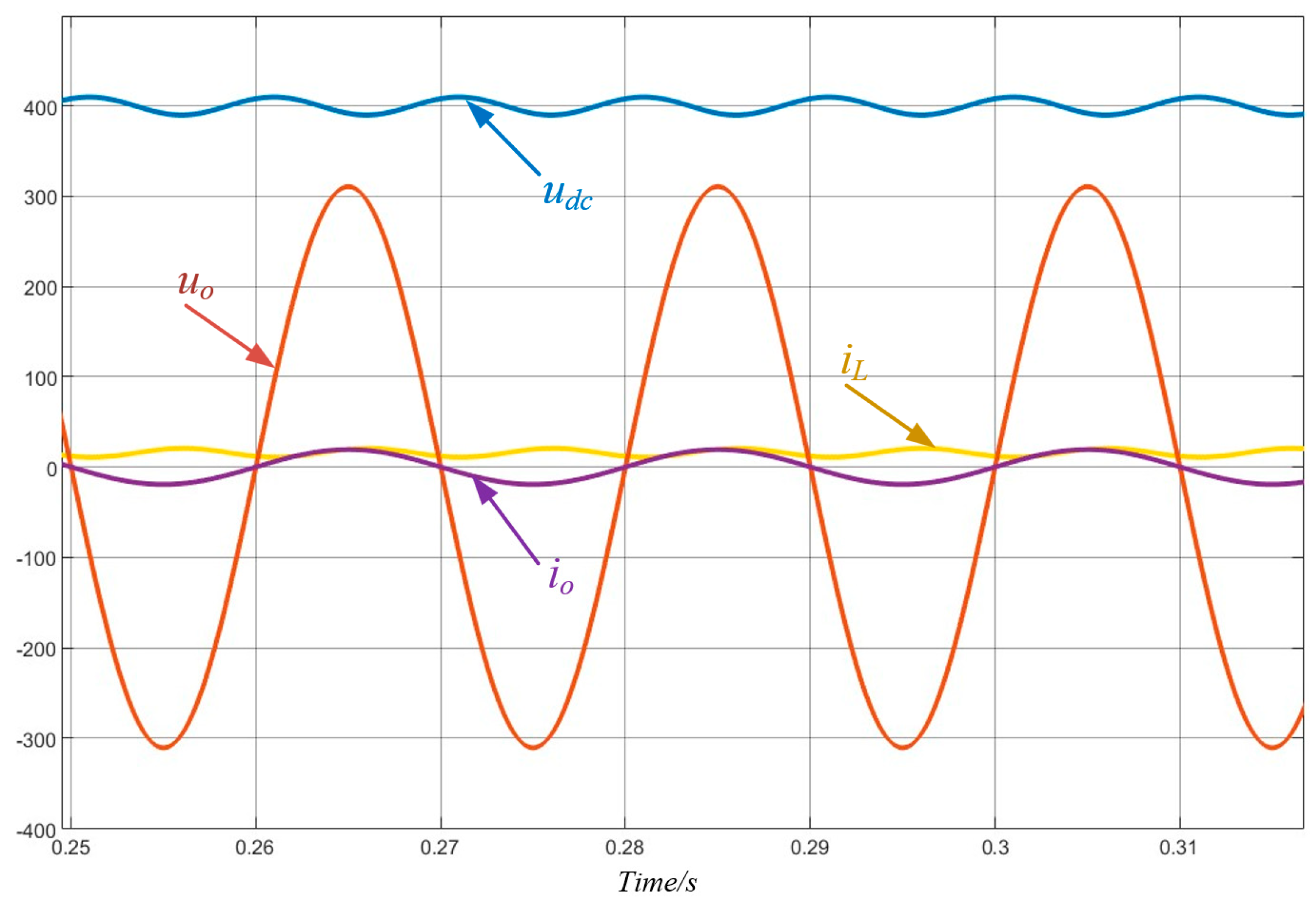

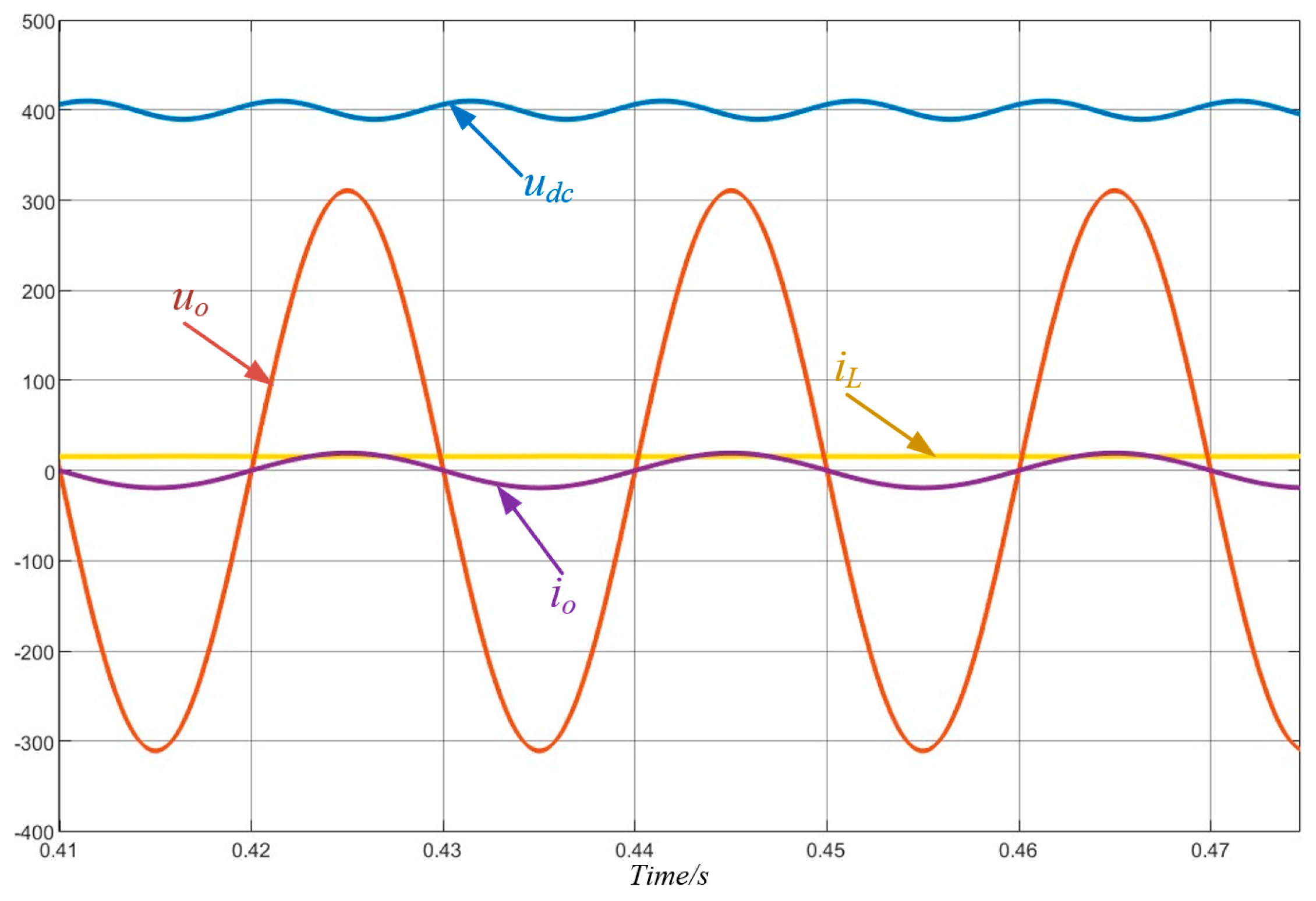

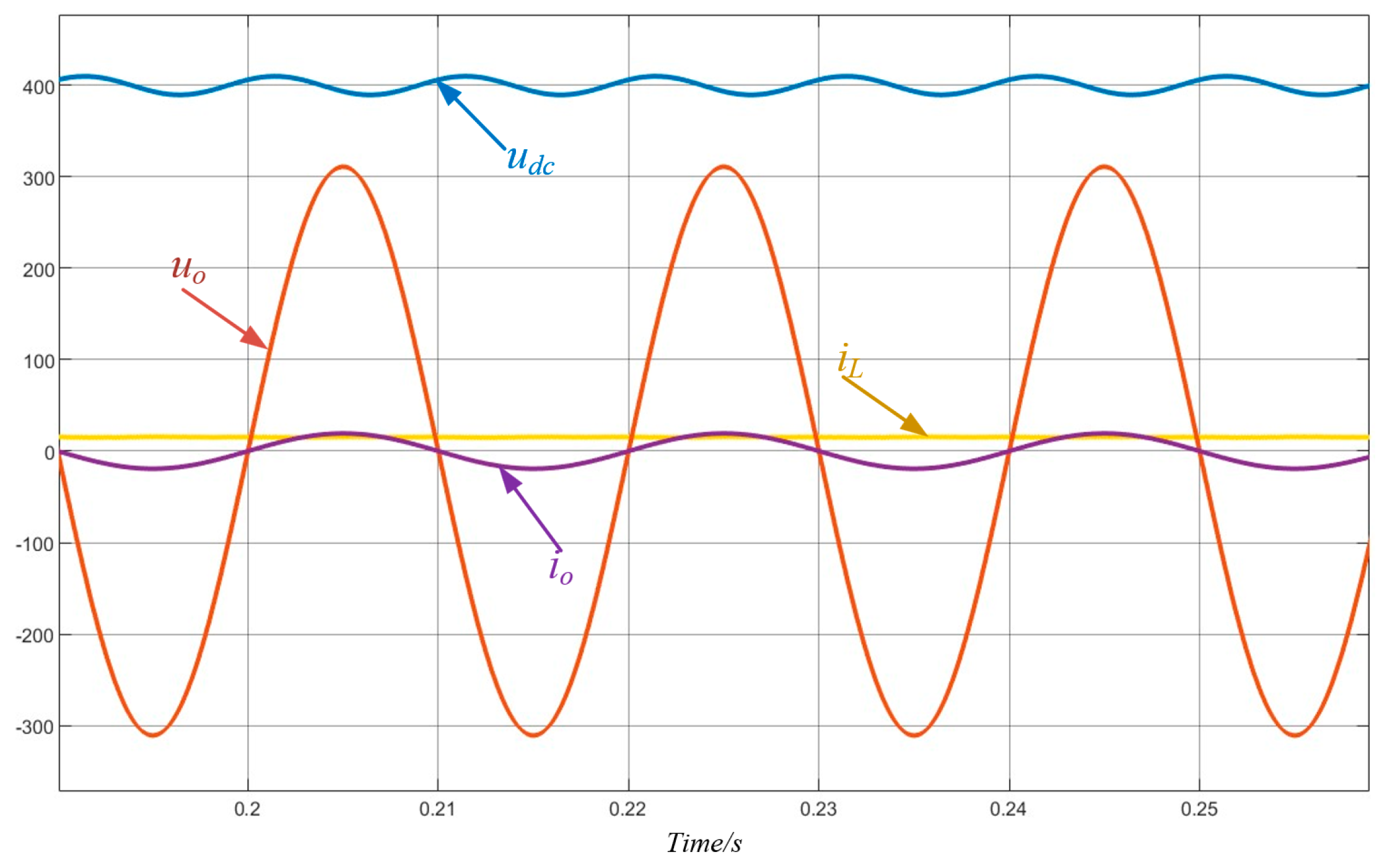

4.1. Simulation Results

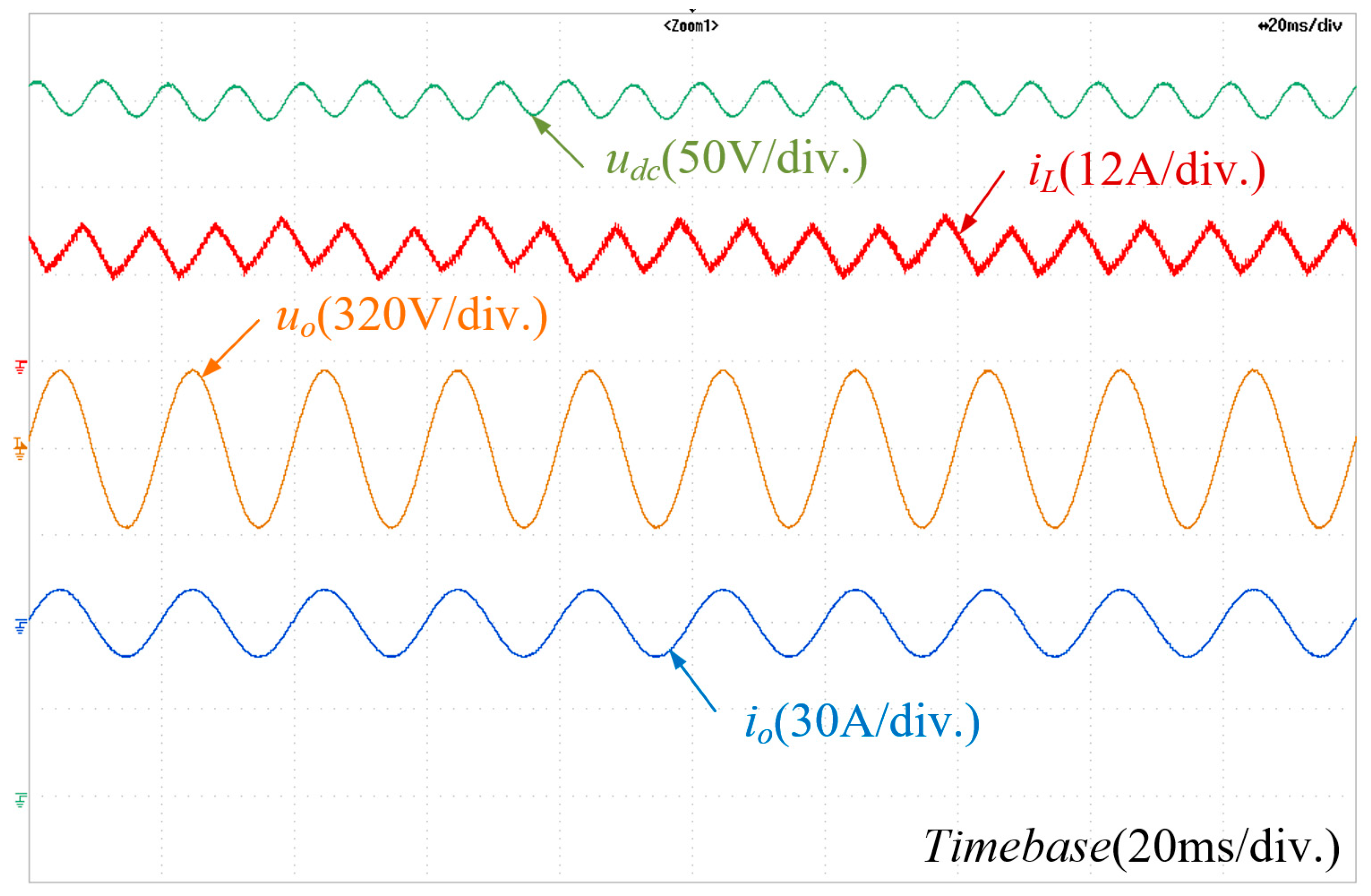

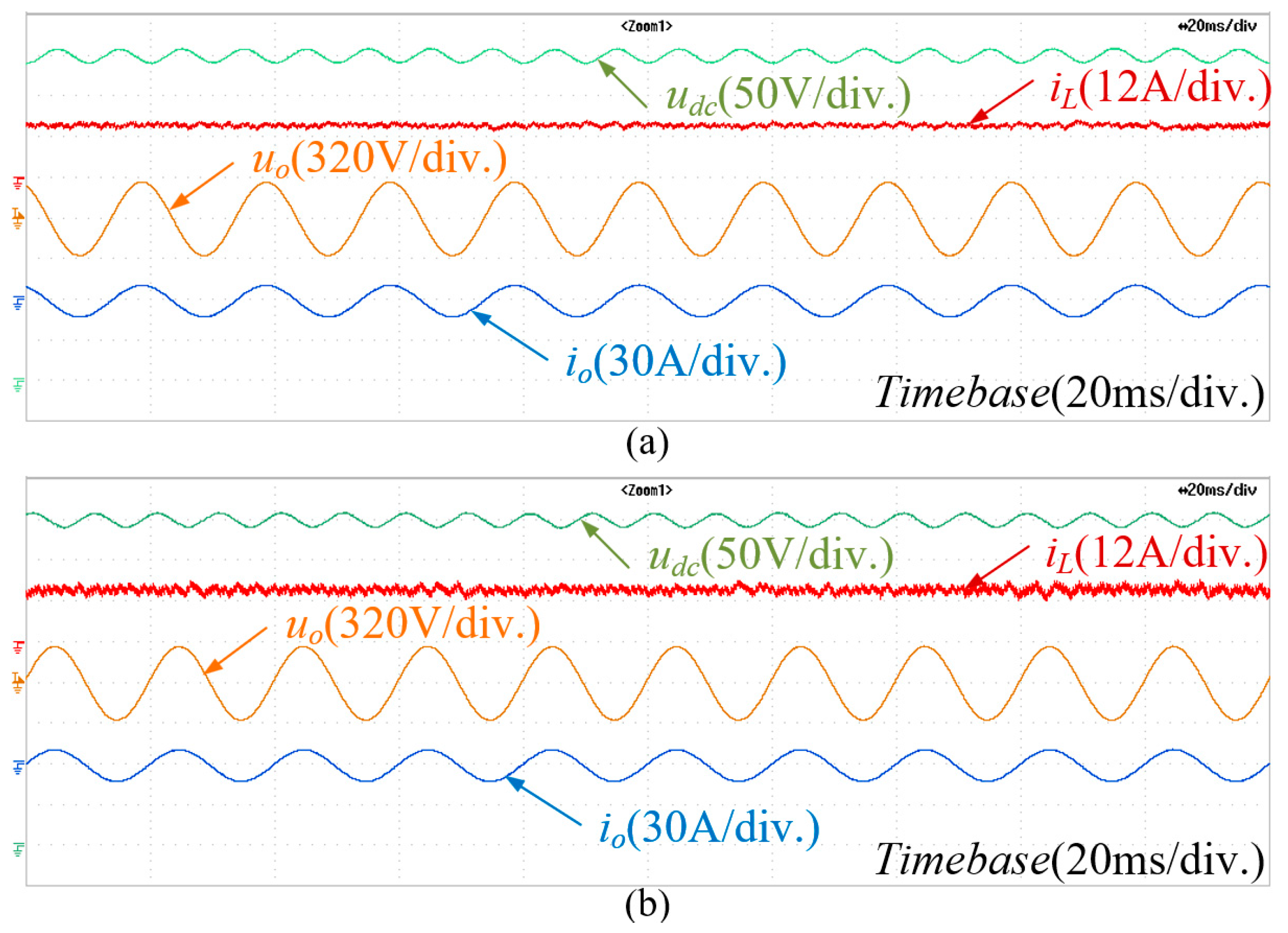

4.2. Experimental Verification

5. Conclusions

- (1)

- The fundamental mechanism behind the increased fourth harmonic content in the input current after introducing VSI and VPI requires further investigation. This study only proposed a possible explanation, which remains unverified.

- (2)

- In real-world applications, DVRs typically encounter complex conditions, such as grid harmonics, nonlinear loads, and load surges, which may limit the effectiveness of virtual impedance. It is necessary to adjust the virtual impedance parameters according to the impedance characteristics of different actual circuits.

- (3)

- Practical applications involve numerous uncertainties and variable conditions. Ensuring and improving the reliability and operational efficiency of DVRs under real-world operating scenarios are highly worthy of research. In subsequent studies, the risk aversion and distributed optimization methods from reference [28] can serve as important guidance.

- (4)

- In the practical application and promotion of DVRs, the cost, lifespan, and reliability of energy storage devices are major concerns for end-users. Reducing investment costs and extending service life to expand DVR adoption will be key research priorities. The shared energy storage service and optimal configuration methods proposed in reference [29] can effectively address these needs and provide critical guidance for our future work.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| DVR | Dynamic Voltage Restorer |

| ES | Energy Storage |

| SRCs | Second-order Ripple Currents |

| VSI | Virtual Series Impedance |

| VPI | Virtual Parallel Impedance |

References

- Martinez, J.A.; Arnedo, J.M. Voltage sag studies in distribution networks—Part I: System modeling. IEEE Trans. Power Del. 2006, 21, 1670–1678. [Google Scholar] [CrossRef]

- Kaniewski, J.; Fedyczak, Z.; Benysek, G. AC voltage sag/swell compensator based on three-phase hybrid transformer with buck–boost matrix-reactance chopper. IEEE Trans. Ind. Electron. 2014, 61, 3835–3846. [Google Scholar]

- Castilla, M.; Miret, J.; Camacho, A.; Matas, J.; de Vicuna, L. Voltage support control strategies for static synchronous compensators under unbalanced voltage sags. IEEE Trans. Ind. Electron. 2014, 61, 808–820. [Google Scholar] [CrossRef]

- Garcia, P.M.; Mancilla, F.; Ramirez, J.M. Per-sequence vector switching matrix converter modules for voltage regulation. IEEE Trans. Ind. Electron. 2013, 60, 5411–5421. [Google Scholar] [CrossRef]

- Kumar, C.; Mishra, M. A multifunctional DSTATCOM operating under stiff source. IEEE Trans. Ind. Electron. 2014, 61, 3131–3136. [Google Scholar]

- Kanjiya, P.; Singh, B.; Chandra, A.; Al-Haddad, K. SRF theory revisited to control self-supported dynamic voltage restorer (DVR) for unbalanced and nonlinear loads. IEEE Trans. Ind. Appl. 2013, 49, 2330–2340. [Google Scholar]

- Wessels, C.; Gebhardt, F.; Fuchs, F.W. Fault ride-through of a DFIG wind turbine using a dynamic voltage restorer during symmetrical and asymmetrical grid faults. IEEE Trans. Power Electron. 2011, 26, 807–815. [Google Scholar]

- Bala, S.; Tengnér, T.; Rosenfeld, P.; Delince, F. The effect of low frequency current ripple on the performance of a Lithium Iron Phosphate (LFP) battery energy storage system. In Proceedings of the 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 3485–3492. [Google Scholar] [CrossRef]

- Liu, C.; Wang, J.; Colombage, K.; Gould, C.; Sen, B.; Stone, D. Current ripple reduction in 4kW LLC resonant converter based battery charger for electric vehicles. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 6014–6021. [Google Scholar] [CrossRef]

- Qian, K.; Zhou, C.; Yuan, Y.; Allan, M. Temperature effect on electric vehicle battery cycle life in Vehicle-to-grid applications. In Proceedings of the 4th China International Conference on Electricity Distribution (CICED 2010), Nanjing, China, 13–16 September 2010; pp. 1–6. [Google Scholar]

- Sun, Y.; Liu, Y.; Su, M.; Xiong, W.; Yang, J. Review of active power decoupling topologies in single-phase systems. IEEE Trans. Power Electron. 2016, 31, 4778–4794. [Google Scholar]

- Tang, Y.; Blaabjerg, F.; Loh, P.C.; Jin, C.; Wang, P. Decoupling of fluctuating power in single-phase systems through a symmetrical half-bridge circuit. IEEE Trans. Power Electron. 2015, 30, 1855–1865. [Google Scholar]

- Lin, Z.; He, L.; Zhou, H. A second harmonic current suppressing method based on negative-order capacitor. IEEE Trans. Power Electron. 2022, 37, 8465–8475. [Google Scholar]

- Almeida, P.S.; Bender, V.C.; Braga, H.A.C.; Costa, M.A.D.; Marchesan, T.B.; Alonso, J.M. Static and dynamic photoelectrothermal modeling of led lamps including low-frequency current ripple effects. IEEE Trans. Power Electron. 2015, 30, 3841–3851. [Google Scholar] [CrossRef]

- Wang, H.; Blaabjerg, F. Reliability of capacitors for dc-link applications in power electronic converters—An overview. IEEE Trans. Ind. Appl. 2014, 50, 3569–3578. [Google Scholar] [CrossRef]

- Liu, C.; Lai, J.-S. Low frequency current ripple reduction technique with active control in a fuel cell power system with inverter load. IEEE Trans. Power Electron. 2007, 22, 1429–1436. [Google Scholar] [CrossRef]

- Wang, J.; Ji, B.; Lu, X.; Deng, X.; Zhang, F.; Gong, C. Steady-state and dynamic input current low-frequency ripple evaluation and reduction in two-stage single-phase inverters with back current gain model. IEEE Trans. Power Electron. 2014, 29, 4247–4260. [Google Scholar] [CrossRef]

- Ksiazek, P.F.; Ordonez, M. Swinging bus technique for ripple current elimination in fuel cell power conversion. IEEE Trans. Power Electron. 2014, 29, 170–178. [Google Scholar] [CrossRef]

- Zhang, L.; Ren, X.; Ruan, X. A bandpass filter incorporated into the inductor current feedback path for improving dynamic performance of the front-end DC–DC converter two-stage inverter. IEEE Trans. Ind. Electron. 2014, 61, 2316–2325. [Google Scholar] [CrossRef]

- Chaturvedi, S.; Fulwani, D.; Patel, D. Dynamic Virtual Impedance-Based Second-Order Ripple Regulation in DC Microgrids. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 1075–1083. [Google Scholar] [CrossRef]

- Zhu, G.; Ruan, X.; Zhang, L.; Wang, X. On the reduction of second harmonic current and improvement of dynamic response for two-stage single-phase inverter. IEEE Trans. Power Electron. 2015, 30, 1028–1041. [Google Scholar] [CrossRef]

- Zhang, L.; Ruan, X.; Ren, X. Second-harmonic current reduction and dynamic performance improvement in the two-stage inverters: An output impedance perspective. IEEE Trans. Ind. Electron. 2015, 62, 394–404. [Google Scholar] [CrossRef]

- Zhou, H.; He, L. Impedance-Edited Multiple Low-Frequency Harmonic Current Adaptive Suppression. IEEE Trans. Power Electron. 2023, 38, 7022–7033. [Google Scholar] [CrossRef]

- Zhou, H.; He, L.; Yang, Z.; Lin, Z. Virtual Fractional-Order-Inductor Based Second Harmonic Current Suppression Method. IEEE Trans. Ind. Electron. 2024, 71, 8949–8959. [Google Scholar] [CrossRef]

- Lei, Y.; Yang, P.; Yu, M. An Improved Deadbeat Control Method for Second Harmonic Current Reduction in Two-Stage Single-Phase Inverter. In Proceedings of the 2022 International Conference on Power Energy Systems and Applications (ICoPESA), Singapore, 25–27 February 2022; pp. 319–325. [Google Scholar]

- Liu, G.; Caldognetto, T.; Mattavelli, P.; Magnone, P. Suppression of Second-Order Harmonic Current for Droop-Controlled Distributed Energy Resource Converters in DC Microgrids. IEEE Trans. Ind. Electron. 2020, 67, 358–368. [Google Scholar] [CrossRef]

- Wang, Y.; Yang, J.-W.; Kim, W.-J.; Kwon, T.-H.; Lee, T.; Park, S.-J. Second Harmonic Current Suppression and Dynamic Response Improvement for V2G System. IEEE Trans. Power Electron. 2023, 38, 9566–9580. [Google Scholar] [CrossRef]

- Zhai, X.; Li, Z.; Li, Z.; Xue, Y.; Chang, X.; Su, J.; Jin, X.; Wang, P.; Sun, H. Risk-averse energy management for integrated electricity and heat systems considering building heating vertical imbalance: An asynchronous decentralized approach. Appl. Energy 2025, 383, 125271. [Google Scholar] [CrossRef]

- Zhang, H.; Li, Z.; Xue, Y.; Chang, X.; Su, J.; Wang, P.; Guo, Q.; Sun, H. A Stochastic Bi-Level Optimal Allocation Approach of Intelligent Buildings Considering Energy Storage Sharing Services. IEEE Trans. Consum. Electron. 2024, 70, 5142–5153. [Google Scholar] [CrossRef]

| Parameters | Specifications | |

|---|---|---|

| Buck/Boost Converter | Ubat/V | 200 |

| fs/kHz | 10 | |

| L/mH | 0.5 | |

| Cbus/mF | 1.36 | |

| Single-phase Inverter | Uac/V | 311 |

| f0/Hz | 50 | |

| Lf/mH | 4 | |

| Cf/mF | 0.13 | |

| Switching Frequency/kHz | 10 | |

| Virtual impedance | rs | 200 |

| QBPF | 2 | |

| QN | 2 | |

| PI controller | kpv | 1 |

| kiv | 10 | |

| kpi | 5 | |

| kii | 20 |

| Methods | Without Virtual Impedance | Reference [27] | With VSI | With VSI and VPI |

|---|---|---|---|---|

| Average of /A | 15.69 | 15.43 | 15.68 | 15.27 |

| Percentage of second-order ripple current | 31.72% | 2.894% | 1.04% | 1.07% |

| Percentage of fourth-order ripple current | 0.22% | \ | 0.13% | 1.16% |

| Methods | Without Virtual Impedance | Reference [27] | With VSI | With VSI and VPI |

|---|---|---|---|---|

| Average of /A | 15.32 | 15.31 | 15.21 | 15.14 |

| Percentage of second-order ripple current | 39.64% | 2.11% | 1.74% | 1.78% |

| Percentage of fourth-order ripple current | 0.54% | \ | 0.64% | 1.62% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, G.; Shi, Q.; Li, W.; Zhang, Q.; Liu, J. Second-Order Ripple Current Suppression Based on Virtual Impedance in the Application of Dynamic Voltage Restorer. Energies 2025, 18, 1896. https://doi.org/10.3390/en18081896

Huang G, Shi Q, Li W, Zhang Q, Liu J. Second-Order Ripple Current Suppression Based on Virtual Impedance in the Application of Dynamic Voltage Restorer. Energies. 2025; 18(8):1896. https://doi.org/10.3390/en18081896

Chicago/Turabian StyleHuang, Guoping, Qiao Shi, Wenqing Li, Qing Zhang, and Junfeng Liu. 2025. "Second-Order Ripple Current Suppression Based on Virtual Impedance in the Application of Dynamic Voltage Restorer" Energies 18, no. 8: 1896. https://doi.org/10.3390/en18081896

APA StyleHuang, G., Shi, Q., Li, W., Zhang, Q., & Liu, J. (2025). Second-Order Ripple Current Suppression Based on Virtual Impedance in the Application of Dynamic Voltage Restorer. Energies, 18(8), 1896. https://doi.org/10.3390/en18081896