Stress Impact of the Annealing Procedure of Cu-Filled TSV Packaging on the Performance of Nano-Scaled MOSFETs Evaluated by an Analytical Solution and FEA-Based Submodeling Technique

Abstract

:1. Introduction

2. Fundamental Theories of 2D Analytical Stress Solution, Lattice Stress Estimation Approach and Piezoresistance Behavior for Stress-Induced Performance Investigation

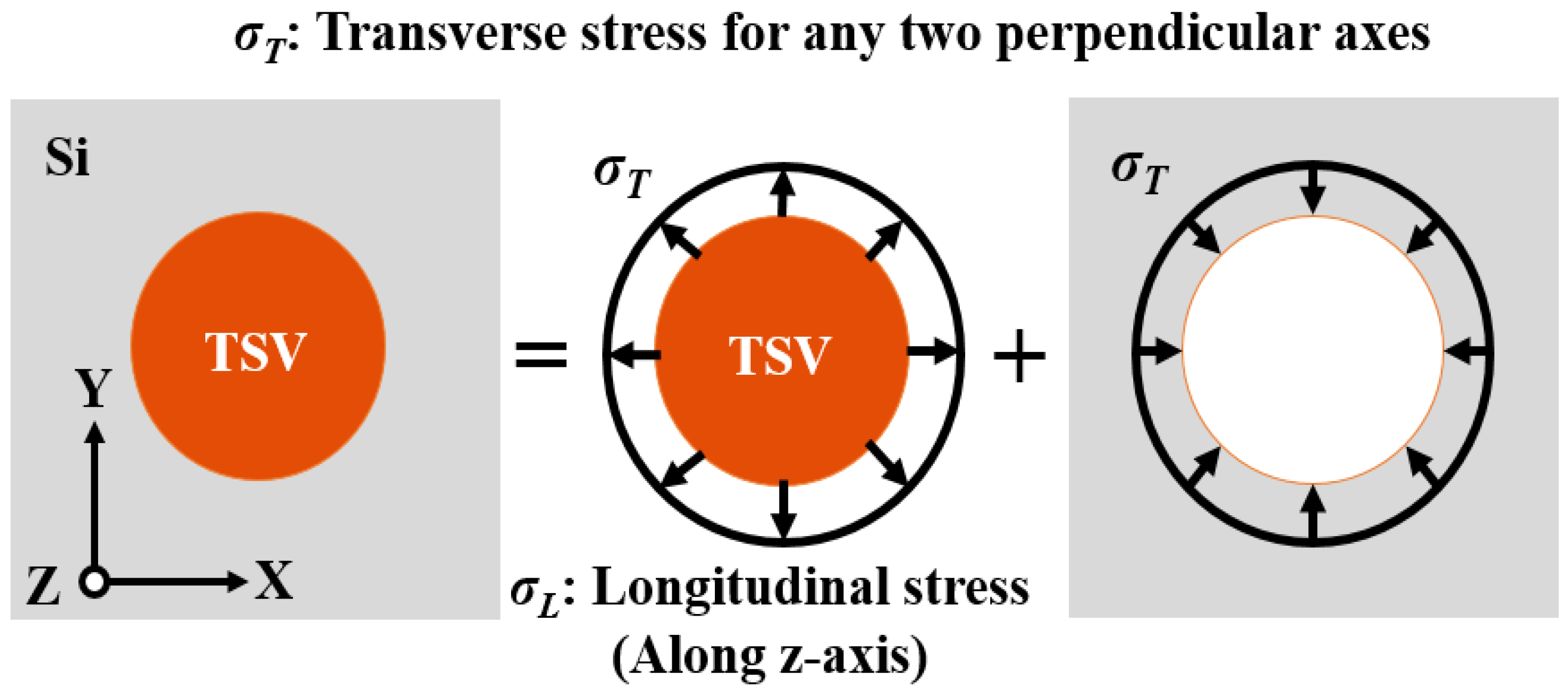

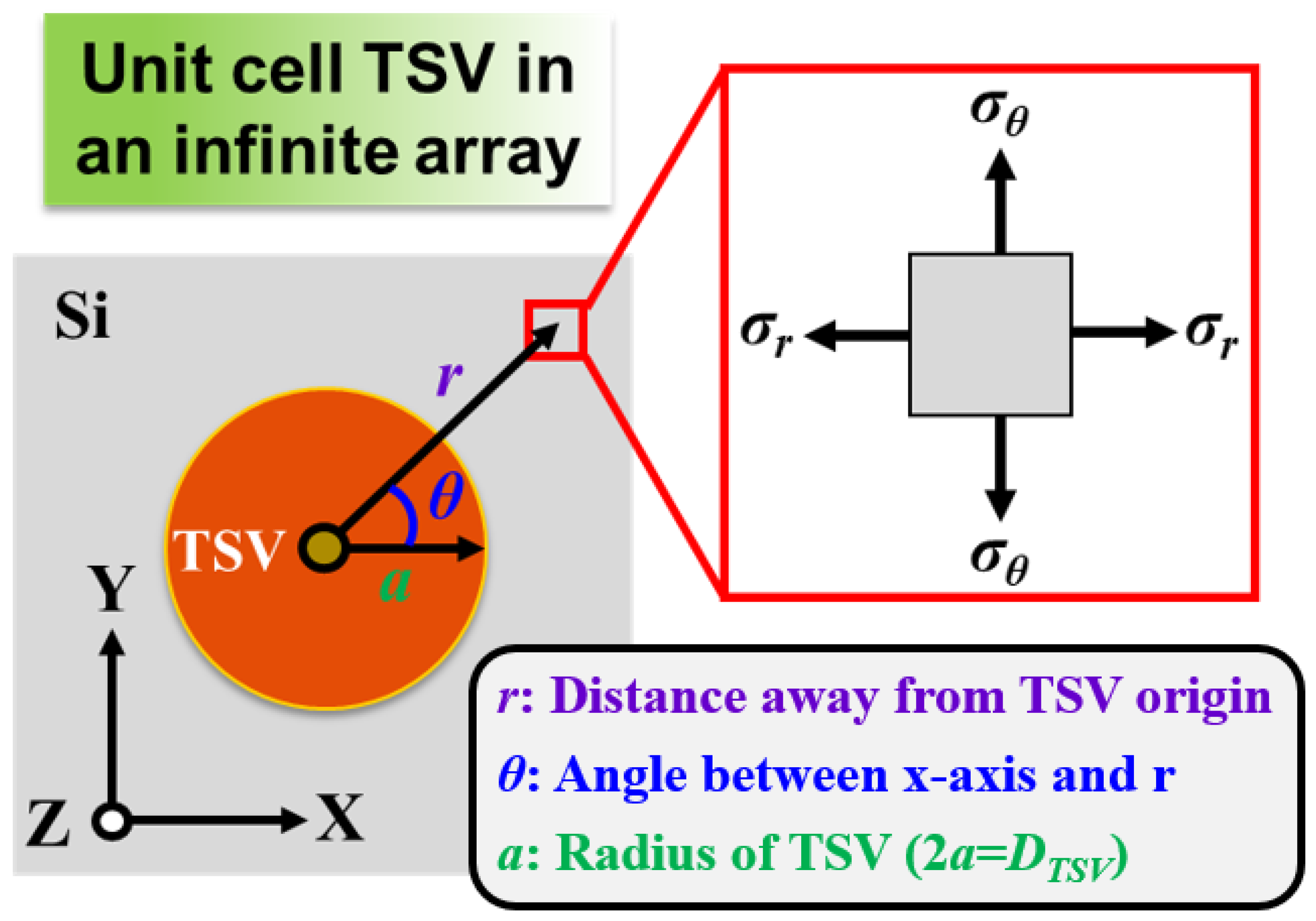

2.1. 2D Analytical Solution for Stress Estimation of TSV and the Surrounding Substrate

2.2. Theotical Calculation of Lattice Mismatch Strain on the Absis of Vegard’s Law

2.3. Piezoresistance Characteristics of Semiconductor Material for Estimating Stress-Induced Carrier Mobility Variation

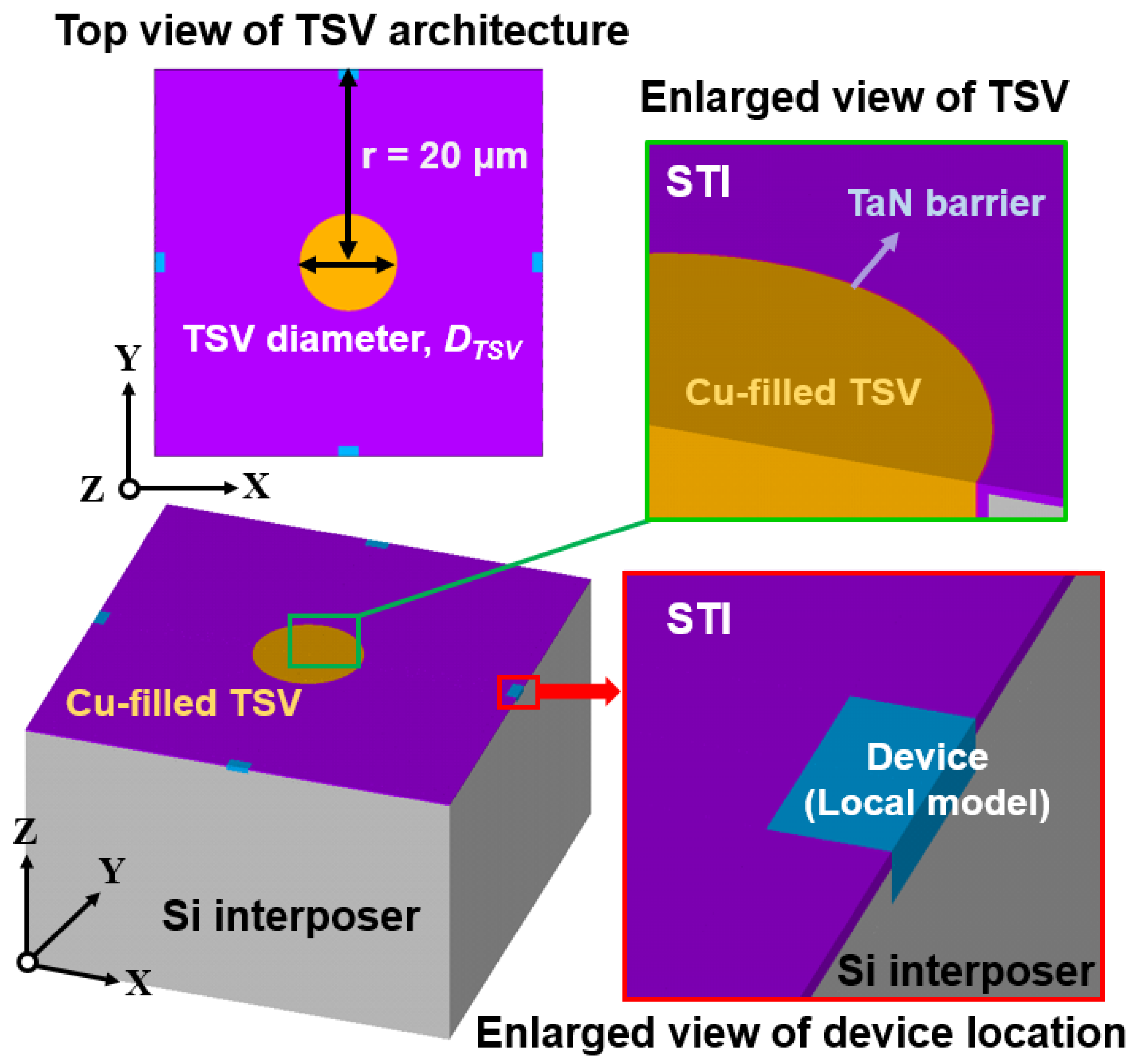

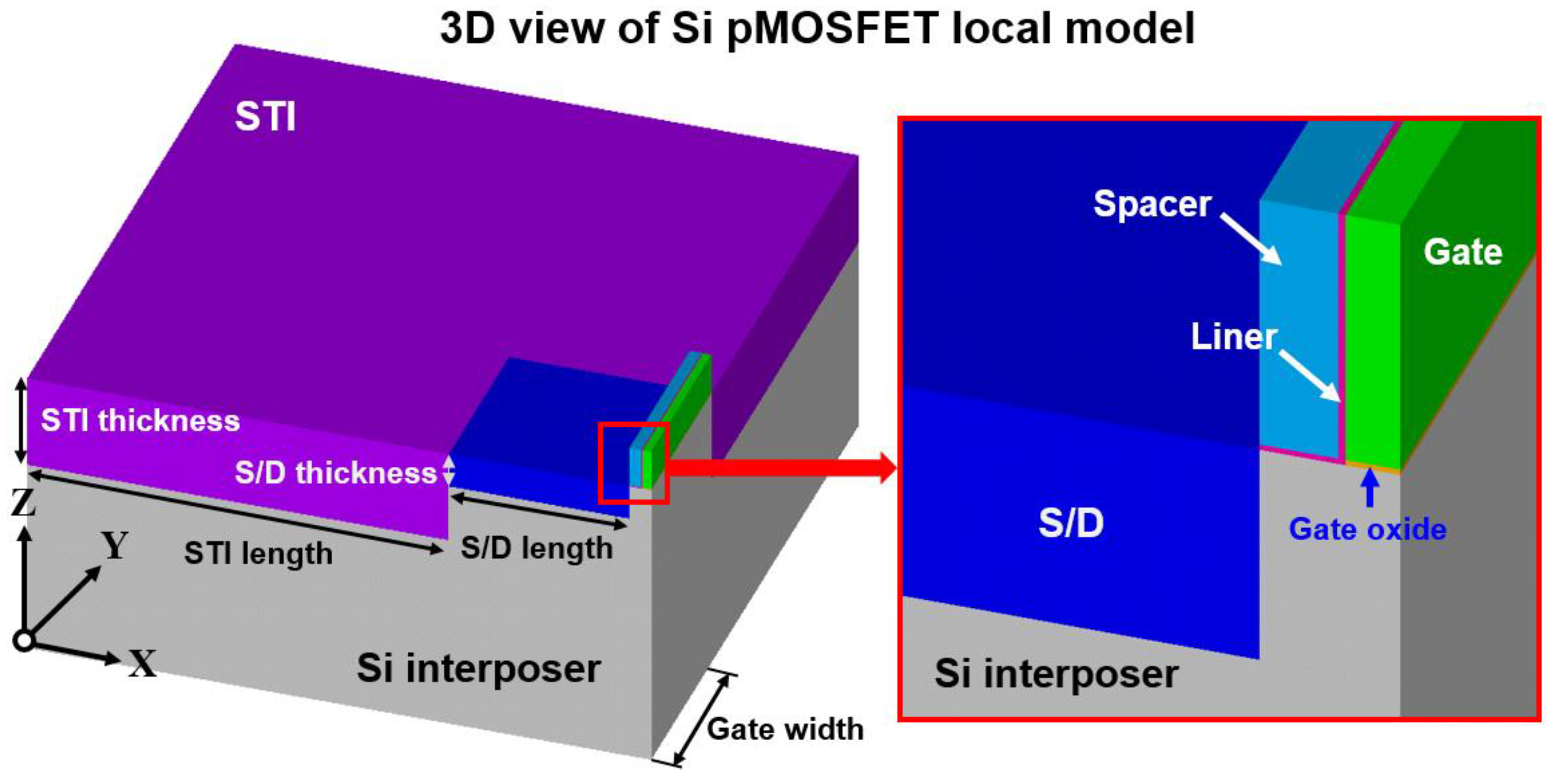

3. FEA Modeling of Global TSV Interposer Packaging Architecture and Local Transistor De-Vice Model Based on the Submodeling Technique

4. Results and Discussions

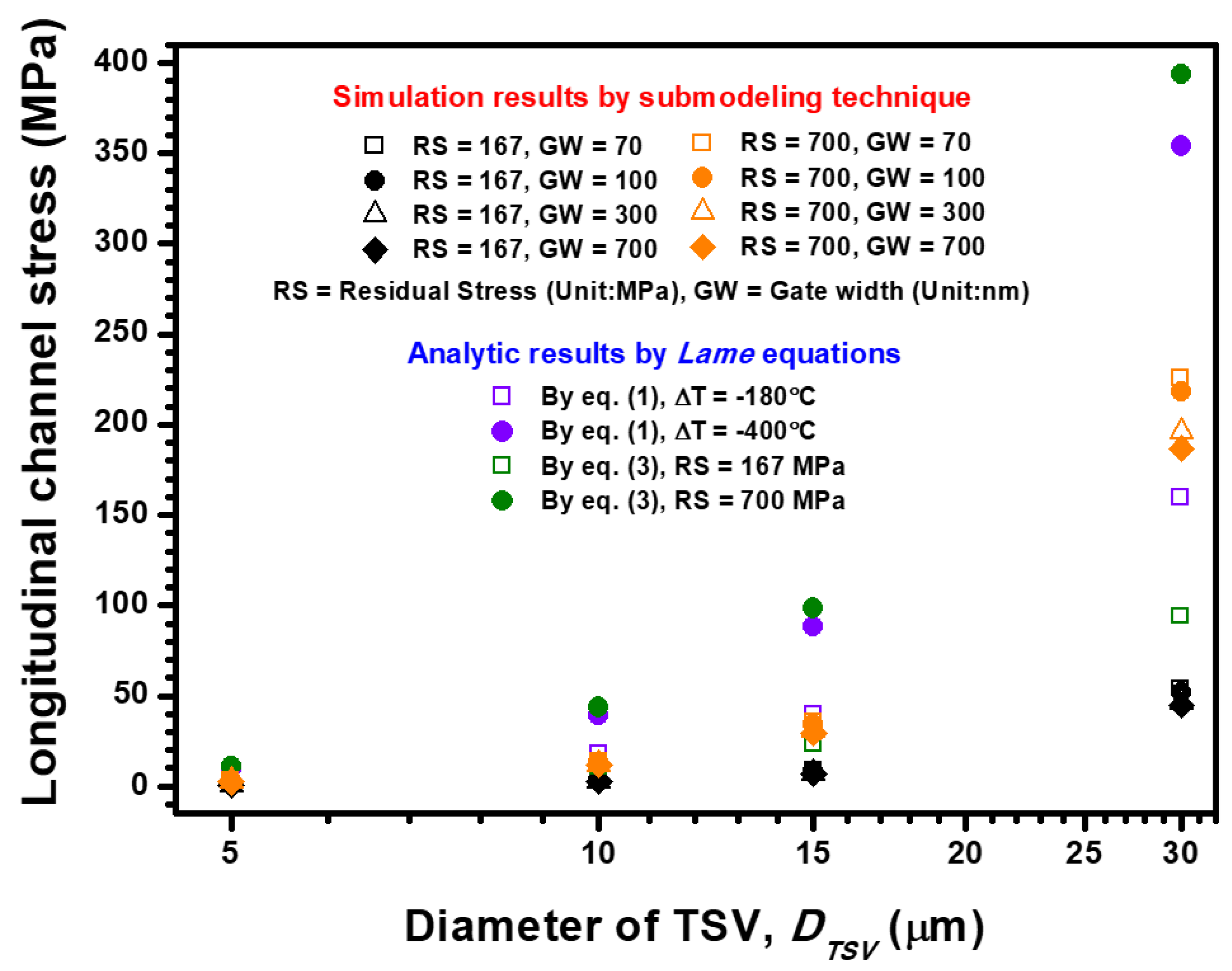

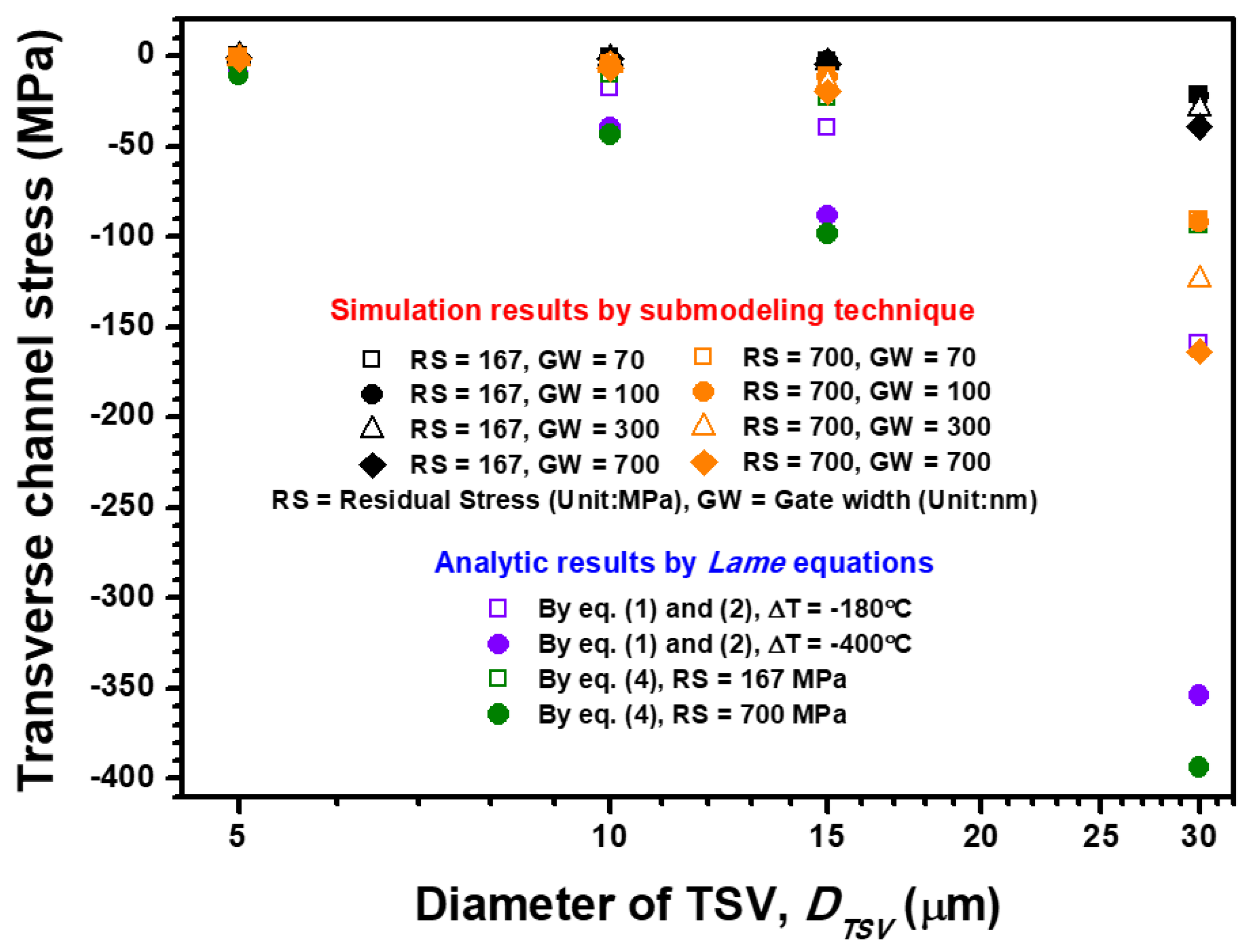

4.1. Comparison of Analytical and FEA Submodeling Results on the Longitudinal and Trasnverse Stress of the Si pMOSFET Device Channel

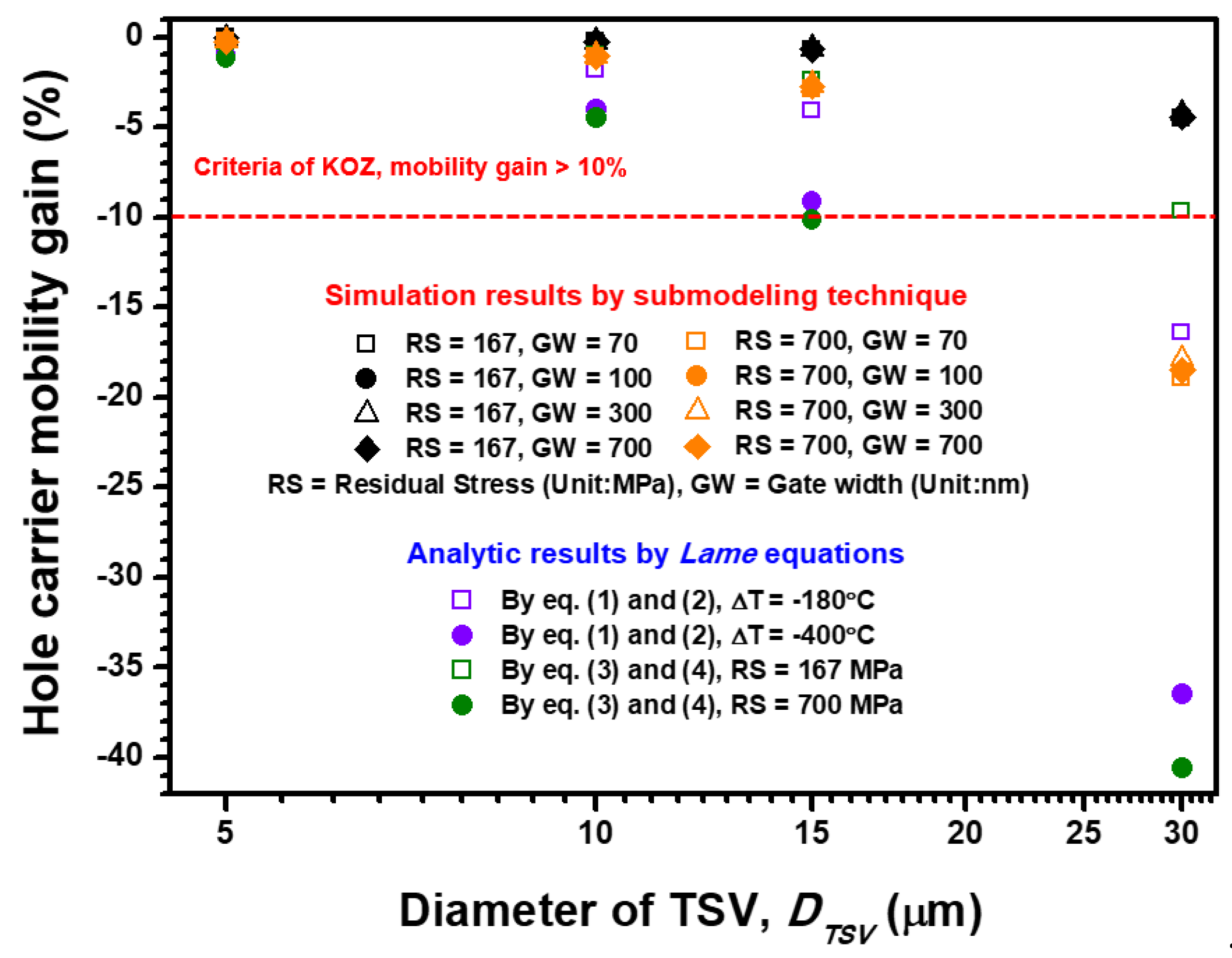

4.2. Stress-Induced Hole Carrier Mobility Gain Change and KOZ Estimation Based on Analytical and FEA Submodeling Results

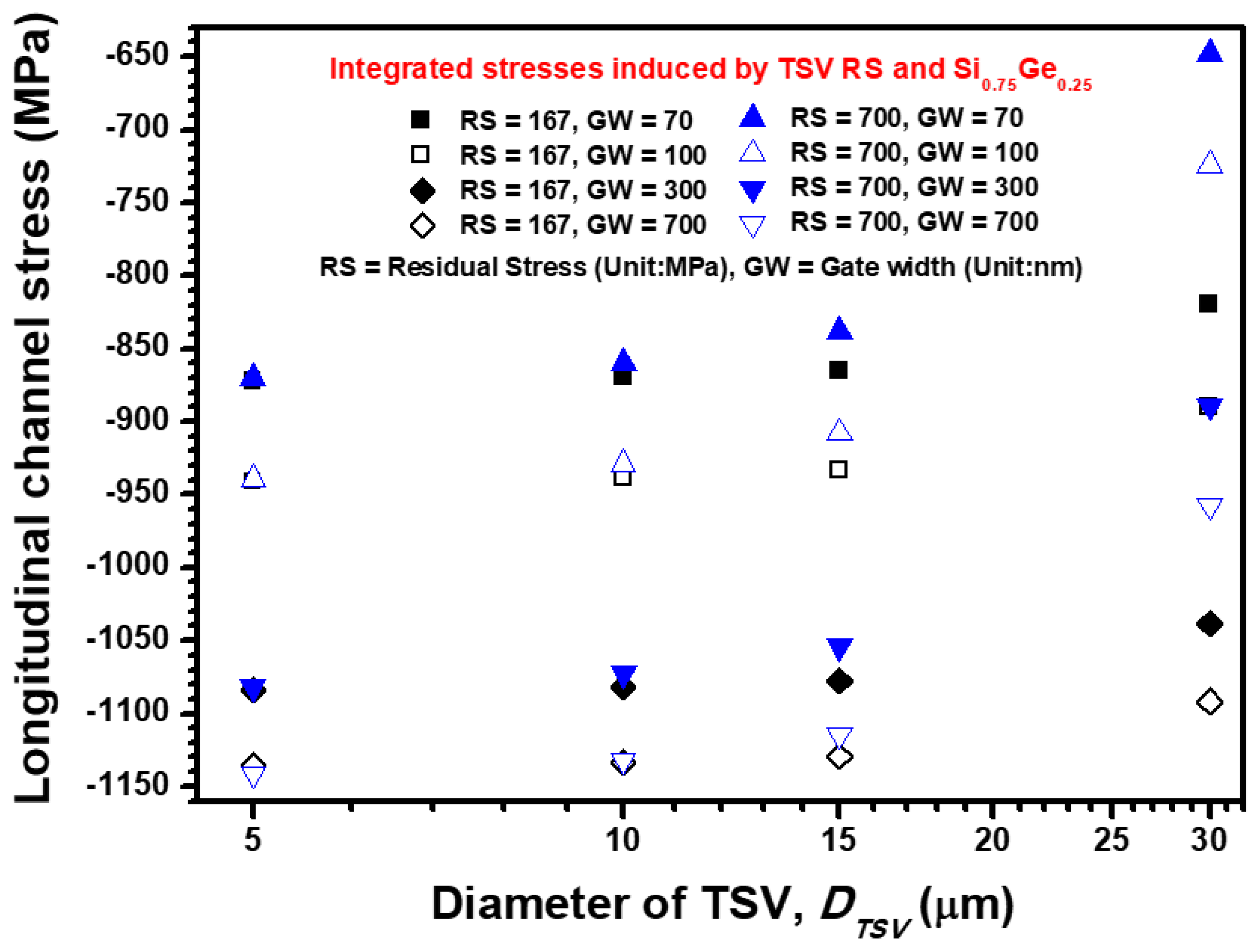

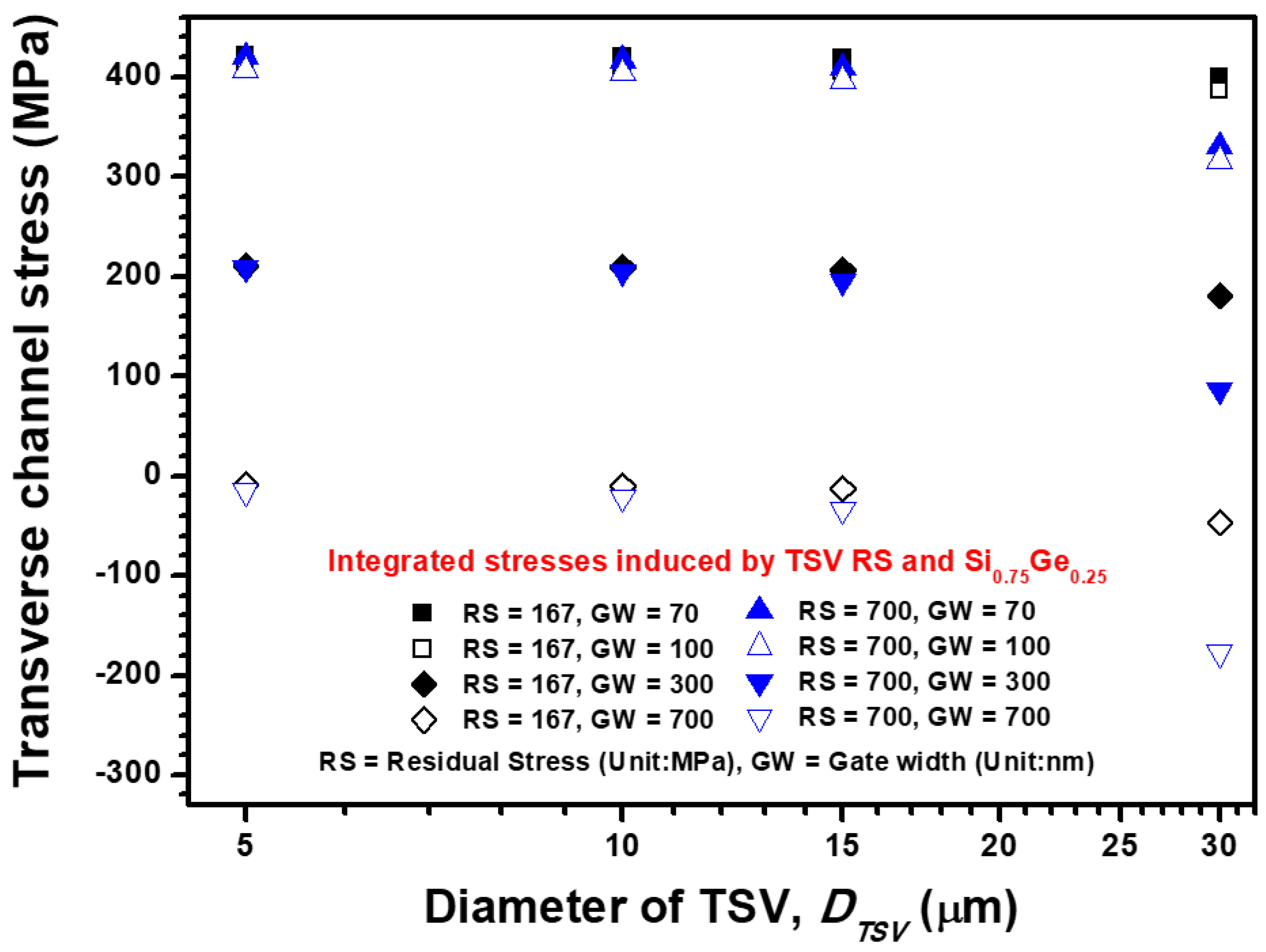

4.3. FEA Submodeling Results on the Longitudinal and Transverse Stresses of the Si pMOSFET Device Channel under the Integrated Effect of TSV RS and Strain Engineering S/D Lattice Stressor

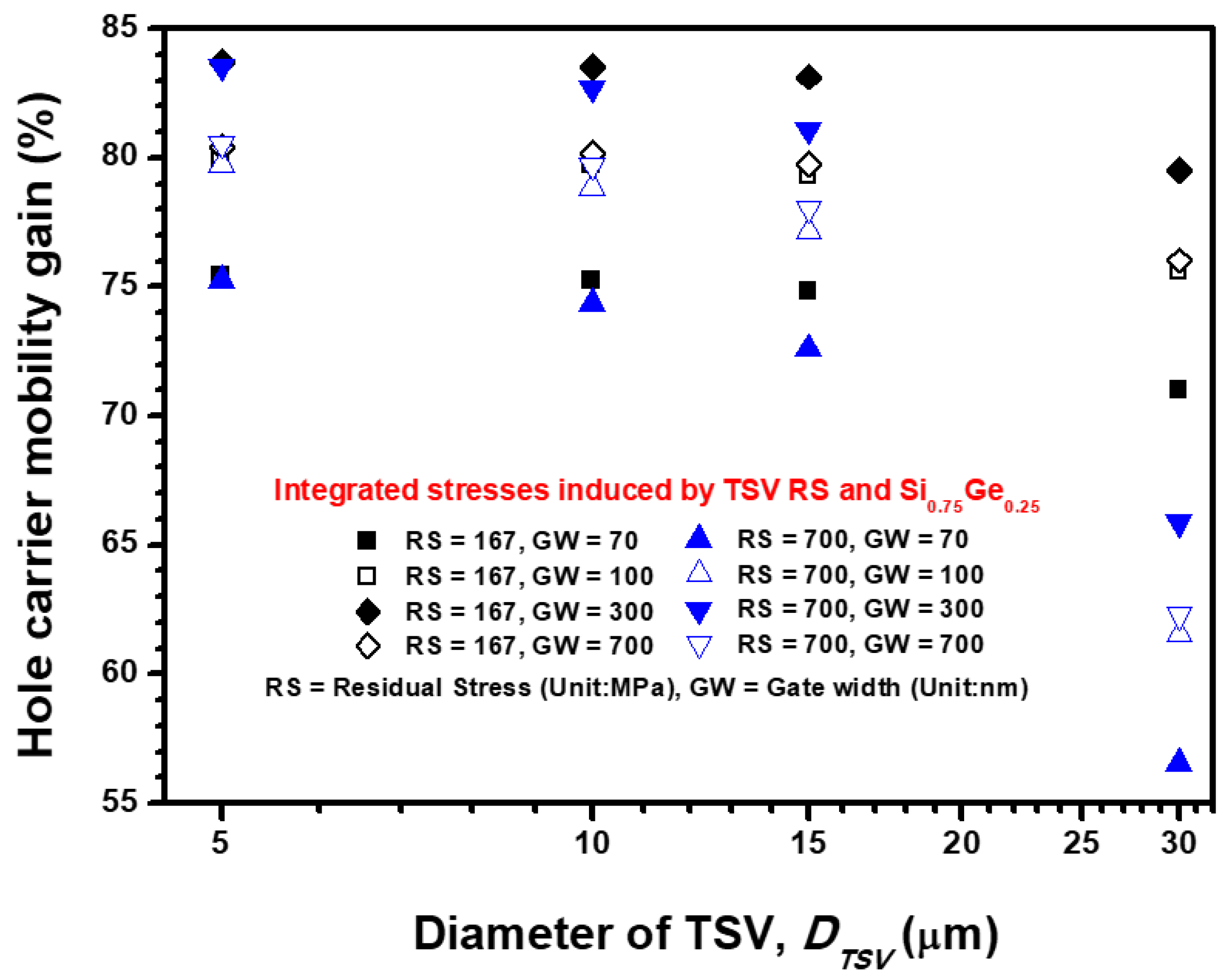

4.4. Stress-Induced Hole Carrier Mobility Gain Change in the S/D Lattice-Strained Si pMOSFET Under the RS Impact Generated by Cu-Filled TSV

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Lubow, A.; Ismail-Beigi, S.; Ma, T.P. Comparison of Drive Currents in Metal-Oxide-Semiconductor Field-Effect Transistors Made of Si, Ge, GaAs, InGaAs, and InAs Channels. Appl. Phys. Lett. 2012, 96, 122105. [Google Scholar] [CrossRef]

- Alamo, J.A. Del. Nanometre-scale Electronics with III–V Compound Semiconductors. Nature 2011, 479, 317–323. [Google Scholar] [CrossRef]

- Suthram, S.; Ziegert, J.C.; Nishida, T.; Thompson, S.E. Piezoresistance Coefficients of (100) Silicon nMOSFETs Measured at Low and High (∼1.5 GPa) Channel Stress. IEEE Electron Device Lett. 2007, 28, 58–61. [Google Scholar] [CrossRef]

- Nainani, A.; Yum, J.; Barnett, J.; Hill, R.; Goel, N.; Huang, J.; Majhi, P.; Jammy, R.; Sarawat, K.C. Study of Piezoresistance Under Unixial Stress for Technologically Relevant III-V Semiconductors Using Wafer Bending Experiments. Appl. Phys. Lett. 2010, 96, 242110. [Google Scholar] [CrossRef]

- Chu, M.; Nishida, T.; Lv, X.; Mohta, N.; Thompson, S.E. Comparison between High-Field Piezoresistance Coefficients of Si Metal-Oxide-Semiconductor Field-Effect Transistors and Bulk Si Under Uniaxial and Biaxial Stress. J. Appl. Phys. 2008, 103, 113704. [Google Scholar] [CrossRef]

- Gambino, J.P.; Adderly, S.A.; Knickerbocker, J.U. An Overview of Through-Silicon-Via Technology and Manufacturing Challenges. Microelectron. Eng. 2015, 135, 73–106. [Google Scholar] [CrossRef]

- Shi, P.; Enloe, J.; van den Boom, R.; Sapp, B. Direct Copper Electrodeposition on a Chemical Vapor-Deposited Ruthenium Seed Layer for Through-Silicon Vias. In Proceedings of the IEEE International Interconnect Technology Conference, San Jose, CA, USA, 4–6 June 2012. [Google Scholar]

- Lau, J.H. Evolution and Outlook of TSV and 3D IC/Si Integration. In Proceedings of the Electronics Packaging Technology Conference, Singapore, 8–10 December 2010. [Google Scholar]

- Lau, J.H. Evolution, challenge, and outlook of TSV, 3D IC integration and 3D Silicon Integration. In Proceedings of the International Symposium on Advanced Packaging Materials, Xiamen, China, 25–28 October 2011. [Google Scholar]

- Li, L.; Ton, P.; Nagar, M.; Chia, P. Reliability Challenges in 2.5D and 3D IC Integration. In Proceedings of the IEEE Electronic Components and Technology Conference, Orlando, FL, USA, 30 May–2 June 2017. [Google Scholar]

- Leduc, P.; Crécy, F.D.; Fayolle, M.; Charlet, B.; Enot, T.; Zussy, M.; Jones, B.; Barbé, J.C.; Kernevez, N.; Sillon, N.; et al. Challenges for 3D IC Integration: Bonding Quality and Thermal Management. In Proceedings of the IEEE International Interconnect Technology Conference, Burlingame, CA, USA, 4–6 June 2007. [Google Scholar]

- Heryanto, A.; Putra, W.N.; Trigg, A.; Gao, S.; Kwon, W.S.; Che, F.X.; Ang, X.F.; Wei, J.; Made, R.I.; Gan, C.L.; et al. Effect of Copper TSV Annealing on Via Protrusion for TSV Wafer Fabrication. J. Electron. Mater. 2012, 41, 2533–2542. [Google Scholar] [CrossRef]

- Che, F.X.; Putra, W.N.; Heryanto, A.; Trigg, A.; Zhang, X.; Gan, C.L. Study on Cu Protrusion of Through-Silicon Via. IEEE Trans. Compon. Pack. Manuf. Technol. 2013, 3, 732–739. [Google Scholar] [CrossRef]

- Ranganathan, N.; Prasad, K.; Balasubramanian, N.; Pey, K.L. A Study of Thermo-Mechanical Stress and Its Impact on Through-Silicon Vias. J. Micromech. Microeng. 2008, 18, 75018. [Google Scholar] [CrossRef]

- Amagai, M.; Suzuki, Y. TSV Stress Testing and Modeling. In Proceedings of the Electronic Components and Technology Conference, Las Vegas, NV, USA, 1–4 June 2010. [Google Scholar]

- Xu, X.; Karmarkar, A. 3D TCAD Modeling for Stress Management in Through Silicon Via (TSV) Stacks. AIP Conf. Proc. 2011, 1378, 53–66. [Google Scholar]

- Zhu, Y.; Zhang, J.; Li, H.Y.; Tan, C.S.; Xia, G. Study of Near-Surface Stresses in Silicon Around Through-Silicon Vias at Elevated Temperatures by Raman Spectroscopy and Simulations. IEEE Trans. Device Mater. Reliab. 2015, 15, 142–148. [Google Scholar] [CrossRef]

- Saettler, P.; Hecker, M.; Boettcher, M.; Rudolph, C.; Wolter, K.J. μ-Raman Spectroscopy and FE-Modeling for TSV-Stress-Characterization. Microelectron. Eng. 2015, 137, 105–110. [Google Scholar] [CrossRef]

- Okoro, C.; Levine, L.E.; Xu, R.; Hummler, K.; Obeng, Y.S. Nondestructive Measurement of the Residual Stresses in Copper Through-Silicon Vias Using Synchrotron-Based Microbeam X-ray Diffraction. IEEE Trans. Electron Devices. 2014, 61, 2473–2479. [Google Scholar]

- Song, Y.; Abbaspour, R.; Bakir, M.S.; Sitaraman, S.K. Thermal Annealing Effects on Copper Microstructure in Through—Silicon-Vias. In Proceedings of the IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Las Vegas, NV, USA, 31 May–3 June 2016. [Google Scholar]

- Mercha, A.; Van der Plas, G.; Moroz, V.; Wolf, I.D.; Asimakopoulos, P.; Minas, N.; Domae, S.; Perry, D.; Choi, M.; Redolfi, A.; et al. Comprehensive Analysis of the Impact of Single and Arrays of Through Silicon Vias Induced Stress on High-k/Metal Gate CMOS Performance. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010. [Google Scholar]

- Okoro, C.; Yang, Y.; Vandevelde, B.; Swinnen, B.; Vandepitte, D.; Verlinden, B.; Wolf, I.D. Extraction of the Appropriate Material Property for Realistic Modeling of Through-Silicon-Vias using µ-Raman Spectroscopy. In Proceedings of the International Interconnect Technology Conference, Burlingame, CA, USA, 1–4 June 2008. [Google Scholar]

- Jung, M.; Pan, D.Z.; Lim, S.K. Through-Silicon-Via Material Property Variation Impact on Full-Chip Reliability and Timing. In Proceedings of the IEEE International Interconnect Technology Conference, San Jose, CA, USA, 20–23 May 2014. [Google Scholar]

- Okoro, C.; Levine, L.E.; Xu, R.; Obeng, Y.S. Experimentally, How Does Cu TSV Diameter Influence its Stress State? In Proceedings of the IEEE Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2015. [Google Scholar]

- Budiman, A.; Shin, H.A.S.; Kim, B.J.; Hwang, S.H.; Son, H.Y.; Suh, M.S.; Chung, Q.H.; Byun, K.Y.; Tamura, N.; Kunz, M. Measurement of Stresses in Cu and Si around Through-Silicon Via by Synchrotron X-ray Microdiffraction for 3-Dimensional Integrated Circuits. Microelectron. Reliab. 2012, 52, 530–533. [Google Scholar] [CrossRef]

- Wolf, I.D.; Croes, K.; Pedreira, O.V.; Labie, R.; Redolfi, A.; Van De Peer, M.; Vanstreels, K.; Okoro, C.; Vandevelde, B.; Beynea, E. Cu Pumping in TSVs: Effect of Pre-CMP Thermal Budget. Microelectron. Reliab. 2011, 51, 1856–1859. [Google Scholar] [CrossRef]

- Lee, C.C.; Huang, C.C. Induced Thermo-Mechanical Reliability of Copper-Flled TSV Interposer by Transient Selective Annealing Technology. Microelectron. Reliab. 2015, 55, 2213–2219. [Google Scholar] [CrossRef]

- Pan, Y.; Li, F.; He, H.; Li, J.; Zhu, W. Effects of Dimension Parameters and Defect on TSV Thermal Behavior for 3D IC packaging. Microelectron. Reliab. 2017, 70, 97–102. [Google Scholar] [CrossRef]

- Jung, M.; Mitra, J.; Pan, D.Z.; Lim, S.K. TSV Stress-Aware Full-Chip Mechanical Reliability Analysis and Optimization for 3D IC. Commun. ACM 2014, 57, 107–115. [Google Scholar] [CrossRef]

- Che, F.X.; Xie, L.; Chen, Z.H.; Wickramanayaka, S. Study on Warpage and Stress of TSV Wafer with Ultra-Fine Pitch Vias for High Density Chip Stacking. In Proceedings of the IEEE Electronics Packaging Technology Conference, Singapore, 6–9 December 2017. [Google Scholar]

- Feng, W.; Bui, T.T.; Watanabe, N.; Shimamoto, H.; Aoyagi, M.; Kikuchi, K. Fabrication and stress analysis of annular-trench-isolated TSV. Microelectron. Reliab. 2016, 63, 142–147. [Google Scholar] [CrossRef]

- Feng, W.; Watanabe, N.; Shimamoto, H.; Kikuchi, K.; Aoyagi, M. Methods to Reduce Thermal Stress for TSV Scaling ~TSV with Novel Structure: Annular-Trench-Isolated TSV. In Proceedings of the IEEE Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2015. [Google Scholar]

- Li, Z.; Tian, Y.; Teng, C.; Cao, H. Recent Advances in Barrier Layer of Cu Interconnects. Materials 2020, 13, 5049. [Google Scholar] [CrossRef]

- Lee, K.W.; Wang, H.; Bea, J.C.; Murugesan, M.; Sutou, Y.; Fukushima, T.; Tanaka, T.; Koike, J.; Koyanagi, M. Barrier Properties of CVD Mn Oxide Layer to Cu Diffusion for 3-D TSV. IEEE Electron Device Lett. 2014, 35, 114–116. [Google Scholar] [CrossRef]

- Lee, K.W.; Nagai, C.; Nakamura, A.; Bea, J.C.; Murugesan, M.; Fukushima, T.; Tanaka, T.; Koyanagi, M. Effects of Electro-less Ni Layer as Barrier/Seed Layers for High Reliable and Low Cost Cu TSV. In Proceedings of the International 3D Systems Integration Conference, Kinsdale, Ireland, 1–3 December 2014. [Google Scholar]

- Li, F.; He, H.; Tian, Q.; Xiao, C.; Li, J.; Zhu, W. A Measurement Method on Nanoscale Thickness of the Ti Barrier Layer of TSV Structure for 3-D IC. IEEE Trans. Compon. Pack. Manuf. Technol. 2016, 6, 954–958. [Google Scholar] [CrossRef]

- Djomeni, L.; Mourier, T.; Minoret, S.; Fadloun, S.; Piallat, F.; Burgess, S.; Price, A.; Zhou, Y.; Jones, C.; Mathiot, D.; et al. Study of Low Temperature MOCVD Deposition of TiN Barrier Layer for Copper Diffusion in High Aspect Ratio Through Silicon Vias. Microelectron. Eng. 2014, 120, 127–132. [Google Scholar] [CrossRef]

- Battegay, F.; Fourel, M. Barrier Material Selection for TSV Last, Flipchip & 3D—UBM & RDL Integrations. In Proceedings of the IEEE Electronic Components and Technology Conference, San Diego, CA, USA, 26–l29 May 2015. [Google Scholar]

- Zare, Y.; Sasajima, Y.; Onuki, J. Evaluation of Cu-TSV Barrier Materials as a Solution to Copper Protrusion. J. Electron. Mater. 2020, 49, 2076–2085. [Google Scholar] [CrossRef]

- Tsai, M.Y.; Huang, P.S.; Huang, C.Y.; Jao, H.; Huang, B.; Wu, B.; Lin, Y.Y.; Liao, W.; Huang, J.; Huang, L.; et al. Investigation on Cu TSV-Induced KOZ in Silicon Chips: Simulations and Experiments. IEEE Trans. Electron Devices. 2013, 60, 2331–2337. [Google Scholar] [CrossRef]

- Wolf, M.J.; Dretschkow, T.; Wunderle, B.; Jürgensen, N.; Engelmann, G.; Ehrmann, O.; Uhlig, A.; Michel, B.; Reichl, H. High Aspect Ratio TSV Copper Filling with Different Seed Layers. In Proceedings of the IEEE Electronic Components and Technology Conference, Lake Buena Vista, FL, USA, 27–30 May 2008. [Google Scholar]

- Lu, K.H.; Zhang, X.; Ryu, S.K.; Im, J.; Huang, R.; Ho, P.S. Thermo-Mechanical Reliability of 3-D ICs containing Through Silicon Vias. In Proceedings of the IEEE Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009. [Google Scholar]

- Ryu, S.K.; Lu, K.H.; Zhang, X.; Im, J.H.; Ho, P.S.; Huang, R. Impact of Near-Surface Thermal Stresses on Interfacial Reliability of Through-Silicon Vias for 3-D Interconnects. IEEE Trans. Device Mater. Reliab. 2011, 11, 35–43. [Google Scholar] [CrossRef]

- Chiang, K.N.; Chang, C.H.; Peng, C.T. Local-Strain Effects in Si/SiGe/Si Islands on Oxide. Appl. Phys. Lett. 2005, 87, 191901. [Google Scholar] [CrossRef]

- Lee, C.C.; Huang, P.C.; Lin, Y.C. Analytical Model Developed for Precise Stress Estimation of Device Channel Within Advanced Planar MOSFET Architectures. IEEE Trans. Electron Devices 2020, 67, 1498–1505. [Google Scholar] [CrossRef]

- Lee, C.C.; Huang, P.C. Layout Study of Strained Ge-Based PMOSFETs Integrated with S/D GeSn Alloy and CESL by Using Process-Oriented Stress Simulations. IEEE Trans. Electron Devices 2018, 65, 4975–4981. [Google Scholar] [CrossRef]

| Model | Components | E, GPa | ν | α, ppm/K |

|---|---|---|---|---|

| Global TSV interposer | TSV (Cu) | 117 | 0.30 | 16.7 |

| Barrier (TaN) | 186 | 0.342 | 6.48 | |

| Interposer (Si) | 169 | 0.26 | 2.3 | |

| STI (SiO2) | 71.7 | 0.16 | 0.51 | |

| Local transistor device | Gate (Poly-Si) | 160 | 0.22 | 2.3 |

| Liner (SiO2) | 71.7 | 0.16 | 0.51 | |

| Spacer (SiN) | 123.3 | 0.30 | 3.05 | |

| S/D (Si0.75Ge0.25) | 161 | 0.265 | 3.2 | |

| Substrate (Si) | 169 | 0.26 | 2.3 | |

| STI (SiO2) | 71.7 | 0.16 | 0.51 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, P.-C.; Lee, C.-C. Stress Impact of the Annealing Procedure of Cu-Filled TSV Packaging on the Performance of Nano-Scaled MOSFETs Evaluated by an Analytical Solution and FEA-Based Submodeling Technique. Materials 2021, 14, 5226. https://doi.org/10.3390/ma14185226

Huang P-C, Lee C-C. Stress Impact of the Annealing Procedure of Cu-Filled TSV Packaging on the Performance of Nano-Scaled MOSFETs Evaluated by an Analytical Solution and FEA-Based Submodeling Technique. Materials. 2021; 14(18):5226. https://doi.org/10.3390/ma14185226

Chicago/Turabian StyleHuang, Pei-Chen, and Chang-Chun Lee. 2021. "Stress Impact of the Annealing Procedure of Cu-Filled TSV Packaging on the Performance of Nano-Scaled MOSFETs Evaluated by an Analytical Solution and FEA-Based Submodeling Technique" Materials 14, no. 18: 5226. https://doi.org/10.3390/ma14185226

APA StyleHuang, P.-C., & Lee, C.-C. (2021). Stress Impact of the Annealing Procedure of Cu-Filled TSV Packaging on the Performance of Nano-Scaled MOSFETs Evaluated by an Analytical Solution and FEA-Based Submodeling Technique. Materials, 14(18), 5226. https://doi.org/10.3390/ma14185226