Abstract

In this paper, the short-circuit robustness of 1200 V silicon carbide (SiC) trench MOSFETs with different gate structures has been investigated. The MOSFETs exhibited different failure modes under different DC bus voltages. For double trench SiC MOSFETs, failure modes are gate failure at lower dc bus voltages and thermal runaway at higher dc bus voltages, while failure modes for asymmetric trench SiC MOSFETs are soft failure and thermal runaway, respectively. The shortcircuit withstanding time (SCWT) of the asymmetric trench MOSFET is higher than that of the double trench MOSFETs. The thermal and mechanical stresses inside the devices during the short-circuit tests have been simulated to probe into the failure mechanisms and reveal the impact of the device structures on the device reliability. Finally, post-failure analysis has been carried out to verify the root causes of the device failure.

1. Introduction

Over the past few decades, wide-bandgap semiconductors like SiC have become more attractive compared to traditional silicon devices due to their high breakdown field, high thermal conductivity, and wide bandgap [1,2]. By now, iC devices such as Schottky diodes have been rapidly developed and are widely used commercially [3,4]. However, the short-circuit performance of SiC MOSFETs is still poor compared to Si-IGBTs. Due to their smaller area and higher power density, SiC MOSFETs have higher junction temperatures than Si-IGBTs and tend to suffer from thermal runaway [5,6,7,8]. In addition, the poor interface state problem of SiC MOSFETs can also lead to gate reliability issues, causing the device gate failure [9,10].

As SiC material growth and device fabrication technologies have evolved, the structure of SiC MOSFETs has become increasingly sophisticated. Today, various commercial SiC MOSFETs with planar and trench gate structures from different manufacturers are available [11,12]. Compared to SiC planar gate MOSFETs, trench gate MOSFETs have higher power density and lower conduction resistance [13]. Although SiC trench MOSFETs have many advantages, their reliability needs further research due to the defects introduced during manufacturing process [14]. First, the inhomogeneity of oxidation during gate formation makes the oxide thickness at the sidewall and trench bottom inconsistent. The oxidation inconsistency increases the SiO/SiC surface roughness, and leads to local electric field concentration at the rough point. Hence, more charges are injected into the gate oxide, increases the charge through the gate oxide, shortening the time to dielectric breakdown [15,16]. Otherwise, threading dislocations (threading screw dislocations (TSDs) and threading edge dislocations (TEDs)) can cause significant leakage points in the device, which can severely degrade the performance of the SiC device [17,18]. The second issue is the infamous interface state problem. In addition, SiC devices tend to be operated under high voltage conditions, which makes the gate oxide layer bear a high electric field. In response, different shielding methods have been proposed, such as double trench MOSFETs (DT-MOSFETs) and asymmetric trench MOSFETs (AT-MOSFETs) [19,20]. The short-circuit failure modes of DT-MOSFETs have been reported in some detail [21,22], while the short-circuit reliability of AT-MOSFETs has been less studied. A comparison of the two devices’ short-circuit reliability has been reported [23], but it focuses more on the safe operating region and failure prediction regarding the device failure mode. The difference in the internal thermal and mechanical stress during the short-circuit process related to the difference in device structures has not been addressed.

In this paper, the short-circuit ruggedness of two 1200 V SiC trench MOSFETs with different gate oxide shielding methods (double-trench and asymmetric-trench) has been investigated. The device characteristics were recorded and analyzed. The maximum short-circuit withstand time (SCWT) of the devices have been measured and compared. To delve into the failure mechanism, the short-circuit process of the devices has been simulated by using a two-dimensional finite element numerical simulation tool. The distribution of currents, lattice temperatures, and mechanical stresses inside the devices were investigated in detail. Finally, the failure was determined by using a failure analysis tool.

2. Device Structure and Experiment Setup

2.1. Device Structure

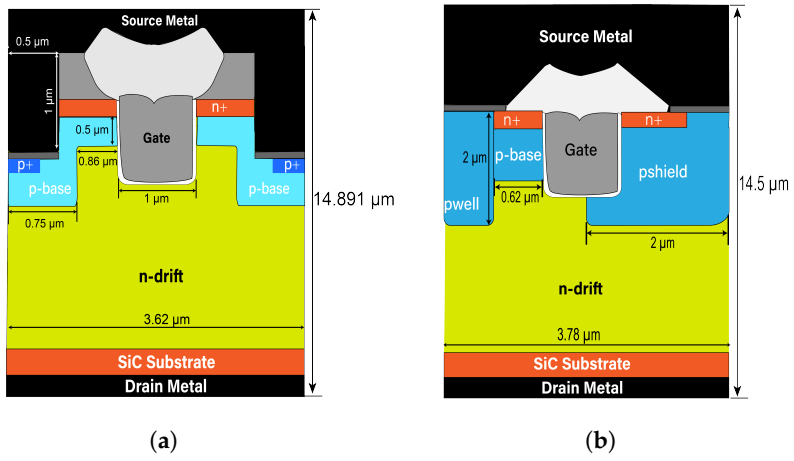

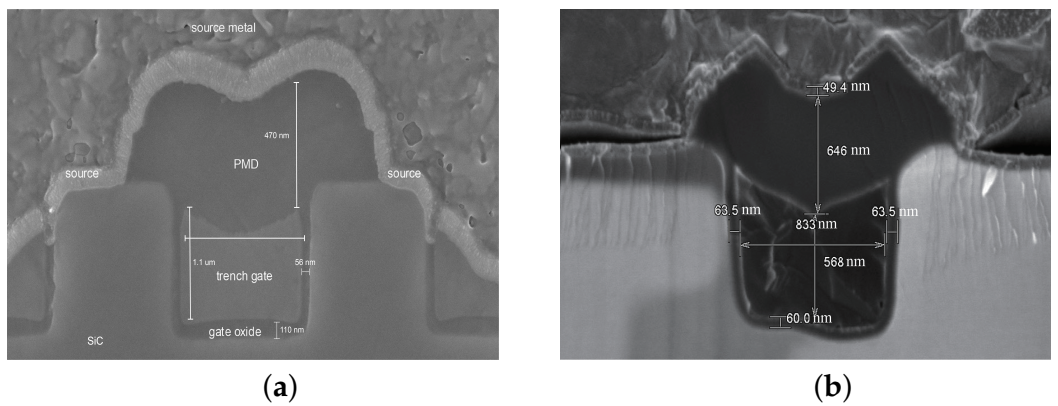

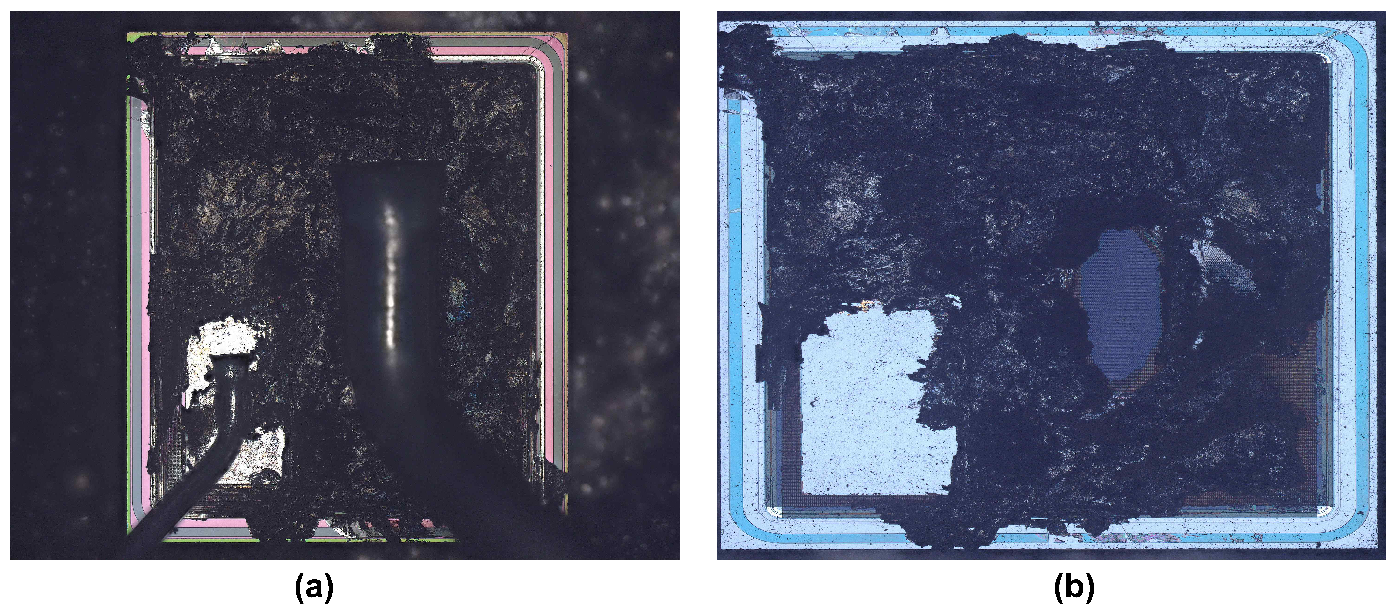

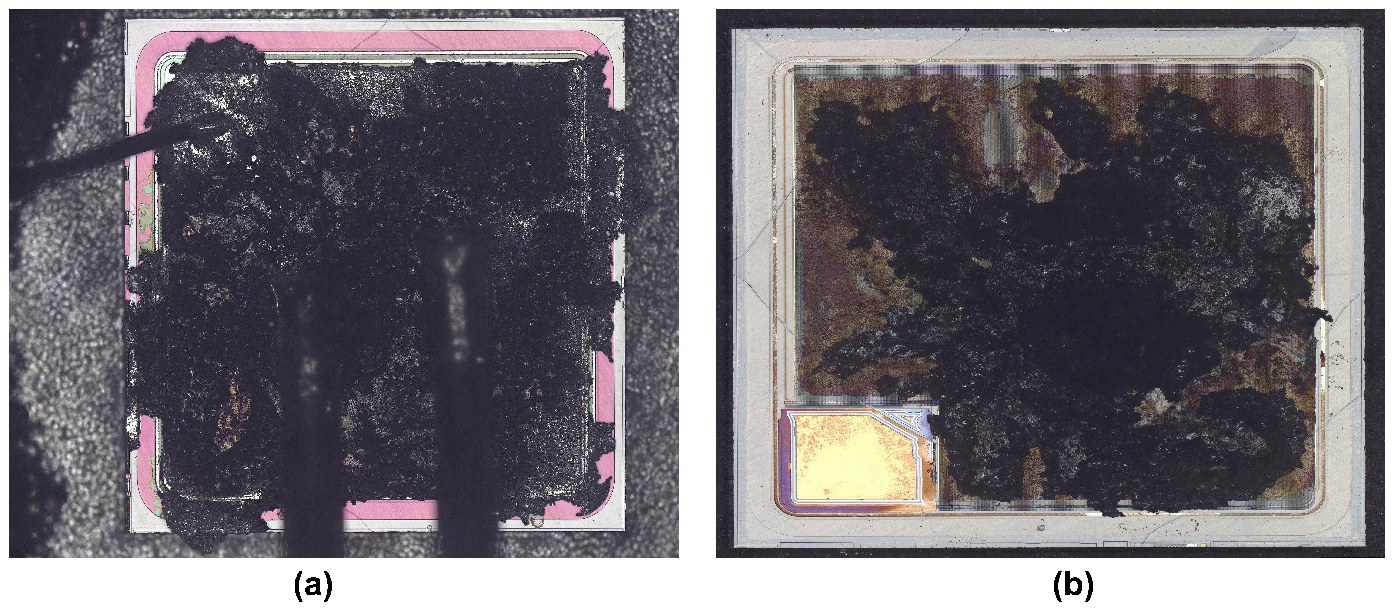

The short-circuit reliability of two 1200 V SiC commercial power trench MOSFETs manufactured by Rohm and Infineon, respectively, have been chosen as the devices under test (DUTs) [24,25]. The main electrical parameters of the devices have been listed in Table 1. Figure 1 shows the cell structure of two devices. The structure parameters of the devices have been obtained by SEM and FIB, as shown in Figure 2. The doping concentrations of the device have been obtained by fitting the device characteristics (transfer curve, output curve, breakdown voltage, etc.) by the numerical simulation.

Table 1.

Device rated parameters.

Figure 1.

Cross-section images of the two trench MOSFETs. (a) DT-MOSFET. (b) AT-MOSFET.

Figure 2.

Cross-section images of the two trench MOSFETs by FIB and SEM. (a) DT-MOSFET. (b) AT-MOSFET.

2.2. Experiment Setup

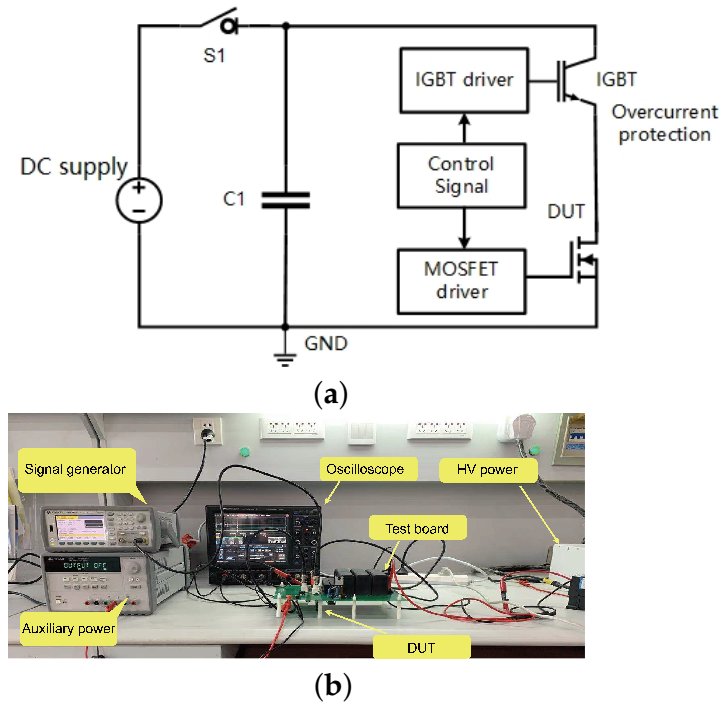

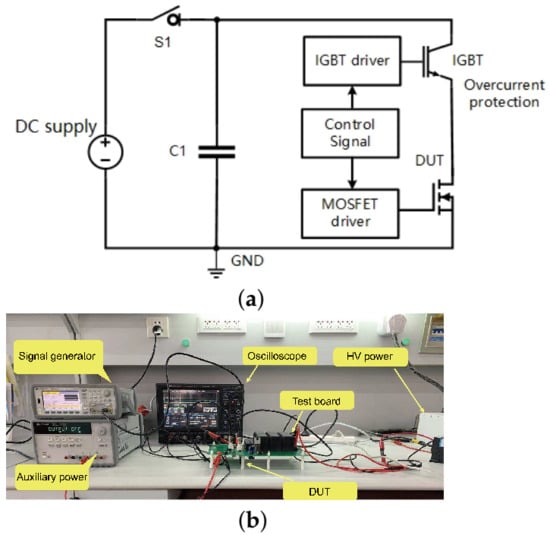

Figure 3 shows the short-circuit test circuit schematic diagram and the photograph of the test platform. To provide sufficient energy during the short-circuit, C1 consisted of six 50 F/1200 V capacitors [26]. In order to avoid device catastrophic failure, an IGBT [27] was employed as the solid-state circuit breaker. Initially, both the IGBT and the DUT were kept off. At first, S1 was turned on and the capacitor C1 was charged to a high voltage via a DC power supply. Afterwards, S1 was turned off and the short-circuit stress was applied to the DUT. The short-circuit pulse width was varied by controlling the gate signals of the IGBT and the DUT. The short-circuit capability of the device can be quantified by the short-circuit withstand time (SCWT), reflecting the maximum short-circuit time that the device can tolerate. After every single test, the device was cooled down to room temperature before the next test started to prevent the heat accumulation inside the devices.

Figure 3.

Circuit schematic diagram: (a) Simplified schematic of the short-circuit test. (b) Photograph of the test platform.

3. Experiment Results

3.1. DT-MOSFET

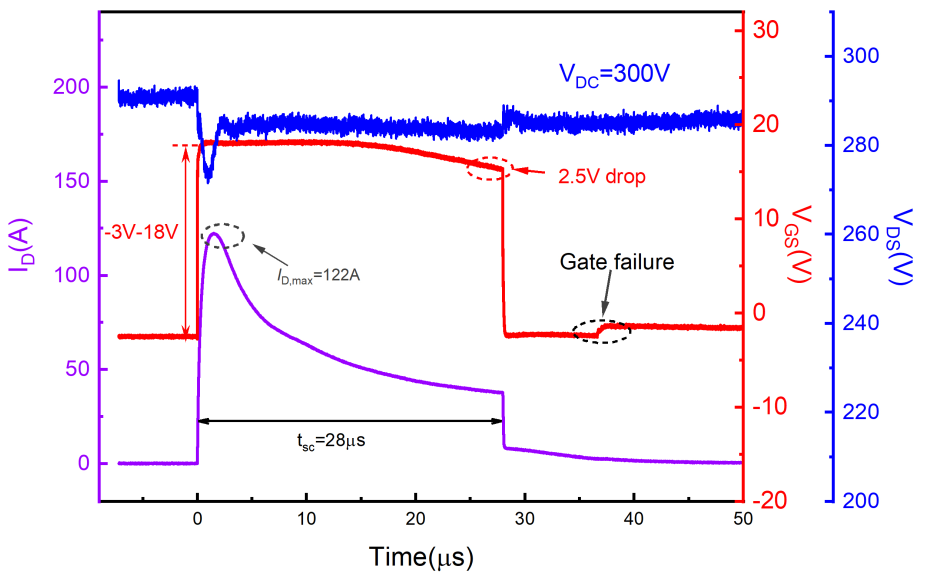

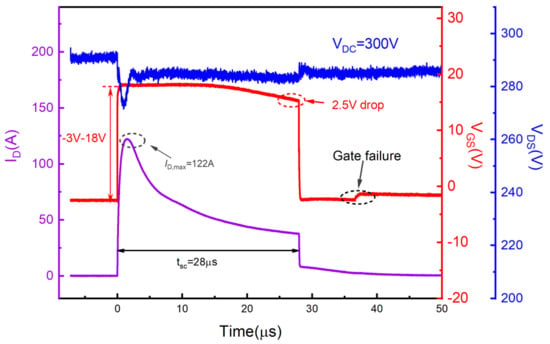

Figure 4 shows typical experimental short-circuit waveforms of SiC DT-MOSFETs with V = 300 V and V = 18 V/−3 V. When the device is turned on, internal parasitic parameters of the device and the test board cause a brief overshoot on V and V. However, this overshoot does not affect the following short-circuit process [28]. The short circuit pulse width was gradually increased to 28 s until the device reached the failure point, accompanied by a peak current value of 125 A and a V drop of 2.5 V. The anomaly only showed on the gate voltage waveform, manifested as a sudden increase of V (from −3 V to 0 V) after the device has been turned off for 7 s, whereby the drain-source voltage still maintained to DC bus voltage. This means that the gate and source terminals are shorted, while the drain-source body diode still has blocking capability. The measured waveforms indicate the gate failure mode [10,29,30]. The same result was demonstrated in the subsequent electrical inspection of the three terminals, as shown in Table 2.

Figure 4.

Short-circuit failure waveforms for the SiC DT-MOSFETs at 300 V DC bus voltage.

Table 2.

DT-MOSFET: Measured resistances between electrodes before and after tests.

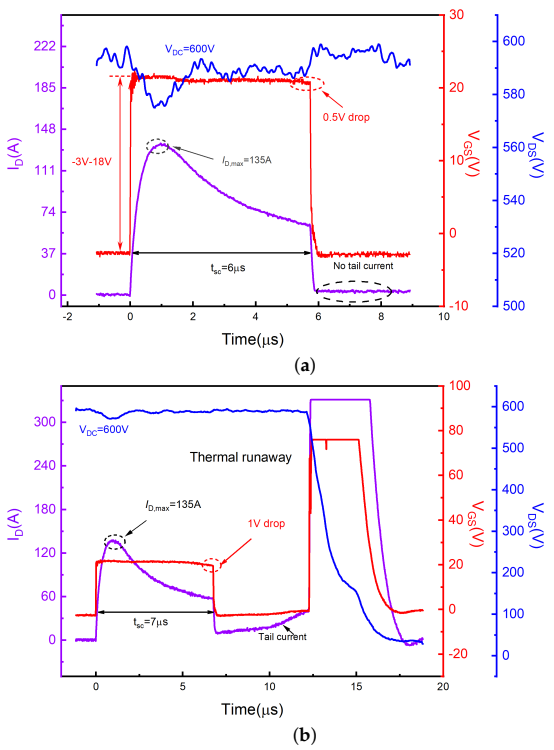

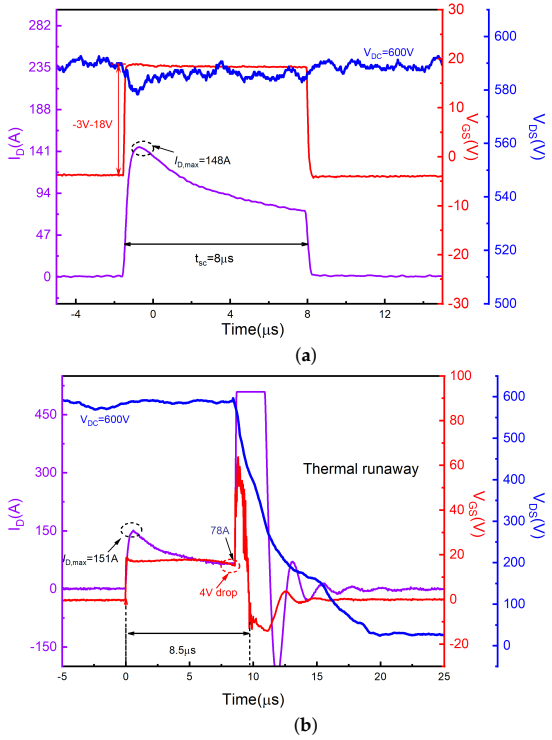

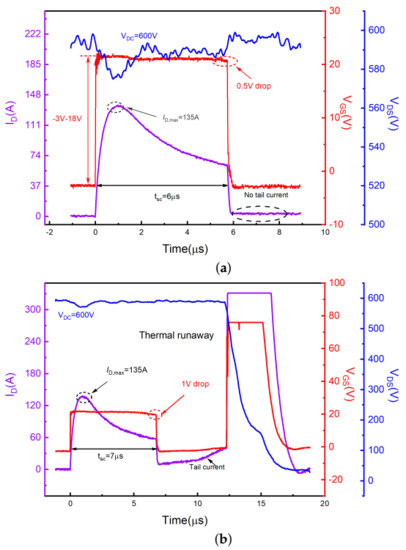

Figure 5 shows the short-circuit waveforms of SiC DT-MOSFETs measured before the failure (a) and at the failure (b), when increasing the bus voltage to 600 V. Higher DC bus voltage leads to higher power dissipation, causing the SCWT to decrease to 7 s. When the device fails, the peak current value is about 135 A, accompanied by the V drop of about 1 V. It can be seen from Figure 5b that a significant trail current appears after the device is turned off, climbing up to 39 A. High junction temperature caused by high power consumption can significantly increase the carrier density. Therefore, the device cannot be completely shut down at the end of short-circuit operation [31]. The hole current is the main cause of tail currents. Due to the existence of the tail current, more heat is generated, forming a positive feedback. If the tail current exceeds the threshold current to trigger the parasitic BJT, the hole density and the junction temperature will increase further and finally lead to thermal runaway [32]. As listed in Table 2, the resistance between the three terminals (R, R, and R) after the short-circuit test became quite low, revealing that all electrodes were shorted.

Figure 5.

Short-circuit waveforms for the SiC DT-MOSFETs at 600 V DC bus voltage. (a) Last waveforms before failure and (b) failure.

3.2. AT-MOSFET

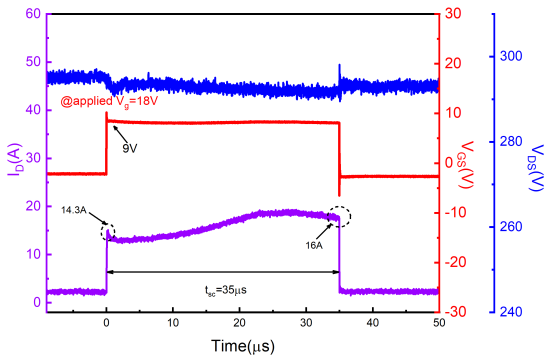

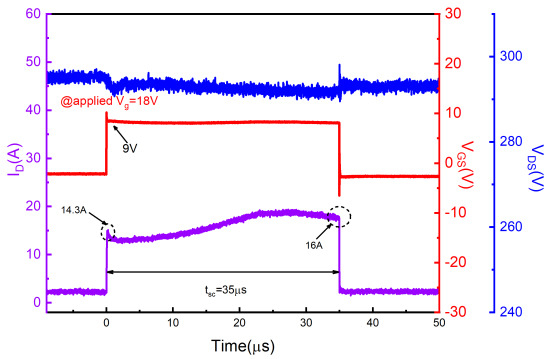

Figure 6 shows typical experimental short-circuit waveforms of SiC AT-MOSFETs at 300 V DC bus voltages, and gate bias was set as V = 18 V/−3 V. Under the same conditions, the SiC AT-MOSFET shows better short-circuit performance than the DT-MOSFET (35 s for AT-MOSFET, 28 s for DT-MOSFET). However, the longer short-circuit time leads to more serious device damage. After withstanding a 35 s short-circuit pulse, the device is no longer able to operate normally. First, the short-circuit current drops to a dozen amps and shows an abnormal upward trend. In addition, the gate voltage is 9 V/−2 V even external 18 V/−3 V is applied. This indicates that a leakage path is formed between the gate and source, but they are not completely shorted, which is referred to as the soft failure. Devices have been previously reported to fail at low bus voltages due to gate-source SiO rupture [33]. Therefore, it can be inferred that the gradual accumulation of dielectric layer damage in AT-MOSFETs under prolonged short-circuit stress may be the root cause of soft failure. The device body diode is still able to carry 300 V. The results of the subsequent electrical inspection of the three terminals are shown in Table 3.

Figure 6.

Short-circuit failure waveforms for the SiC AT-MOSFETs at 300 V DC bus voltage.

Table 3.

AT-MOSFET: Measured resistances between electrodes before and after tests.

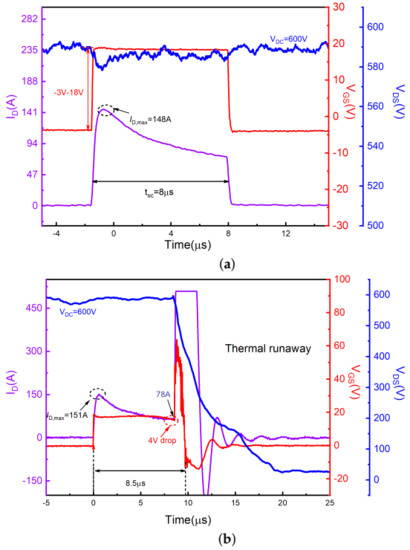

Figure 7 shows short-circuit waveforms of SiC AT-MOSFETs at 600 V DC bus voltages, and gate bias was set as V = 18 V/−3 V. At higher bus voltage, the device is subjected to higher power dissipation and the AT-MOSFET exhibits a thermal runaway mode after a 8.5 s SC pulse. The performance is slightly better than that of DT-MOSFETs, but it is somewhat different from the thermal runaway mode of DT-MOSFETs. First, the thermal runaway of the AT-MOSFETs does not occur after the device is turned off, but during the period when the short-circuit stress is applied. A comparison with the last waveforms measured before failure shows that the current increases during the short-circuit pulse. For example, the drain current increased from 66 A to 78 A at 7 s. This indicates that a trailing current has occurred during the short-circuit pulse. As the junction temperature increases further, the current value is sufficient to trigger the parasitic BJT before the device shuts down. Compared to the DT-MOSFETs, the higher power level of the AT-MOSFET results in a higher peak current than the DT-MOSFETs, making the junction temperature rise faster, thus causing the thermal runaway mode to be triggered before the device is turned off. The second point is that the gate-source voltage of the AT-MOSFETs exhibites anomalies during the short-circuit pulse. There is a gate voltage drop of about 4 V near the point of failure, indicating that a high leakage current is flowing across the gate resistance. This indicates that the gate degradation occurs also. However, the junction temperature rises rapidly due to the higher bus voltage, so that there is not enough time for the gate to be damaged seriously before the thermal runaway occurs. The electrical characteristics in Table 3 also shows that all three terminals of the device are shorted together.

Figure 7.

Short-circuit waveforms for the SiC AT-MOSFETs at 600 V DC bus voltage. (a) Last waveforms measured before failure and (b) at failure.

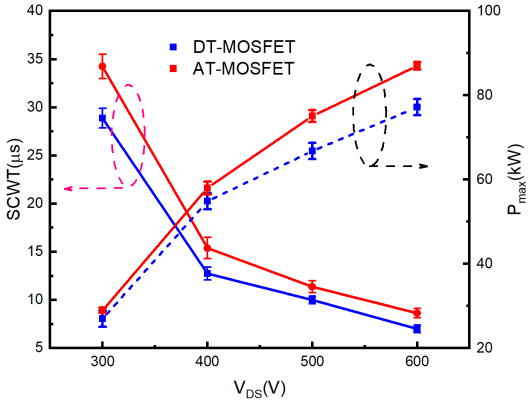

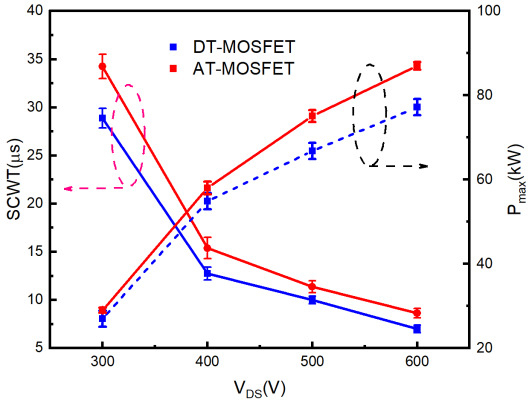

The results of SCWT and extracted comparison between DUTs are shown in Figure 8. The maximum power dissipated in the short-circuit test is higher because the AT-MOSFETs has a higher current rating than the DT-MOSFETs. However, the survival time of DT-MOSFETs at different bus voltages are shorter than that of AT-MOSFETs, which needs further study.

Figure 8.

SCWT and Extracted comparison of different DUTs under different conditions.

4. Failure Mechanism

4.1. Finite Element Numerical Simulation

To investigate the internal behavior of SiC MOSFETs during short-circuit stress and to obtain deep insight into the failure mechanisms, Sentaurus TCAD software was employed to evaluate the electrical-thermal-mechanical stress distribution of these two trench gate structures at room temperature (300 K). The device structure parameters used in the simulations are shown in Table 4.

Table 4.

Device structure parameters.

Some critical dimension parameters are marked in Figure 1.

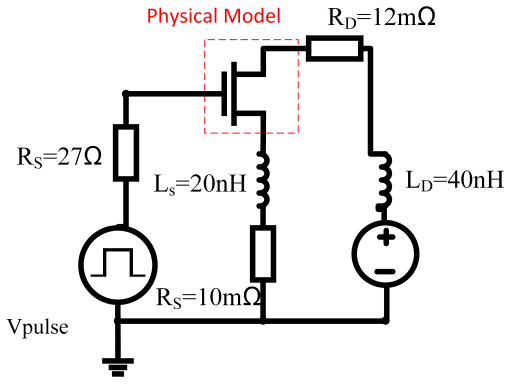

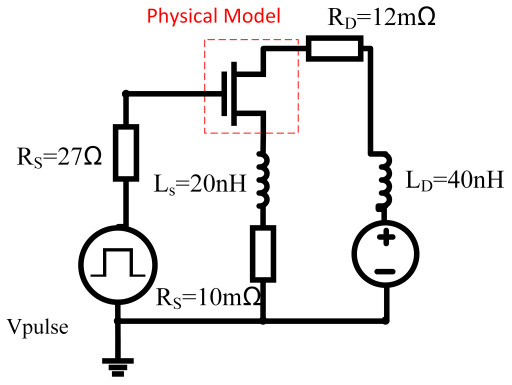

The mixed-mode transient simulations (Sentaurus TCAD) have been performed to study the short-circuit reliability. The test circuit schematic is shown in Figure 9. In the simulation, the characteristics of the MOSFET were solved by finite element numeric analysis, while other components were modeled by Spice electric models. Additional passive elements were included to consider the actual parasitic effects in the circuit. Specifically, the stray inductance and parasitic resistance at the MOSFET source terminal L, R) affect the in the conduction mode, and the stray inductance L at the drain terminal is used to simulate voltage spikes during the switching transients.The values of these parasitic parameters are obtained by simulation fitting the actual switching curve, and the temperature of the substrate was set to be 300 K. Considering the self-heating effect of the device, the junction temperature was solved and updated during the simulations. The short-circuit pulse width is set to be 12 s. At the end of the pulse, the current density and temperature distribution inside the device were extracted to investigate the failure mechanism. Then, the simulated temperature distribution from the electro-thermal simulation was extracted and imported into Sentaurus interconnect [34]. Using the temperature information, the mechanical stress inside the device was calculated.

Figure 9.

The mixed-mode schematic in Sentaurus TCAD.

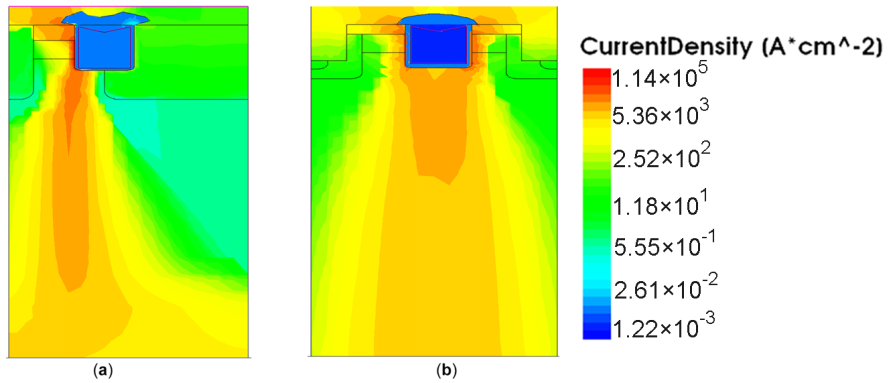

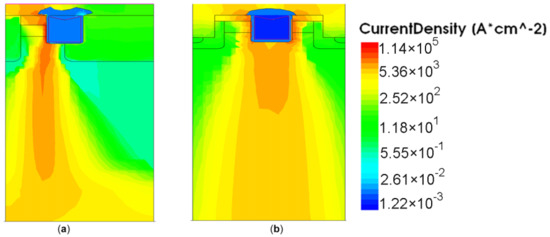

The current density distribution of the DT-MOSFETs and AT-MOSFETs are plotted in Figure 10. As can be seen from Figure 10, because the AT-MOSFET in forward conduction mode only uses half of the channel, the device’s on-state current is more concentrated on one side, while in the DT-MOSFET’s the current is uniformly distributed on both sides. The current distribution between the two structures also results in a difference in temperature distribution. As in the AT-MOSFET a built-in JFET is formed around the trench gate structure of the deep P-Shield, the current density in this JFET region can be effectively reduced. In turn, it causes the current to spread deeper into the device internal region. Since the melting temperature of the electrode metal is much lower than that of SiC, pushing the current away from the metal/SiC interface enables the device to withstand longer short-circuit stress. Therefore, the SCWT of the AT-MOS is still higher than that of the DT-MOS. However, the channel of this JFET is directly controlled by V. Therefore, when V increases, the single-side short-circuit current density at the junction near the P and N increases rapidly, and local self-heating occurs, leading to the triggering of the parasitic transistor and hence early thermal runaway.

Figure 10.

Conduction current density distribution in the device (when the peak junction temperature occurs): (a) DT-MOSFET(b) AT-MOSFET.

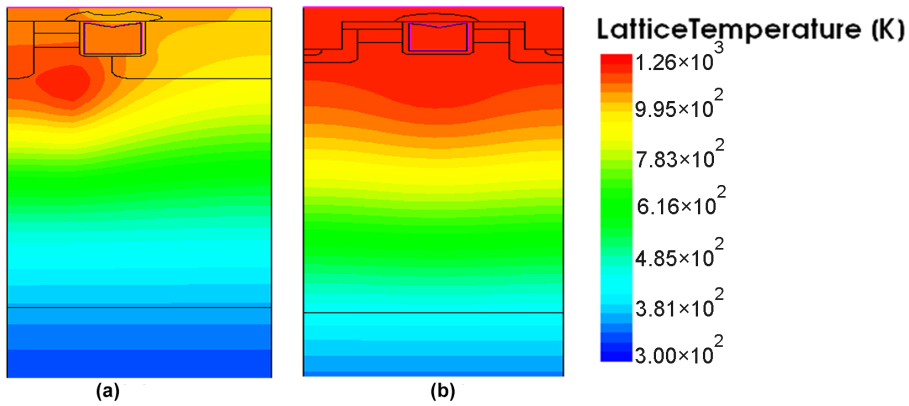

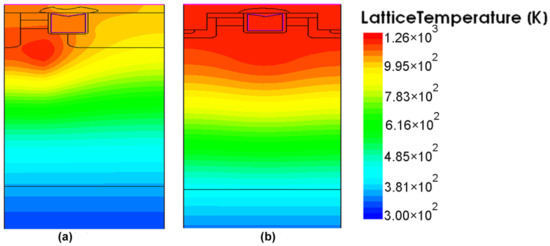

The temperature distribution of the DT-MOSFETs and AT-MOSFETs are shown in Figure 11. For the DT-MOSFET, the current distribution is also symmetrical due to its symmetrical structure, and the temperature drops uniformly from source to drain. The simulated temperatures in the SiC and Al regions are 1371 K and 1382 K, respectively, which already exceed the melting point of Aluminum. For the AT-MOSFET, the temperature is mainly concentrated on one side due to the deep p-region surrounding the gate. Its highest temperature is concentrated in the body region. The aluminum metal near the conduction side is subjectedto a higher temperature than the other side. Likewise, the temperature of the aluminum metal near the on-state side exceeds the melting point of aluminum. Therefore, the melting of the upper aluminum metal may also occur during the short-circuit operation.

Figure 11.

Lattice temperature distribution in the device (when the peak junction temperature occurs): (a) DT-MOSFET (b) AT-MOSFET.

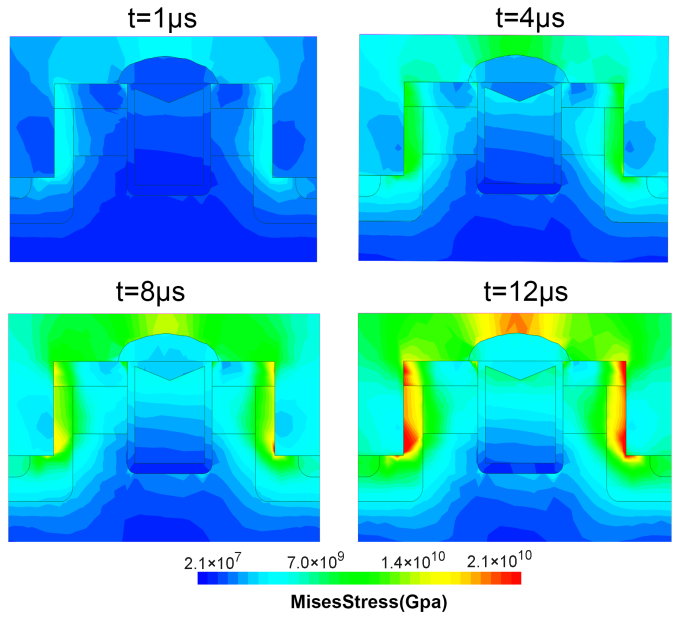

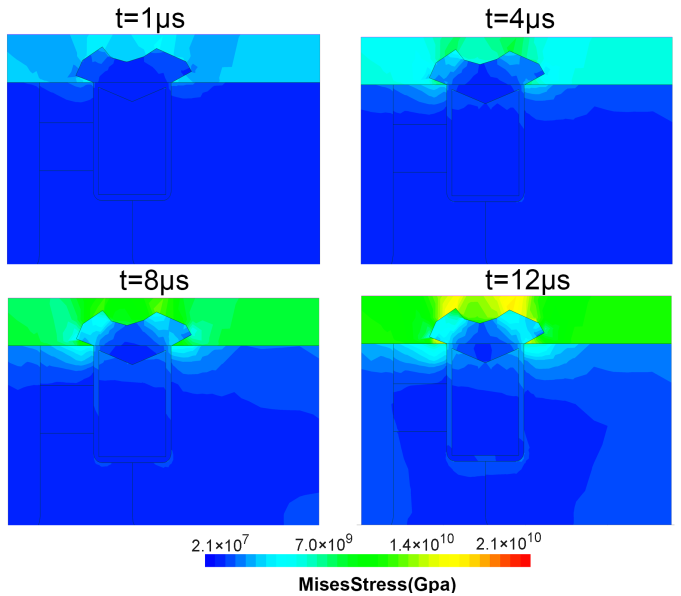

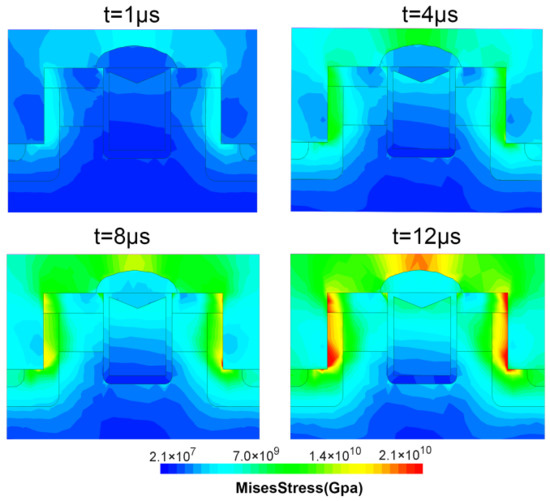

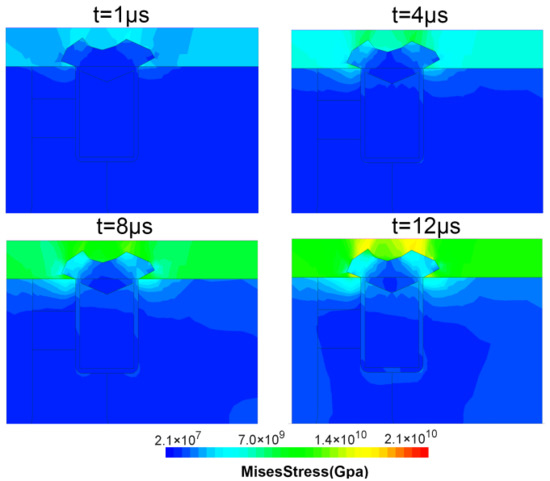

Table 5 shows the melting points and thermal expansion coefficients of the materials used in the MOSFET manufacturing process. Since the thermal expansion of aluminum is more significant than that of SiC and the insulators, large mechanical stresses may be generated at the SiO layer and the Al/SiC interface, which may lead to cracks in these regions [35]. As the junction temperature of the device increases during the short-circuit stress, the temperature gradient increases and the thermal stress inside also increases. As shown in Figure 12, with the increase of short-circuit pulse width, the simulated stress is concentrated in the gate insulation layer and near the source trenchand increases gradually versus time. Finally, the stress in these regions exceeds the materials’ strength, and cracks occur. It is possible that this is the root cause of the gate-source short. In addition, the mechanical stress in the AT-MOSFET is simulated and plotted in Figure 13. Due to the lower temperature distribution in the metal part than in the DT-MOSFET, the mechanical stress in the metal above SiC regions is lower than that of the DT-MOSFETs.

Table 5.

Melting point and thermal expansion coefficient of materials.

Figure 12.

The von Mises stress distribution in the DT-MOSFET during SC condition.

Figure 13.

The von Mises stress distribution in the AT-MOSFET during SC condition.

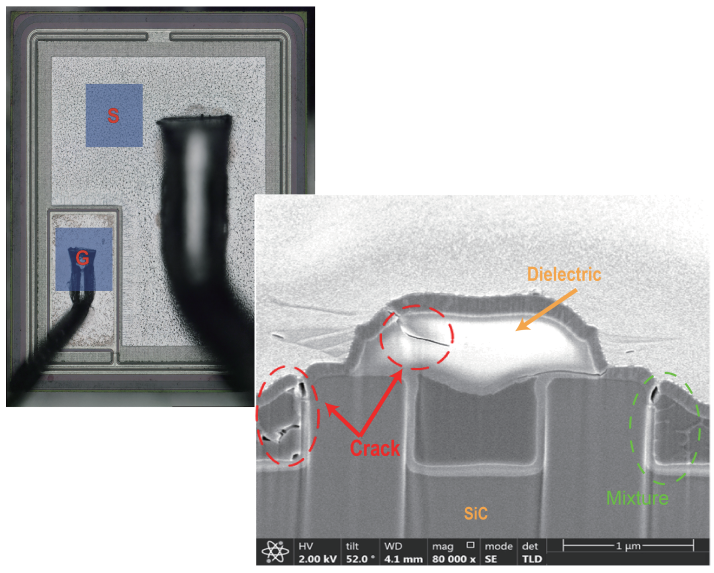

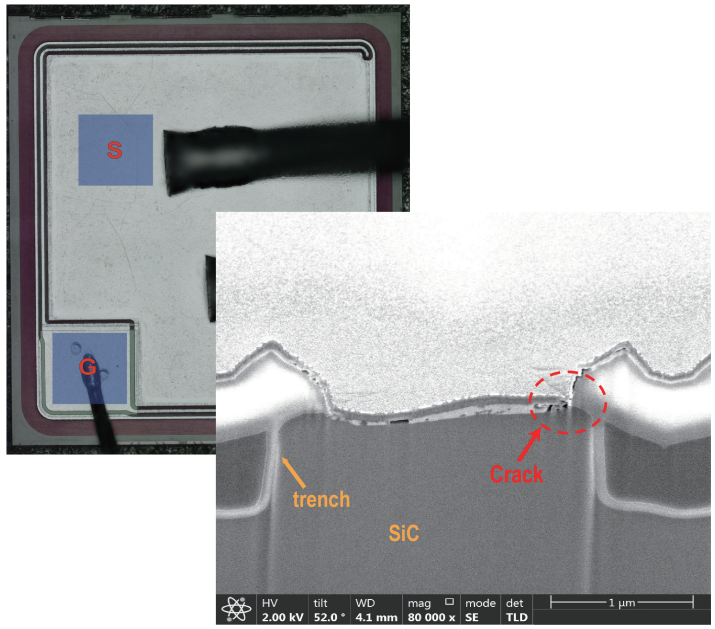

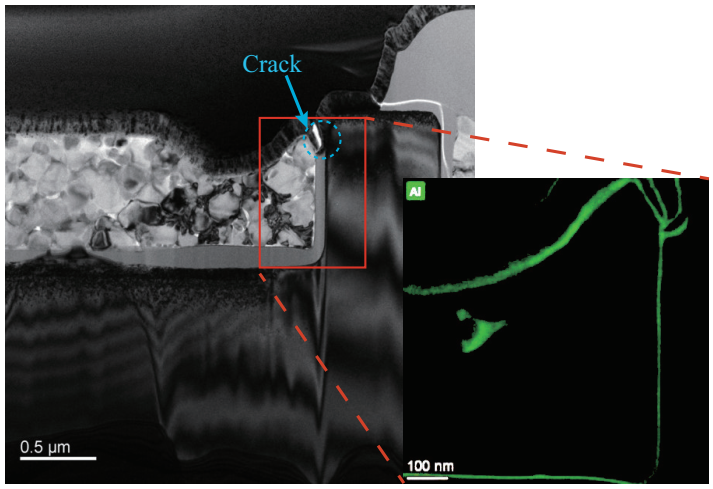

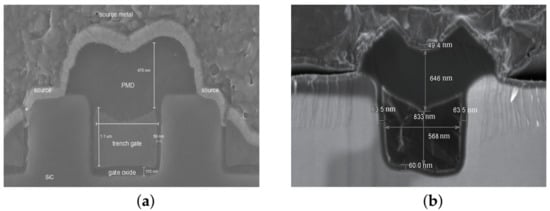

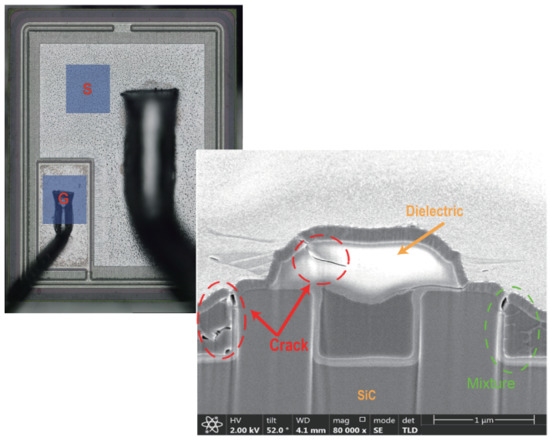

4.2. Post-Failure Analysis

To further investigate the failure mechanisms of the devices and to verify the conclusions drawn by performing device simulations, failure analysis has been carried out on the failed devices. Figure 14 and Figure 15 show the failed DT-MOSFETs and AT-MOSFETs at 300 V bus voltage, respectively. The DT-MOSFET failed due to gate failure and the AT-MOSFET failed due to soft failure. The bonding wires and joints remain intact and no visible damage can be observed on the chip surface. By using focused ion beam (FIB) dicing (based on emission microscopy analysis), the locations of the cracks inside the devices have been identified.

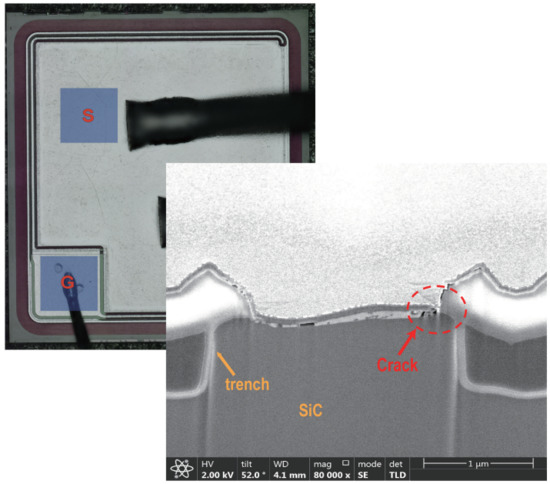

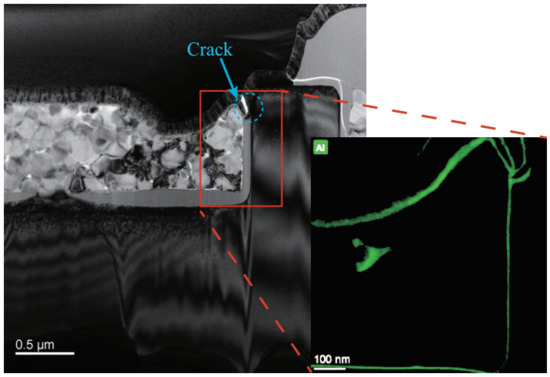

Figure 14.

Cross-sectional SEM image of failed DT-MOSFET cell at 300 V DC voltage. The red dotted circles identify the cracks.

Figure 15.

Cross-sectional SEM image of failed AT-MOSFET cell at 300 V DC voltage. The red dotted circles identify the cracks.

For the DT-MOSFETs, the cracks appear at the corner of the source trench and the pre-Metal dielectric of the gate. In addition, a suspected metal mixture was found in the trench corners. Therefore, the energy- dispersive X-ray spectroscopy (EDX) was employed to analyze the composition of the metal particles, (Figure 16). It was identified as the elemental Aluminum, indicating that the melting of aluminum occurred during the short-circuit operation. Due to the thermal expansion of the materials with the rising temperature, the stress in these regions exceeded the limit of the material and cracks appearred. Next, the melted aluminum flowed into the cracks. Since it took time for Aluminum to fill the cracks, the gate failure occurred within a few microseconds after the device is turned off. For AT-MOSFETs, the damage is less than observed in DT-MOSFETs. The failure point appears in the metal above the channel, while the pre-Metal dielectric of the gate remains intact. Therefore, the AT-MOSFET showed a soft failure, with a large amount of leakage gate current, but was still able to support a part of the applied voltage.

Figure 16.

Atom spectrum analysis after failure. The green part represents the distribution of aluminium.

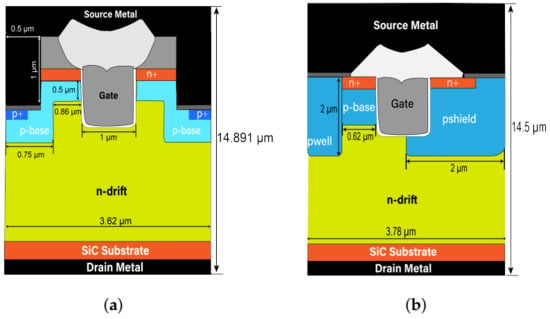

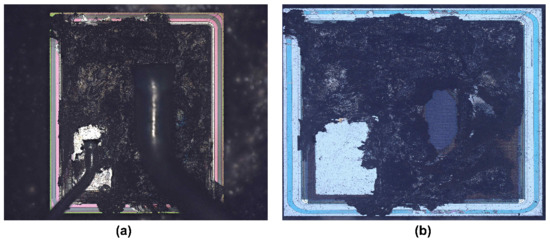

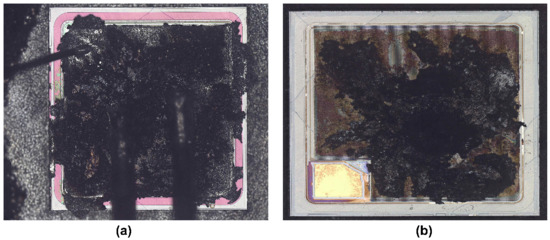

Figure 17 and Figure 18 show the failed DT-MOSFETs and AT-MOSFETs after the 600 V test, respectively. At 600 V, the entire surface has been burned due to the triggering of the parasitic transistors. To further observe the device burn-ins, the device was dissected to the substrate layer. It was found that the burned area was mainly concentrated near the source bonding wires, verifying that the high temperature caused by the high current induced the thermal runaway and catastrophic failure of the device. In addition, the burned area of the AT-MOSFET on the substrate is smaller compared to that of the DT-MOSFET. Since only one side of the AT-MOSFET conducts when it turns on, resulting in localized overheating during the short circuit, as a result, the damage point is more concentrated.

Figure 17.

Images of failed DT-MOSFET at 600 V DC voltage. (a) Surface. (b) Substrate.

Figure 18.

Images of failed AT-MOSFET at 600 V DC voltage. (a) Surface. (b) Substrate.

5. Conclusions

The short-circuit performance of 1200 V SiC trench MOSFETs with asymmetric and double-trench shielding structures has been investigated. Three SiC MOSFET failure mechanisms have been identified: thermal runaway, gate failure, and soft failure modes. The double trench MOSFETs failed with thermal runaway and gate failure modes. For asymmetric trench MOSFETs, the failure modes were thermal runaway and soft failure. The AT-MOSFETs exhibit better short-circuit performance under the same conditions. The numerical simulation results reveal that the deep P-region around the gate in the AT-MOSFETs can effectively limit the short-circuit current, due to the JFET region formed with the adjacent Pbase region. Thus, the current can be distributed more evenly into the device, allowing the maximum temperature to penetrate deeper into the body region, thus preventing the relatively fragile metal and dielectric layers on the surface from exposure to excessive heat. Further numerical simulations have indicated that the mechanical stress is the root cause of gate failure. The post-failure analysis has located cracks in the insulation layer and the source metal. In addition, EDX elemental analysis confirmed the presence of molten aluminum into the cracks, proving the credibility of the simulation results.

Author Contributions

Conceptualization, H.X.; Data curation, Y.Z.; Formal analysis, H.W.; Investigation, Y.Z.; Methodology, Y.Z. and H.X.; Project administration, J.W.; Resources, J.W. and H.W.; Writing—original draft, Y.Z.; Writing—review & editing, J.W. All authors have read and agreed to the published version of the manuscript.

Funding

The authors would like to acknowledge the support from the National Natural Science Foundation of China (Grant no. 51877198).

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

The data presented in this study are available upon request from the corresponding author.

Acknowledgments

Thanks for instrument support from the Technology Innovation and Training Center (Polytechnic Institute, Zhejiang University, Hangzhou, Zhejiang, China).

Conflicts of Interest

The authors declare no conflict of interest.

References

- She, X.; Huang, A.Q.; Lucía, Ó.; Ozpineci, B. Review of silicon carbide power devices and their applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Li, S.; Lu, S.; Mi, C.C. Revolution of Electric Vehicle Charging Technologies Accelerated by Wide Bandgap Devices. Proc. IEEE 2021, 109, 985–1003. [Google Scholar] [CrossRef]

- Kumar, V.; Maan, A.S.; Akhtar, J. Barrier height inhomogeneities induced anomaly in thermal sensitivity of Ni/4H-SiC Schottky diode temperature sensor. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2014, 32, 041203. [Google Scholar] [CrossRef]

- Kumar, V.; Verma, J.; Maan, A.; Akhtar, J. Epitaxial 4H–SiC based Schottky diode temperature sensors in ultra-low current range. Vacuum 2020, 182, 109590. [Google Scholar] [CrossRef]

- Cao, L.; Guo, Q.; Sheng, K. Comparative evaluation of the short circuit capability of SiC planar and trench power MOSFET. In Proceedings of the 2018 IEEE 2nd International Electrical and Energy Conference (CIEEC), Beijing, China, 4–6 November 2018; pp. 653–656. [Google Scholar]

- Cao, L.; Gao, Z.; Guo, Q.; Sheng, K. Experimental Investigations of SiC MOSFETs under Short-Circuit Operations. In Proceedings of the 2019 IEEE 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 227–230. [Google Scholar]

- Wang, Z.; Shi, X.; Tolbert, L.M.; Wang, F.; Liang, Z.; Costinett, D.; Blalock, B.J. Temperature-dependent short-circuit capability of silicon carbide power MOSFETs. IEEE Trans. Power Electron. 2015, 31, 1555–1566. [Google Scholar] [CrossRef]

- Romano, G.; Maresca, L.; Riccio, M.; d’Alessandro, V.; Breglio, G.; Irace, A.; Fayyaz, A.; Castellazzi, A. Short-circuit failure mechanism of SiC power MOSFETs. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 345–348. [Google Scholar]

- Boige, F.; Richardeau, F.; Trémouilles, D.; Lefebvre, S.; Guibaud, G. Investigation on damaged planar-oxide of 1200 V SiC power MOSFETs in non-destructive short-circuit operation. Microelectron. Reliab. 2017, 76, 500–506. [Google Scholar] [CrossRef]

- Liu, J.; Zhang, G.; Wang, B.; Li, W.; Wang, J. Gate failure physics of SiC MOSFETs under short-circuit stress. IEEE Electron Device Lett. 2019, 41, 103–106. [Google Scholar] [CrossRef]

- CREE. Discrete Silicon Carbide MOSFETs. 2011. Available online: https://www.wolfspeed.com/products/power/sic-mosfets (accessed on 4 January 2022).

- Nakamura, R.; Nakano, Y.; Aketa, M.; Noriaki, K.; Ino, K. 1200 V 4H-SiC trench devices. In Proceedings of the PCIM Europe 2014; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 20–22 May 2014; VDE: Nuremberg, Germany, 2014; pp. 1–7. [Google Scholar]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer Science & Business Media: Berlin, Germany, 2008. [Google Scholar]

- Nguyen, T.T.; Ahmed, A.; Thang, T.V.; Park, J.H. Gate Oxide Reliability Issues of SiC MOSFETs Under Short-Circuit Operation. IEEE Trans. Power Electron. 2015, 30, 2445–2455. [Google Scholar] [CrossRef]

- Pappis, D.; Zacharias, P. Failure modes of planar and trench SiC MOSFETs under single and multiple short circuits conditions. In Proceedings of the 2017 IEEE 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; p. P.1. [Google Scholar]

- Kutsuki, K.; Murakami, Y.; Watanabe, Y.; Onishi, T.; Yamamoto, K.; Fujiwara, H.; Ito, T. Effect of surface roughness of trench sidewalls on electrical properties in 4H-SiC trench MOSFETs. Jpn. J. Appl. Phys. 2018, 57, 04FR02. [Google Scholar] [CrossRef] [Green Version]

- Fiorenza, P.; Alessandrino, M.; Carbone, B.; Di Martino, C.; Russo, A.; Saggio, M.; Venuto, C.; Zanetti, E.; Giannazzo, F.; Roccaforte, F. Understanding the role of threading dislocations on 4H-SiC MOSFET breakdown under high temperature reverse bias stress. Nanotechnology 2020, 31, 125203. [Google Scholar] [CrossRef] [PubMed]

- Claeys, C.; Simoen, E.; Put, S.; Giusi, G.; Crupi, F. Impact strain engineering on gate stack quality and reliability. Solid-State Electron. 2008, 52, 1115–1126. [Google Scholar] [CrossRef]

- Nakamura, T.; Nakano, Y.; Aketa, M.; Nakamura, R.; Mitani, S.; Sakairi, H.; Yokotsuji, Y. High performance SiC trench devices with ultra-low ron. In Proceedings of the 2011 IEEE International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 26.5.1–26.5.3. [Google Scholar]

- Peters, D.; Basler, T.; Zippelius, B.; Aichinger, T.; Bergner, W.; Esteve, R.; Kueck, D.; Siemieniec, R. The new CoolSiC™ trench MOSFET technology for low gate oxide stress and high performance. In Proceedings of the PCIM Europe 2017 International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 16–18 May 2017; VDE: Nuremberg, Germany, 2017; pp. 1–7. [Google Scholar]

- Wei, J.; Liu, S.; Tong, J.; Zhang, X.; Sun, W.; Huang, A.Q. Understanding Short-Circuit Failure Mechanism of Double-Trench SiC Power MOSFETs. IEEE Trans. Electron Devices 2020, 67, 5593–5599. [Google Scholar] [CrossRef]

- Namai, M.; An, J.; Yano, H.; Iwamuro, N. Experimental and numerical demonstration and optimized methods for SiC trench MOSFET short-circuit capability. In Proceedings of the 2017 IEEE 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 363–366. [Google Scholar]

- Deng, X.; Li, X.; Li, X.; Zhu, H.; Xu, X.; Wen, Y.; Sun, Y.; Chen, W.; Li, Z.; Zhang, B. Short-Circuit Capability Prediction and Failure Mode of Asymmetric and Double Trench SiC MOSFETs. IEEE Trans. Power Electron. 2020, 36, 8300–8307. [Google Scholar] [CrossRef]

- ROHM. SCT3160KLGC11 Datasheet. 2018. Available online: https://fscdn.rohm.com/en/products/databook/datasheet/discrete/sic/mosfet/sct3160kl-e.pdf (accessed on 12 November 2021).

- Infineon. IMW120R090M1HXKSA1 Datasheet. 2020. Available online: https://www.infineon.com/dgdl/Infineon-IMW120R090M1H-DataSheet-v02_02-EN.pdf (accessed on 12 November 2021).

- Vishay. MKP1848C Datasheet. 2021. Available online: https://www.vishay.com/docs/26015/mkp1848cdclink.pdf (accessed on 4 January 2022).

- Onsemi. FGL40N120AN Datasheet. 2007. Available online: https://www.onsemi.com/products/discrete-power-modules/igbts/fgl40n120an (accessed on 4 January 2022).

- Wang, J.; Jiang, X.; Li, Z.; Shen, Z.J. Short-circuit ruggedness and failure mechanisms of Si/SiC hybrid switch. IEEE Trans. Power Electron. 2018, 34, 2771–2780. [Google Scholar] [CrossRef]

- Sadik, D.P.; Colmenares, J.; Lim, J.K.; Bakowski, M.; Nee, H.P. Comparison of Thermal Stress During Short-Circuit in Different Types of 1.2-kV SiC Transistors Based on Experiments and Simulations. IEEE Trans. Ind. Electron. 2020, 68, 2608–2616. [Google Scholar] [CrossRef]

- Peters, D.; Siemieniec, R.; Aichinger, T.; Basler, T.; Esteve, R.; Bergner, W.; Kueck, D. Performance and ruggedness of 1200V SiC—Trench—MOSFET. In Proceedings of the 2017 IEEE 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 239–242. [Google Scholar]

- Romano, G.; Fayyaz, A.; Riccio, M.; Maresca, L.; Breglio, G.; Castellazzi, A.; Irace, A. A comprehensive study of short-circuit ruggedness of silicon carbide power MOSFETs. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 978–987. [Google Scholar] [CrossRef]

- Riccio, M.; d’Alessandro, V.; Romano, G.; Maresca, L.; Breglio, G.; Irace, A. A temperature-dependent SPICE model of SiC Power MOSFETs for within and out-of-SOA simulations. IEEE Trans. Power Electron. 2017, 33, 8020–8029. [Google Scholar] [CrossRef]

- Okawa, M.; Aiba, R.; Kanamori, T.; Yano, H.; Iwamuro, N.; Harada, S. Experimental and numerical investigations of short-circuit failure mechanisms for state-of-the-art 1.2 kV SiC trench MOSFETs. In Proceedings of the 2019 IEEE 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 167–170. [Google Scholar]

- Sentaurus, T. Manuals; Synopsys Inc.: Mountain View, CA, USA, 2009; Volume 94043. [Google Scholar]

- Yao, K.; Yano, H.; Tadano, H.; Iwamuro, N. Investigations of SiC MOSFET short-circuit failure mechanisms using electrical, thermal, and mechanical stress analyses. IEEE Trans. Electron Devices 2020, 67, 4328–4334. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).