GaN Vertical Transistors with Staircase Channels for High-Voltage Applications

Abstract

1. Introduction

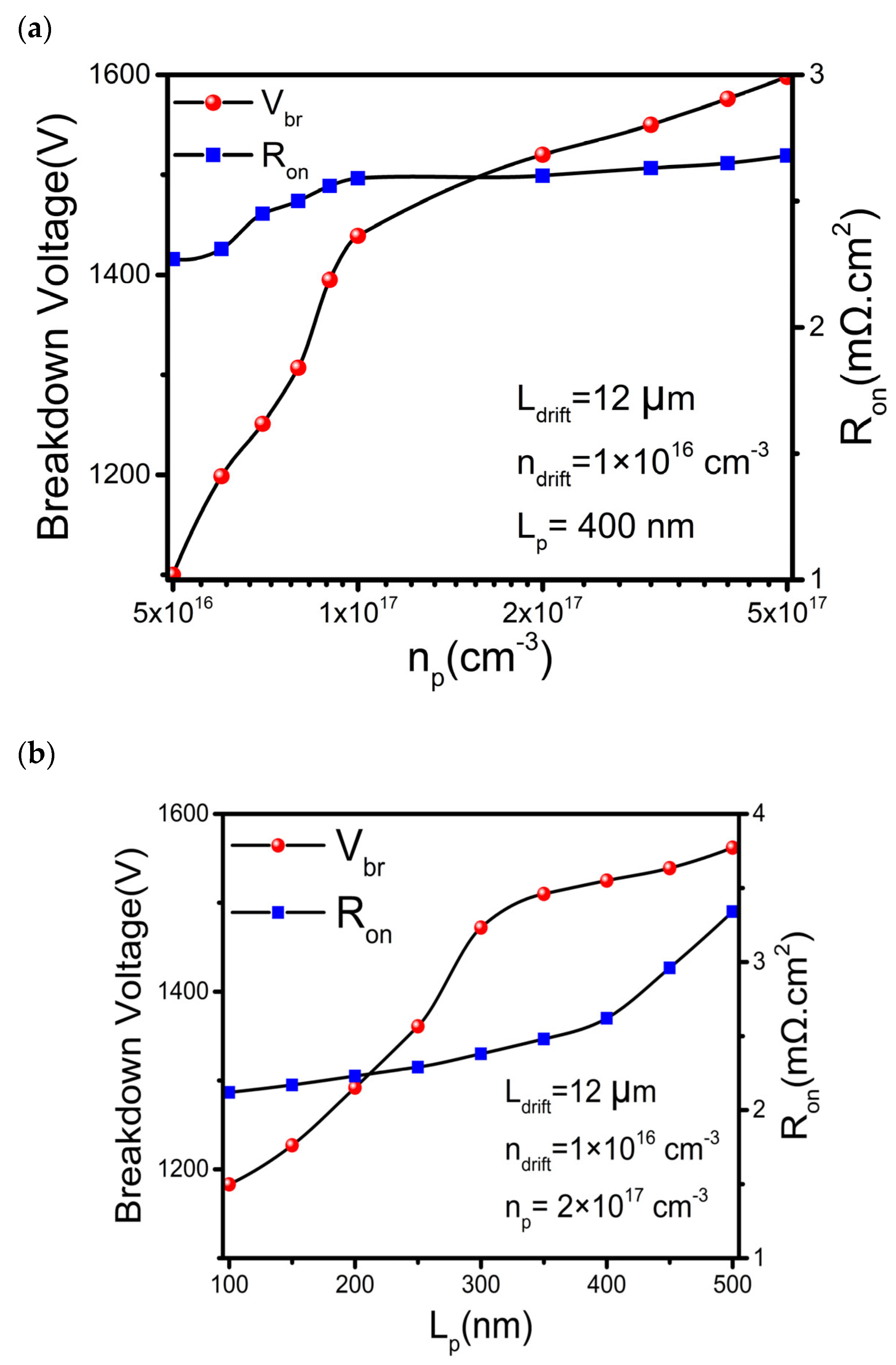

2. Design and Simulation

3. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Abid, I.; Kabouche, R.; Bougerol, C.; Pernot, J.; Masante, C.; Comyn, R.; Cordier, Y.; Medjdoub, F. High Lateral Breakdown Voltage in Thin Channel AlGaN/GaN High Electron Mobility Transistors on AlN/Sapphire Templates. Micromachines 2019, 10, 690. [Google Scholar] [CrossRef]

- Enricoo Zanoni, G.M. Integrated Circuits and Systems Gallium Nitride-Enabled High Frequency and High Efficiency Power Conversion; Springer Nature Publishing: Cham, Switzerland, 2018. [Google Scholar]

- Lee, C.H.; Lin, W.R.; Lee, Y.H.; Huang, J.J. Characterizations of Enhancement-Mode Double Heterostructure GaN HEMTs with Gate Field Plates. IEEE Trans. Electron Devices 2018, 65, 488–492. [Google Scholar] [CrossRef]

- Nela, L.; Erine, C.; Oropallo, M.V.; Matioli, E. Figures-of-Merit of Lateral GaN Power Devices: Modeling and Comparison of HEMTs and PSJs. IEEE J. Electron Devices Soc. 2021, 9, 1066–1075. [Google Scholar] [CrossRef]

- Lin, D.J.; Yang, J.Y.; Chang, C.K.; Huang, J.J. Study of Current Collapse Behaviors of Dual-Gate AlGaN/GaN HEMTs on Si. IEEE J. Electron Devices Soc. 2022, 10, 59–64. [Google Scholar] [CrossRef]

- Amano, H.; Baines, Y.; Beam, E.; Borga, M.; Bouchet, T.; Chalker, P.R.; Charles, M.; Chen, K.J.; Chowdhury, N.; Chu, R.; et al. The 2018 GaN Power Electronics Roadmap. J. Phys. D Appl. Phys. 2018, 51. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, M.; Liu, Z.; Piedra, D.; Lee, H.S.; Gao, F.; Fujishima, T.; Palacios, T. Electrothermal Simulation and Thermal Performance Study of GaN Vertical and Lateral Power Transistors. IEEE Trans. Electron Devices 2013, 60, 2224–2230. [Google Scholar] [CrossRef]

- Ajayan, J.; Nirmal, D.; Mohankumar, P.; Mounika, B.; Bhattacharya, S.; Tayal, S.; Fletcher, A.S.A. Challenges in Material Processing and Reliability Issues in AlGaN/GaN HEMTs on Silicon Wafers for Future RF Power Electronics & Switching Applications: A Critical Review. Mater. Sci. Semicond. Process. 2022, 151, 106982. [Google Scholar]

- Yang, J.X.; Lin, D.J.; Wu, Y.R.; Huang, J.J. Deep Source Metal Trenches in GaN-On-Si HEMTs for Relieving Current Collapse. IEEE J. Electron Devices Soc. 2021, 9, 557–563. [Google Scholar] [CrossRef]

- Kumar Subramani, N.; Couvidat, J.; Al Hajjar, A.; Nallatamby, J.-C.; Sommet, R.; Quéré, R. Identification of GaN Buffer Traps in Microwave Power AlGaN/GaN HEMTs Through Low Frequency S-Parameters Measurements and TCAD-Based Physical Device Simulations. IEEE J. Electron Devices Soc. 2017, 5, 175–181. [Google Scholar] [CrossRef]

- Abdul Khadar, R.M.; Liu, C.; Soleimanzadeh, R.; Matioli, E. Fully Vertical GaN-on-Si Power MOSFETs. IEEE Electron Device Lett. 2019, 40, 443–446. [Google Scholar] [CrossRef]

- Ma, J.; Matioli, E. High Performance Tri-Gate GaN Power MOSHEMTs on Silicon Substrate. IEEE Electron Device Lett. 2017, 38, 367–370. [Google Scholar] [CrossRef]

- Nie, H.; Diduck, Q.; Alvarez, B.; Edwards, A.P.; Kayes, B.M.; Zhang, M.; Ye, G.; Prunty, T.; Bour, D.; Kizilyalli, I.C. 1.5-KV and 2.2-Mω-Cm2 Vertical Gan Transistors on Bulk-GaN Substrates. IEEE Electron Device Lett. 2014, 35, 939–941. [Google Scholar] [CrossRef]

- Liu, S.; Song, X.; Zhang, J.; Zhao, S.; Luo, J.; Zhang, H.; Zhang, Y.; Zhang, W.; Zhou, H.; Liu, Z.; et al. Comprehensive Design of Device Parameters for GaN Vertical Trench MOSFETs. IEEE Access 2020, 8, 57126–57135. [Google Scholar] [CrossRef]

- Ishida, T.; Pil Nam, K.; Matys, M.; Uesugi, T.; Suda, J.; Kachi, T. Improvement of Channel Property of GaN Vertical Trench MOSFET by Compensating Nitrogen Vacancies with Nitrogen Plasma Treatment. Appl. Phys. Express 2020, 13, 124003. [Google Scholar] [CrossRef]

- Ishida, T.; Sakao, K.; Kachi, T.; Suda, J. Impact of Channel Mobility on Design Optimization of 600-3300 V-Class High-Speed GaN Vertical-Trench MOSFETs Based on TCAD Simulation. Appl. Phys. Express 2021, 14. [Google Scholar] [CrossRef]

- Chowdhury, S.; Mishra, U.K. Lateral and Vertical Transistors Using the Algan/GAN Heterostructure. IEEE Trans. Electron Devices 2013, 60, 3060–3066. [Google Scholar] [CrossRef]

- Ji, D.; Laurent, M.A.; Agarwal, A.; Li, W.; Mandal, S.; Keller, S.; Chowdhury, S. Normally off Trench CAVET with Active Mg-Doped GaN as Current Blocking Layer. IEEE Trans. Electron Devices 2017, 64, 805–808. [Google Scholar] [CrossRef]

- He, W.; Li, J.; Liao, Z.; Lin, F.; Wu, J.; Wang, B.; Wang, M.; Liu, N.; Chiu, H.C.; Kuo, H.C.; et al. 1.3 KV Vertical GaN-Based Trench MOSFETs on 4-Inch Free Standing GaN Wafer. Nanoscale Res. Lett. 2022, 17, 14. [Google Scholar] [CrossRef]

- Subramani, N.K.; Couvidat, J.; Hajjar, A.A.; Nallatamby, J.C.; Quéré, R. Low-Frequency Drain Noise Characterization and TCAD Physical Simulations of GaN HEMTs: Identification and Analysis of Physical Location of Traps. IEEE Electron Device Lett. 2018, 39, 107–110. [Google Scholar] [CrossRef]

- Fu, H.; Fu, K.; Yang, C.; Liu, H.; Hatch, K.A.; Peri, P.; Herath Mudiyanselage, D.; Li, B.; Kim, T.H.; Alugubelli, S.R.; et al. Selective Area Regrowth and Doping for Vertical Gallium Nitride Power Devices: Materials Challenges and Recent Progress. Mater. Today 2021, 49, 296–323. [Google Scholar] [CrossRef]

- Koblmuller, G.; Chu, R.M.; Raman, A.; Mishra, U.K.; Speck, J.S. High-Temperature Molecular Beam Epitaxial Growth of AlGaN/GaN on GaN Templates with Reduced Interface Impurity Levels. J. Appl. Phys. 2010, 107, 043527. [Google Scholar] [CrossRef]

- King, S.W.; Barnak, J.P.; Bremser, M.D.; Tracy, K.M.; Ronning, C.; Davis, R.F.; Nemanich, R.J. Cleaning of AlN and GaN Surfaces. J. Appl. Phys. 1998, 84, 5248–5260. [Google Scholar] [CrossRef]

- Li, W.; Nomoto, K.; Lee, K.; Islam, S.; Hu, Z.; Zhu, M.; Gao, X.; Pilla, M.; Jena, D.; Xing, H.G. Development of GaN Vertical Trench-MOSFET with MBE Regrown Channel. IEEE Trans. Electron Devices 2018, 65, 2558–2564. [Google Scholar] [CrossRef]

- Ji, D.; Gupta, C.; Agarwal, A.; Chan, S.H.; Lund, C.; Li, W.; Keller, S.; Mishra, U.K.; Chowdhury, S. Large-Area In-Situ Oxide, GaN Interlayer-Based Vertical Trench MOSFET (OG-FET). IEEE Electron Device Lett. 2018, 39, 711–714. [Google Scholar] [CrossRef]

- Strempel, K.; Römer, F.; Yu, F.; Meneghini, M.; Bakin, A.; Wehmann, H.H.; Witzigmann, B.; Waag, A. Vertical 3D Gallium Nitride Field-Effect Transistors Based on Fin Structures with Inverted p-Doped Channel. Semicond. Sci. Technol. 2020, 36, 014002. [Google Scholar] [CrossRef]

- Sun, M.; Zhang, Y.; Gao, X.; Palacios, T. High-Performance GaN Vertical Fin Power Transistors on Bulk GaN Substrates. IEEE Electron Device Lett. 2017, 38, 509–512. [Google Scholar] [CrossRef]

- Maes, W.; de Meyer, K.; van Overstraeten, R. Impact ionization in silicon: A review and update. Solid-State Electron. 1990, 33, 705–718. [Google Scholar] [CrossRef]

- Grasser, T.; Kosina, H.; Heitzinger, C.; Selberherr, S. Accurate Impact Ionization Model Which Accounts for Hot and Cold Carrier Populations. Appl. Phys. Lett. 2002, 80, 613–615. [Google Scholar] [CrossRef]

- Jin, Y.-K.; Chiang, H.-Y.; Lin, K.-H.; Lee, C.-A.; Huang, J. Luminescence Efficiency Improvement of Small-Size Micro Light-Emitting Diodes by Digital Etching Technology. Opt. Lett. 2022, 47, 6277–6280. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Barman, K.; Lin, D.-J.; Gupta, R.; Chang, C.-K.; Huang, J.-J. GaN Vertical Transistors with Staircase Channels for High-Voltage Applications. Materials 2023, 16, 582. https://doi.org/10.3390/ma16020582

Barman K, Lin D-J, Gupta R, Chang C-K, Huang J-J. GaN Vertical Transistors with Staircase Channels for High-Voltage Applications. Materials. 2023; 16(2):582. https://doi.org/10.3390/ma16020582

Chicago/Turabian StyleBarman, Kuntal, Dai-Jie Lin, Rohit Gupta, Chih-Kang Chang, and Jian-Jang Huang. 2023. "GaN Vertical Transistors with Staircase Channels for High-Voltage Applications" Materials 16, no. 2: 582. https://doi.org/10.3390/ma16020582

APA StyleBarman, K., Lin, D.-J., Gupta, R., Chang, C.-K., & Huang, J.-J. (2023). GaN Vertical Transistors with Staircase Channels for High-Voltage Applications. Materials, 16(2), 582. https://doi.org/10.3390/ma16020582