Effective Macroscopic Thermomechanical Characterization of Multilayer Circuit Laminates for Advanced Electronic Packaging

Abstract

:1. Introduction

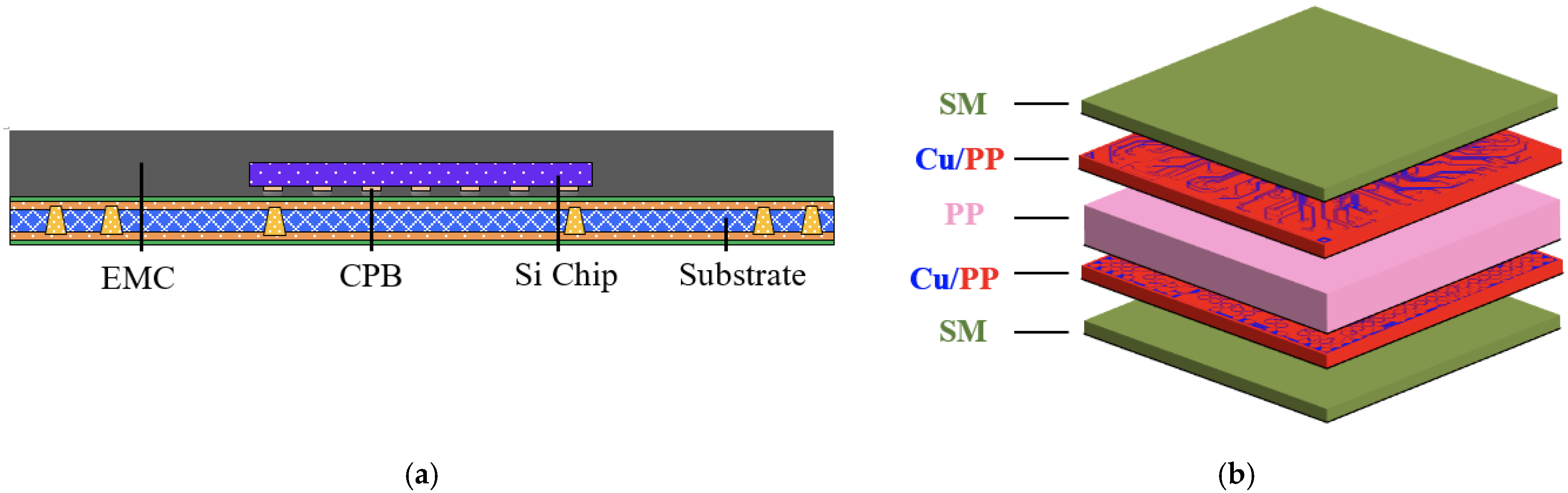

2. Effective Modeling Approach

2.1. Rule of Mixture (ROM)/Analytical Estimate

2.2. FEA-Based Effective Method

2.3. The SFT Effective Approach

3. Results and Discussion

3.1. Validation of the TMM Technique

3.2. Validation of the Proposed Effective Approach

3.3. Validation Test on the Process-Induced Warpage Prediction of FCCSP

4. Conclusions

- The TMM technique proves to be an easy, efficient, and robust approach for modeling highly complicated and intricate metal circuit layouts. In addition, a more refined mesh gives a higher-resolution description of the structural and material details of the Cu circuit traces.

- The proposed SFT effective approach turns out to be an effective, efficient, and cost-effective tool for characterizing the equivalent elastic orthotropic and anisotropic properties of large-scale, high-density, multimaterial, and multiscale laminate substrates.

- Irrespective of the use of an elastic orthotropic or anisotropic material model for the laminate substrates, the proposed SFT effective approach is shown to outperform the conventional mixture models (VA and RV-average) in macroscopically capturing the thermomechanical properties of the circuit laminates.

- As compared with the WFT effective approach, the proposed SFT approach has superior efficiency and feasibility, especially in the macroscopic modeling of large-scale and high-density circuit laminates while still maintaining comparable prediction accuracy.

- Though the effective elastic orthotropic model for the laminate substrates is slightly inferior in prediction accuracy to the effective elastic anisotropic one, its higher efficiency and cost-effectiveness make it the ideal and preferred choice for this problem.

- The proposed SFT effective approach gives a better prediction of the process-induced warpage of the FCCSP, as compared with the WVA and SVA approaches.

- The close agreement of the measured and simulated warpage results of the FCCSP after the mold cure process suggests the effectiveness of the proposed process simulation and the proposed subregion homogenization modeling framework.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Su, Q.H.; Chiang, K.N. Predicting wafer-level package reliability life using mixed supervised and unsupervised machine learning algorithms. Materials 2022, 15, 3897. [Google Scholar] [CrossRef]

- Huang, Y.W.; Chiang, K.N. Study of shear locking effect on 3D solder joint reliability analysis. J. Mech. 2022, 38, 176–184. [Google Scholar] [CrossRef]

- Zhou, M.; Li, L.; Hou, F.; He, G.; Fan, J. Thermal modeling of a chiplet-based packaging with a 2.5-D through-silicon via interposer. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 956–963. [Google Scholar] [CrossRef]

- Kim, J.C.; Ren, Z.; Yuksel, A.; Dede, E.M.; Bandaru, P.R.; Oh, D.; Lee, J. Recent advances in thermal metamaterials and their future applications for electronics packaging. J. Electron. Packag. 2021, 13, 010801. [Google Scholar] [CrossRef]

- Zhang, H.Y. Thermal analysis of 2.5-D package designs with joule heating effect along TSVs. In Proceedings of the 15th International Conference on Electronic Packaging Technology, Chengdu, China, 12–15 August 2014. [Google Scholar]

- Che, F.X.; Yamamoto, K.; Rao, V.S.; Sekhar, V.N. Panel warpage of fan-out panel-level packaging using RDL-first technology. IEEE Trans. Compon. Packag. Manuf. Technol. 2020, 10, 304–313. [Google Scholar] [CrossRef]

- Cheng, H.-C.; Tai, L.-C.; Liu, Y.-C. Theoretical and experimental investigation of warpage evolution of flip chip package on packaging during fabrication. Materials 2021, 14, 4816. [Google Scholar] [CrossRef]

- Chao, S.H.; Hung, C.P.; Chen, M.; Lee, Y.; Huang, J.; Kao, G.; Luh, D.B. An embedded trace FCCSP substrate without glass cloth. Microelectron. Reliab. 2016, 57, 101–110. [Google Scholar] [CrossRef]

- Liu, W.W.; Weng, B.; Li, J.; Yeh, C.K. FCCSP IMC growth under reliability stress following automotive standards. J. Microelectron. Electron. Packag. 2019, 16, 21–27. [Google Scholar]

- Reddy, V.V.B.; Ume, I.C.; Williamson, J.; Sitaraman, S.K. Evaluation of the quality of BGA solder balls in FCBGA packages subjected to thermal cycling reliability test using laser ultrasonic inspection technique. IEEE Trans. Compon. Packag. Manuf. Technol. 2021, 11, 589–597. [Google Scholar] [CrossRef]

- Lau, J.H. Recent advances and trends in multiple system and heterogeneous integration with TSV interposers. IEEE Trans. Compon. Packag. Manuf. Technol. 2023, 13, 3–25. [Google Scholar] [CrossRef]

- Joshi, H.; Mathur, R. A study of 3D IC’s integration and formation using TSV. Int. J. Eng. Trends Technol. 2020, 3, 353–357. [Google Scholar]

- Shih, M.-K.; Lee, T.-K.; Chang, J.-G. Warpage modeling and characterization of intelligent power modules (IPMs). J. Mech. 2021, 37, 543–550. [Google Scholar] [CrossRef]

- Cheng, E.J.; Shen, Y.L. Thermal expansion behavior of through-silicon-via structures in three-dimensional microelectronic packaging. Microelectron. Reliab. 2012, 52, 534–540. [Google Scholar] [CrossRef]

- Cheng, H.-C.; Li, R.-S.; Lin, S.-C.; Chen, W.-H.; Chiang, K.-N. Macroscopic mechanical constitutive characterization of through-silicon-via-based 3-D integration. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 432–446. [Google Scholar] [CrossRef]

- Cheng, Z.; Ding, Y.; Zhang, Z.; Zhou, M.; Chen, Z. Coupled thermo-mechanical analysis of 3D ICs based on an equivalent modeling methodology with sub-modeling. IEEE Access 2020, 8, 14146–14154. [Google Scholar] [CrossRef]

- Raoa, X.; Songa, J.; Tianb, Q.; Liua, H.; Jin, C.; Xiao, C. A universal and efficient equivalent modeling method for thermal analysis of 3D ICs containing tapered TSVs. Int. Commun. Heat Mass Transf. 2022, 136, 106161. [Google Scholar] [CrossRef]

- Lee, C.C.; Wang, C.W.; Chen, C.Y. Comparison of mechanical modeling to warpage estimation of RDL-first fan-out panel-level packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 1100–1108. [Google Scholar] [CrossRef]

- Grenestedt, J.L.; Parsaoran, H. Influence of electric artwork on thermomechanical properties and warpage of printed circuit boards. J. Appl. Phys. 2003, 94, 686–696. [Google Scholar] [CrossRef]

- Veldhuijzen van Zanten, J.F.J.; Schuerink, G.; Tullemans, A.; Legtenberg, R.; Wits, W. Method to determine thermoelastic material properties of constituent and copper-patterned layers of multilayer printed circuit boards. J. Mater. Sci. Mater. Electron. 2018, 29, 900–914. [Google Scholar] [CrossRef]

- Cheng, H.-C.; Ma, C.-L.; Liu, Y.-L. Development of ANN-based warpage prediction model for FCCSP via subdomain sampling and Taguchi hyperparameter optimization. Micromachines 2023, 14, 1325. [Google Scholar] [CrossRef]

- Chen, C.; Su, M.; Ma, R.; Zhou, Y.; Li, J.; Cao, L. Investigation of warpage for multi-die fan-out wafer-level packaging process. Materials 2022, 15, 1683. [Google Scholar] [CrossRef] [PubMed]

- Tsai, M.-Y.; Wang, Y.-W.; Liu, C.-M. Thermally-induced deformations and warpages of flip-chip and 2.5D IC packages measured by strain gauges. Materials 2021, 14, 3723. [Google Scholar] [CrossRef] [PubMed]

- Hutapea, P.; Grenestedt, J.L.; Modi, M.; Frutschy, M. Prediction of microelectronic substrate warpage using homogenized finite element models. Microelectron. Eng. 2006, 83, 557–569. [Google Scholar] [CrossRef]

- Zhang, K.; Kao, N.; Lai, D.; Wang, Y.P. Warpage simulation study by trace mapping method for FCCSP with ETS substrate. In Proceeding of the 54th International Symposium on Microelectronics, San Diego, CA, USA, 11–14 October 2021. [Google Scholar]

- Yaddanapudi, V.K.; Krishnaswamy, S.; Rath, R.; Gandhi, R. Validation of new approach of modelling traces by mapping mechanical properties for a printed circuit board mechanical analysis. In Proceeding of the IEEE 17th Electronics Packaging and Technology Conference (EPTC), Singapore, 2–4 December 2015. [Google Scholar]

- Schapery, R. Thermal expansion coefficients of composite materials based on energy principles. J. Compos. Mater. 1968, 2, 380–404. [Google Scholar] [CrossRef]

- Cheng, H.-C.; Liu, Y.-C. Warpage characterization of molded wafer for fan-out wafer-level packaging. J. Electron. Packag. Trans. ASME 2020, 142, 011004. [Google Scholar] [CrossRef]

| Tensile Test | Ux (μm) | Diff. (%) | Uy (μm) | Diff. (%) | Uz (μm) | Diff. (%) |

| DD-FEA | 6.08 | - | 5.16 | - | 3.34 | - |

| VA | 4.19 | 31.1 | 4.19 | 18.8 | 3.26 | 2.4 |

| SFT(Orthotropic) | 5.79 | 4.7 | 5.03 | 2.4 | 3.37 | 0.7 |

| SFT(Anisotropic) | 5.88 | 3.3 | 5.06 | 1.8 | 3.41 | 2.0 |

| Thermomechanical Test | Ux (μm) | Diff. (%) | Uy (μm) | Diff. (%) | Uz (μm) | Diff. (%) |

| DD-FEA | 2.15 | - | 2.49 | - | 2.48 | - |

| VA | 2.17 | 0.8 | 2.17 | 12.8 | 2.28 | 7.9 |

| SFT(Orthotropic) | 2.16 | 0.2 | 2.43 | 2.4 | 2.41 | 2.5 |

| SFT(Anisotropic) | 2.16 | 0.2 | 2.43 | 2.4 | 2.41 | 2.5 |

| Tensile Test | Ux (μm) | Diff. (%) | Uy (μm) | Diff. (%) | Uz (μm) | Diff. (%) |

| DD-FEA | 2.16 | - | 1.93 | - | 1.86 | - |

| VA | 1.67 | 22.6 | 1.67 | 13.4 | 1.18 | 36.4 |

| RV-average | 1.94 | 10.2 | 1.94 | 0.5 | 1.37 | 26.0 |

| SFT (Orthotropic) | 2.30 | 6.2 | 2.01 | 3.9 | 1.73 | 6.9 |

| SFT (Anisotropic) | 2.30 | 6.2 | 2.00 | 3.3 | 1.90 | 2.3 |

| Heating Test | Ux (μm) | Diff. (%) | Uy (μm) | Diff. (%) | Uz (μm) | Diff. (%) |

| DD-FEA | 2.17 | - | 2.41 | - | 52.79 | - |

| VA | 1.88 | 13.5 | 1.88 | 21.9 | 58.28 | 10.4 |

| RV-average | 2.19 | 0.8 | 2.19 | 9.0 | 55.76 | 5.6 |

| SFT (Orthotropic) | 2.00 | 7.8 | 2.29 | 4.7 | 52.72 | 0.1 |

| SFT (Anisotropic) | 2.02 | 6.9 | 2.30 | 4.5 | 52.92 | 0.2 |

| Warpage (µm) | Difference (%) | |

|---|---|---|

| Measurement | 25.6 (18.0~31.0) | - |

| WFT (Anisotropic) | 27.8 | 8.8 |

| WFT (Orthotropic) | 29.9 | 16.8 |

| WVA (Isotropic) | 36.9 | 44.3 |

| SFT (Anisotropic) | 28.8 | 12.8 |

| SFT (Orthotropic) | 30.8 | 20.3 |

| SVA (Isotropic) | 35.6 | 39.1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cheng, H.-C.; Jhu, W.-Y. Effective Macroscopic Thermomechanical Characterization of Multilayer Circuit Laminates for Advanced Electronic Packaging. Materials 2023, 16, 7491. https://doi.org/10.3390/ma16237491

Cheng H-C, Jhu W-Y. Effective Macroscopic Thermomechanical Characterization of Multilayer Circuit Laminates for Advanced Electronic Packaging. Materials. 2023; 16(23):7491. https://doi.org/10.3390/ma16237491

Chicago/Turabian StyleCheng, Hsien-Chie, and Wen-You Jhu. 2023. "Effective Macroscopic Thermomechanical Characterization of Multilayer Circuit Laminates for Advanced Electronic Packaging" Materials 16, no. 23: 7491. https://doi.org/10.3390/ma16237491