Abstract

A new architecture has become necessary owing to the power consumption and latency problems of the von Neumann architecture. A neuromorphic memory system is a promising candidate for the new system as it has the potential to process large amounts of digital information. A crossbar array (CA), which consists of a selector and a resistor, is the basic building block for the new system. Despite the excellent prospects of crossbar arrays, the biggest obstacle for them is sneak current, which can cause a misreading between the adjacent memory cells, thus resulting in a misoperation in the arrays. The chalcogenide-based ovonic threshold switch (OTS) is a powerful selector with highly nonlinear I–V characteristics that can be used to address the sneak current problem. In this study, we evaluated the electrical characteristics of an OTS with a TiN/GeTe/TiN structure. This device shows nonlinear DC I–V characteristics, an excellent endurance of up to 109 in the burst read measurement, and a stable threshold voltage below 15 mV/dec. In addition, at temperatures below 300 °C, the device exhibits good thermal stability and retains an amorphous structure, which is a strong indication of the aforementioned electrical characteristics.

1. Introduction

The success of today’s computing systems is due to the von Neumann architecture, whose design involves moving data back and forth between the processor and the memory. There are two major reasons for the success of this architecture. The first one is its Turing completeness, which means that, given a sufficient amount of memory and time, it can complete any mathematical task. The second one is its scalability, which makes it possible to expand the memory. As the amount of data increases, the computation speed also increases. There is no need to modify the architecture or the associated programming model [1,2,3,4,5,6,7,8,9,10,11,12,13,14,15]. However, this data transfer system accounts for a large part of the power consumed. Even though the next-generation computer systems can perform exascale (1018) calculations per second, enabling them to deal with complex data, they will consume about 30 MW of power when using the von Neumann architecture. Furthermore, the von Neumann system suffers from latency owing to the huge amount of data transfer between the separate memory unit and logic unit [16,17]. This problem resulted in the development of a neuromorphic computing system, which is inspired by the biological neural system and has a much lower power consumption than that of conventional processors. This new computing system has the potential to process large amounts of digital information and can be used for natural language processing, driving automation, and big data analysis.

A crossbar array (CA) is the basic building block of the neuromorphic system; it is composed of a memory and a selector. The memory acts as a synaptic weight for storing information and processing of input signals. Among the candidates for the memory, resistive random-access memory (RRAM) is the most promising one because of its high capacity, multilevel programming, high speed, and scalability down to the 4F2 design rule. The role of the selector is to prevent sneak current through unchosen cells, which leads to disruption in data reading and programming [18,19,20,21,22,23,24,25]. The chalcogenide-based ovonic threshold switch (OTS) is currently the best device for the selector. The OTS has a fast switching speed, bidirectional rectifying characteristics, and CMOS compatibility [26,27,28,29,30,31,32]. Furthermore, it uses amorphous materials, enabling it to achieve its fast switching speed and nonlinearity in I–V characteristics [33,34,35,36,37,38].

In this study, we investigated an OTS device, namely, GeTe (GT), which has shown excellent thermal stability and electrical endurance characteristic.

2. Materials and Methods

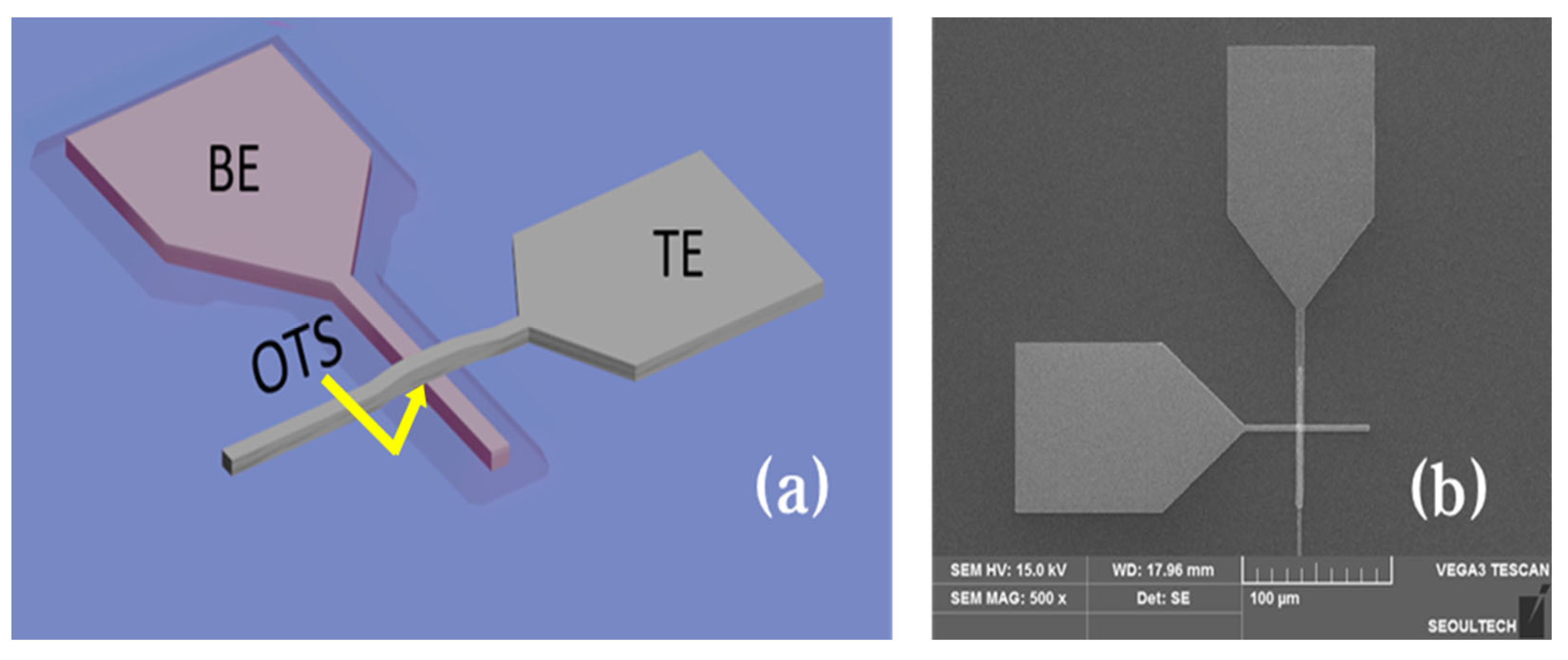

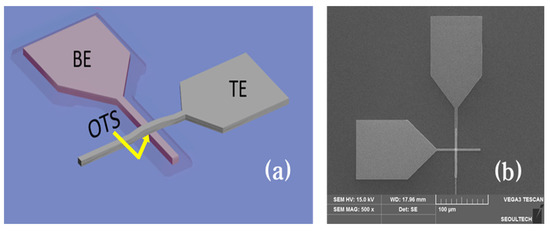

Device Fabrication:Figure 1a shows a schematic diagram of the top electrode (TE) TiN/OTS (GT)/bottom electrode (BE) TiN structure. A heavily doped P-type Si wafer (ρ < 0.01 Ωcm) and a thermally oxidized SiO2 wafer with a dimension of 300 nm were used as the substrates. The BE was patterned using an inductively coupled plasma-reactive ion etching method after depositing the TiN with a physical vapor deposition system.

Figure 1.

(a) Schematic diagram of the BE TiN/OTS (GT)/TE TiN structure and (b) SEM image of the same device.

A radio frequency (RF) sputtering system with a Ge-Te (1:1) target was used to deposit the GT layers. The basal vacuum pressure in the chamber was set to less than 1.0 × 10−6 Torr, and the working pressure of the Ar gas (purity of 99.999%) and RF power were maintained at 2.0 × 10−3 Torr and 50 W, respectively, during sputtering. Before the deposition, pre-sputtering was performed for 30 min to eliminate any contaminants on the target. After the deposition of the GT layers, TE TiN was deposited and patterned using the lift-off method. Figure 1b shows a top-view image of the device.

Materials Analysis: The samples for material analysis were prepared simultaneously for the GT device on the SiO2/Si substrate. The sample for the high-resolution transmission electron microscopy (HR-TEM) analysis was prepared by a focused ion beam operation (FIB (Leeuwarden, The Netherlands), Helios NanoLab™ (Sarasota, FL, USA), FEI (Hillsboro, OR, USA)). HR-TEM (Tecnai G2 F30 S-TWIN, FEI) analysis was then performed to obtain a cross-sectional view of the Si/SiO2/TiN/GeT/TiN stacked device.

Electrical Measurements: The electrical characteristics of the device were measured using an HP4145B semiconductor parameter analyzer (SPA) in the DC I–V sweep mode. The temperature was controlled by a hot-stage microscope using a temperature controller. Pulse-based electrical measurements were conducted using the HP4145B, an arbitrary function generator (Agilent 81150 A, Santa Clara, CA, USA), an oscilloscope (MSOX3024T, Tektronix, Beaverton, OR, USA), and an electromechanical RF electrical circuit switch box. Throughout the measurement process, the voltage was biased to the TiN TE, while the TiN BE was electrically grounded. The resistance (or current) values of the programming and erasure were verified at 2 V using the SPA. These two types of electrical circuits were alternately used by the electromechanical RF electrical circuit switch boxes. All the electrical measurements were performed using a LabVIEW-based control program.

3. Results

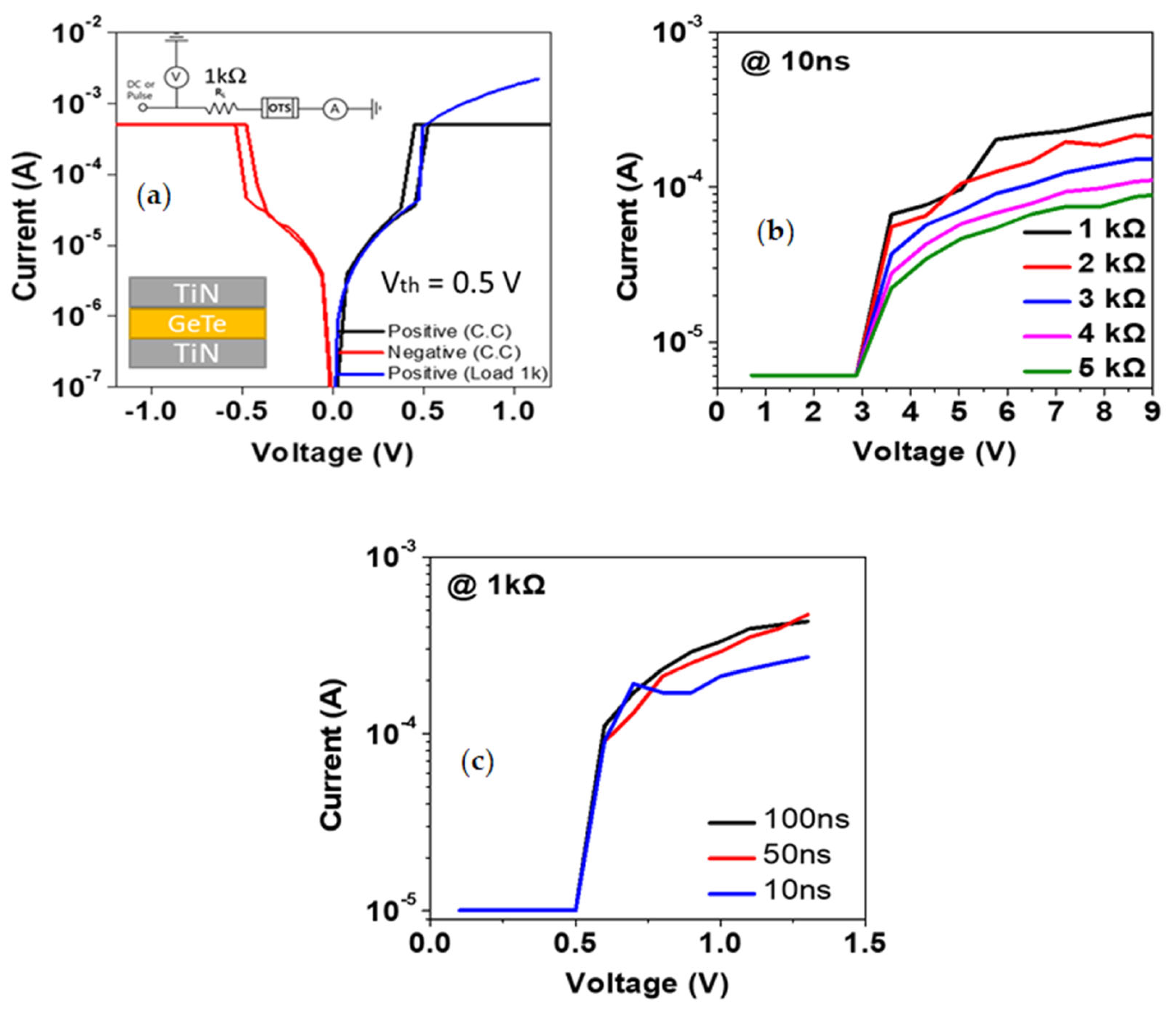

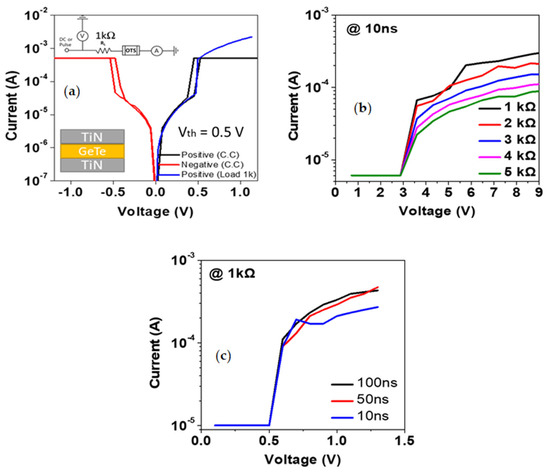

Figure 2a shows the DC I–V characteristic curves of the TiN/OTS (GT)/TiN device, which were measured by applying a DC bias. We set the compliance current to prevent a dielectric breakdown of the device. The black lines in the positive bias region and the red lines in the negative bias region were the results of the measurement under a current compliance of 500 µA. Moreover, the blue line is the characteristic under the bias of an external 1-kΩ load resistor. We found that the threshold voltage (Vth) of this device was under 0.5 V during the forward voltage sweep. At Vth, the OTS device maintained a high resistance state (off state), and the current increased abruptly (on state). During the backward sweep, the on state returned to the off state again.

Figure 2.

(a) DC I–V characteristic curves of the BE TiN/OTS (GT)/TE TiN device. The black line is the sweep curve for the positive bias region, and the red line is that for the negative bias region. A current compliance of 500 µA was applied to the device to prevent a permanent breakdown. The blue line is the DC I–V characteristic curve under the 1-kΩ external load resistor. (b) Pulse-based current voltage characteristics showing forming voltage values of devices with different external load resistances. (c) Pulse-based current voltage characteristics of the device with different pulse widths under the 1-kΩ external load resistor.

The OTS device exhibited identical values of Vth. Considering that typical OTS devices generally have different Vth values, our OTS device shows special features and, thus, should be investigated further [28,29]. In the results of the study, Valea, A. et al., it can be confirmed that the Vth is 1.4 V, which is different from the Vth (0.5 V) of our OTS device. In addition, the results of studies by Laguna, C. et al. also show that Vth is different from ours. Figure 2b shows the pulse-based current voltage (PIV) characteristics of the device with different external load resistors. Here, the pulse is ISPP (Incremental step pulse programming), and a method of measuring while continuously increasing the amplitude value in the same pulse width state is applied. During the PIV measurement, a series of pulses with different voltages was applied, and the resistance value of each step was measured using an oscilloscope. To prevent the device from breakdown during AC measurement, we set the external load resistance from 1 kΩ to 5 kΩ to check for breakdown voltage, which did not occur. As the external resistance approaches zero, more current flows through the element. Therefore, the pulse width was changed from 10 ns to 100 ns at a fixed external load of 1 kΩ to determine the minimum pulse width for proper operation of the device, as shown in Figure 2c.

The OTS is not used alone but is connected in series to the RRAM in the CA. The most important role of the OTS is to prevent a sneak current during a read operation. The leakage paths through unselected cells in the CA can lead to an inaccurate output signal and clear identification of the high-resistance state from the low-resistance state of the RRAM cell. Figure 2 shows the nonlinear characteristics of the OTS, which can suppress sneak current and thus improve the read margin of the CA.

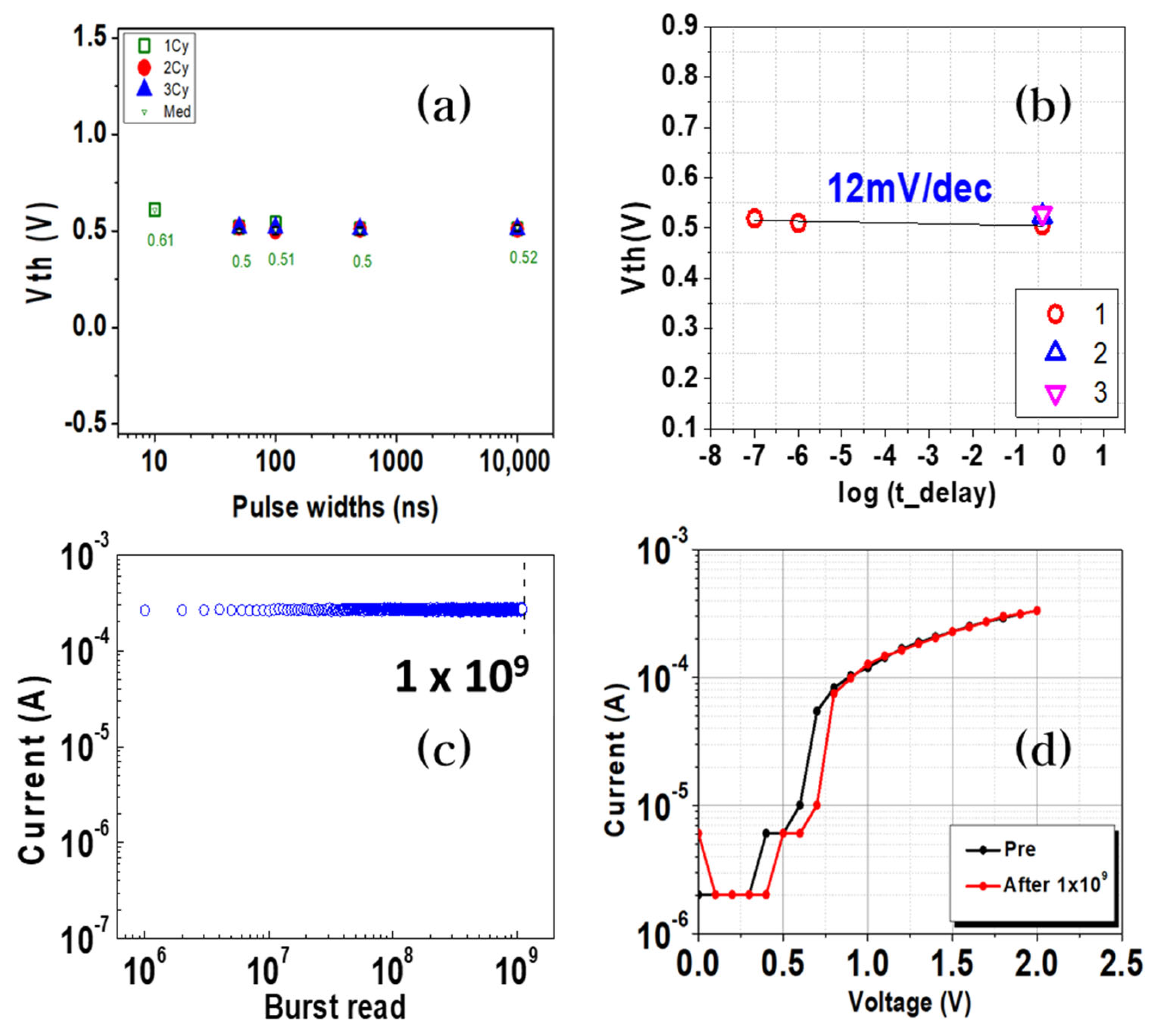

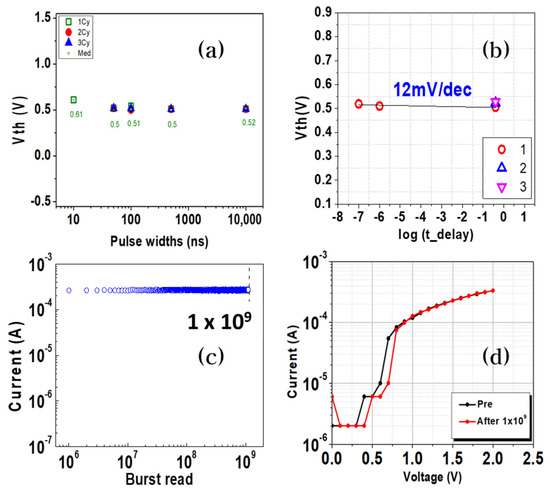

Figure 3a shows the Vth change with different pulse widths. We changed the pulse widths from 10 ns to 10 µs and checked the Vth value of each state, which showed little change. It has excellent stability, and the result has significance for CA applications. Because the OTS is part of the 1 Selector-1 Resistance (1S1R) CA, how the RRAM works is very important. Therefore, the operating voltage of the memristor affects the operation of the selector. The maximum operating voltage of the memristor that the selector can operate is up to 3 V. However, if the voltage is greater than 3 V, breakdown may occur in the initial cycle, so the lower the voltage, the better. The current trend for increasing the memory density is by using multi-bit operation, which is a very effective way to store more information in a single device. For the RRAM, multi-bit resistive switching has been reported in previous studies by setting the current compliance, changing the reset voltage, and modulating the voltage pulse amplitude or height. Among those studies, Alamgir et al. reported the feasibility of the multi-bit operation of the RRAM by modulating the pulse width [39,40,41]. They demonstrated this possibility by changing the pulse width without any overlapping of the resistance levels. If the OTS is serially connected to the RRAM, the crucial role of the OTS is to maintain Vth while voltages of different pulse widths are applied to the cell. Figure 3b shows the Vth shift with delay time.

Figure 3.

(a) Threshold voltage (Vth) endurance with different pulse widths. Even though the pulse widths were changed from 10 ns to 10 us, the threshold voltage maintained almost the same value. (b) Vth shift with delay time on a log scale. Vth was retained under 15 mV/dec, which shows stable characteristics. (c) Results of the burst read endurance test showing excellent endurance. Read voltage equal to Set voltage (=0.5 V). The burst read scheme differs from the conventional one, which repeats the write/read operation. The resistance of the OTS was determined after 10 to n numbers of pulses were applied to the OTS cell. (d) Comparison of the PIV results before and after the endurance test. We found robust OTS characteristics, which show good switching characteristics after 109 cycles of the endurance test.

After the OTS was turned on, the values of Vth were measured at different times on a log scale to check whether the OTS maintained its initial value. The OTS endurance was measured because the reliability of the OTS is a key issue that can affect the performance and accuracy of a large-scale cell array. The burst read endurance was measured, as shown in Figure 3c. In contrast to nonvolatile memory, such as the RRAM, the OTS is a volatile device. The burst read scheme differs from the conventional one, which repeats the write/read operation. After 10 to n numbers of pulses were applied to the OTS cell, the OTS resistance was determined. Through this method, we can reduce the read damage using the conventional read scheme. Figure 3d shows a comparison of the PIV results before and after the endurance test. Robust OTS characteristics showed good switching characteristics after 109 cycles of the endurance test. From the results, we can confirm the robust endurance of the OTS cell.

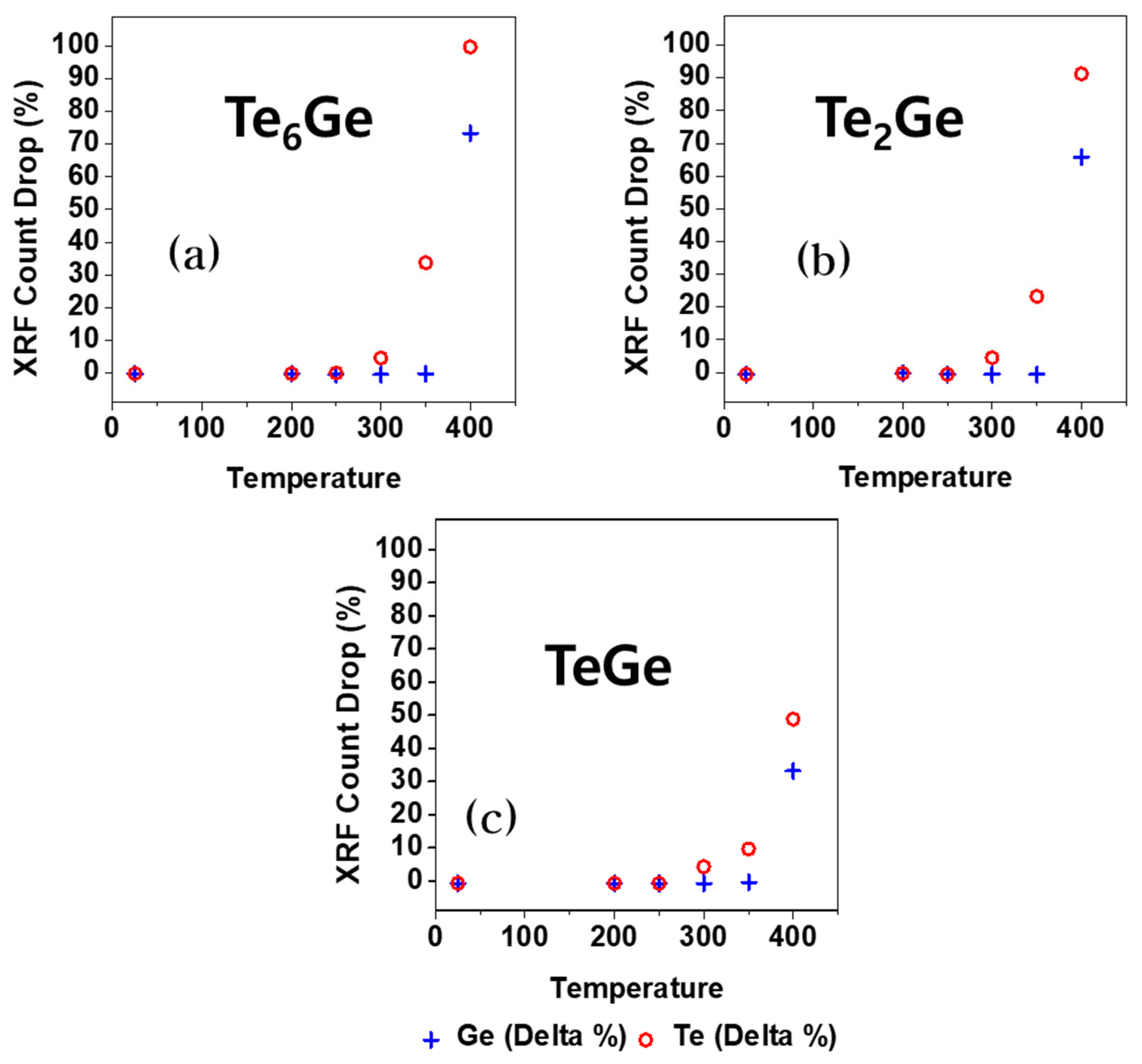

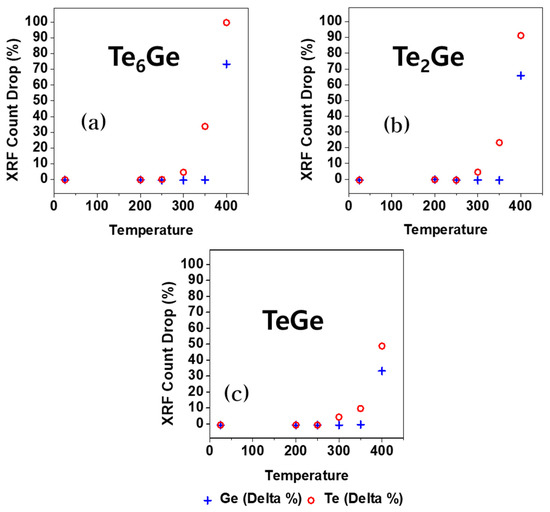

To confirm the thermal stability, we performed an XRF analysis on the different components of the GT samples. A quantitative analysis of the Ge and Te of the compounds was performed every 50 °C after 200 °C. As shown in Figure 4a–c, the quantity of Te dramatically decreases after 350 °C, and the rate of decrease of Te is higher than that of Ge at 400 °C.

Figure 4.

Drop in the XRF count of the OTS device with increasing temperature. (a–c) are the Te6Ge, Te2Ge, and TeGe, respectively.

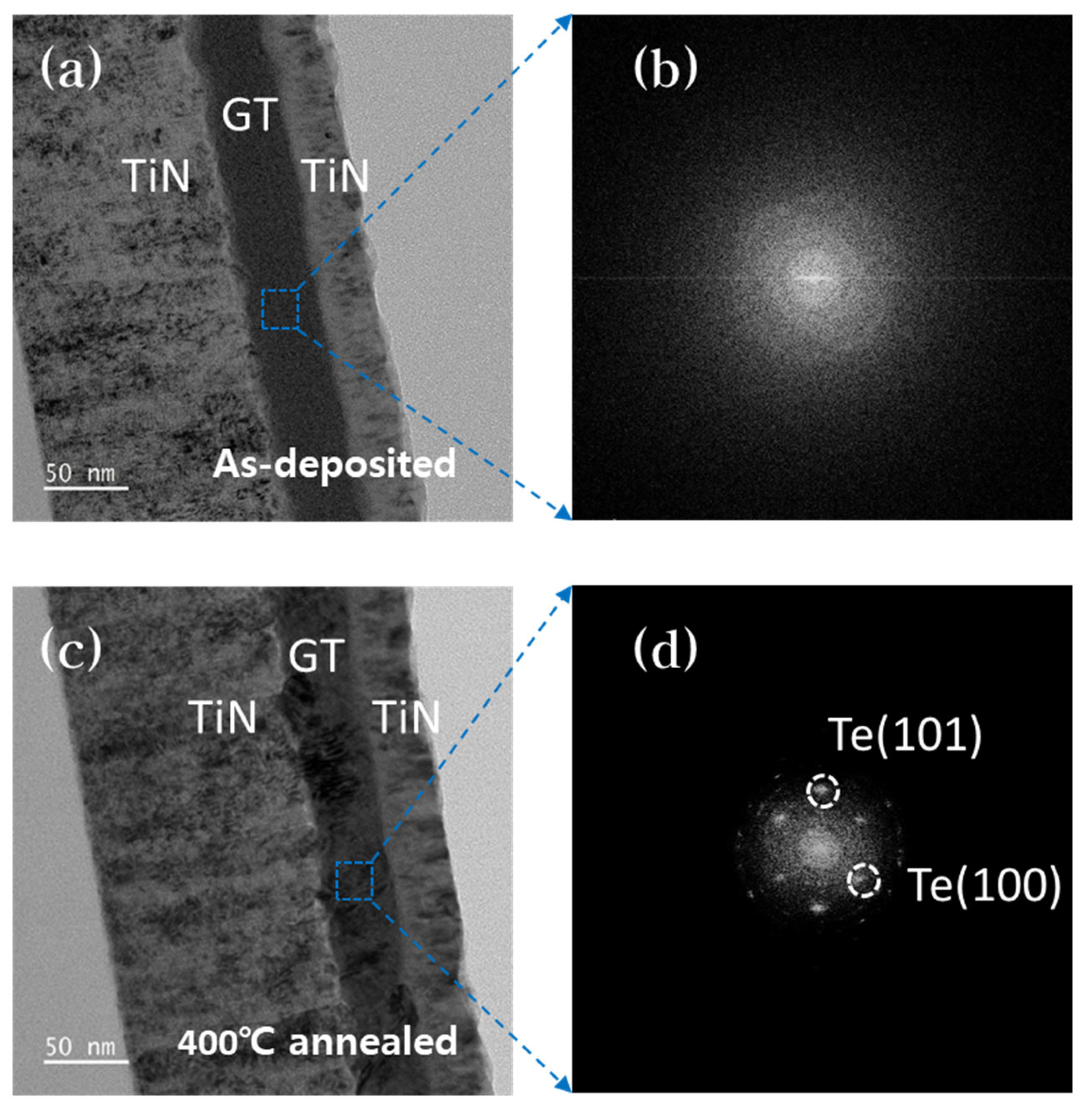

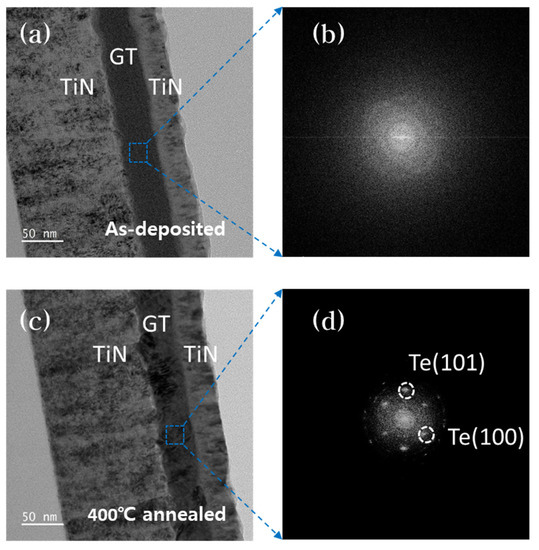

We performed an HR-TEM analysis for the direct observation of the GT thin film. Figure 5a shows a cross-sectional view of a TiN/GT/TiN structure before annealing the GT layer. Figure 5c shows a cross-sectional view of the same structure after 400 °C annealed. We analyzed the diffraction pattern in the blue dotted-ray rectangular region visible in the GT layer according to the fast Fourier transform (FFT) method. Figure 5b shows the diffraction pattern in the GT layer before annealing, and Figure 5d shows the pattern after 400 °C annealing. The FFT results of the GT layer before annealing showed amorphous characteristics, as illustrated in Figure 5b, and crystalline Te could be observed in the GT layer after annealing. This indicates that GT loses its amorphous properties at this temperature.

Figure 5.

(a,c) are cross-sectional view before and after annealing GT with TiN/GT/TiN structures obtained by high-resolution transmission electron microscope (HR-TEM) analysis for direct observation of GT thin films. (b,d) show the FFT results of (a,c) layers.

The biggest advantage of the OTS is its highly nonlinear current flow (in the DC I–V characteristic), which plays a crucial role in preventing sneak current in the 1S1R cell array structure, as mentioned earlier. In particular, the endurance of the OTS in pulse-based operations must be greater than that of the resistor because the OTS is turned on for every programming and reading event. The amorphous structure of the OTS is responsible for this endurance, which offers electronic trap sites between the conduction band and the Fermi level. Trapping and de-trapping by the external electric field can cause high nonlinearity.

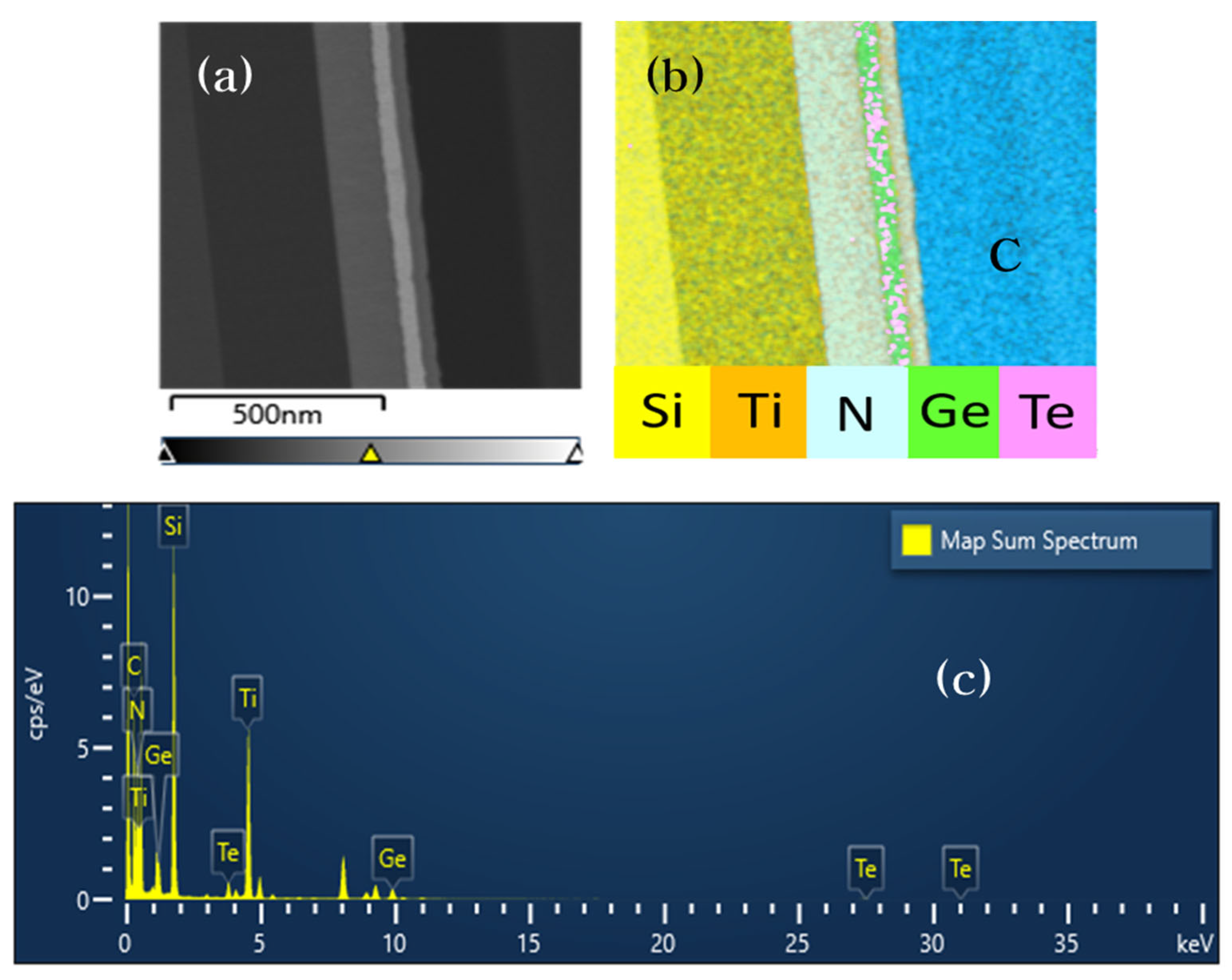

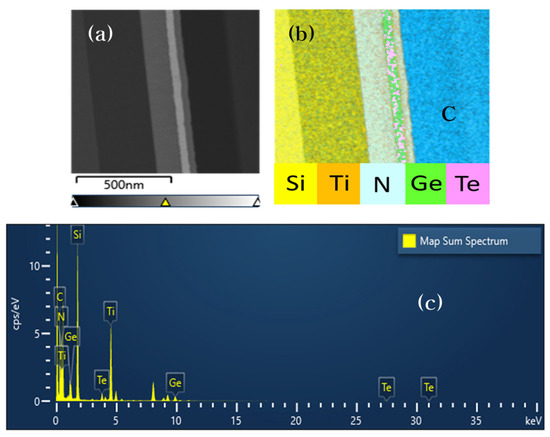

To investigate the composition of the device, we performed a transmission electron microscopy (TEM)/energy dispersive X-ray spectroscopy (EDS) analysis on the sample. Figure 6a shows a cross-sectional image of the TiN/GT/TiN device obtained by TEM analysis, and Figure 6b illustrates the results of the EDS analysis of the cross-section of the device. We can confirm that Te and Ge coexist between the bottom and top TiN layers. Figure 6c shows the map sum spectrum of the sample. The elements and atomic ratios of the TiN/GT/TiN device are shown in Table 1.

Figure 6.

(a) Cross-sectional view of the Si/SiO2/TiN/GT/TiN device. The top of the sample carbon layer was deposited for analysis. (b) Map of the sample with every element of the sample. (c) Map sum spectrum of the device.

Table 1.

Map sum spectrum of the TiN/GT/TiN device.

4. Conclusions

In summary, in this study, the electrical characteristics of an OTS with a TiN/GT/TiN structure were investigated. This device shows nonlinear DC I–V characteristics and excellent endurance of up to 109 in the burst read measurement. Considering that the OTS is turned on for every programming and reading event, the endurance of the OTS must be greater than that of the resistor, and the device meets this requirement. In addition, the device exhibited a stable threshold voltage below 15 mV/dec. The thermal stability indicates a stable thermal property below 300 °C. The thermal stability above this temperature requires further study. Moreover, the device retains an amorphous structure below 300 °C, which is a strong indication of the aforementioned electrical characteristics.

Author Contributions

D.S. and S.Y.L. contributed equally to this work. Experiments and writing, D.S. and S.Y.L.; methodology, M.K.Y.; conceptualization, H.K.S., M.P. and J.-W.K.; supervision, M.K.Y. All authors have read and agreed to the published version of the manuscript.

Funding

This paper was supported by the Academic Research Fund of Dr. Myung Ki (MIKE) Hong in 2020 (RI12020078).

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Wright, C.D.; Hosseini, P.; Diosdado, J.A.V. Beyond von-Neumann computing with nanoscale phase-change memory devices. Adv. Funct. Mater. 2013, 23, 2248. [Google Scholar] [CrossRef]

- Zhang, W.; Gao, B.; Tang, J.; Yao, P.; Yu, S.; Chang, M.F.; Yoo, H.; Qian, H.; Wu, H. Neuro-Inspired Computing Chips. Nat. Electron. 2020, 3, 371. [Google Scholar] [CrossRef]

- Sebastian, A.; Gallo, M.L.; Khaddam-Aljameh, R.; Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 2020, 15, 529. [Google Scholar] [CrossRef] [PubMed]

- Xu, M.; Mai, X.; Lin, J.; Zhang, W.; Li, Y.; He, Y.; Tong, H.; Hou, X.; Zhou, P.; Miao, X. Recent Advances on Neuromorphic Devices Based on Chalcogenide Phase-Change Materials. Adv. Funct. Mater. 2020, 30, 2003419. [Google Scholar] [CrossRef]

- Upadhyay, N.K.; Jiang, H.; Wang, Z.; Asapu, S.; Xia, Q.; Yang, J. Emerging Memory Devices for Neuromorphic Computing. Adv. Mater. Technol. 2019, 4, 1800589. [Google Scholar] [CrossRef]

- Upadhyay, N.K.; Joshi, S.; Yang, J.J. Synaptic electronics and neuromorphic computing. Sci. China Inf. Sci. 2016, 59, 061404. [Google Scholar] [CrossRef]

- Linn, E.; Rosezin, R.; Kügeler, C.; Waser, R. Complementary resistive switches for passive nanocrossbar memories. Nat. Mater. 2010, 9, 403. [Google Scholar] [CrossRef]

- Wang, Z.; Wu, H.; Burr, G.W.; Hwang, C.S.; Wang, K.L.; Xia, Q.; Ynag, J.J. Resistive switching materials for information processing. Nat. Rev. Mater. 2020, 5, 173. [Google Scholar] [CrossRef]

- Zhang, W.; Mazzarello, R.; Wutting, M.; Ma, E. Designing crystallization in phase-change materials for universal memory and neuro-inspired computing. Nat. Rev. Mater. 2019, 4, 150–168. [Google Scholar] [CrossRef]

- Lelmini, D.; Wong, H.S.P. In-memory computing with resistive switching devices. Nat. Electron. 2018, 1, 333–343. [Google Scholar] [CrossRef]

- Kuzum, D.; Yu, S.; Wong, H.S. Synaptic electronics: Materials, devices and applications. Nanotechnology 2013, 24, 382001. [Google Scholar] [CrossRef] [PubMed]

- Zhu, J.; Zhang, T.; Yang, Y.; Huang, R. A comprehensive review on emerging artificial neuromorphic devices. Appl. Phys. Rev. 2020, 7, 011312. [Google Scholar] [CrossRef]

- Borghetti, J.; Snider, G.S.; Kuekes, P.J.; Yang, J.J.; Stewart, D.R.; Williams, R.S. ‘Memristive’ switches enable ‘stateful’ logic operations via material implication. Nature 2010, 464, 873. [Google Scholar] [CrossRef] [PubMed]

- Yang, J.J.; Strukov, D.B.; Stewart, D.R. Memristive devices for computing. Nat. Nanotechnol. 2013, 8, 13. [Google Scholar] [CrossRef]

- Ohno, T.; Hasegawa, T.; Tsuruoka, T.; Terabe, K.; Gimzewski, J.; Aono, M. Short-term plasticity and long-term potentiation mimicked in single inorganic synapses. Nat. Mater. 2011, 10, 591–595. [Google Scholar] [CrossRef]

- Wang, S.; Song, L.; Chen, W.; Wang, G.; Hao, E.; Li, C.; Hu, Y.; Pan, Y.; Nathan, A.; Hu, G.; et al. Memristor-Based Intelligent Human-Like Neural Computing. Adv. Electron. Mater. 2022, 9, 2200877. [Google Scholar] [CrossRef]

- Jayaram, C.; Tekir, U. Von Neumann regular modules. Comm. Algebra 2018, 46, 2205–2217. [Google Scholar] [CrossRef]

- Zhou, J.; Kim, K.H.; Lu, W.W. Crossbar RRAM arrays: Selector device requirements during read operation. IEEE Trans. Electron Devices 2014, 61, 1369. [Google Scholar] [CrossRef]

- Park, W.Y.; Kim, G.H.; Seok, J.Y.; Kim, K.M.; Song, S.J.; Lee, M.H.; Hwang, C.S. Bipolar resistive switching with self-rectifying effects in Al/ZnO/Si structure. Nanotechnology 2010, 21, 195201. [Google Scholar] [CrossRef]

- Shi, L.; Zheng, G.; Tian, B.; Dkhil, B.; Duan, C. Research progress on solutions to the sneak path issue in memristor crossbar arrays. Nanoscale Adv. 2020, 2, 1811. [Google Scholar] [CrossRef]

- Hu, M.; Graves, C.E.; Li, C.; Li, Y.; Ge, N.; Montgomery, E.; Davila, N.; Jiang, H.; Williams, R.S.; Yang, J.J.; et al. Memristor-Based Analog Computation and Neural Network Classification with a Dot Product Engine. Adv. Mater. 2018, 30, 1705914. [Google Scholar] [CrossRef] [PubMed]

- Xia, Q.; Yang, J.J. Memristor crossbar arrays for brain-inspired computing. Nat. Mater. 2019, 18, 309–323. [Google Scholar] [CrossRef] [PubMed]

- Li, H.; Wang, S.; Zhang, X.; Wang, W.; Yang, R.; Sun, Z.; Feng, W.; Lin, P.; Wang, Z.; Sun, L.; et al. Memristive Crossbar Arrays for Storage and Computing Applications. Adv. Intell. Syst. 2021, 3, 2100017. [Google Scholar] [CrossRef]

- Kim, K.-H.; Gaba, S.; Wheeler, D.; Cruz-Albrecht, J.M.; Hussain, T.; Srinivasa, N.; Lu, W. A functional hybrid memristor crossbar-array/CMOS system for data storage and neuromorphic applications. Nano Lett. 2012, 12, 389. [Google Scholar] [CrossRef] [PubMed]

- Xia, Q.; Robinett, W.; Cumbie, M.W.; Banerjee, N.; Crdinali, T.J.; Yang, J.J.; Wu, W.; Li, X.; Tong, W.M.; Strukov, D.B.; et al. Memristor−CMOS Hybrid Integrated Circuits for Reconfigurable Logic. Nano Lett. 2009, 9, 3640. [Google Scholar] [CrossRef] [PubMed]

- Redaelli, A.; Pirovano, A.; Benvenuti, A.; Lacaita, A. Threshold switching and phase transition numerical models for phase change memory simulations. J. Appl. Phys. 2008, 103, 111101. [Google Scholar] [CrossRef]

- Adler, D.; Shur, M.S.; Silver, M.; Ovshinsky, S.R. Threshold switching in chalcogenide-glass thin films. J. Appl. Phys. 1980, 51, 3289. [Google Scholar] [CrossRef]

- Velea, A.; Opsomer, K.; Devulder, W.; Dumortier, J.; Fan, J.; Detavernier, C.; Jurczak, M.; Govoreanu, B. Te-based chalcogenide materials for selector applications. Sci. Rep. 2017, 7, 8103. [Google Scholar] [CrossRef]

- Laguna, C.; Bernard, M.; Bernier, N.; Rouchon, D.; Rochat, N.; Garrione, J.; Jannaud, A.; Nolot, E.; Meli, V.; Castellani, N.; et al. Multilayer OTS Selectors Engineering for High Temperature Stability, Scalability and High Endurance. In Proceedings of the 2021 IEEE International Memory Workshop (IMW), Dresden, Germany, 16–19 May 2021. [Google Scholar]

- Laguna, C.; Castellani, N.; Bernard, M.; Rochat, N.; Rouchon, D.; Sabbione, C.; Garrione, J.; Nolot, E.; Bourgeois, G.; Cyrille, M.C.; et al. Innovative Multilayer OTS Selectors for Performance Tuning and Improved Reliability. In Proceedings of the 2020 IEEE International Memory Workshop (IMW), Dresden, Germany, 17–20 May 2020; pp. 1–4. [Google Scholar]

- Zhu, M.; Ren, K.; Song, Z. Ovonic threshold switching selectors for three-dimensional stackable phase-change memory. MRS Bull. 2019, 44, 715. [Google Scholar] [CrossRef]

- Seo, H.K.; Ryu, J.J.; Lee, S.Y.; Park, M.; Park, S.G.; Song, W.; Kim, G.H.; Yang, M.K. Material and structural engineering of ovonic threshold switch for highly reliably performance. Adv. Electron. Mater. 2022, 8, 2200161. [Google Scholar] [CrossRef]

- Chen, Z.; Tong, H.; Li, X.; Wang, L.; Zhao, R.; Gu, W.; Miao, X. Experimental evidence for non-purely electric field-induced threshold switching and modified thermal-assisted model in GeTe phase change material. Appl. Phys. Lett. 2021, 118, 203502. [Google Scholar] [CrossRef]

- Vinod, E.; Singh, A.; Ganesan, R.; Sangunni, K. Effect of selenium addition on the GeTe phase change memory alloys. J. Alloys Compd. 2022, 537, 127. [Google Scholar] [CrossRef]

- Bruns, G.; Merkelbach, P.; Schlockermann, C.; Salinga, M.; Wuttig, M.; Happ, T.D.; Philipp, J.B.; Kund, M. Nanosecond switching in GeTe phase change memory cells. Appl. Phys. Lett. 2009, 95, 043108. [Google Scholar] [CrossRef]

- Chien, W.C.; Yeh, C.W.; Bruce, R.L.; Cheng, H.Y.; Kuo, I.T.; Yang, C.H.; Ray, A.; Miyazoe, H.; Kim, W.; Carta, F.; et al. A study on OTS-PCM pillar cell for 3-D stackable memory. IEEE Trans. Electron Devices 2018, 65, 5172–5179. [Google Scholar] [CrossRef]

- Lam, C.H. Phase change memory and its intended applications. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; p. 29. [Google Scholar]

- Anbarasu, M.; Wimmer, M.; Bruns, G.; Salinga, M.; Wuttig, M. Nanosecond threshold switching of GeTe6 cells and their potential as selector devices. Appl. Phys. Lett. 2012, 100, 143505. [Google Scholar] [CrossRef]

- Hu, W.; Zou, L.; Cao, C.; Guo, Y.; Bao, D. High speed and multi-level resistive switching capability of Ta2O5 thin films for nonvolatile memory application. J. Alloys Compd. 2016, 676, 356. [Google Scholar] [CrossRef]

- Zhang, W.; Kong, J.; Cao, Z.; Li, A.; Wang, L.; Zhu, L.; Li, X.; Cao, Y.; Wu, D. Bipolar Resistive Switching Characteristics of HfO2/TiO2/HfO2 Trilayer-Structure RRAM Devices on Pt and TiN-Coated Substrates Fabricated by Atomic Layer Deposition. Nanoscale Res. Lett. 2017, 12, 393. [Google Scholar] [CrossRef]

- Simanjuntak, F.; Chandrasekaran, S.; Lin, C.-C.; Tseng, T.-Y. Switching failure mechanism in zinc peroxide-based programmable metallization cell. Nanoscale Res. Lett. 2018, 13, 327. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).