A Droop-Controlled Interlink Converter for a Dual DC Bus Nanogrid with Decentralized Control

Abstract

1. Introduction

2. Power Control and Current Sharing in a Single DC Bus Nanogrid

3. Power Control of the Interlink Converter

4. Interlink Converter Modeling and Control Design in Dual DC Buses Nanogrid

5. Case Study

- Boost:

- K factor:

- Zeros and Poles:

- Gain:

6. Simulation Results

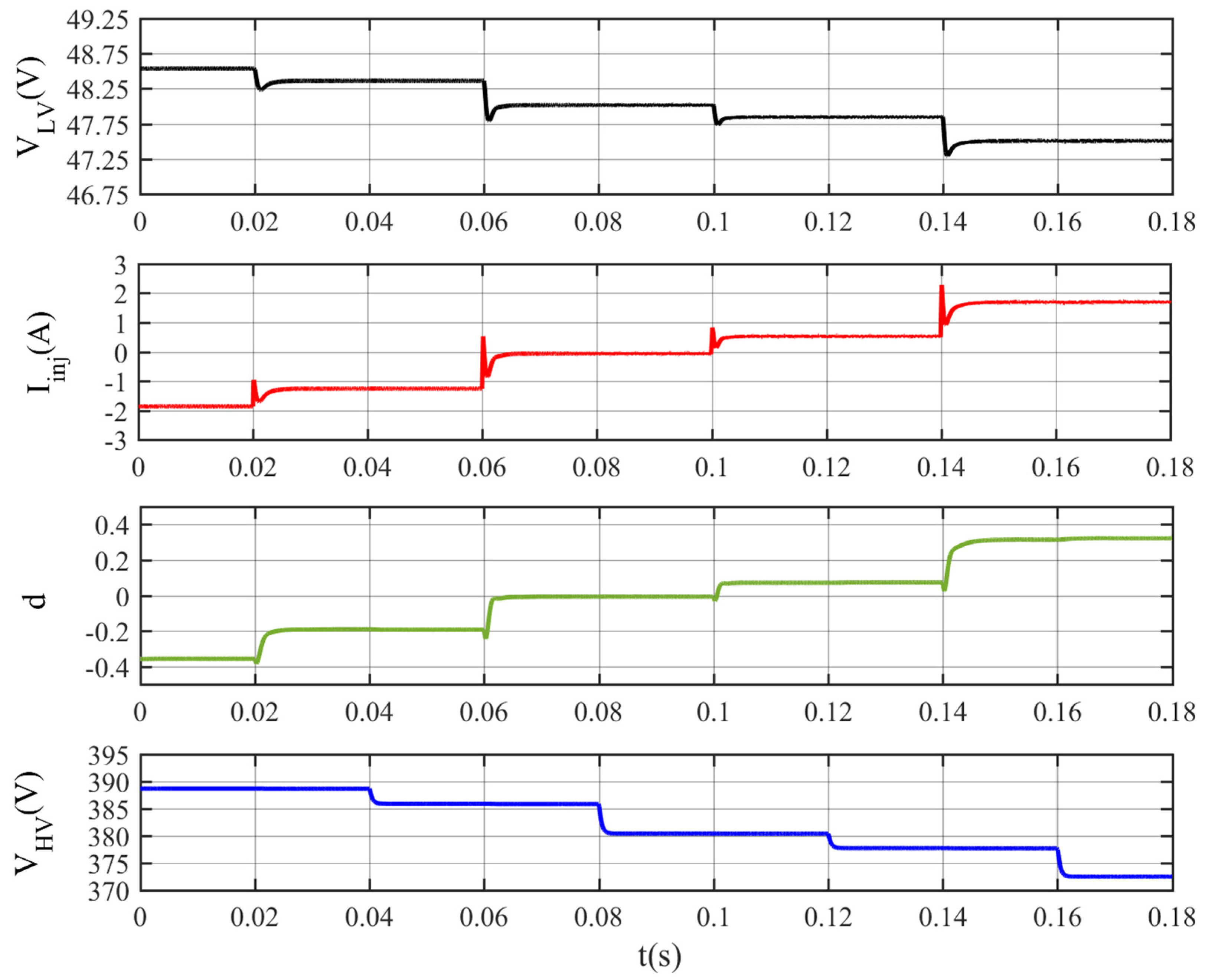

6.1. Simulation Results of DAB as Interlink Converter

6.2. Simulation Results of Dual DC Buses Nanogrid

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| RES | Renewable Energy Source |

| ICT | Information and Communication Technology |

| DER | Distributed Energy Resources |

| NZEH | Net-Zero Energy Homes |

| ELV | Extra Low Voltage |

| LV | Low Voltage |

| HV | High Voltage |

| DBS | DC Bus Signaling |

| MPPT | Maximum Power Point Tracking |

| SoC | State of Charge |

| DAB | Dual Active Bridge |

| SPS | Single-Phase Shift |

| d | Phase-Shift Ratio |

| PWM | Pulse Width Modulation |

References

- Alepuz, S.; Busquets-Monge, S.; Bordonau, J.; Gago, J.; Gonzalez, D.; Balcells, J. Interfacing Renewable Energy Sources to the Utility Grid Using a Three-Level Inverter. IEEE Trans. Ind. Electron. 2006, 53, 1504–1511. [Google Scholar] [CrossRef]

- Gungor, V.C.; Sahin, D.; Kocak, T.; Ergut, S.; Buccella, C.; Cecati, C.; Hancke, G.P. Smart Grid Technologies: Communication Technologies and Standards. IEEE Trans. Ind. Inform. 2011, 7, 529–539. [Google Scholar] [CrossRef]

- Bryan, J.; Duke, R.; Round, S. Distributed generation-nanogrid transmission and control options. In Proceedings of the International Power Engineering Conference, Singapore, 27–29 November 2003; pp. 341–346. [Google Scholar]

- Leonori, S.; Rizzoni, G.; Mascioli, F.M.F.; Rizzi, A. Intelligent energy flow management of a nanogrid fast charging station equipped with second life batteries. Int. J. Electr. Power Energy Syst. 2020, 127, 106602. [Google Scholar] [CrossRef]

- Rubio, C.; Siddiqui, A. Shape of the microgrid. In Proceedings of the 2001 IEEE Power Engineering Society Winter Meeting, Columbus, OH, USA, 28 January–1 February 2001; pp. 150–153. [Google Scholar]

- Lakhina, U.; Elamvazuthi, I.; Badruddin, N.; Jangra, A.; Truong, B.-H.; Guerrero, J.M. A Cost-Effective Multi-Verse Optimization Algorithm for Efficient Power Generation in a Microgrid. Sustainability 2023, 15, 6358. [Google Scholar] [CrossRef]

- Boroyevich, D.; Cvetković, I.; Dong, D.; Burgos, R.; Wang, F.; Lee, F. Future electronic power distribution systems a contemplative view. In Proceedings of the 2010 12th International Conference on Optimization of Electrical and Electronic Equipment, Brasov, Romania, 20–22 May 2010. [Google Scholar]

- Sartori, I.; Napolitano, A.; Voss, K. Net zero energy buildings: A consistent definition framework. Energy Build. 2012, 48, 220–232. [Google Scholar] [CrossRef]

- Muhsen, H.; Alkhraibat, A.; Al-Halhouli, A. Real-Time Simulation and Energy Management Attainment of Microgrids. Sustainability 2023, 15, 2696. [Google Scholar] [CrossRef]

- Al-Quraan, A.; Al-Mhairat, B.; Malkawi, A.M.A.; Radaideh, A.; Al-Masri, H.M.K. Optimal Prediction of Wind Energy Resources Based on WOA—A Case Study in Jordan. Sustainability 2023, 15, 3927. [Google Scholar] [CrossRef]

- Hammerstrom, D.J. AC Versus DC Distribution Systemsdid We Get it Right? In Proceedings of the 2007 IEEE Power Engineering Society General Meeting, Tampa, FL, USA, 24–28 June 2007; pp. 1–5. [Google Scholar]

- Silveira, J.P.C.; Neto, P.J.D.S.; Barros, T.A.d.S.; Filho, E.R. Power management of energy storage system with modified interlinking converters topology in hybrid AC/DC microgrid. Int. J. Electr. Power Energy Syst. 2021, 130, 106880. [Google Scholar] [CrossRef]

- Malkawi, A.; Lopes, L.A.C. Control of the power electronics interface of a PV source in a smart residential DC nanogrid. In Proceedings of the 2016 IEEE Canadian Conference on Electrical and Computer Engineering (CCECE), Vancouver, BC, Canada, 15–18 May 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Committee ISC. IEEE Standard for Interconnecting Distributed Resources with Electric Power Systems; Institute of Electrical and Electronics Engineers: New York, NY, USA, 2003.

- Dong, D.; Thacker, T.; Burgos, R.; Boroyevich, D.; Wang, F.; Giewont, B. Control design and experimental verification of a multi-function single-phase bidirectional PWM converter for renewable energy systems. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009; pp. 1–10. [Google Scholar]

- Thacker, T.; Burgos, R.; Wang, F.; Boroyevich, D. Single-phase islanding detection based on phase-locked loop stability. In Proceedings of the 2009 IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 3371–3377. [Google Scholar]

- Roggia, L.; Schuch, L.; Baggio, J.E.; Rech, C.; Pinheiro, J.R. Integrated Full-Bridge-Forward DC-DC Converter for a Residential Microgrid Application. IEEE Trans Power Electron 2013, 28, 1728–1740. [Google Scholar] [CrossRef]

- Tazy, A.; Samy, M.M.; Ghalib, M.A. Enhancement and Control of Reactive Power Sharing Utilizing Circulating Current in AC Microgrids. In Proceedings of the 2022 23rd International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 13–15 December 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Balog, R.S.; Krein, P.T. Bus Selection in Multibus DC Microgrids. IEEE Trans. Power Electron. 2010, 26, 860–867. [Google Scholar] [CrossRef]

- Chen, J.; Chen, J.; Chen, R.; Zhang, X.; Gong, C. Decoupling control of the non-grid-connected wind power system with the droop strategy based on a DC micro-grid. In Proceedings of the 2009 World Non-Grid-Connected Wind Power and Energy Conference, Nanjing, China, 24–26 September 2009; pp. 1–6. [Google Scholar] [CrossRef]

- Blaabjerg, F.; Consoli, A.; Ferreira, J.; Vanwyk, J. Special Feature The Future of Electronic Power Processing and Conversion. IEEE Trans. Ind. Appl. 2005, 41, 3–8. [Google Scholar] [CrossRef]

- Correa, J.M.; Farret, F.A.; Simoes, M.; Ramos, D.B.; Ferrigolo, F.Z. Aspects of the integration of alternative sources of energy for application in distributed generation systems. In Proceedings of the XI Brazilian Power Electronics Conference, Natal, Brazil, 11–15 September 2011; pp. 819–824. [Google Scholar] [CrossRef]

- Biczel, P. Power Electronic Converters in DC Microgrid. In Proceedings of the 2007 Compatibility in Power Electronics, Gdansk, Poland, 29 May–1 June 2007; pp. 1–6. [Google Scholar]

- Sun, K.; Zhang, L.; Xing, Y.; Guerrero, J.M. A Distributed Control Strategy Based on DC Bus Signaling for Modular Photovoltaic Generation Systems with Battery Energy Storage. IEEE Trans. Power Electron. 2011, 26, 3032–3045. [Google Scholar] [CrossRef]

- Xu, L.; Chen, D. Control and Operation of a DC Microgrid With Variable Generation and Energy Storage. IEEE Trans. Power Deliv. 2011, 26, 2513–2522. [Google Scholar] [CrossRef]

- E-Merge Alliance. Public Overview of the EMerge Alliance Data. Telecom Center Standard Version. 2014. Available online: https://www.emergealliance.org/standards/data-telecom/ (accessed on 26 June 2023).

- E-Merge Alliance. Public Overview of the EMerge Alliance Occupied Space Standard. 2015. Available online: https://www.emergealliance.org/standards/occupied-space-2/ (accessed on 26 June 2023).

- Liu, C.; Chau, K.; Diao, C.; Zhong, J.; Zhang, X.; Gao, S.; Wu, D. A new DC micro-grid system using renewable energy and electric vehicles for smart energy delivery. In Proceedings of the 2010 IEEE Vehicle Power and Propulsion Conference, Lille, France, 1–3 September 2010; pp. 1–6. [Google Scholar] [CrossRef]

- Lago, J.; Heldwein, M.L. Operation and Control-Oriented Modeling of a Power Converter for Current Balancing and Stability Improvement of DC Active Distribution Networks. IEEE Trans. Power Electron. 2011, 26, 877–885. [Google Scholar] [CrossRef]

- Malkawi, A.; Lopes, L. A novel seamless control algorithm for a single-stage photovoltaic interface employing DC bus signaling. Int. J. Electr. Power Energy Syst. 2019, 113, 90–103. [Google Scholar] [CrossRef]

- Malkawi, A.M.A.; Lopes, L.A.C. Improved Dynamic Voltage Regulation in a Droop Controlled DC Nanogrid Employing Independently Controlled Battery and Supercapacitor Units. Appl. Sci. 2018, 8, 1525. [Google Scholar] [CrossRef]

- Malkawi, A.M.A.; Al-Quraan, A.; Lopes, L.A.C. Extending DC Bus Signaling and Droop Control for Hybrid Storage Units to Improve the Energy Management and Voltage Regulation. Inventions 2022, 7, 55. [Google Scholar] [CrossRef]

- Ghalib, M.A.; Samy, M.M. Magnification of Performance Operation for Low Voltage DC Microgrids Based on Adaptive Droop Control Technique. In Proceedings of the 2021 22nd International Middle East Power Systems Conference (MEPCON), Assiut, Egypt, 14–16 December 2021; pp. 424–429. [Google Scholar] [CrossRef]

- Guerrero, J.M.; Vasquez, J.C.; Matas, J.; de Vicuna, L.G.; Castilla, M. Hierarchical Control of Droop-Controlled AC and DC Microgrids—A General Approach Toward Standardization. IEEE Trans. Ind. Electron. 2011, 58, 158–172. [Google Scholar] [CrossRef]

- Noroozian, R.; Abedi, M.; Gharehpetian, G.; Hosseini, S. Combined operation of DC isolated distribution and PV systems for supplying unbalanced AC loads. Renew. Energy 2009, 34, 899–908. [Google Scholar] [CrossRef]

- Justo, J.J.; Mwasilu, F.; Lee, J.; Jung, J. AC-microgrids versus DC-microgrids with distributed energy resources: A review. Renew. Sustain. Energy Rev. 2013, 24, 387–405. [Google Scholar] [CrossRef]

- Kakigano, H.; Nishino, A.; Ise, T. Distribution voltage control for DC microgrid with fuzzy control and gain-scheduling control. In Proceedings of the 8th International Conference on Power Electronics–ECCE Asia, Jeju, Republic of Korea, 30 May–3 June 2011; pp. 256–263. [Google Scholar] [CrossRef]

- Chedid, R.; Rahman, S. Unit sizing and control of hybrid wind-solar power systems. IEEE Trans. Energy Convers. 1997, 12, 79–85. [Google Scholar] [CrossRef]

- Dalbon, W.; Roscia, M.; Zaninelli, D.; Leva, S. Hybrid photovoltaic system control for enhancing sustainable energy. In Proceedings of the IEEE Power Engineering Society Summer Meeting, Chicago, IL, USA, 21–25 July 2002. [Google Scholar] [CrossRef]

- Tsikalakis, A.G.; Hatziargyriou, N.D. Centralized control for optimizing microgrids operation. In Proceedings of the 2011 IEEE Power and Energy Society General Meeting, Detroit, MI, USA, 24–28 July 2011; pp. 1–8. [Google Scholar] [CrossRef]

- Bhaskara, S.N.; Chowdhury, B.H. Microgrids—A review of modeling, control, protection, simulation and future potential. In Proceedings of the 2012 IEEE Power and Energy Society General Meeting, San Diego, CA, USA, 22–26 July 2012; pp. 1–7. [Google Scholar]

- Zhang, L.; Wang, Y.; Cheng, L.; Kang, W. A Three-Parameter Adaptive Virtual DC Motor Control Strategy for a Dual Active Bridge DC–DC Converter. Electronics 2023, 12, 1412. [Google Scholar] [CrossRef]

- Zhang, W.; Lee, F.C.; Huang, P.-Y. Energy management system control and experiment for future home. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 3317–3324. [Google Scholar] [CrossRef]

- Karlsson, P.; Svensson, J. DC bus voltage control for a distributed power system. IEEE Trans. Power Electron. 2003, 18, 1405–1412. [Google Scholar] [CrossRef]

- Kim, J.-W.; Choi, H.-S.; Cho, B.H. A novel droop method for converter parallel operation. IEEE Trans. Power Electron. 2002, 17, 25–32. [Google Scholar] [CrossRef]

- Kurohane, K.; Senjyu, T.; Yona, A.; Urasaki, N.; Muhando, E.B.; Funabashi, T. A high quality power supply system with DC smart grid. In Proceedings of the IEEE PES T&D 2010, New Orleans, LA, USA, 19–22 April 2010; pp. 1–6. [Google Scholar] [CrossRef]

- Kollimalla, S.K.; Mishra, M.K.; Narasamma, N.L. Design and Analysis of Novel Control Strategy for Battery and Supercapacitor Storage System. IEEE Trans Sustain. Energy 2014, 5, 1137–1144. [Google Scholar] [CrossRef]

- Kolluri, S.; Narasamma, N.L. Analysis, modeling, design and implementation of average current mode control for interleaved boost converter. In Proceedings of the 2013 IEEE 10th International Conference on Power Electronics and Drive Systems (PEDS), Kitakyushu, Japan, 22–25 April 2013; pp. 280–285. [Google Scholar] [CrossRef]

| The Parameter | The Value |

|---|---|

| Transformer turns ratio (n) | 0.25 |

| Leakage inductance (L) | 300 µH |

| Switching frequency (fs) | 20 kHz |

| HV and LV capacitors (CHV = CLV) | 1500 µF |

| The LV DC bus threshold voltage (VNL_LV) | 49.25 V |

| The LV droop constant (RdLV) | 0.289 Ω |

| The HV DC bus threshold voltage (VNL_HV) | 390 V |

| The HV droop constant (RdHV) | 0.289 Ω |

| The load resistance (RLoad) | 10 Ω |

| Time (s) | Load (Ω) | VHV(V) | IPV_380(A) | IG(A) | IB_380(A) | ILoad_380(A) |

|---|---|---|---|---|---|---|

| Initially | 305 | 379.3 | 13.2 | 1.8 | −12.2 | 1.2 |

| t = 0.2 | 63.4 | 378 | 13.2 | 5.2 | −10.5 | 6 |

| t = 0.4 | 35.4 | 376.7 | 13.25 | 8.6 | −8.8 | 10.7 |

| t = 0.6 | 24.5 | 375.3 | 13.3 | 12.3 | −7 | 15.3 |

| t = 0.8 | 18.8 | 374 | 13.3 | 15.6 | −5.3 | 20 |

| Time (s) | Load (Ω) | VLV(V) | IPV_48(A) | Iint(A) | IB_48(A) | ILoad_48(A) |

|---|---|---|---|---|---|---|

| Initially | 40 | 47.94 | 41.7 | 2 | −42 | 1.2 |

| t = 0.1 | 7 | 47.86 | 41.7 | 4.8 | −40 | 6.8 |

| t = 0.3 | 3 | 47.75 | 41.7 | 8.7 | −35 | 16 |

| t = 0.5 | 1.95 | 47.62 | 42 | 13 | −30 | 24.4 |

| t = 0.7 | 1.64 | 47.56 | 42 | 15.2 | −28 | 29 |

| t = 0.9 | 1.27 | 47.45 | 42 | 19 | −24 | 37.5 |

| Time (s) | Load (Ω) | VHV(V) | IPV_380(A) | IG(A) | IB_380(A) | ILoad_380(A) |

|---|---|---|---|---|---|---|

| Initially | 305 | 378 | 13.2 | 0 | −10.5 | 1.2 |

| t = 0.2 | 63.4 | 374.3 | 13.25 | 0 | −5.6 | 5.9 |

| t = 0.4 | 35.4 | 370.5 | 13.4 | 0 | −0.5 | 10.5 |

| t = 0.5 | No change | 370 | 13.5 | 0 | 0 | 10.5 |

| t = 0.6 | 24.5 | 368 | 13.5 | 0 | 2.5 | 15 |

| t = 0.8 | 18.8 | 364.7 | 13.6 | 0 | 7 | 19.5 |

| Time (s) | Load (Ω) | VLV(V) | IPV_48(A) | Iint(A) | IB_48(A) | ILoad_48(A) |

|---|---|---|---|---|---|---|

| Initially | 40 | 47.94 | 41.7 | 2 | −42 | 1.2 |

| t = 0.1 | 7 | 47.86 | 41.7 | 4.8 | −40 | 6.8 |

| t = 0.3 | 3 | 47.75 | 41.7 | 8.7 | −35 | 16 |

| t = 0.5 | 1.95 | 47.62 | 42 | 13 | −30 | 24.4 |

| t = 0.6 | No change | 47.28 | 42 | 0 | −18 | 24.2 |

| t = 0.7 | 1.64 | 47.16 | 42 | 0 | −14 | 28.8 |

| t = 0.9 | 1.27 | 46.93 | 42 | 0 | −6 | 37 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Malkawi, A.M.A.; AL-Quraan, A.; Lopes, L.A.C. A Droop-Controlled Interlink Converter for a Dual DC Bus Nanogrid with Decentralized Control. Sustainability 2023, 15, 10394. https://doi.org/10.3390/su151310394

Malkawi AMA, AL-Quraan A, Lopes LAC. A Droop-Controlled Interlink Converter for a Dual DC Bus Nanogrid with Decentralized Control. Sustainability. 2023; 15(13):10394. https://doi.org/10.3390/su151310394

Chicago/Turabian StyleMalkawi, Ahmad M. A., Ayman AL-Quraan, and Luiz A. C. Lopes. 2023. "A Droop-Controlled Interlink Converter for a Dual DC Bus Nanogrid with Decentralized Control" Sustainability 15, no. 13: 10394. https://doi.org/10.3390/su151310394

APA StyleMalkawi, A. M. A., AL-Quraan, A., & Lopes, L. A. C. (2023). A Droop-Controlled Interlink Converter for a Dual DC Bus Nanogrid with Decentralized Control. Sustainability, 15(13), 10394. https://doi.org/10.3390/su151310394