Hysteresis Behavior of the Donor–Acceptor-Type Ambipolar Semiconductor for Non-Volatile Memory Applications

Abstract

:1. Introduction

2. Materials and Methods

2.1. Synthesis of PDPPT-TT

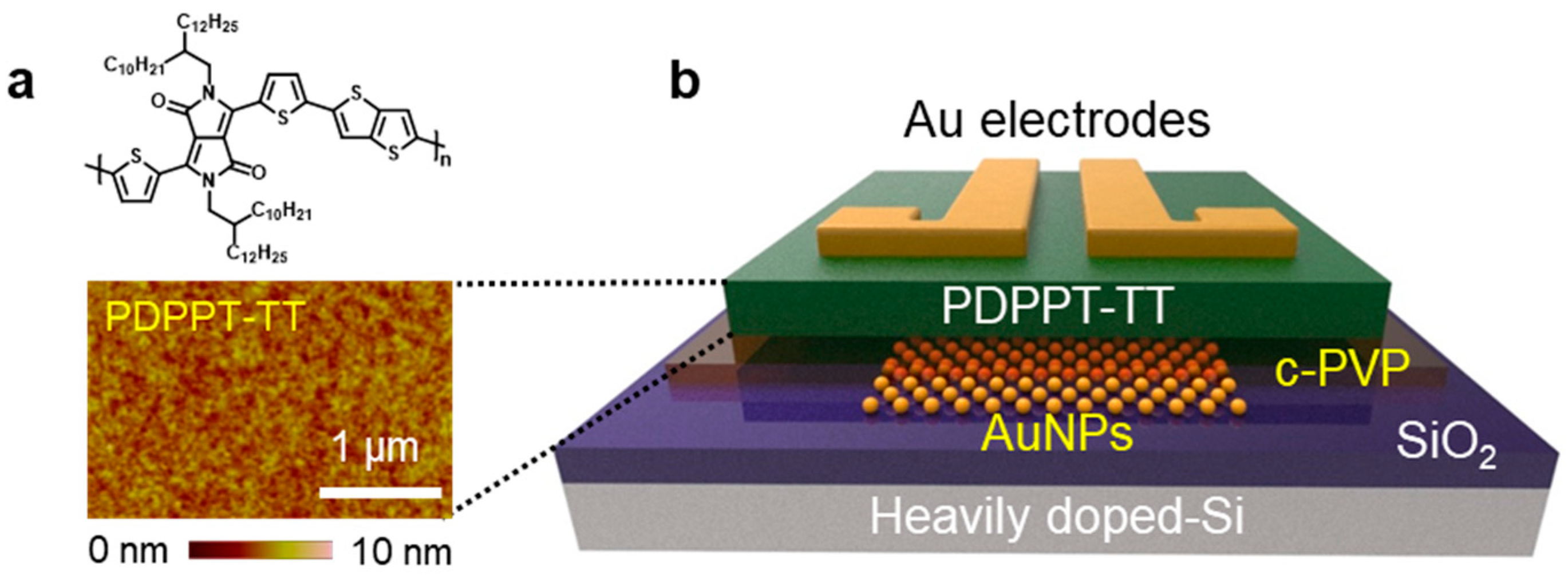

2.2. PDPPT-TT-Based Transistor Fabrication

3. Results and Discussion

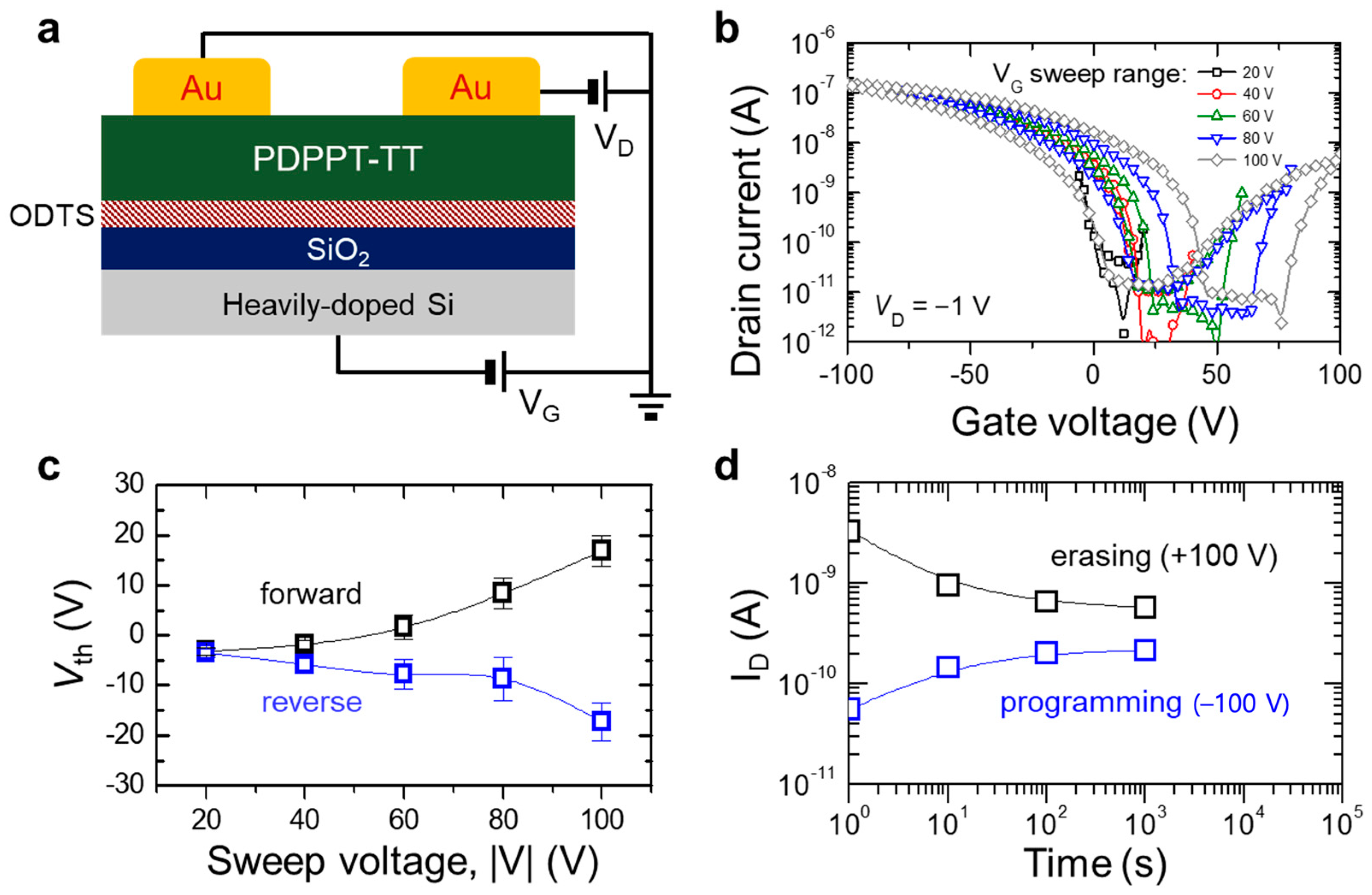

3.1. Electrical Properties of PDPPT-TT

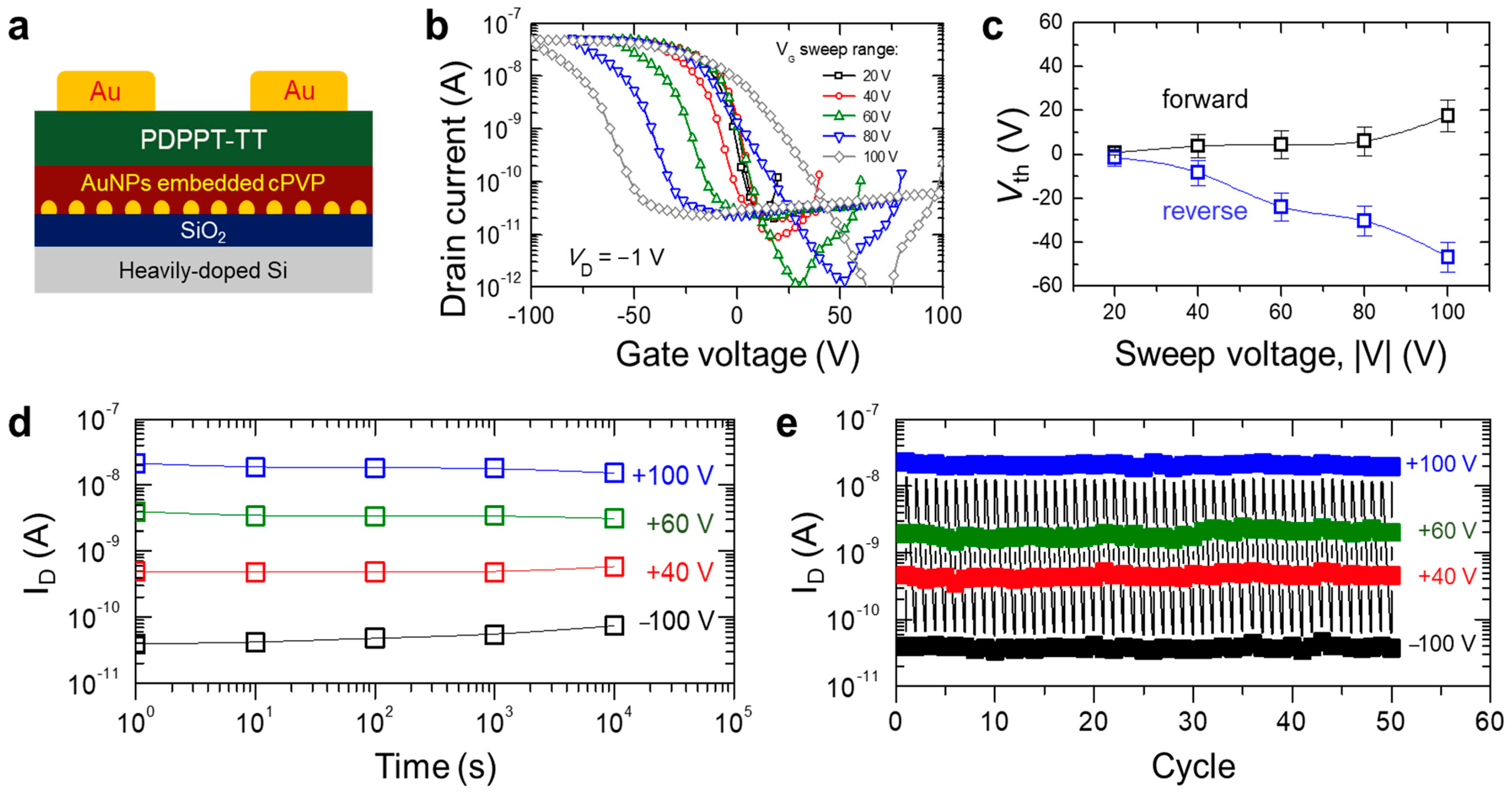

3.2. Non-Volatile Memory Behavior of PDPPT-TT-Based Device

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Conflicts of Interest

References

- Chua, L.L.; Zaumseil, J.; Chang, J.F.; Ou, E.C.W.; Ho, P.K.H.; Sirringhaus, H.; Friend, R.H. General observation of n-type field-effect behaviour in organic semiconductors. Nature 2005, 434, 194–199. [Google Scholar] [CrossRef] [PubMed]

- Yan, H.; Chen, Z.H.; Zheng, Y.; Newman, C.; Quinn, J.R.; Dotz, F.; Kastler, M.; Facchetti, A. A high-mobility electron-transporting polymer for printed transistors. Nature 2009, 457, 679. [Google Scholar] [CrossRef] [PubMed]

- Zaumseil, J.; Sirringhaus, H. Electron and ambipolar transport in organic field-effect transistors. Chem. Rev. 2007, 107, 1296–1323. [Google Scholar] [CrossRef] [PubMed]

- Anthony, J.E.; Facchetti, A.; Heeney, M.; Marder, S.R.; Zhan, X.W. n-type organic semiconductors in organic electronics. Adv. Mater. 2010, 22, 3876–3892. [Google Scholar] [CrossRef] [PubMed]

- Zhang, X.T.; Dong, H.L.; Hu, W.P. Organic semiconductor single crystals for electronics and photonics. Adv. Mater. 2018, 30, 1801048. [Google Scholar] [CrossRef] [PubMed]

- Heremans, P. Semiconductor electronics-organic crystals at large. Nature 2006, 444, 828. [Google Scholar] [CrossRef] [PubMed]

- Arias, A.C.; MacKenzie, J.D.; McCulloch, I.; Rivnay, J.; Salleo, A. Materials and applications for large area electronics: Solution-based approaches. Chem. Rev. 2010, 110, 3–24. [Google Scholar] [CrossRef] [PubMed]

- Bronstein, H.; Chen, Z.Y.; Ashraf, R.S.; Zhang, W.M.; Du, J.P.; Durrant, J.R.; Tuladhar, P.S.; Song, K.; Watkins, S.E.; Geerts, Y.; et al. Thieno[3,2-b]thiophene-Diketopyrrolopyrrole-containing polymers for high-performance organic field-effect transistors and organic photovoltaic devices. J. Am. Chem. Soc. 2011, 133, 3272–3275. [Google Scholar] [CrossRef] [PubMed]

- Crouch, D.J.; Skabara, P.J.; Lohr, J.E.; McDouall, J.J.W.; Heeney, M.; McCulloch, I.; Sparrowe, D.; Shkunov, M.; Coles, S.J.; Horton, P.N.; et al. Thiophene and selenophene copolymers incorporating fluorinated phenylene units in the main chain: Synthesis, characterization, and application in organic field-effect transistors. Chem. Mater. 2005, 17, 6567–6578. [Google Scholar] [CrossRef]

- Lei, T.; Cao, Y.; Zhou, X.; Peng, Y.; Bian, J.; Pei, J. Systematic investigation of isoindigo-based polymeric field-effect transistors: Design strategy and impact of polymer symmetry and backbone curvature. Chem. Mater. 2012, 24, 1762–1770. [Google Scholar] [CrossRef]

- Mei, J.G.; Kim, D.H.; Ayzner, A.L.; Toney, M.F.; Bao, Z.A. Siloxane-terminated solubilizing side chains: Bringing conjugated polymer backbones closer and boosting hole mobilities in thin-film transistors. J. Am. Chem. Soc. 2011, 133, 20130–20133. [Google Scholar] [CrossRef] [PubMed]

- Tsao, H.N.; Cho, D.M.; Park, I.; Hansen, M.R.; Mavrinskiy, A.; Yoon, D.Y.; Graf, R.; Pisula, W.; Spiess, H.W.; Mullen, K. Ultrahigh mobility in polymer field-effect transistors by design. J. Am. Chem. Soc. 2011, 133, 2605–2612. [Google Scholar] [CrossRef] [PubMed]

- Guo, X.G.; Kim, F.S.; Seger, M.J.; Jenekhe, S.A.; Watson, M.D. Naphthalene diimide-based polymer semiconductors: Synthesis, structure-property correlations, and n-channel and ambipolar field-effect transistors. Chem. Mater. 2012, 24, 1434–1442. [Google Scholar] [CrossRef]

- Chen, S.Y.; Meng, Y.Z.; Li, Y.N.; Qu, B.; Zhuo, D.X. Effect of the length and branching point of alkyl side chains on DPP-thieno [3,2-b]thiophene copolymers for organic thin-film transistors. Opt. Mater. 2019, 88, 500–507. [Google Scholar] [CrossRef]

- Kang, W.; Jung, M.; Cha, W.; Jang, S.; Yoon, Y.; Kim, H.; Son, H.J.; Lee, D.K.; Kim, B.; Cho, J.H. High crystalline dithienosilole-cored small molecule semiconductor for ambipolar transistor and nonvolatile memory. ACS Appl. Mater. Inter. 2014, 6, 6589–6597. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Y.; Kim, C.; Lin, J.; Nguyen, T.Q. Solution-processed ambipolar field-effect transistor based on diketopyrrolopyrrole functionalized with benzothiadiazole. Adv. Funct. Mater. 2012, 22, 97–105. [Google Scholar] [CrossRef]

- Chen, H.Y.; Hou, J.H.; Hayden, A.E.; Yang, H.; Houk, K.N.; Yang, Y. Silicon atom substitution enhances interchain packing in a thiophene-based polymer system. Adv. Mater. 2010, 22, 371. [Google Scholar] [CrossRef] [PubMed]

- Welch, G.C.; Bakus, R.C.; Teat, S.J.; Bazan, G.C. Impact of regiochemistry and isoelectronic bridgehead substitution on the molecular shape and bulk organization of narrow bandgap chromophores. J. Am. Chem. Soc. 2013, 135, 2298–2305. [Google Scholar] [CrossRef] [PubMed]

- Li, Y.N.; Singh, S.P.; Sonar, P. A high mobility P-type DPP-Thieno[3,2-b]thiophene copolymer for organic thin-film transistors. Adv. Mater. 2010, 22, 4862. [Google Scholar] [CrossRef] [PubMed]

- Sun, B.; Hong, W.; Aziz, H.; Abukhdeir, N.M.; Li, Y.N. Dramatically enhanced molecular ordering and charge transport of a DPP-based polymer assisted by oligomers through antiplasticization. J. Mater. Chem. C 2013, 1, 4423–4426. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, Y.J.; Kim, J.; Kim, M.J.; Ryu, H.S.; Woo, H.Y.; Cho, J.H.; Kang, J. Hysteresis Behavior of the Donor–Acceptor-Type Ambipolar Semiconductor for Non-Volatile Memory Applications. Micromachines 2021, 12, 301. https://doi.org/10.3390/mi12030301

Choi YJ, Kim J, Kim MJ, Ryu HS, Woo HY, Cho JH, Kang J. Hysteresis Behavior of the Donor–Acceptor-Type Ambipolar Semiconductor for Non-Volatile Memory Applications. Micromachines. 2021; 12(3):301. https://doi.org/10.3390/mi12030301

Chicago/Turabian StyleChoi, Young Jin, Jihyun Kim, Min Je Kim, Hwa Sook Ryu, Han Young Woo, Jeong Ho Cho, and Joohoon Kang. 2021. "Hysteresis Behavior of the Donor–Acceptor-Type Ambipolar Semiconductor for Non-Volatile Memory Applications" Micromachines 12, no. 3: 301. https://doi.org/10.3390/mi12030301

APA StyleChoi, Y. J., Kim, J., Kim, M. J., Ryu, H. S., Woo, H. Y., Cho, J. H., & Kang, J. (2021). Hysteresis Behavior of the Donor–Acceptor-Type Ambipolar Semiconductor for Non-Volatile Memory Applications. Micromachines, 12(3), 301. https://doi.org/10.3390/mi12030301