Abstract

Voltage-controlled oscillators (VCOs) can be an excellent means of converting a magnitude into a readable value. However, their design becomes a real challenge for power-and-area-constrained applications, especially when a linear response is required. This paper presents a VCO for smart dust systems fabricated by 65 nm technology. It is designed to minimize leakage, limit high peak currents and provide an output whose frequency variation is linear with the input voltage, while allowing rail-to-rail input range swing. The oscillator occupies 592 , operates in a frequency range from 43 to 53 Hz and consumes a maximum average power of 210 pW at a supply voltage of 1 V and 4 pW at 0.3 V. In addition, the proposed VCO exhibits a quasi-linear response of frequency vs. supply voltage and temperature, allowing easy temperature compensation with complementary to absolute temperature (CTAT) voltage.

1. Introduction

Autonomous microsystems are systems that require no external power to operate and communicate for a given period of time, while having dimensions smaller than the diameter of a human hair (<100 m). These microsystems enable new uses for electronics, made possible solely by their smaller size, such as sensing in confined spaces, like microfluidic channels [1] or the human body. However, their main disadvantage is that their tiny size results in a very limited power budget and reduced functionality.

Analog-to-digital conversion is one of the first and most important steps to be performed in any system working with signals from the physical world. Traditional ADCs perform this conversion by comparing the signal’s amplitude with respect to a given reference. Still, they tend to be very area- and power-hungry for applications where these two characteristics are severely constrained. In a microsystems context, digitization can be achieved in the time domain by using voltage-controlled oscillators (VCOs), where the input signal is converted to a modulated frequency and the output can be easily digitized by measuring the frequency with counters. However, the main challenge with this type of conversion is to achieve a linear voltage–frequency response, since the resolution of the digitization is highly dependent on the linearity of the VCO. Many VCO-based converters [2] include calibration circuitry, such as look-up tables (LUTs) [3], to linearize their performance, but these take up considerable area and power.

On the other hand, since autonomous microsystems do not need to be fast, a common approach to reducing power consumption is to operate at very low frequencies [4]. However, this is neither easy nor trivial when the large passive components required to generate slow time constants are not affordable, due to area constraints. The most commonly used strategies for designing very slow oscillators within these constraints are based on the use of very low currents, such as those provided by the transistor gate leakage current [5,6] and subthreshold leakage current [7,8,9,10].

Many other systems, apart from autonomous microsystems, require to stay in idle state for very long periods when they enter sleep mode, to save power [5]. Most of the time, only a few subsystems remain active, and the wake-up timer is always one of them. Consequently, wake-up timers must consume very little energy, making ultra-low-frequency- and -power oscillators very suitable for these cases. It can also be interesting to put the system into hibernation for a longer or shorter period, depending on a certain magnitude or condition, so it is desirable to equip these oscillators with a simple mechanism to vary their frequency without significantly worsening the energy consumption.

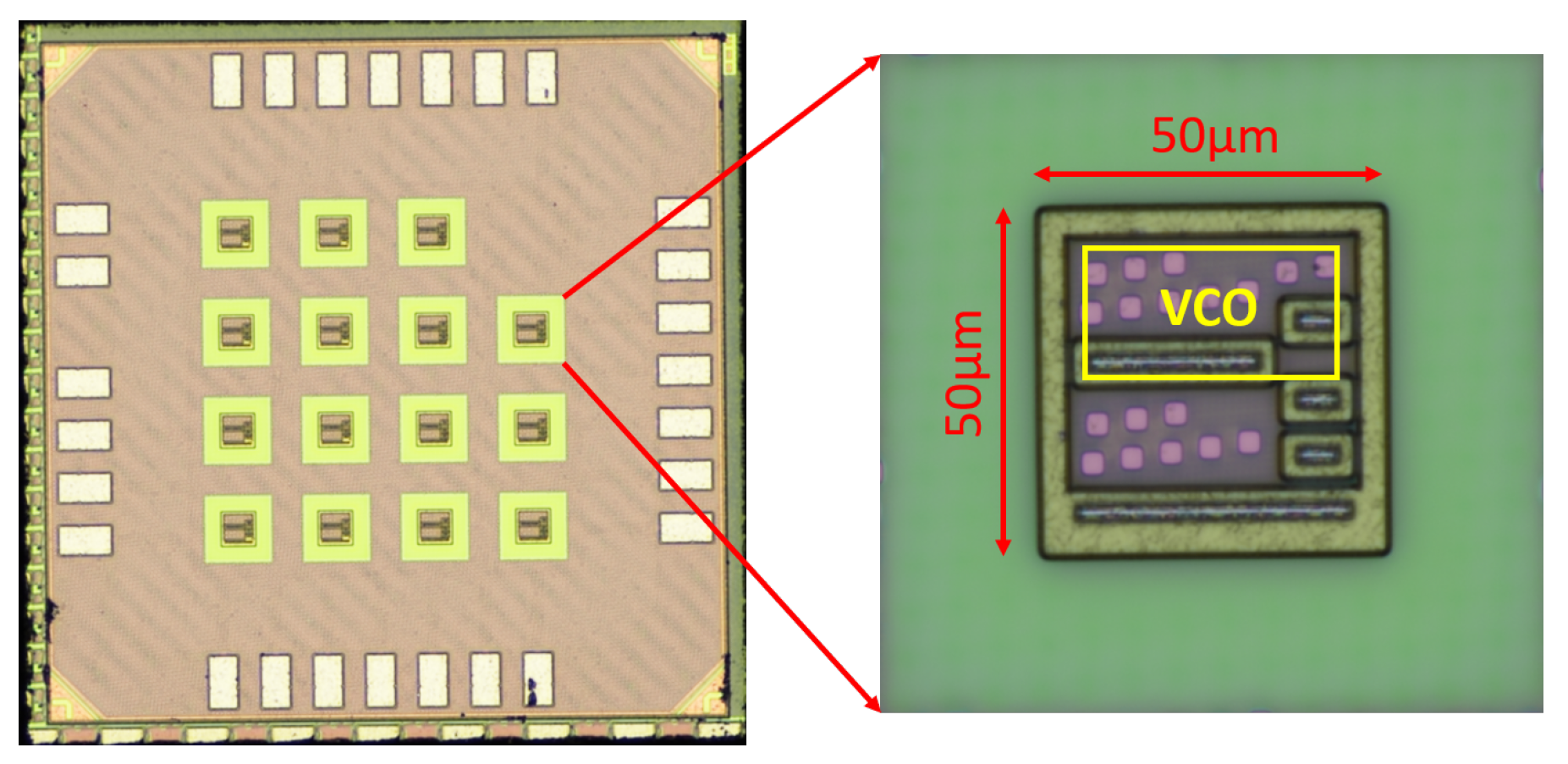

Our target scenario is a special case of autonomous microsystem, the second generation of MIT SynCells [11], which includes a 50 × 50 Si chip that, among other tasks, interfaces the analog voltage coming from a sensor. Given the limited area and power, voltage-to-frequency conversion [12] emerges as an interesting way to perform digitization. In this paper, we propose a highly linear VCO with ultra-low area, power and frequency. It is important to note that no reported ADC comes close to meeting the very stringent constraints of working in the sub-nW power regime and cell size scale. The chip was designed and manufactured using 65 nm commercial CMOS technology. This technology provides a good compromise between a small transistor size, which directly translates into die area reduction and affordable variability, and short channel effects and matching issues, which mostly complicate the design of the analog blocks of the microsystem.

The main contributions of this work are as follows:

- Design of a 65 nm ultra-low frequency–area–power VCO with linearized response of the frequency vs. the control voltage.

- The proposed linearization method is applicable to other oscillator structures and any available supply range.

- Quasi-linear response of frequency vs. supply voltage and temperature, making it easy to achieve temperature compensation with a complementary to absolute temperature (CTAT) voltage supply type.

The paper is organized as follows. First, we introduce the microsystem in which the VCO will operate. Next, the delay element used in the oscillator is presented along with the constraints that drove the entire design process. The proposed VCO is then described and analyzed. Finally, the results are presented and some conclusions are drawn.

2. Overall System Description and Design Constraints

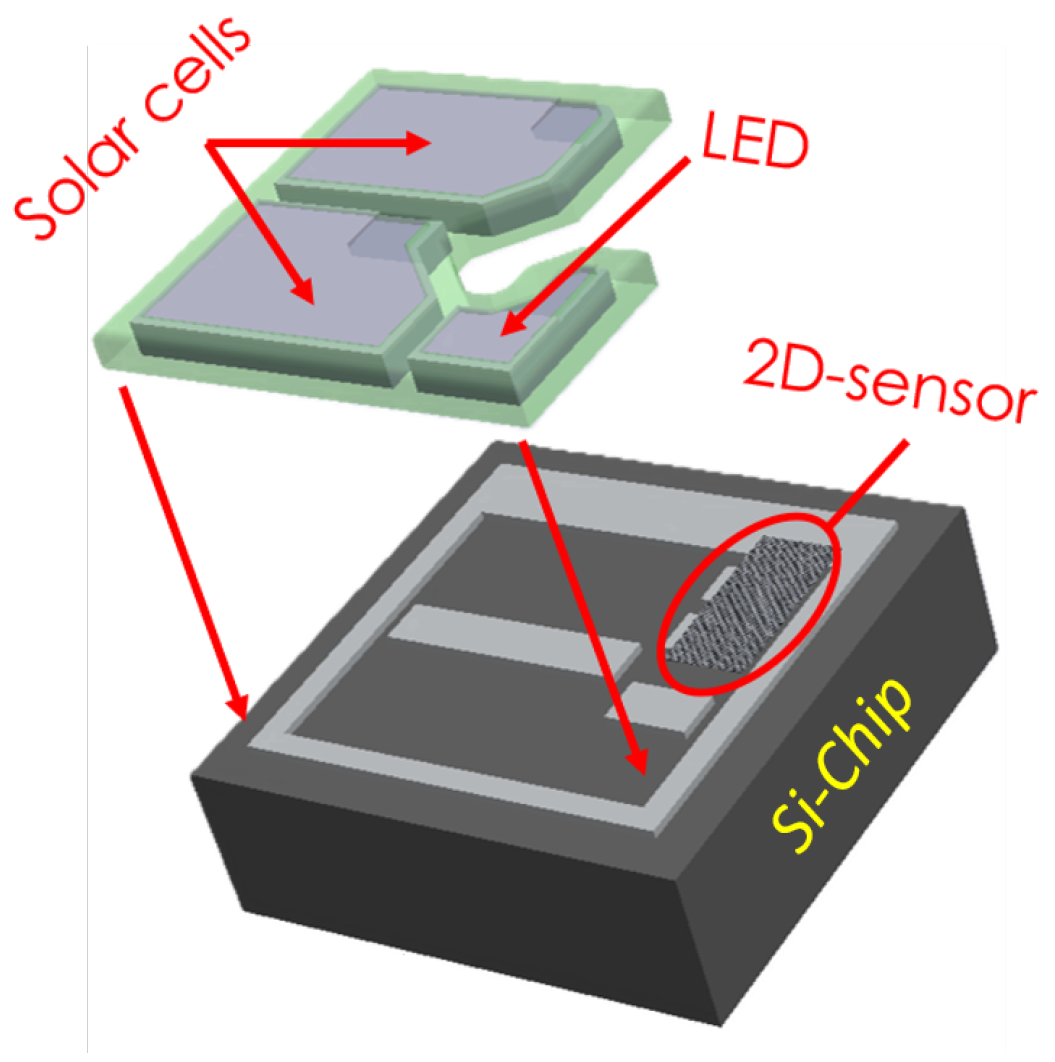

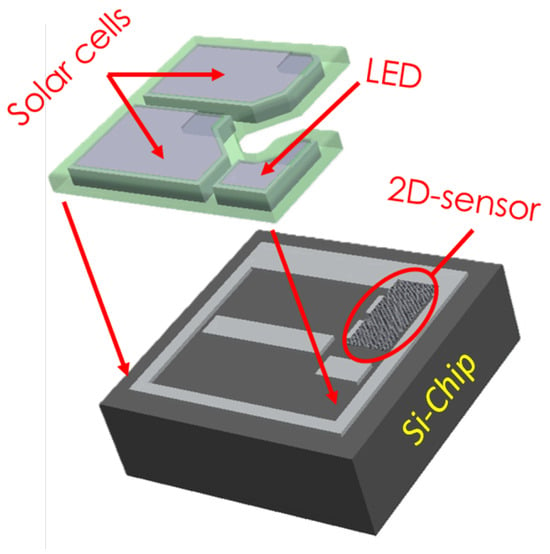

Figure 1 shows a 3-D representation of the integration of the targeted 50 × 50 MIT microsystem for which this VCO was designed. The second generation of SynCells consists of two solar cells connected in series for energy harvesting, a -based sensor, a LED for optical communication and a CMOS Si-chip that regulates the power generated by the solar cells and drives the LED while serving as the carrier for the rest of the microsystem elements. In this way, the information captured by the sensor is transmitted to the outside world through light pulses of varying frequency. The sensor is composed of two -based devices set in a voltage divider configuration. One of them is passivated while the other one is sensitive to chemical exposure. This sensor setup converts the change of resistance in a voltage change that can swing from 0.2 to 0.8 , depending on the chemical concentration. The VCO described in this paper converts the voltage from the sensor into a variable-frequency square-wave signal. The output of the VCO is then used by the LED driver to control the current flow to the LED, causing the LED to flash at a frequency proportional to the physical magnitude being measured. In this way, the sensor information is communicated to the receiver, which captures the light pulses with a CCD camera.

Figure 1.

Integration scheme for the SynCell.

The extremely reduced size of the microsystem necessitates that the implemented solar cells are also very small (23 × 35 ). Therefore, the generated power was particularly limited for this scenario. Before integrating the microsystem, a solar cell was tested in-lab, to determine the power budget of the design. For the microsystem to be able to be powered on low-energetic light, such as ambiance light, a constrained power budget of only 200 nA was estimated. The LED requires at least 60 nA to become visible and the sensor can draw up to 100 nA, depending on the chemical concentration.

Due to its very weak nature, the microsystem’s power source can collapse if the required current exceeds certain limits, causing a critical voltage drop that will shut down the system. Therefore, a sub-nW VCO is highly desirable for the system. However, it is important not only to keep the average power consumption within affordable limits but also to monitor the transient power peaks carefully. Even if these peaks are not large enough to collapse the system, they can cause variations in the supply voltage that can affect the precision with which the system operates. Hence, peak currents in the order of nA are targeted for the VCO, so as not to interfere with the proper operation of the solar cells.

In the first in vitro application of the SynCell, the measured magnitude is a chemical compound known as putrescine, which is a diamine present in all organisms [13]. In meat or fish, its concentration increases as decomposition begins, making it a natural bioindicator of food quality [14]. Additionally, putrescine can be an indicator of cell proliferation and cell growth [15]. In this way, it is particularly relevant in plants [16]. The absence of putrescine in plants is associated with an increase in both parasite and fungal populations.

As a result, autonomous tracking of putrescine concentrations in a very localized manner shows many beneficial use cases.

3. Sub-Threshold Leakage-Based Delay Element

Most oscillators designed for very slow frequencies currently use large R, L and C elements or frequency dividers that take up too much area. However, we can use the sub-threshold leakage currents of CMOS transistors to generate large time constants, together with a reduction in short circuit currents, by creating very steep slopes through positive feedback. This approach results in ultra-low power consumption while keeping the area under very low limits. To achieve this, we used the element proposed in [7] as a starting point for our voltage-controlled oscillator. However, when this element is scaled down, important modifications are required, to achieve ultra-low frequency–area–power goals.

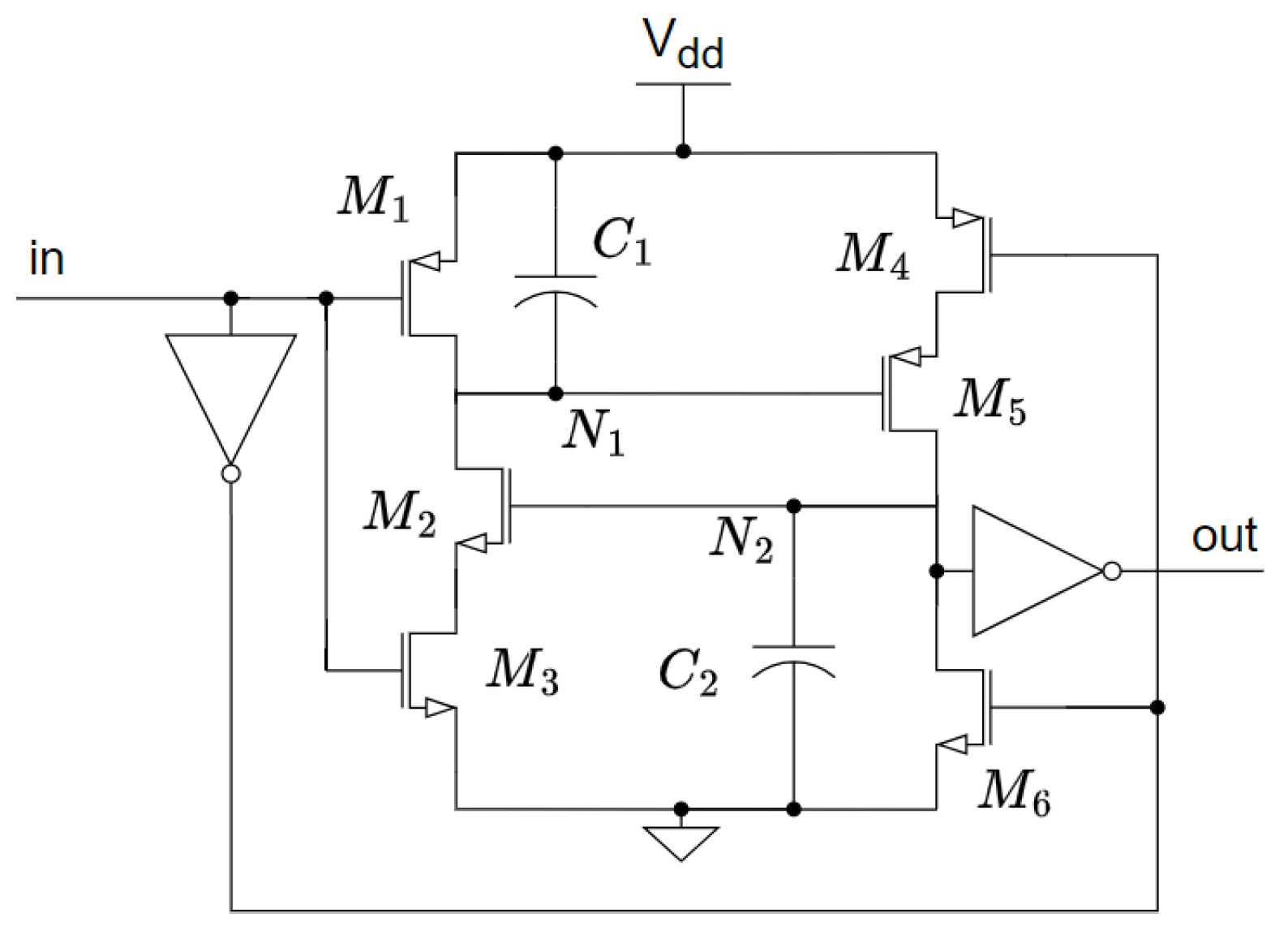

The delay element [7] is based on a thyristor structure, as is shown in Figure 2. To explain how it works, let us assume that the input is low, which causes transistors and to be on and and to be off. This leads node to charge to and to discharge to GND. Consequently, transistors and are off. A transition from low to high of the signal In is then assumed. and are now off while and are turned on. The leakage current of is then used to charge and the leakage current of discharges the negative terminal of . When the voltage on becomes greater than the threshold voltage, , becomes conductive, fully discharging , which exponentially increases the conductivity of and, thus, the voltage on . This positive feedback loop ensures that the transition of the output node is slow when all transistors are in the sub-threshold region and fast when the transistors are conducting. Although the overall power consumption is very low, peak currents in the microampere range have been observed during the short period when the transistors are conducting. These currents represent an excessive power demand if energy harvesters were to power the system, and they must be significantly reduced.

Figure 2.

Leakage-based delay element.

Eventually, the delay provided by this circuit is given by

The full oscillator consists of N cascaded delay elements arranged and connected as a ring oscillator with a period N-times the delay of a single delay element.

At the same time, ref. [7] suggested a method to make the frequency controllable. By adding four transistors, the currents used to charge and discharge can be increased or decreased. However, their structure does not satisfy several design features that we consider critical for our target applications:

- The V-f response is highly non-linear; it follows an exponential equation, which results in a poor resolution when this VCO is used for time domain digitization.

- The power consumption grows exponentially with the control voltage, a critical drawback for ultra-low power systems.

- The input range does not support a rail-to-rail input swing, which is also necessary for time-domain digitization.

- Important current peaks, in the microampere range, were found in the structure presented in [7], which can cause some energy harvesters to collapse.

In this work, a highly linear VCO is presented, to overcome all these issues.

4. Proposed Structure

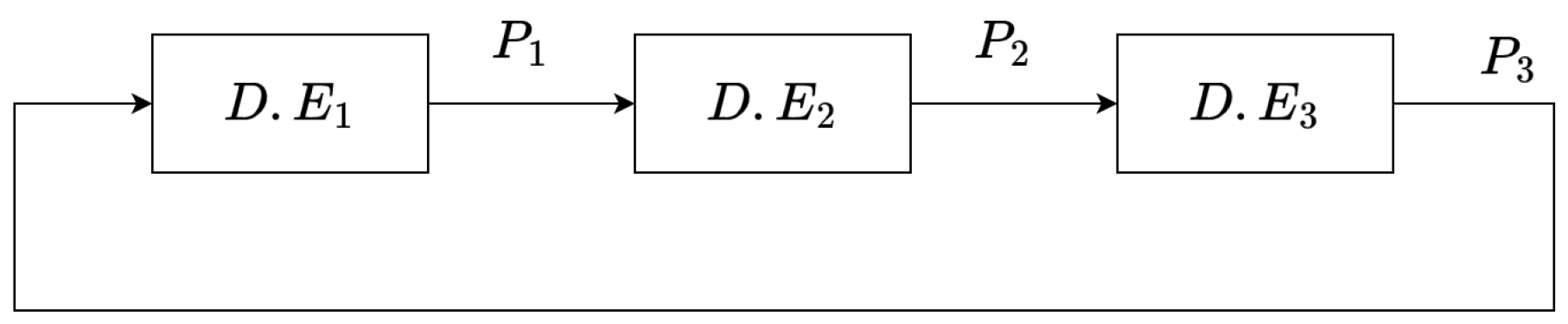

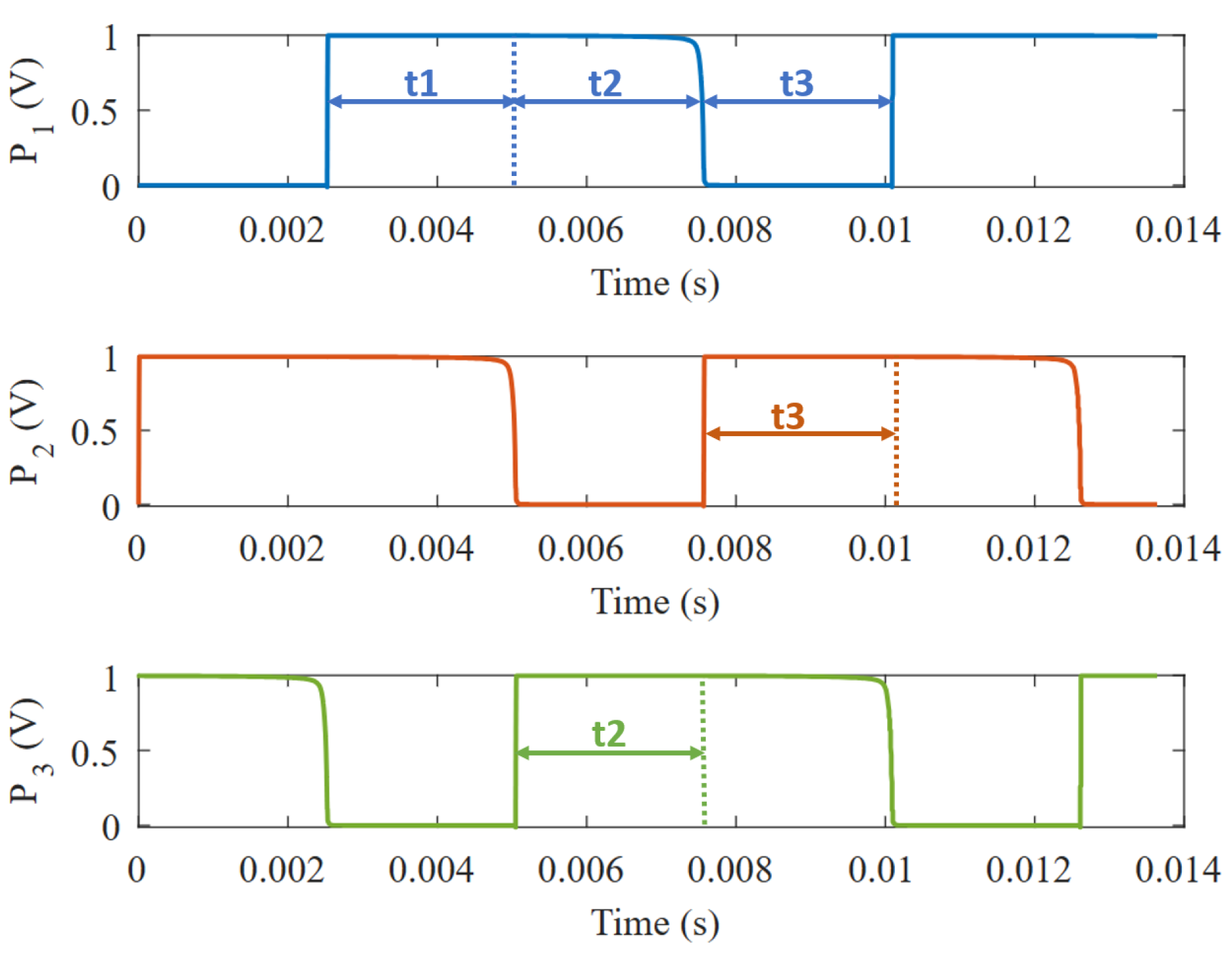

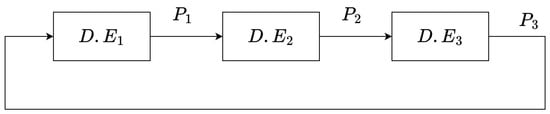

The proposed VCO follows a ring-oscillator structure with three delay elements connected in series, as shown in Figure 3. Consequently, the period is given by the addition of the three delays generated in the circuit, as illustrated in Figure 4.

Figure 3.

VCO composed of three delay elements.

Figure 4.

Transient simulation of the three phases of the VCO.

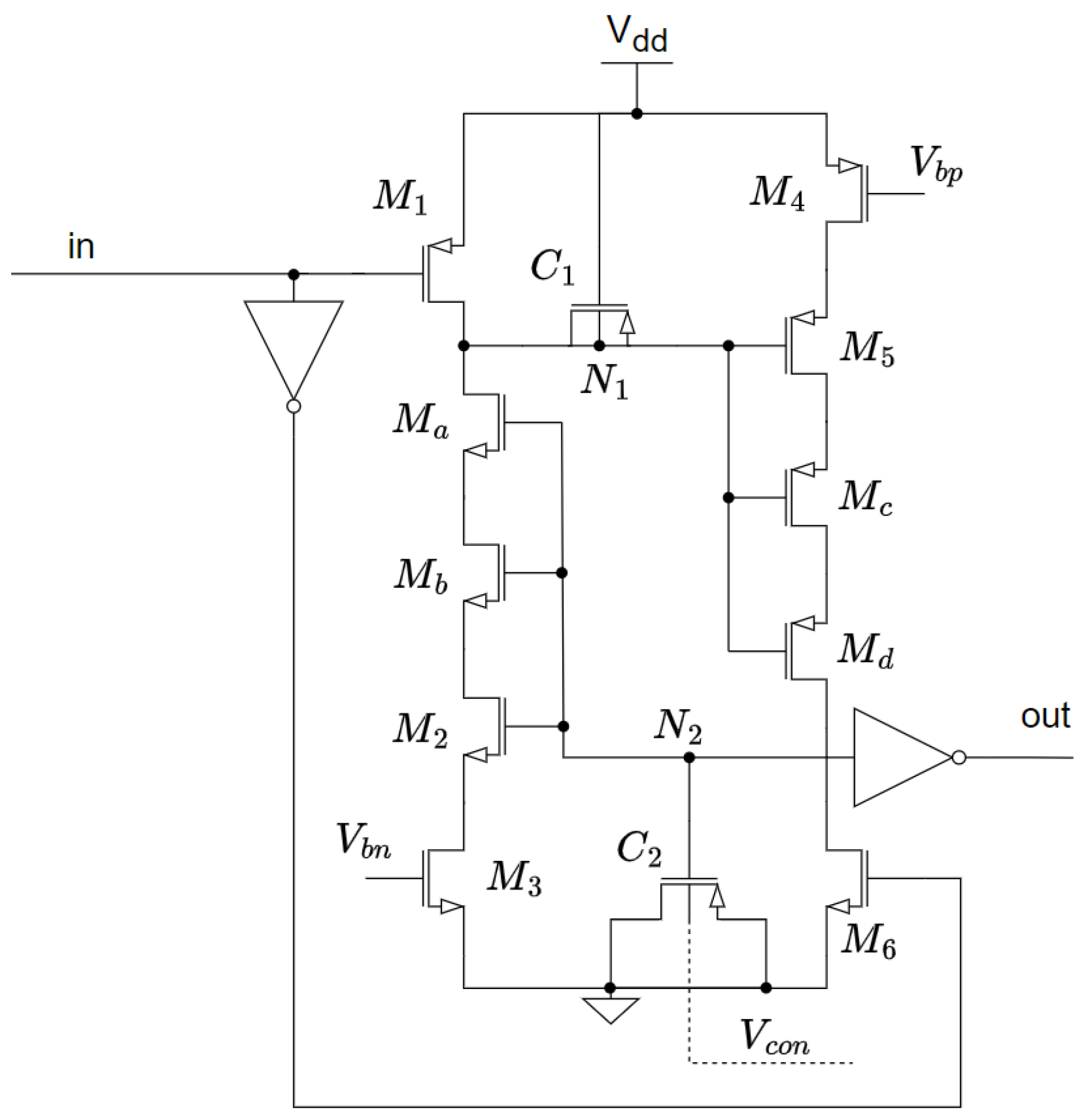

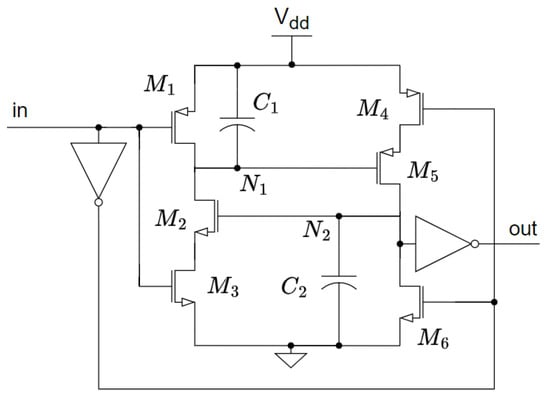

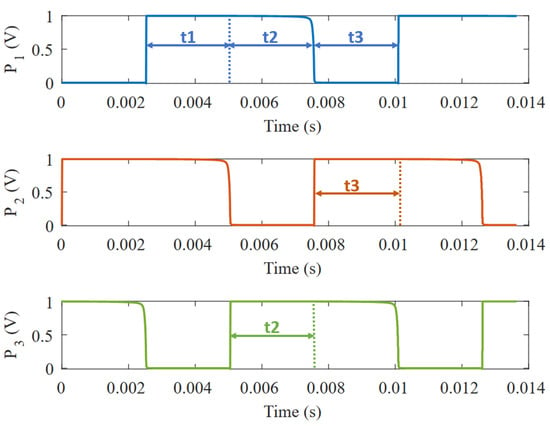

The thyristor-based delay element used to solve the aforementioned problems is shown in Figure 5. The main goals of this design were: (1) to provide an ultra-slow frequency with reduced area; (2) to reduce the peak power; and (3) to generate an output frequency that varies linearly with an input voltage, while having no significant impact on area or power consumption.

Figure 5.

Proposed delay element with capacitance tuning as voltage control.

4.1. Large Time Constants with Nanometer Technologies

The best way to reduce the area of microsystem circuits is to use a smaller technology node. This simple solution, which directly benefits the size of the circuits, comes with many other drawbacks and challenges. One of them, as explained in [17], is that leakage currents become more significant with smaller technology nodes.

Since the goal of our circuit is to generate very low oscillation frequencies, to dissipate as little power as possible, we first looked at methods of modifying and controlling the leakage currents that play a key role in the oscillator.

In our case, the leakage currents for 65 nm technology are significantly higher than for the 180 nm technology used in [7], thus leading to smaller time constants and, consequently, higher power consumption.

The main contributor to these currents is the subthreshold leakage current. Gate and body leakage can be disregarded, since simulations show them to be at least two orders of magnitude smaller. Therefore, the expression for the subthreshold leakage current is [18]

where is the nominal threshold voltage and n is a fitting parameter. S is the subthreshold swing attending to the following equation:

and

where is the carrier mobility, is the oxide capacitance per area, q is the the electron charge, is the Boltzmann constant and T is the temperature.

In Equation (2), the drain-induced barrier lowering (DILB), which reduces the , is modeled by and, similarly, the body effect is taken into account through . These two effects constitute a direct mechanism to reduce the leakage currents while the transistor is turned off ( V).

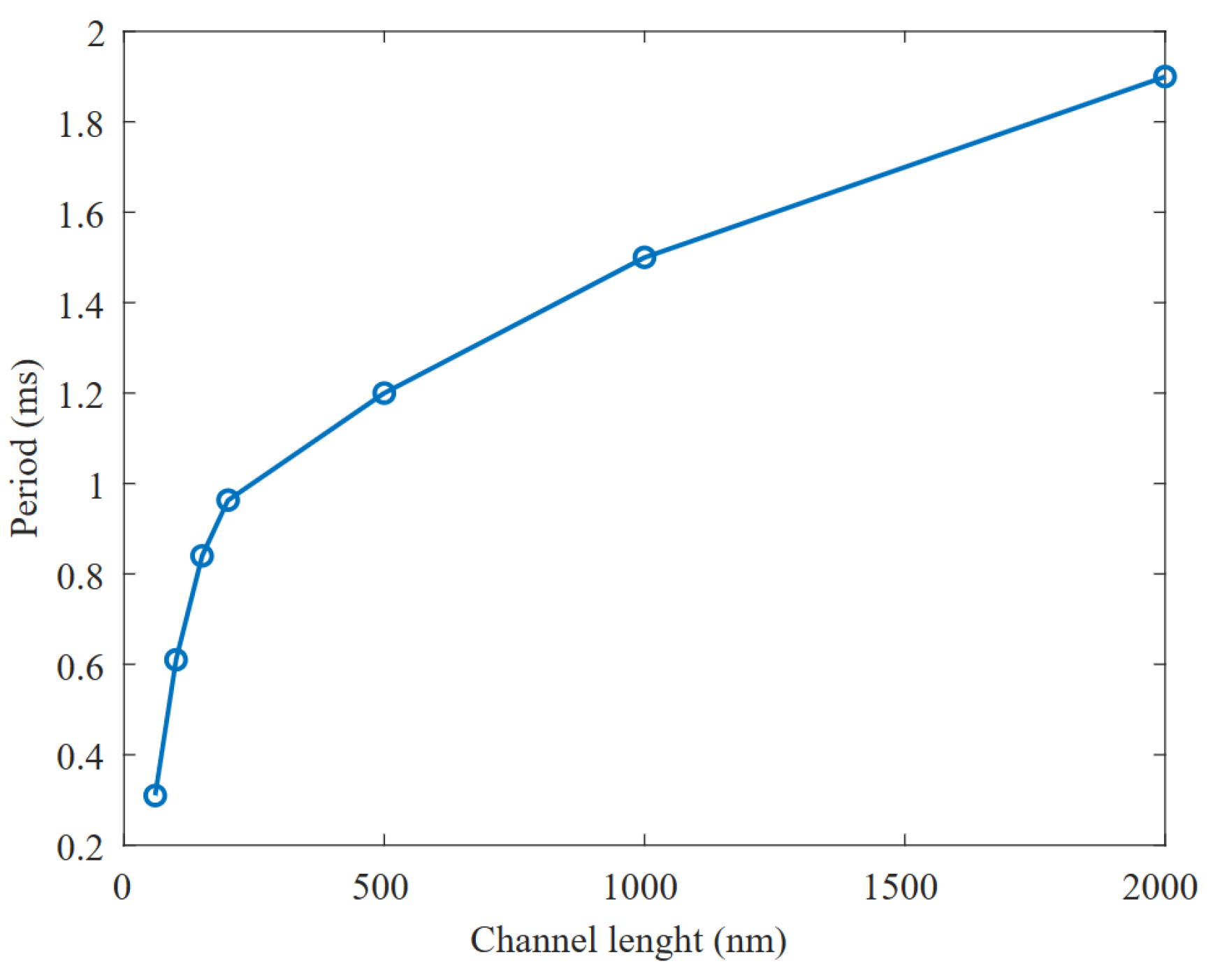

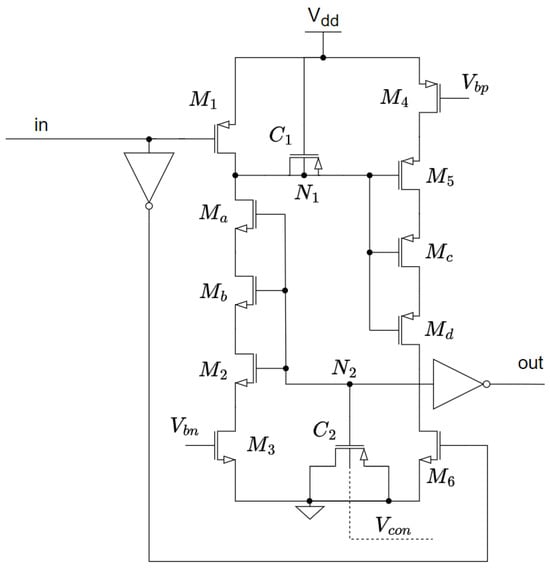

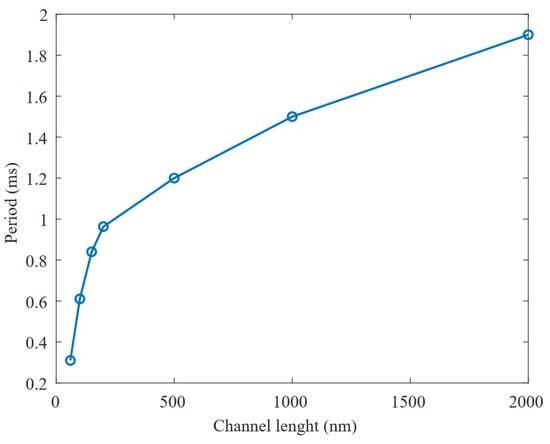

We have taken two measures to minimize the DILB effect in Equation (2). First, it is known that the DILB effect has a greater impact on transistors with shorter channels. This is due to the depletion regions of the drain and source junctions depleting a larger fraction of the channel as the channel becomes shorter. This lowers the threshold voltage, , and causes an increase in the subthreshold leakage, which is more noticeable in smaller devices. For this reason, leakage currents can be significantly reduced by avoiding the use of minimum channel lengths. Figure 6 plots the period achieved at the output of the oscillator versus the channel length used for the thyristor transistors from the schematic shown in Figure 2. In our 65 nm technology, it makes sense to move from 60 nm channel length to 200 nm, as in this region any variation will provide substantial improvements. Enlarging the channel much beyond 200 nm loses effectiveness, in terms of area, in obtaining the desired delay, as the slope in Figure 6 decreases drastically.

Figure 6.

Influence of the channel length variation on the period of the generated signal.

Second, to further reduce the DILB effect, we decided to stack transistors in Figure 5, to reduce the voltage. This does not require much additional area, but it has a noticeable effect on the leakage currents, as is reduced from a value close to to just a few mV.

At the same time, to take advantage of the body effect, the bulk terminals of and were set to ground and , respectively. This increases their and helps to further reduce the subthreshold leakage.

On the other hand, the in Equation (2) is another parameter that can be modified to achieve a larger delay. HVT transistors could have been used instead of standard transistors for the thyristor. This approach increases the threshold voltage by about ∼150 mV, which greatly reduces leakage currents. This reduction would translate into lower frequencies for the same area, or a reduction in capacitor size to save die area for the same target frequency. However, we ultimately rejected this option, due to the increased variability of this transistor type. Although the typical case simulations gave excellent results, we found multiple runs in the Monte Carlo simulation that did not oscillate at all. To solve this problem, the leakage currents needed to be increased, thus losing the main advantage of this technique. At the same time, this technique requires a higher minimum supply voltage (from 0.3 V to 0.7 V) for the oscillator to start operating, which can be another significant drawback in some cases.

Finally, it can be seen from Equation (1) that the leakage currents of the transistors should ideally be maximized, to increase the period. However, if they exceed a certain ratio to the leakage, the oscillator may stop oscillating. To avoid this, the currents of the transistors are set to of the currents. This ensures that the VCO operates correctly even under the high process variability characteristic of thyristor-based topologies.

4.2. Ultra-Low Power Dissipation

Another issue with the design proposed in [7] that needs to be adjusted for our target application is the peak current. The short period of time that the transistors in Figure 2 are on results in a very high peak current to charge or discharge both capacitors from to (or GND). Since the power supply in our case comes from a weak energy harvester, a high peak current will result in an unacceptably large voltage drop. For this reason, the and gates have been biased to a voltage ( V and V, respectively) that will not significantly affect the leakage currents that charge/discharge the capacitors, but will limit the peak currents that occur when the positive feedback is activated. In other words, the bias voltages and limit the maximum currents through and to a few nA, and since the leakage currents used in the thyristor are in the order of tens of pA they are not affected; thus, the frequency of the oscillator remains unchanged.

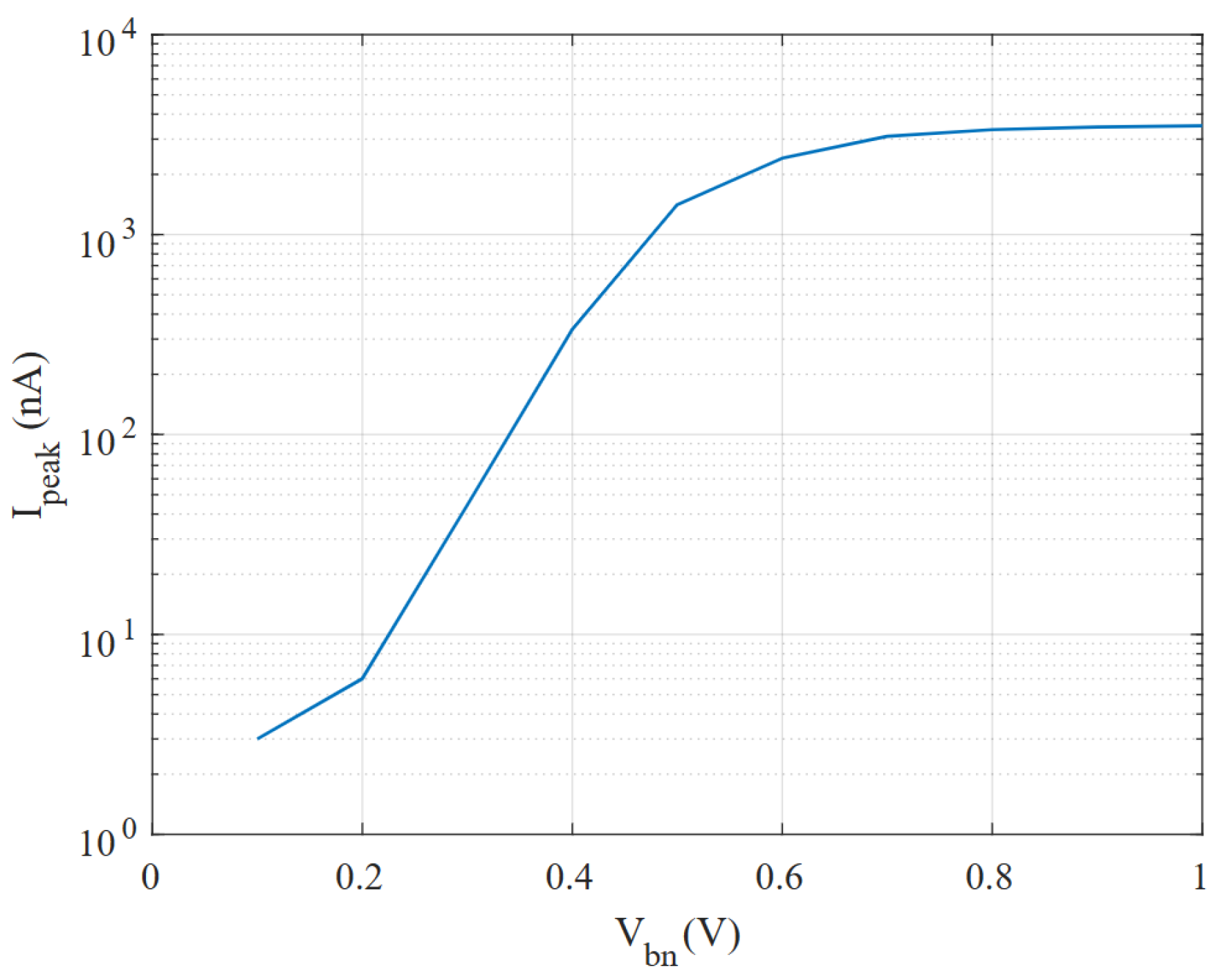

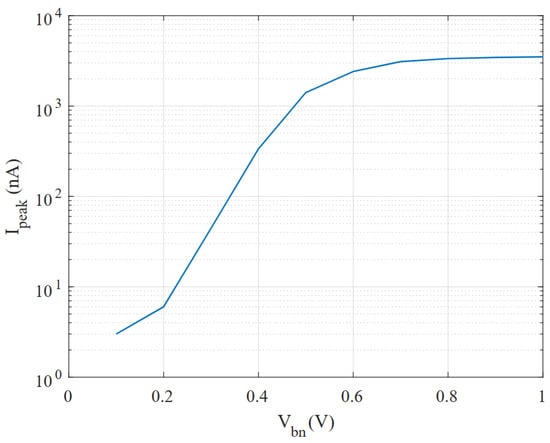

With the same purpose of reducing the peak power consumption, the inverters are made current-starved with the same bias voltages, and . A simulation of how these bias voltages affect the peak currents is shown in Figure 7, to illustrate the importance of setting the correct bias for transistors and if peak currents are to be monitored. The voltages and are generated by a robust power-management unit present in the chip containing this oscillator.

Figure 7.

Simulation of the peak current drawn in the proposed VCO for different values.

4.3. Linearized Voltage-Controlled Oscillator

When it comes to dynamically changing the output frequency of the oscillator, the RC time constant of the delay element must be tuned, with respect to the input signal. We propose an approach where the capacitance of the delay element is modified to produce a quasi-linear response.

The proposed structure is shown in Figure 5. As can be seen, the capacitors used for this delay element are PMOS transistors with their source and drain terminals directly connected. CMOS transistors used as capacitors [19] are one of the most popular solutions to implement these passive components: firstly, they are available for any CMOS fabrication process without additional steps, which also translates into cheaper fabrication processes; secondly, they have the highest capacitance density of any option available in today’s processes, which is why we have chosen them to produce large time constants in the smallest possible area.

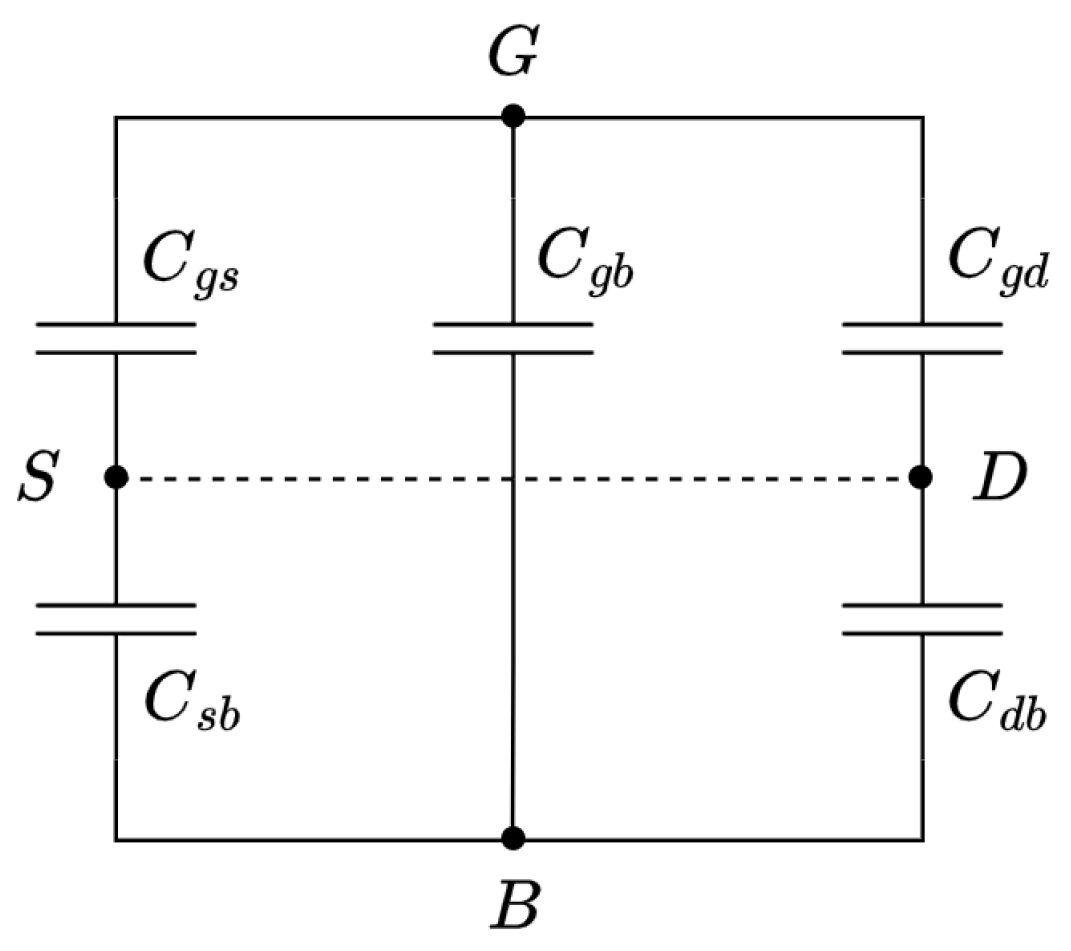

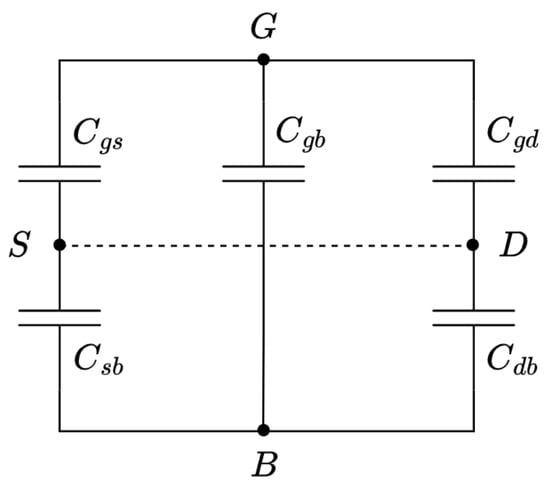

The parasitic capacitance model of an MOS transistor is depicted in Figure 8. It consists mainly of the following:

Figure 8.

Parasitic capacitances model of an MOS transistor with source and drain connected.

- Two overlap capacitances ( and ) similar to a parallel-plates capacitor and independent of the biasing voltage.

- Two junction capacitances ( and ) resulting from the charge accumulation fluctuation around the depletion layer. These depend on the biasing voltage.

- The gate-to-bulk capacitance (), which has two components, one bias-dependent, the channel-to-bulk capacitance, and another one independent, the gate-to-channel capacitance.

After some simplifications, the effective capacitance between gate and source–drain () can be expressed as

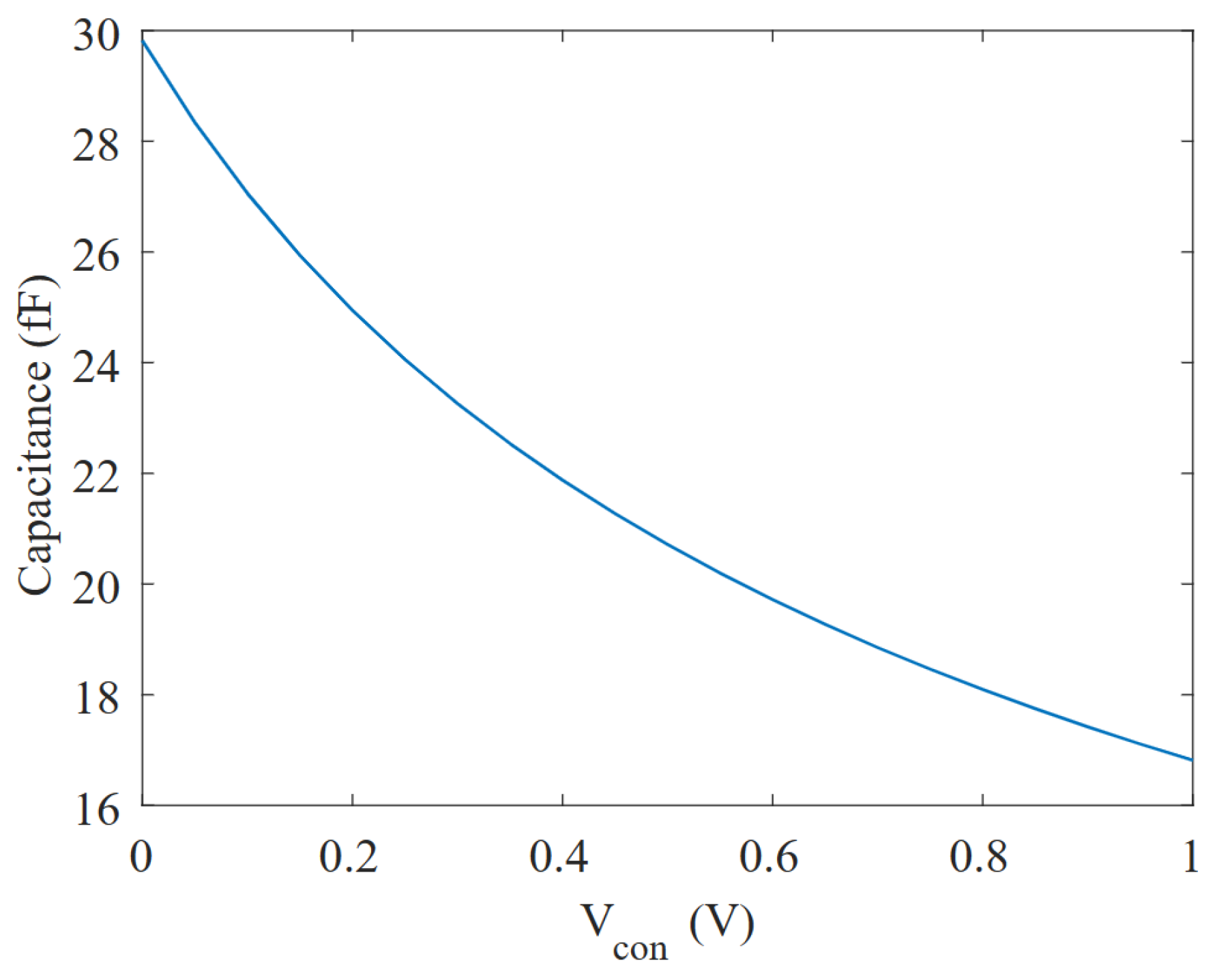

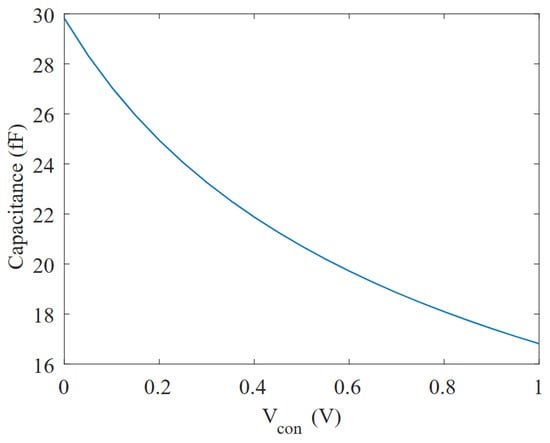

To vary the capacitance of the PMOS transistors () used in the RC time constant of the VCO, the voltage must be tuned. This directly affects the parasitic capacitances , and by thickening or thinning their depletion layers, which act as their dielectrics. Since the only voltage-dependent term in Equation (5) consists of depletion capacitances, the capacitance , according to the depletion capacitance theory [20,21], follows a quadratic relationship with respect to the voltage (shown in Figure 9), similar to

where and are constants that can be obtained by simulation.

Figure 9.

Simulation of the capacitance variation () vs. .

Combining Equations (1) and (6), and taking into account that , the following expression that correlates the frequency with respect to is obtained:

where D stands for

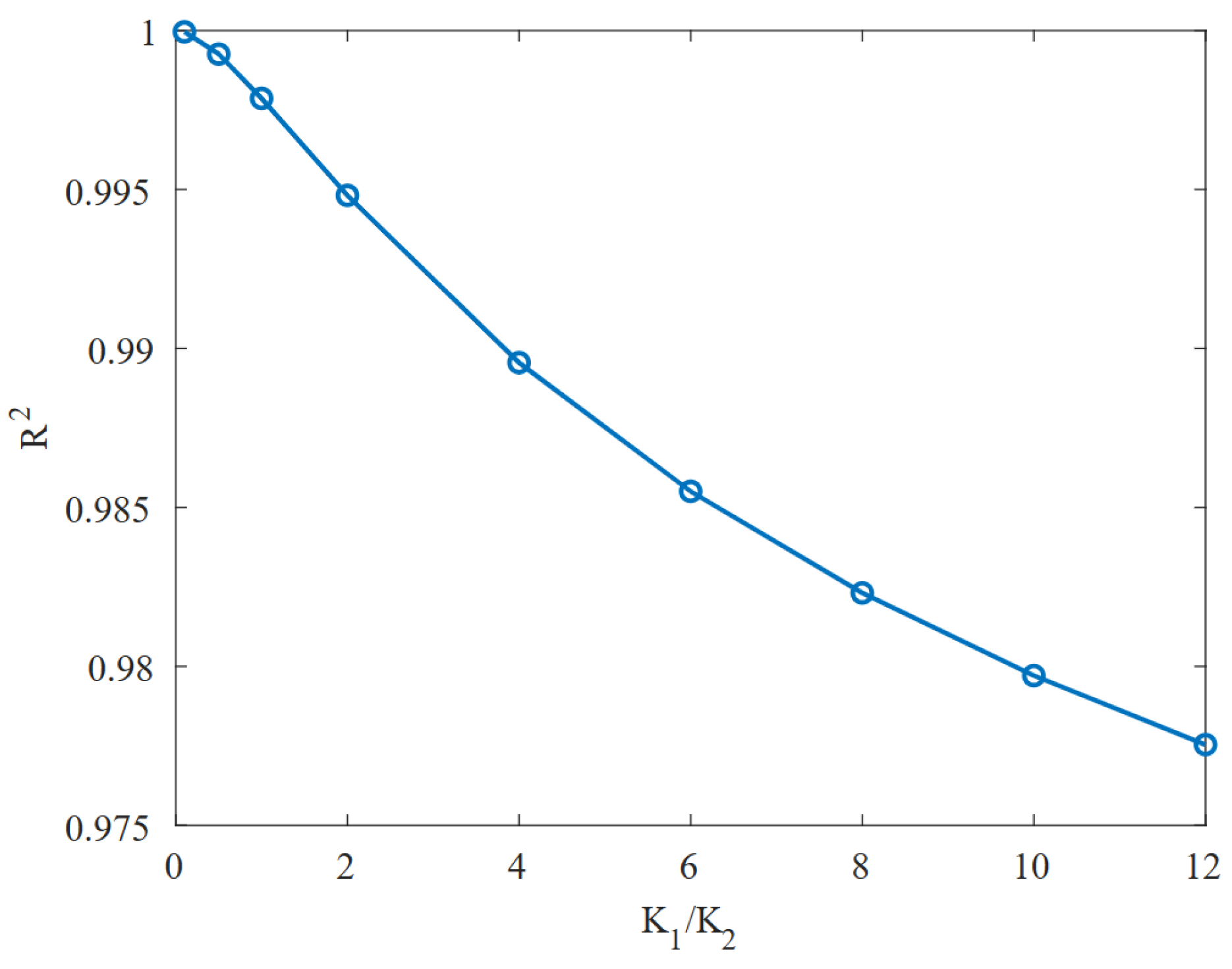

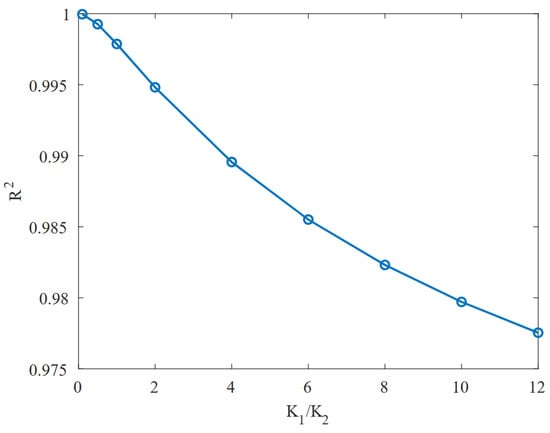

The expression given in Equation (7) can be linearized, with an factor greater than 0.99, as will be proved by experimental results in the following section, using a simple statistical regression model. The reason for this highly linear fit is the relatively small capacitance variation ratio , which makes the square root present in Equation (7) almost flat in any available range of . A graph showing how the linear regression fit evolves as a function of this ratio is shown in Figure 10. The lower , the more linear the frequency response becomes with respect to the input voltage. However, there is a trade-off concerning the VCO gain, since a ratio of 0 would result in an oscillator that no longer had the ability to change its frequency, so the higher the capacitance variation ratio the higher the VCO gain. For this reason, we conducted a study to discuss the different transistors that could be used as capacitors. The most relevant parameters discussed for the selection are summarized in Table 1, namely, the ratio, the area and the linearity. Since for our application a linear fit greater than 0.99 () is valid, all of them provide a sufficiently linear response. Next, we focused on getting the largest possible capacitance variation ratio, which directly translates into a larger VCO gain, where LVT and core PMOS stand out with similar values, but for a small improvement in the LVT transistor takes up more than 40% more area than the core transistor. Consequently, the core PMOS was chosen for this design.

Figure 10.

factor vs. .

Table 1.

PMOS transistor type comparison for their use in the VCO.

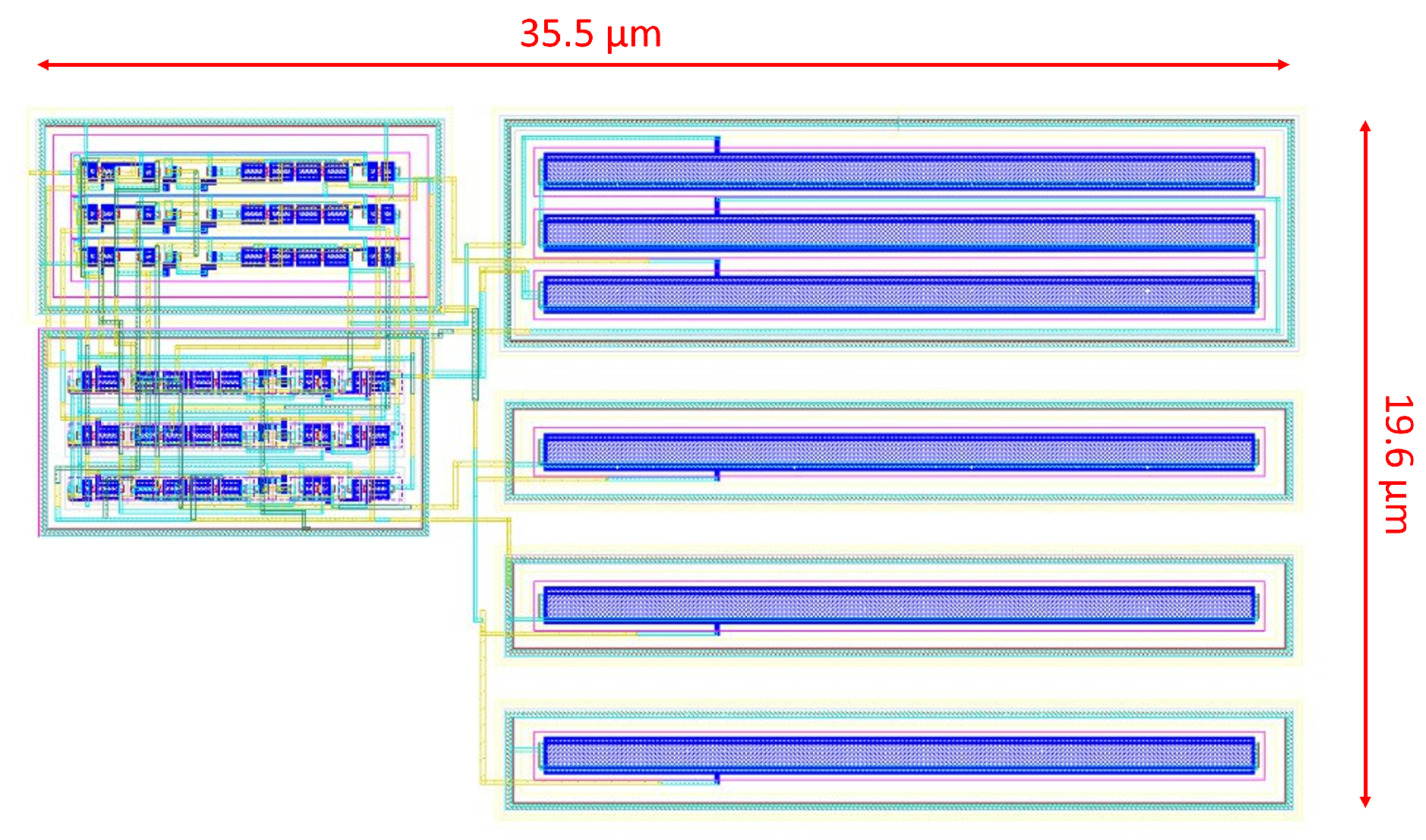

5. Results

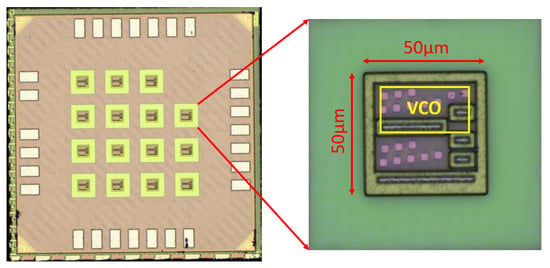

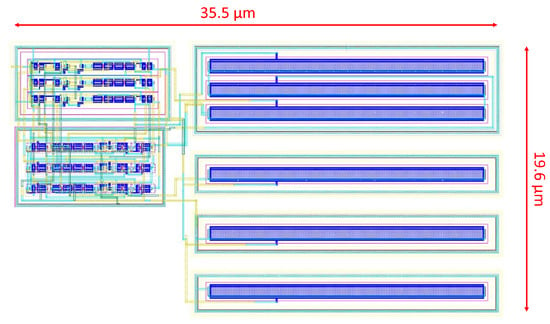

Figure 11 shows the fabricated CMOS silicon part of the MIT microsystem for which the oscillator was designed. The green rectangular shapes in the zoomed area are the probe pads that will later be used as the connection points for the rest of the microsystem through heterogeneous integration. The VCO, represented with a yellow box in Figure 11, occupies an area of . The layout of the VCO is shown in Figure 12. It is worth noting that there is a space of approximately at the bottom-left corner for placing the biasing stage, which is part of the power-management unit (PMU) of the system, near the VCO.

Figure 11.

Fabricated chip.

Figure 12.

Layout of the fabricated VCO.

Transistors and having a 200 nm/500 nm W/L ratio and the rest remaining at a minimum size of 200 nm/60 nm ratio, and were both implemented with PMOS transistors with a 700 nm/20 W/L ratio.

The simulation and measurements of the proposed VCO are discussed in the following subsections.

5.1. Simulation Results

The VCO circuit was first simulated using Virtuoso IC 6.1.7.715 from Cadence software.

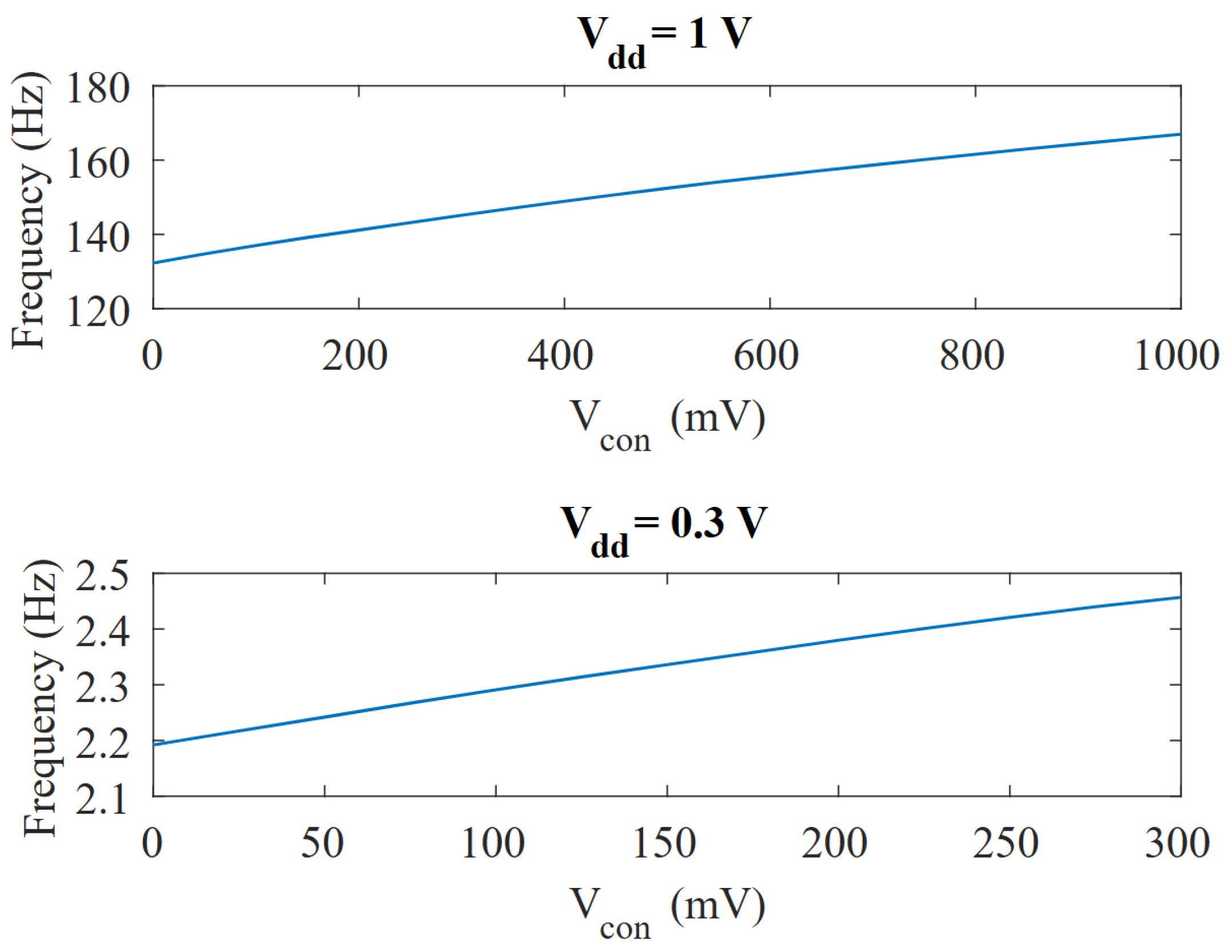

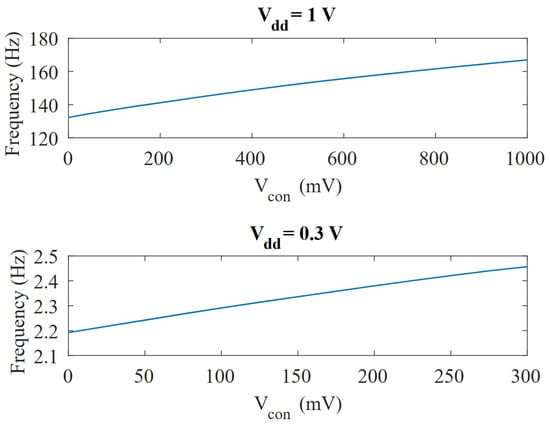

The VCO response to the control voltage, , at both nominal voltage (1 V) and minimum voltage (0.3 V), is shown in Figure 13. At nominal voltage, the VCO outputs a frequency that ranges from 132.4 Hz to 167 Hz, which represents a gain of ∼26%/V. At the same time, the VCO response holds good linearity, as it can be approximated by a straight line with a coefficient of determination () of 0.994.

Figure 13.

Simulation of the frequency variation vs. at V (top) and V.

On the other hand, when the circuit is powered at the minimum supply voltage, V and the control voltage is swept from 0 V to , the absolute change in the capacitance is reduced but the linearity is further improved. Although the maximum frequency change also decreases (2.2 Hz to 2.46 Hz), the relative frequency shift per volt increases, due to the higher slope of the capacitance variation at lower bias voltages. As a result, when operating at 0.3 V we obtained a VCO gain of 36%/V and a coefficient of determination of 0.997. In both cases, the frequency change produced by this VCO is sufficient to perform an accurate voltage-to-frequency conversion.

Although a factor of about 1.8 was observed between the corresponding minimum and maximum capacitance values (16.5–30 fF) for the maximum and minimum possible voltages (as shown in Figure 9), for the RC time constant and, hence, the oscillation frequency experiments only a ∼26% change was observed, as shown in Figure 13.

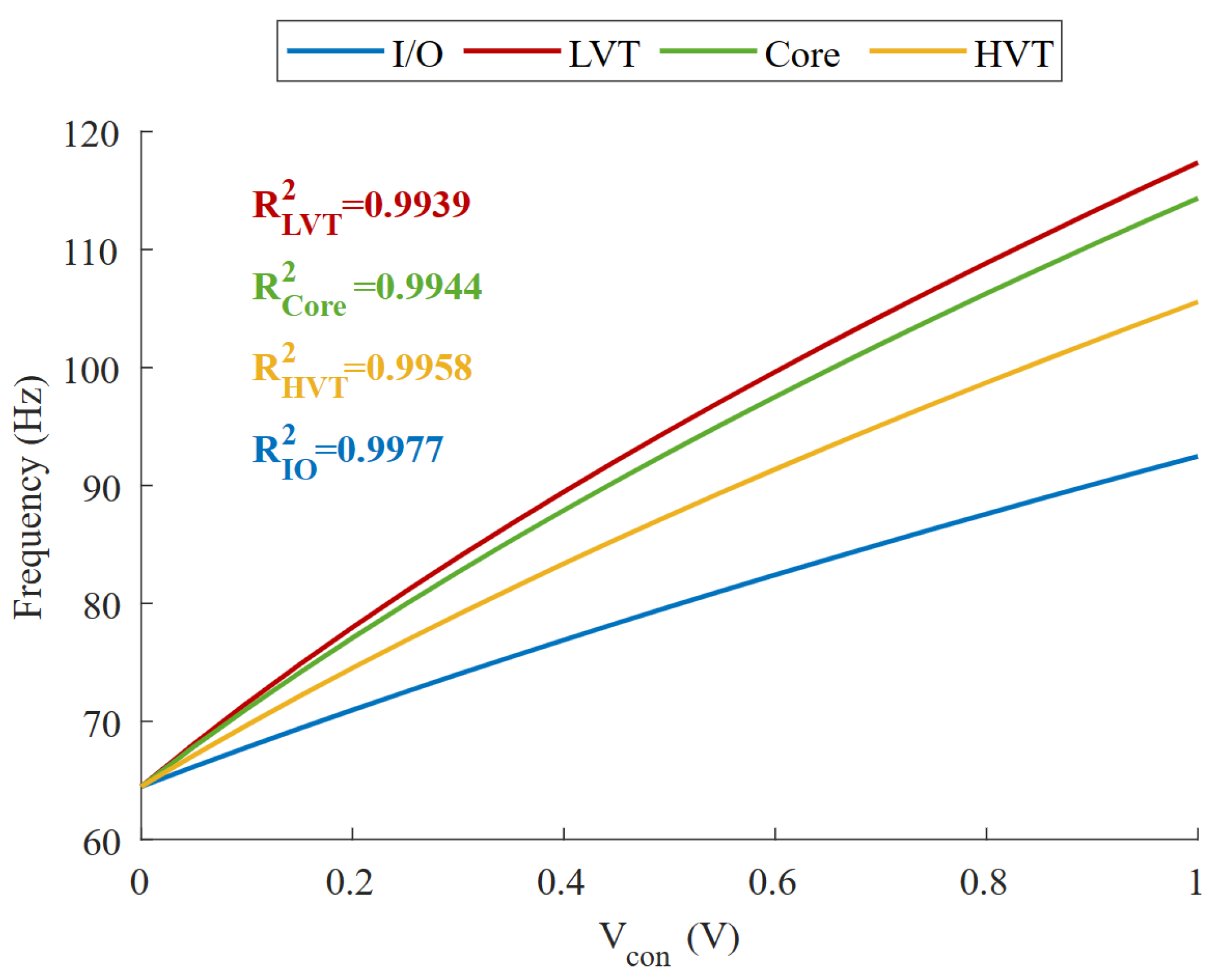

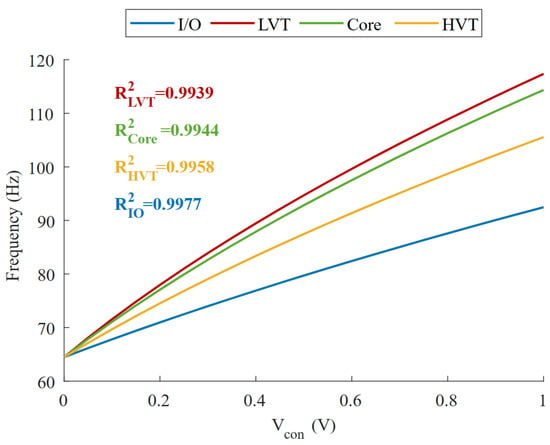

If double-well technology were available, both capacitors and could be tuned simultaneously by using an NMOS transistor in its own p-well, with its source and drain tied to , acting as the capacitor . As a result, the same principle could be used to achieve a highly linear response with a slope of ∼2 if a higher gain was required. A theoretical model simulation, including the four available transistor options, of how the frequency changes if both capacitors could be tuned simultaneously is shown in Figure 14.

Figure 14.

Simulation of frequency variation vs. for core, I/O, LVT and HVT transistors if both capacitances are tuned at the same time.

In terms of power consumption, the VCO consumes only about 200 pW at the nominal supply voltage and around 4 pW at 0.3V and remains almost invariant to the control voltage (200 pW @ 0 V and 210 pW @ 1 V). It is important to note that the peak currents have been reduced to a maximum of 11 nA at the nominal supply voltage, which is low enough to be supplied by most harvesters without any significant impact.

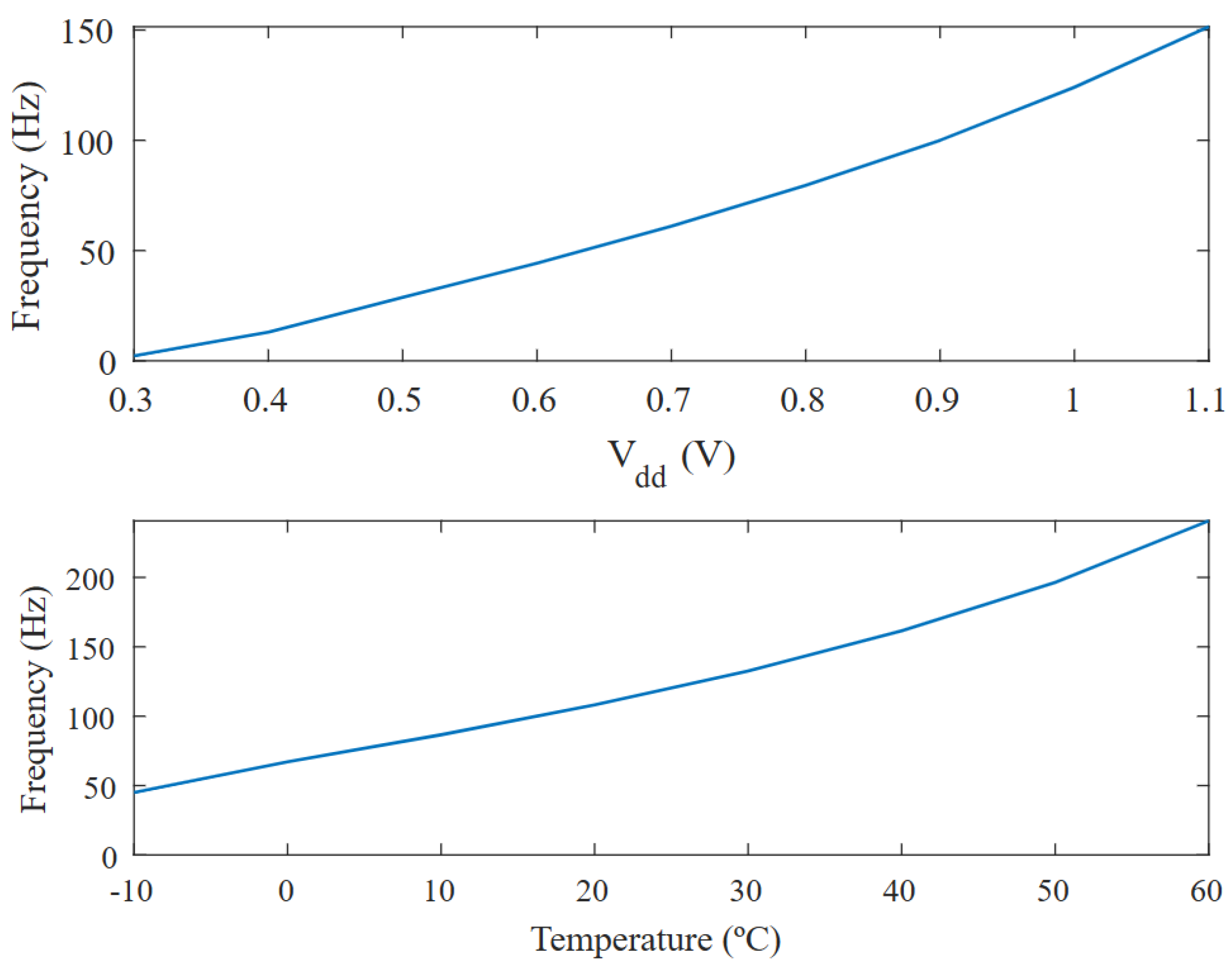

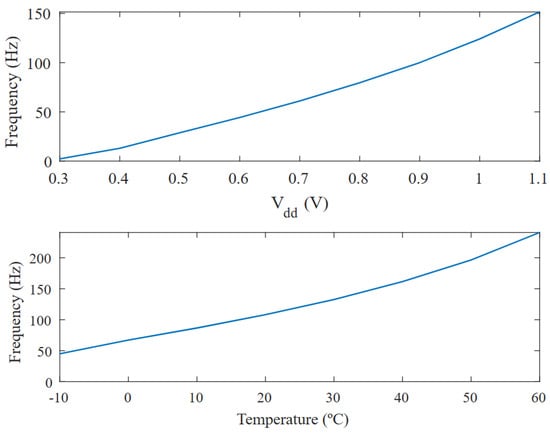

Both the voltage () and temperature responses are shown in Figure 15. Although this VCO is intended for use in temperature-stable environments, the responses shown in Figure 15 are quite convenient if a temperature-invariant oscillator is required. If the temperature range over which the oscillator is going to operate is not too wide, the frequency variations due to temperature and supply voltage can be considered linear, making it possible to neglect the temperature effect on the frequency if the oscillator’s supply voltage comes from a specified CTAT generator that matches the observed slope. This has not yet been implemented, because in vitro operation is being considered, although it is planned for future versions of the MIT microsystem.

Figure 15.

Simulation of frequency variation vs. and temperature at V.

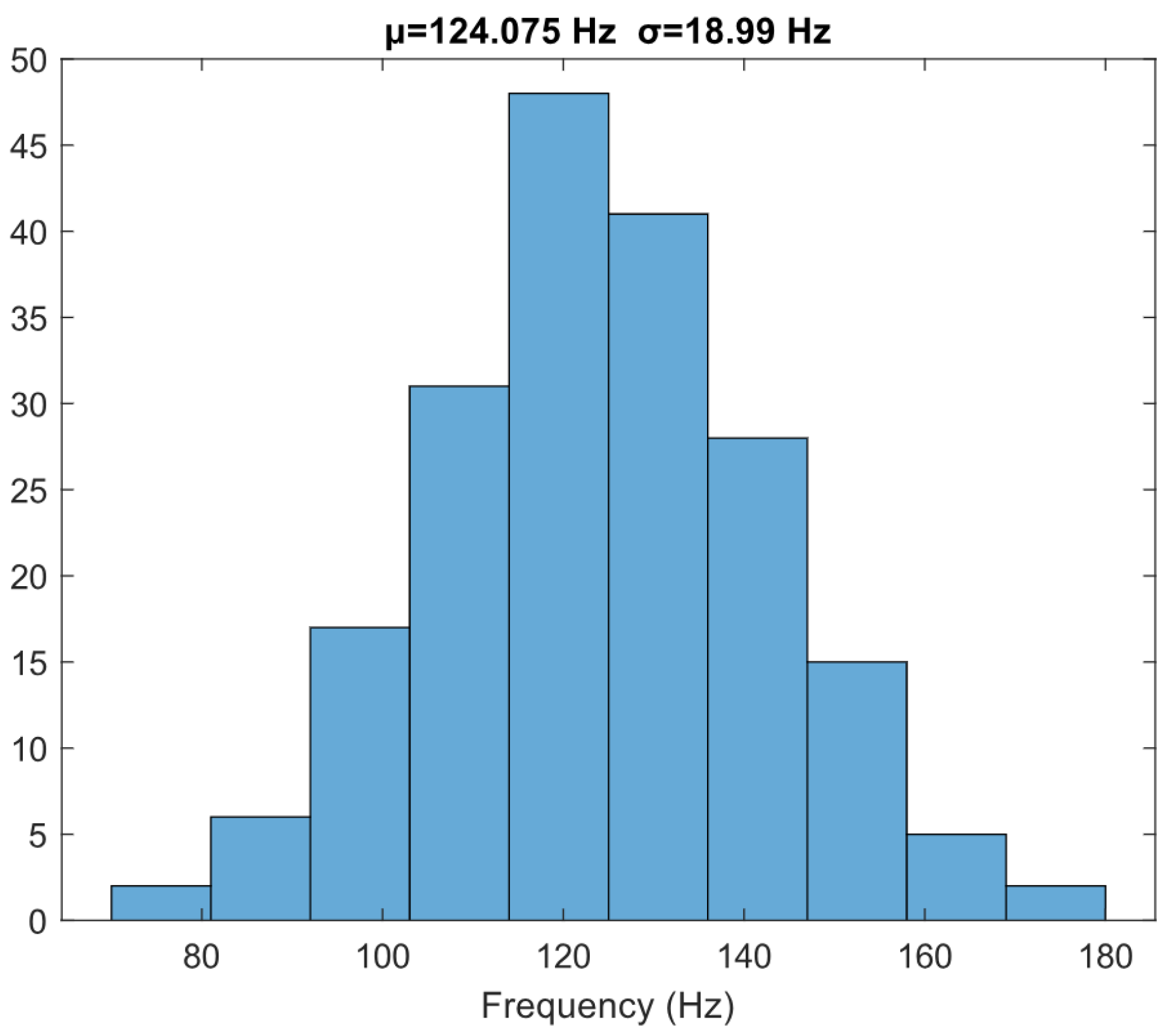

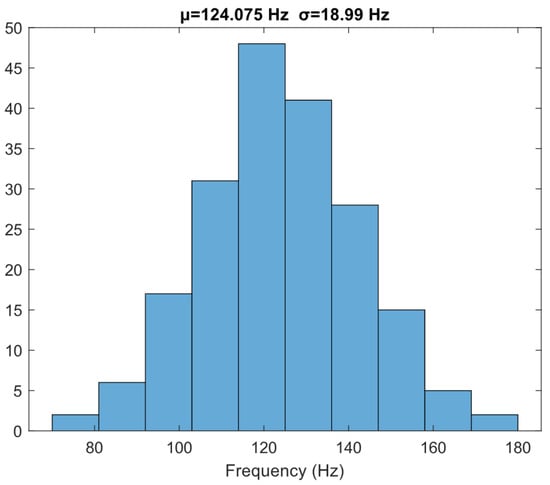

The Monte Carlo was also simulated for the nominal frequency of the VCO, shown in Figure 16, giving a mean value of 124.075 Hz @ 0V and a standard deviation of 18.99 Hz (). The corner analysis was also simulated, and the results are collected in Table 2.

Figure 16.

Monte Carlo frequency simulation.

Table 2.

Corner analysis simulation results at V.

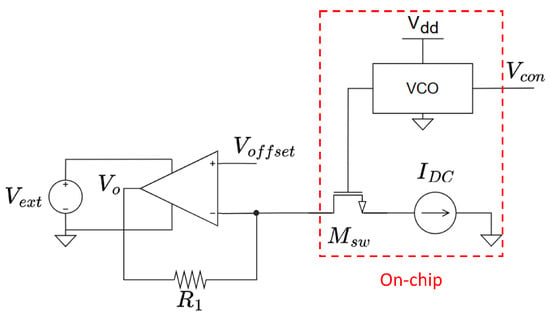

5.2. Measurement Results

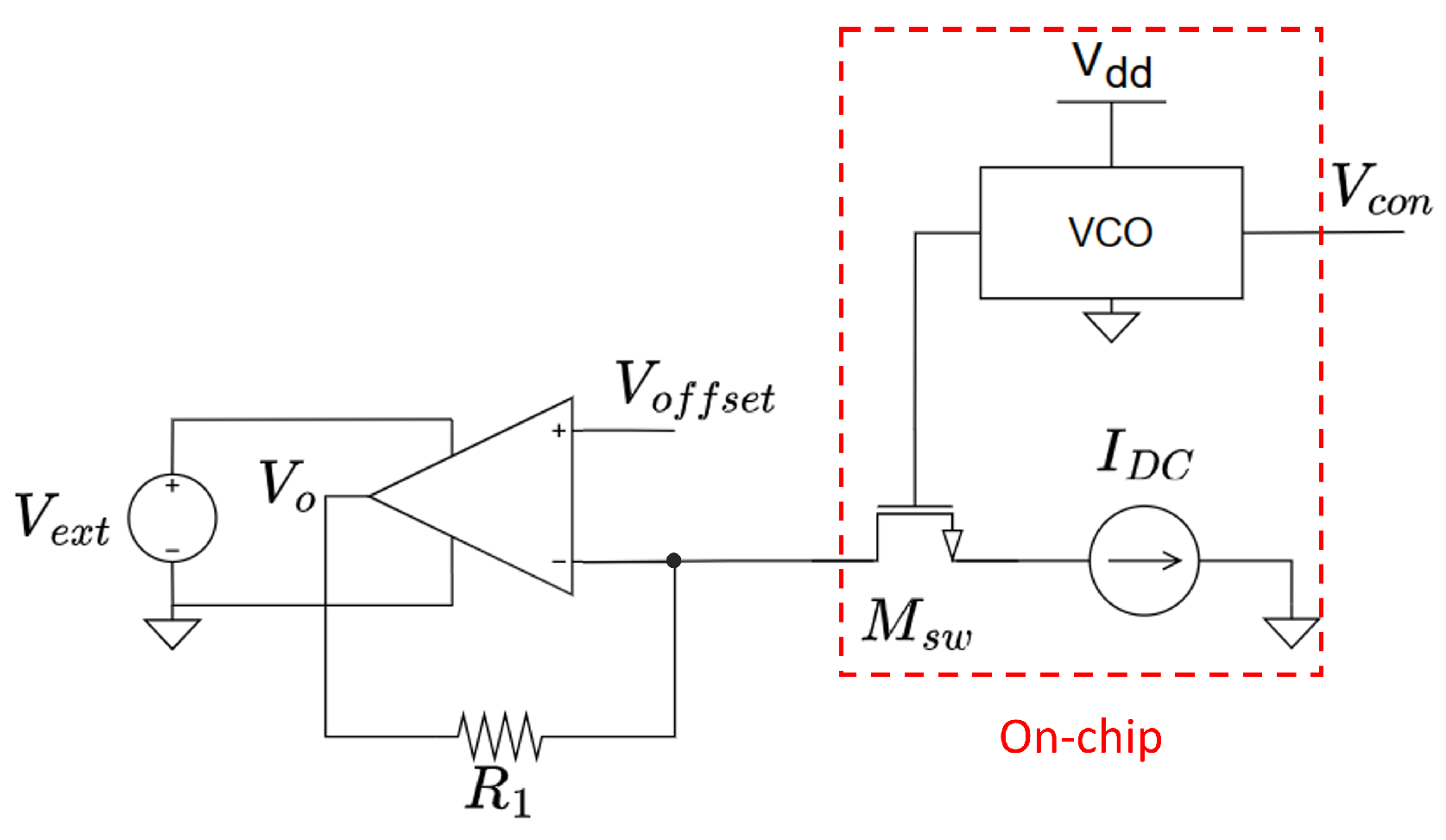

The measurement setup is shown in Figure 17. The VCO drives a transistor acting as a switch (), which allows the current imposed by the current source, , to flow or not. These current pulses are converted into voltage pulses by a trans-impedance amplifier. The amplitude of the current pulses follows the relationship , and their frequency is that of the oscillator, avoiding any possible load effect in the measurement. As also shown in Figure 17, the oscillator as well as the switching device () and the current source are on-chip elements, while the trans-impedance amplifier is placed off-chip, and it does not share the same power supply as the previously mentioned parts. This configuration was chosen because it accurately represents a divisible stage of the SynCell system.

Figure 17.

Measurement setup for the VCO.

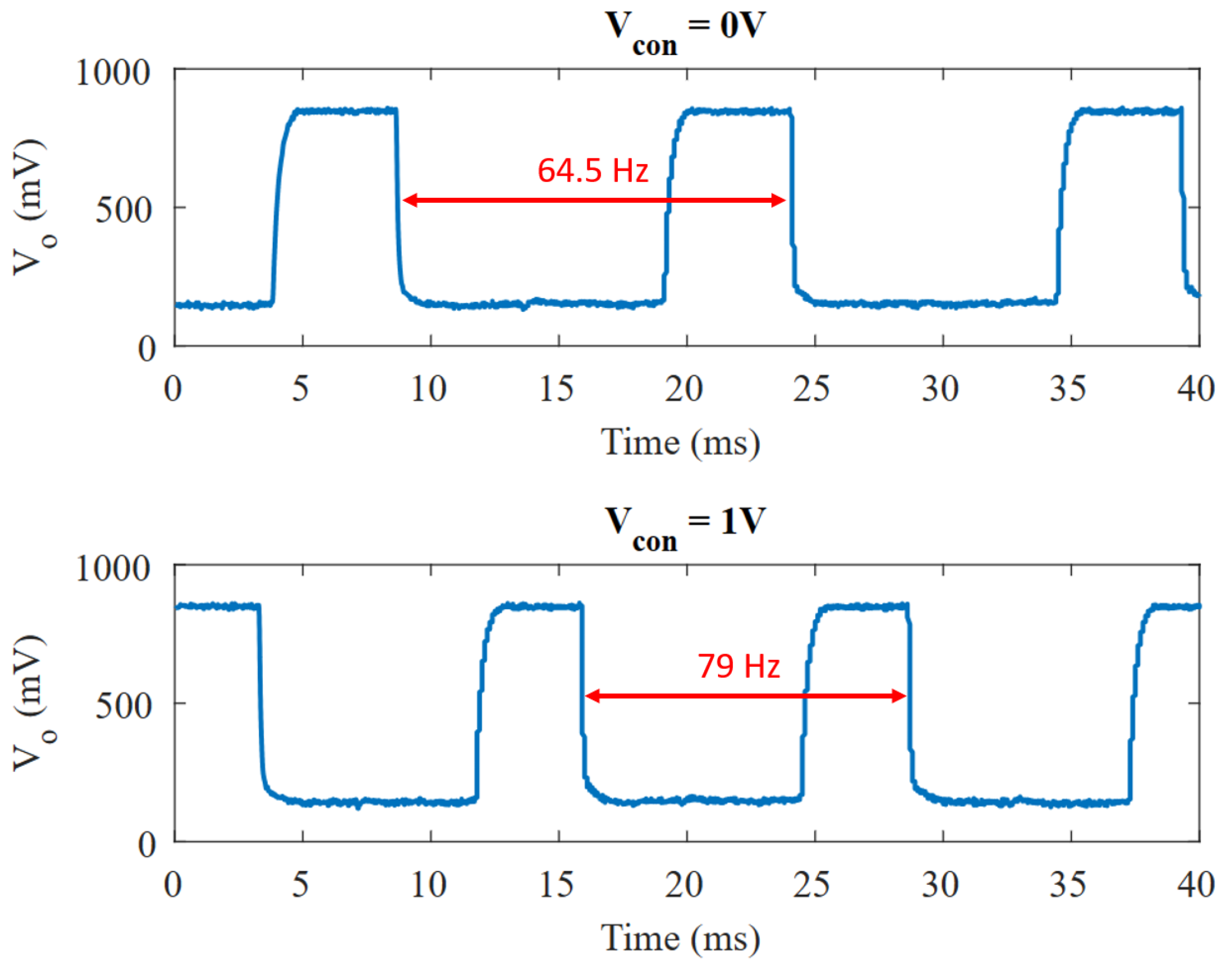

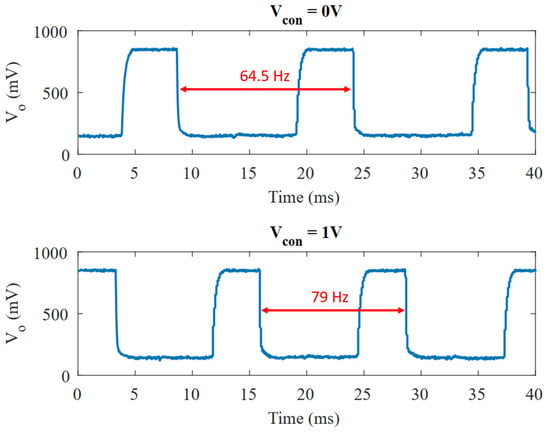

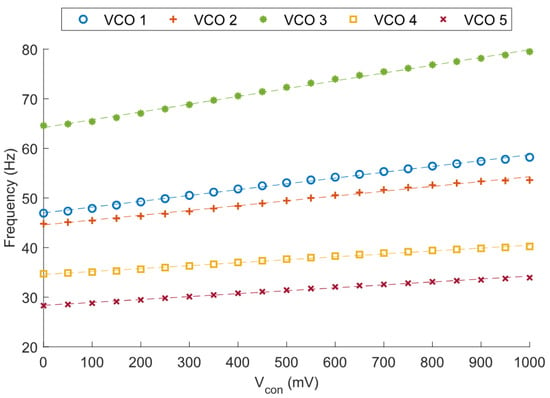

A total of five samples from different dice were measured. Figure 18 shows the transient measurement of one sample’s output at minimum and maximum values. Table 3 collects the frequency-related data from each sample. A factor of ∼2–3x can be noticed between the simulated and the measured frequency. This also happened, to a similar extent, in [7].

Figure 18.

Transient measurements of the VCO at V and V.

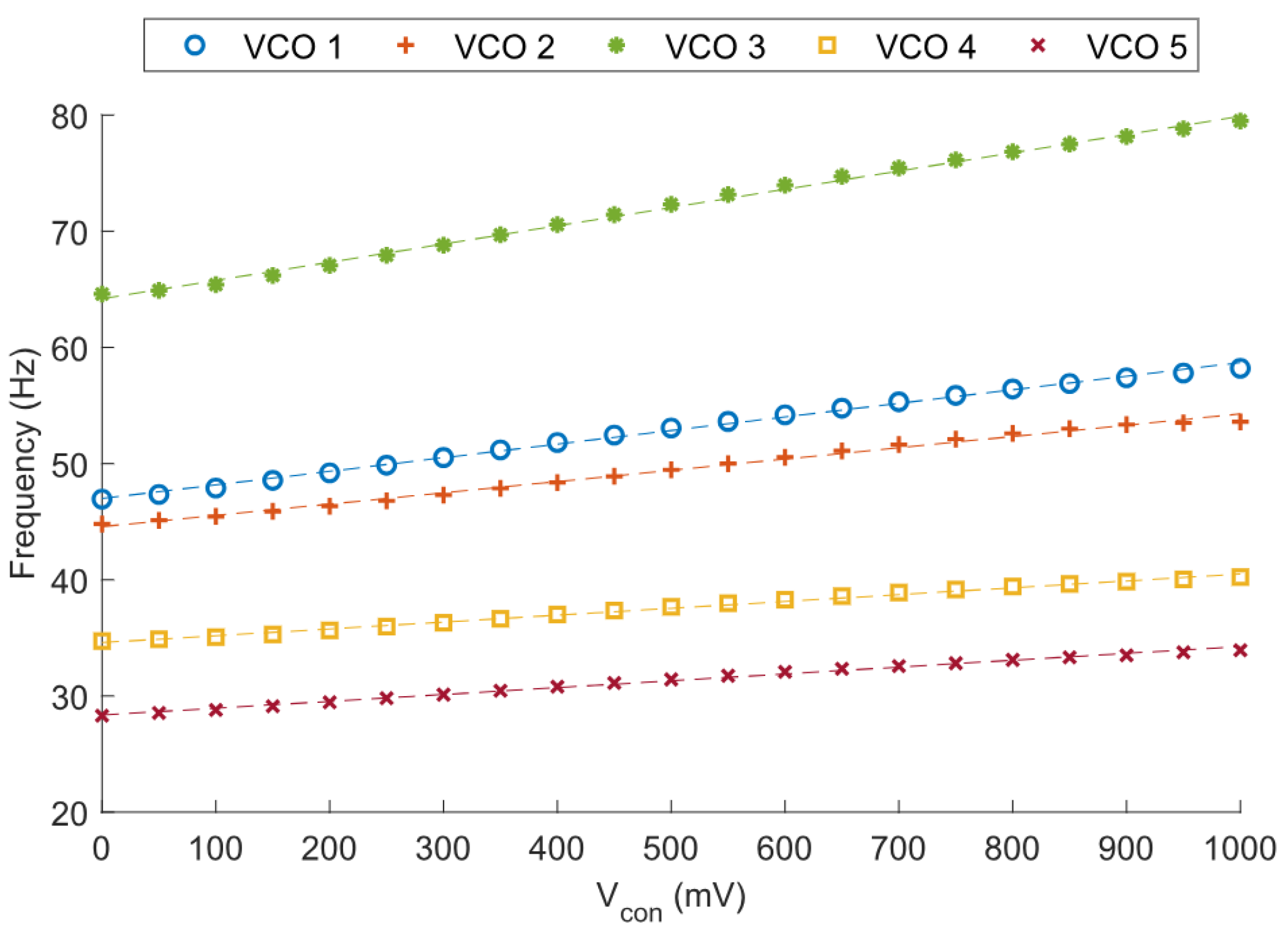

Table 3.

Collected data from the five measured samples at V.

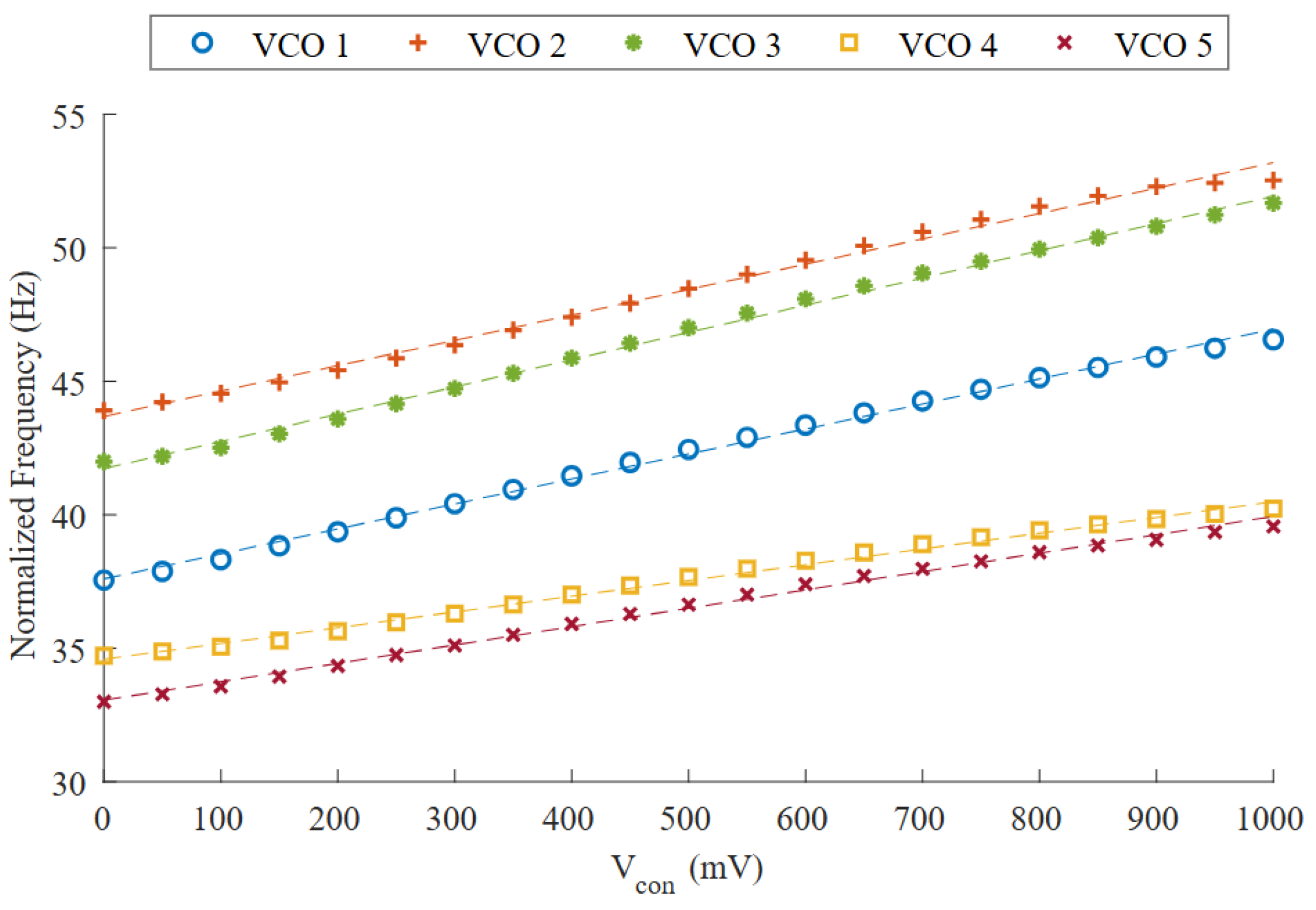

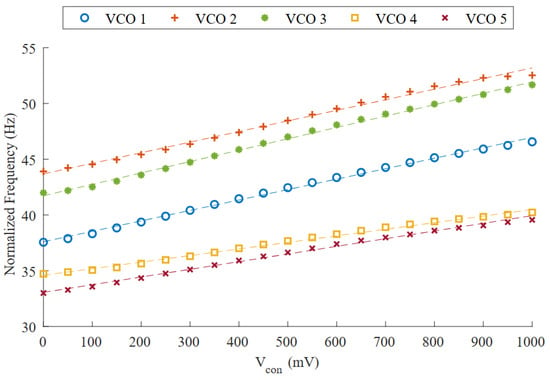

In our case, there are a few possible reasons for this simulation-to-measurement delta. First, the models used to estimate the leakage currents may not be precise enough to determine the output frequency accurately. Another possible source of variation could be unexpected parasitic capacitance. Since the capacitors used in the circuit are very low (as low as 16 fF, in the case of V) any parasitic capacitance in a sensitive node, not accounted for in the post-layout simulation, can alter the output frequency. Finally, any deviation of the supply voltage from the simulation value will introduce a certain frequency delta between the measurements and the simulations. The measured VCOs are powered by a low-dropout regulator (LDO) designed to provide a 1 V output. However, process variations cause each LDO to report a different output voltage, with 0.967 V and 1.110 V being the minimum and maximum values. To account for this effect, the frequency of each sample was normalized. To perform the normalization, each LDO output was measured, and then a correction factor was applied to the measured frequencies of each sample, based on how the frequency changes with respect to the power supply. Figure 19 shows the raw VCO measurements, and Figure 20 shows the normalized responses. While there is a significant dispersion in Figure 19, presenting a of , after the normalization it is largely reduced to .

Figure 19.

Frequency variation vs. through C-tuning for V.

Figure 20.

Normalized frequency variation vs. through C-tuning for V.

The power supply voltage disparity error can be minimized with the aforementioned normalization. However, due to the process variation effect, not only does the frequency at V shift from one sample to another, but they also differ in their respective gains. Consequently, a 2-point calibration is required, to find out the conversion ratio between the frequency produced by the VCO and its input voltage. A straight line can be extrapolated from the two measured points and then used to model the VCO’s behavior. Because of the linear nature of the VCO, the maximum relative error committed should be small. As long as the environmental conditions, such as the temperature, remain stable, the oscillation frequency should remain invariant, so the calibration only needs to be performed once. The resolution of the digitization will eventually depend on how many pulses the counter can count in a full period, which can easily be large, due to the very slow time base generated by the oscillator.

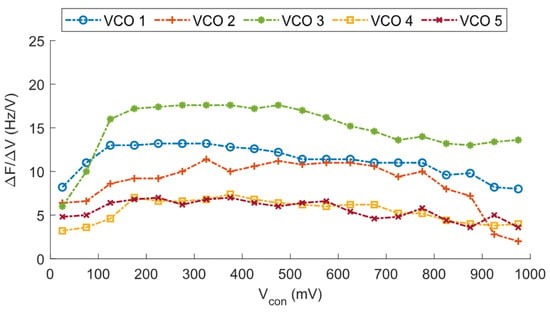

Linearity-wise, the average coefficient of determination () measured is 0.995, with a standard deviation of 0.002 in such coefficients (). This slight improvement of linearity with respect to the simulations ( = 0.994) is directly correlated to the slight VCO gain reduction found in the measurements. The measured frequency variation shows a change of about 22 %/V in the control voltage when working at the nominal supply (1 V), and of about 27 %/V in simulations. This difference is mainly attributable to process variation.

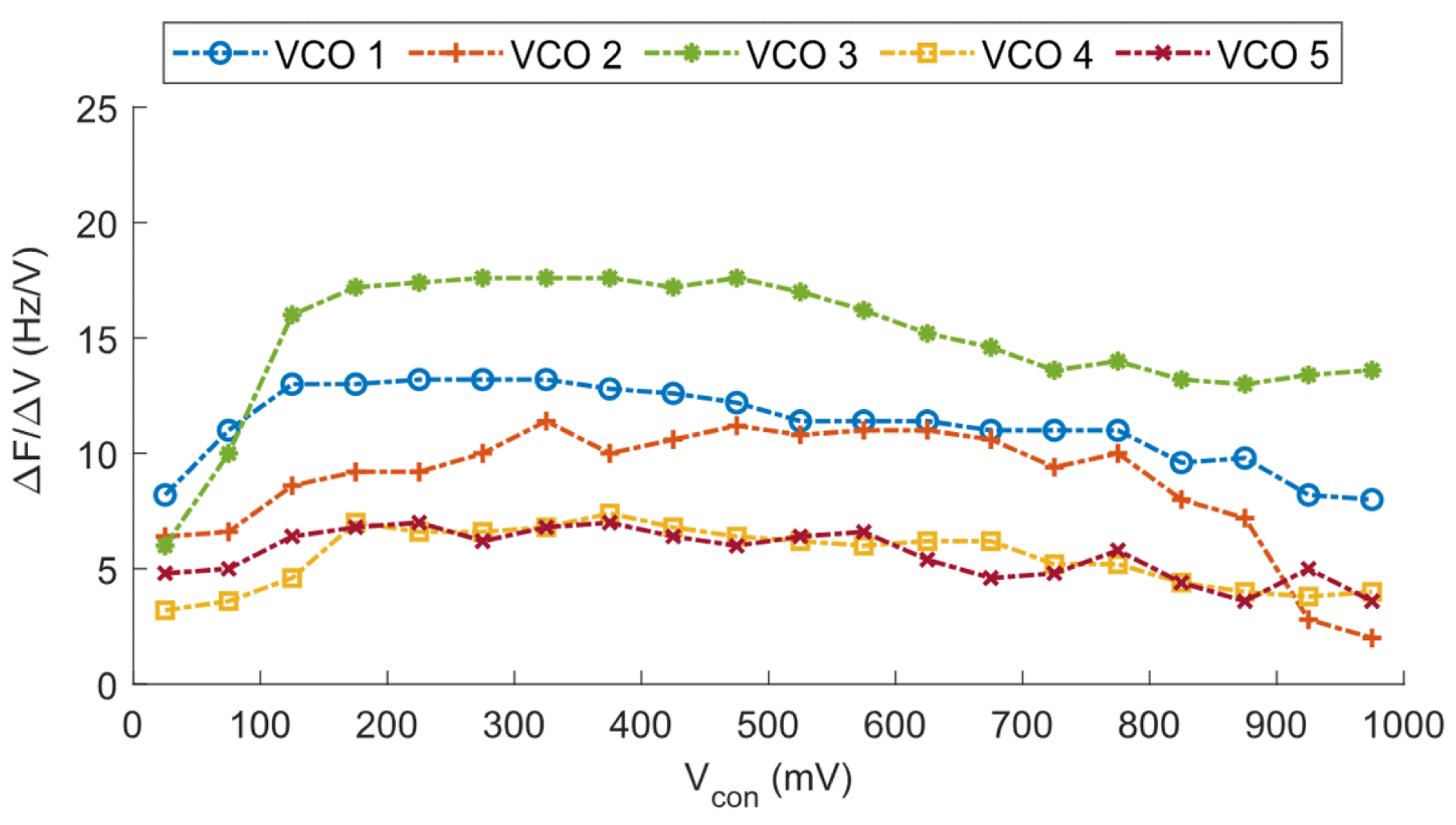

To further examine the linearity of this oscillator, Figure 21 shows the derivative of the measured frequency for each measured control voltage. Ideally, a straight line would give a flat derivative. However, in our case some distortion occurs at control voltages close to the ground or , while the VCO presents a higher linearity at more centered voltages. Although the control voltage can be swept from GND to , we recommend restricting its range from ∼0.1 to ∼0.9 for a more precise linear approximation, which results in less error committed in the voltage-to-frequency conversion.

Figure 21.

vs. for V.

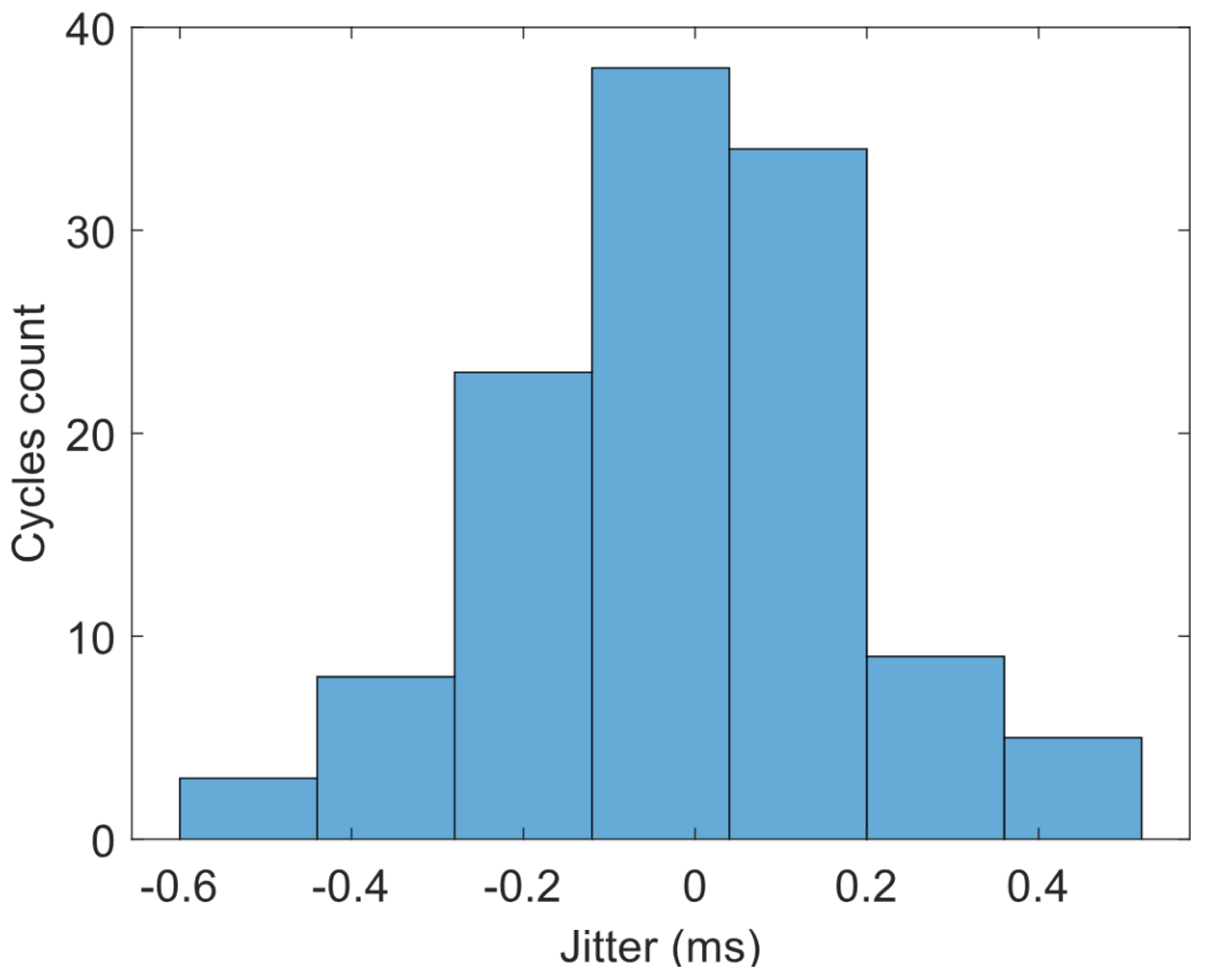

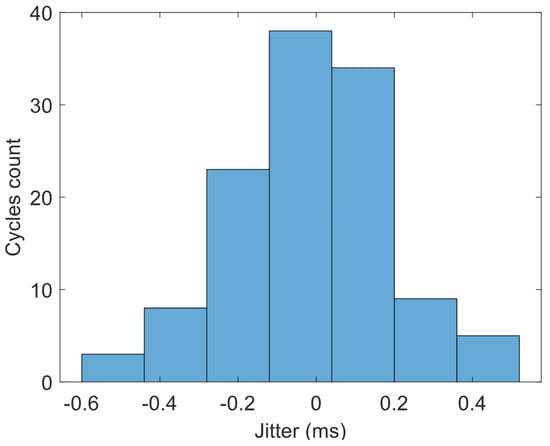

A common source of uncertainty for every oscillator is the jitter, measured in the time domain, or the phase noise if we consider the frequency domain. In our case, we measured the average period of one sample to be 15.4 ms at 0 V, with a standard deviation of 0.19 ms, resulting in a 1.2% relative error. The measured jitter is shown in Figure 22. To minimize the impact of jitter in our application, the system’s reader records the oscillations for a sufficient period of time (e.g., 2 s) and uses the average of the n recorded periods for voltage-to-time conversion. This approach divides the error by the number of periods counted, leading to a considerable improvement in the relative error. At the cost of slowing down the measurement process, which is not a concern for our application, it makes a reasonable conversion possible.

Figure 22.

Jitter measurement of the proposed VCO at V and V.

A comparison with the existing literature has been made in Table 4. It is important to note that the data provided for this design, such as the frequency, are the average of all the measurements carried out, instead of specific sample results.

The VCOs that we found in the literature are centered in frequency ranges going from MHz to GHz, so they consume much more power, rendering them invalid for our microsystem and, thus, comparing this work to them may be meaningless. On the other hand, we found several oscillators (without voltage control) that aim at similar area, power and frequency constraints as the one proposed here. Apart from these limitations, all of these designs have in common that they are intended to be used in temperature-stable environments, since designing a temperature-compensated structure would involve a significant area penalty, as in [10,22,23,24].

Table 4.

Comparison of results against previous works.

Table 4.

Comparison of results against previous works.

| Reference | This Work | [7]a | [7]b | [8] | [9] | [5] | [6] | [25] |

|---|---|---|---|---|---|---|---|---|

| Oscillator | subth. | subth. | subth. | subth. | subth. | gate | gate | digital |

| principle | leakage | leakage | leakage | leakage | leakage | leakage | leakage | with DLS |

| Process (nm) | 65 | 180 | 180 | 250 | 350 | 130 | 55 | 180 |

| (V) | 0.3–1.2 | 0.2–1.8 | 0.2–1.8 | 2.5 | 3.3 | 0.6 | 0.29 | 0.4 |

| Freq. † (Hz) | 43.7–53.0 | 10–600 × 103 | 20 | 8.9 | 0.0308 | 0.09 | - | - |

| Freq. ‡ (Hz) | 2.2–2.46 | - | 20 | - | - | - | 0.64 * | 4 |

| Power (pW) | 4 ‡–210 † | 7 × –350 × | 3 ‡–230 † | 5.7 × | 1.98 × | 2 × | 4.5 | 3.32 |

| Area () | 592 | - | 630 | - | 25,000 | 480 | 28 | 1600 |

| Freq. control | yes | yes | no | no | no | no | no | no |

| Linear control | yes | no | no | no | no | no | no | no |

| FOM @ | 18.9 | - | 6.2 | - | 21.5 | 46.3 | - | - |

| FOM @ | 748.6 | - | 52.9 | - | - | - | 35,962.3 * | 141.2 |

* Frequency and duty cycle unstable in time. Max Freq. 2.36 Hz. Min Freq. 0.16 Hz; † at nominal ; ‡ at minimum .

The only VCO reported in Table 4 is [7]a, since it commits to ultra-low frequency, area, and power, which is the reason why it is necessary to point out some important differences between our work and [7]a not collected in Table 4. First, our VCO allows a linear frequency control, which is the best approach for time-domain digitization, while the VCO reported in [7]a presents an exponential frequency response. The input range in [7]a is very limited, in some cases as constrained as just 50 mV. Our VCO, on the other hand, provides the full input voltage swing while maintaining the linearity. The current drawn by the VCO in [7]a exhibits an undesirable exponential behavior as a function of the input voltage, deviating from the ultra-low power paradigm, but in our proposal it remains almost invariant at a very low value. Although the proposed VCO uses a smaller technology node, which should have higher process variability, the standard deviation over the mean () of this design is half that of [7]a, meaning that this design is less sensitive to process variations. Since the area of the VCO in [7]a was not reported and its power consumption is taken from the given graphs, where it is not very clear how much power it requires, their well-documented only oscillator version [7]b was also included in the comparison.

A figure of merit (FOM) has been proposed, to ease the comparison. The proposed FOM highlights those designs with low power consumption, low circuit area, low nominal frequency and large frequency variation (vs. the control voltage). Since the power consumption and the frequency are normally very dependent on the supply voltage, has also been added to the FOM, to try to counter the effect that the different supply voltages have on each design. For those works that reported power and frequency at nominal and minimum the FOM is given for both cases, for a fairer comparison. The proposed FOM showcases those works with better performance, in terms of the cited metrics with a higher score. The FOM is calculated with the following expression:

This FOM has been defined to allow comparison with simple oscillators, since there are no VCOs with characteristics similar to ours. This design ranks second in this FOM, among the works cited, for minimum supply voltage. However, in this figure of merit, we had to sacrifice important features of our design, such as linearity or control range, which impaired our metrics.

6. Conclusions

An ultra-low-area-power-and-frequency VCO has been designed and manufactured, using 65 nm technology as a digitization method, that saves area and power at the expense of accuracy compared to more conventional analog-to-digital converters. It is based on using a sub-threshold leakage current-type delay element and provides a quasi-linear response. It minimizes leakage and limits high peak currents while allowing rail-to-rail input range swing. The oscillator occupies 592 , operates in the frequency range of 43.7 Hz to 53.0 Hz and consumes a maximum average power of 210 pW at nominal supply voltage. The proposed circuit shows an excellent frequency–area–power compromise not only for MIT Smart Dust SynCells but also for any biomedical application where the available space is very limited and the temperature remains stable.

Author Contributions

Conceptualization, J.d.M.P., T.P., M.H. and M.L.V. Methodology, J.d.M.P.; Validation, J.d.M.P.; Formal analysis, J.d.M.P.; Investigation, J.d.M.P. and M.H.; Resources, T.P., M.H. and M.L.V.; Writing—original draft, J.d.M.P.; Writing—review & editing, M.L.V.; Supervision, T.P. and M.L.V.; Project administration, T.P. and M.L.V.; Funding acquisition, M.L.V. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by the NeuroSpaceWare project (PID2022-141391OB-C21) from the Ministry of Science, Innovation and Universities, and the grant Autonomous Sensing Platform for Structural Monitoring of Transmission Towers from the MIT.

Data Availability Statement

The original contributions presented in the study are included in the article, further inquiries can be directed to the corresponding author.

Conflicts of Interest

The authors declare no conflict of interest. Marek Hempel is employee of Analog Devices, Inc. The paper reflects the views of the scientists, and not the company.

References

- Hempel, M.; Schroeder, V.; Park, C.; Koman, V.B.; Xue, M.; McVay, E.; Spector, S.; Dubey, M.; Strano, M.S.; Park, J.; et al. SynCells: A 60 × 60 μm2 electronic platform with remote actuation for sensing applications in constrained environments. ACS Nano 2021, 15, 8803–8812. [Google Scholar] [CrossRef] [PubMed]

- Hamilton, J.; Yan, S.; Viswanathan, T. An uncalibrated 2 MHz, 6 mW, 63.5 dB SNDR discrete-time input VCO-based ΔΣ ADC. In Proceedings of the IEEE 2012 Custom Integrated Circuits Conference, San Jose, CA, USA, 9–12 September 2012; pp. 1–4. [Google Scholar]

- McNeill, J.A.; Majidi, R.; Gong, J. Split ADC background linearization of VCO-based ADCs. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 62, 49–58. [Google Scholar] [CrossRef]

- Funke, D.A.; Mayr, P.; Straczek, L.; McCaskill, J.S.; Oehm, J.; Pohl, N. A 200 μm by 100 μm Smart Dust system with an average current consumption of 1.3 nA. In Proceedings of the 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), Monte Carlo, Monaco, 11–14 December 2016; pp. 512–515. [Google Scholar] [CrossRef]

- Lin, Y.S.; Sylvester, D.; Blaauw, D. A sub-pW timer using gate leakage for ultra low-power sub-Hz monitoring systems. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 397–400. [Google Scholar]

- Nishio, Y.; Kobayashi, A.; Niitsu, K. Design and calibration of a small-footprint, low-frequency, and low-power gate leakage timer using differential leakage technique. IEICE Trans. Electron. 2019, 102, 269–275. [Google Scholar] [CrossRef]

- Funke, D.A.; Mayr, P.; Maeke, T.; McCaskill, J.S.; Sharma, A.; Straczek, L.; Oehm, J. Ultra low-power,-area and-frequency CMOS thyristor based oscillator for autonomous microsystems. Analog. Integr. Circuits Signal Process. 2016, 89, 347–356. [Google Scholar] [CrossRef]

- Mahato, A.K. Ultra low frequency CMOS ring oscillator design. In Proceedings of the 2014 Recent Advances in Engineering and Computational Sciences (RAECS), Chandigarh, India, 6–8 March 2014; pp. 1–5. [Google Scholar] [CrossRef]

- Ponce, P.M.; Sayed, G.; Saleh, L.A.; Krautschneider, W.H.; Kuhl, M. A 1.9 nw timer and clock generation unit for low data-rate implantable medical devices. In Proceedings of the 2020 IEEE 11th Latin American Symposium on Circuits & Systems (LASCAS), San José, Costa Rica, 25–28 February 2020; pp. 1–4. [Google Scholar]

- Geläschus, A.; Absar, M.W.; Singer, J.A.; Bahr, A.; Kuhl, M. Low Frequency and Low Power Oscillator using Thyristor-Based Delay Elements for Optoelectronic Implants. In Proceedings of the 2023 30th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Istanbul, Turkey, 4–7 December 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Hempel, M. Technology and Applications of 2D Materials in Micro- and Macroscale Electronics. Ph.D. Thesis, Massachusetts Institute of Technology, Cambridge, MA, USA, 2020. [Google Scholar]

- Kim, J.; Cho, S. A time-based analog-to-digital converter using a multi-phase voltage controlled oscillator. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems (ISCAS), Kos, Greece, 21–24 May 2006. [Google Scholar]

- Cui, J.; Pottosin, I.; Lamade, E.; Tcherkez, G. What is the role of putrescine accumulated under potassium deficiency? Plant Cell Environ. 2020, 43, 1331–1347. [Google Scholar] [CrossRef] [PubMed]

- Edwards, R.; Dainty, R.; Hibbard, C. Putrescine and cadaverine formation in vacuum packed beef. J. Appl. Microbiol. 1985, 58, 13–19. [Google Scholar] [CrossRef] [PubMed]

- Chen, X.F.; Xia, X.X.; Lee, S.Y.; Qian, Z.G. Engineering tunable biosensors for monitoring putrescine in Escherichia coli. Biotechnol. Bioeng. 2018, 115, 1014–1027. [Google Scholar] [CrossRef] [PubMed]

- González-Hernández, A.I.; Scalschi, L.; Vicedo, B.; Marcos-Barbero, E.L.; Morcuende, R.; Camañes, G. Putrescine: A key metabolite involved in plant development, tolerance and resistance responses to stress. Int. J. Mol. Sci. 2022, 23, 2971. [Google Scholar] [CrossRef] [PubMed]

- Kim, N.S.; Austin, T.; Baauw, D.; Mudge, T.; Flautner, K.; Hu, J.S.; Irwin, M.J.; Kandemir, M.; Narayanan, V. Leakage current: Moore’s law meets static power. Computer 2003, 36, 68–75. [Google Scholar]

- Rabaey, J. Low Power Design Essentials; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2009. [Google Scholar]

- Razavi, B. Design of Analog CMOS Integrated Circuits, 1st ed.; McGraw-Hill: New York, NY, USA, 2001. [Google Scholar]

- Hu, C. Modern Semiconductor Devices for Integrated Circuits; Prentice Hall: Upper Saddle River, NJ, USA, 2010; Volume 2. [Google Scholar]

- Kleider, J.P.; Alvarez, J.; Brézard-Oudot, A.; Gueunier-Farret, M.E.; Maslova, O. Revisiting the theory and usage of junction capacitance: Application to high efficiency amorphous/crystalline silicon heterojunction solar cells. Sol. Energy Mater. Sol. Cells 2015, 135, 8–16. [Google Scholar] [CrossRef]

- Lee, Y.; Giridhar, B.; Foo, Z.; Sylvester, D.; Blaauw, D.B. A sub-nW multi-stage temperature compensated timer for ultra-low-power sensor nodes. IEEE J.-Solid-State Circuits 2013, 48, 2511–2521. [Google Scholar] [CrossRef]

- Jeong, S.; Lee, I.; Blaauw, D.; Sylvester, D. A 5.8 nW CMOS wake-up timer for ultra-low-power wireless applications. IEEE J.-Solid-State Circuits 2015, 50, 1754–1763. [Google Scholar] [CrossRef]

- Kobayashi, A.; Niitsu, K. Low-Voltage Gate-Leakage-Based Timer Using an Amplifier-Less Replica-Bias Switching Technique in 55-nm DDC CMOS. IEEE Open J. Circuits Syst. 2020, 1, 107–114. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Lin, L.; Alioto, M. A pW-power Hz-range oscillator operating with a 0.3–1.8-V unregulated supply. IEEE J.-Solid-State Circuits 2019, 54, 1487–1496. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).