Enhancement of Electrical Safe Operation Area of 60 V nLDMOS by Engineering of Reduced Surface Electrical Field in the Drift Region

Abstract

:1. Introduction

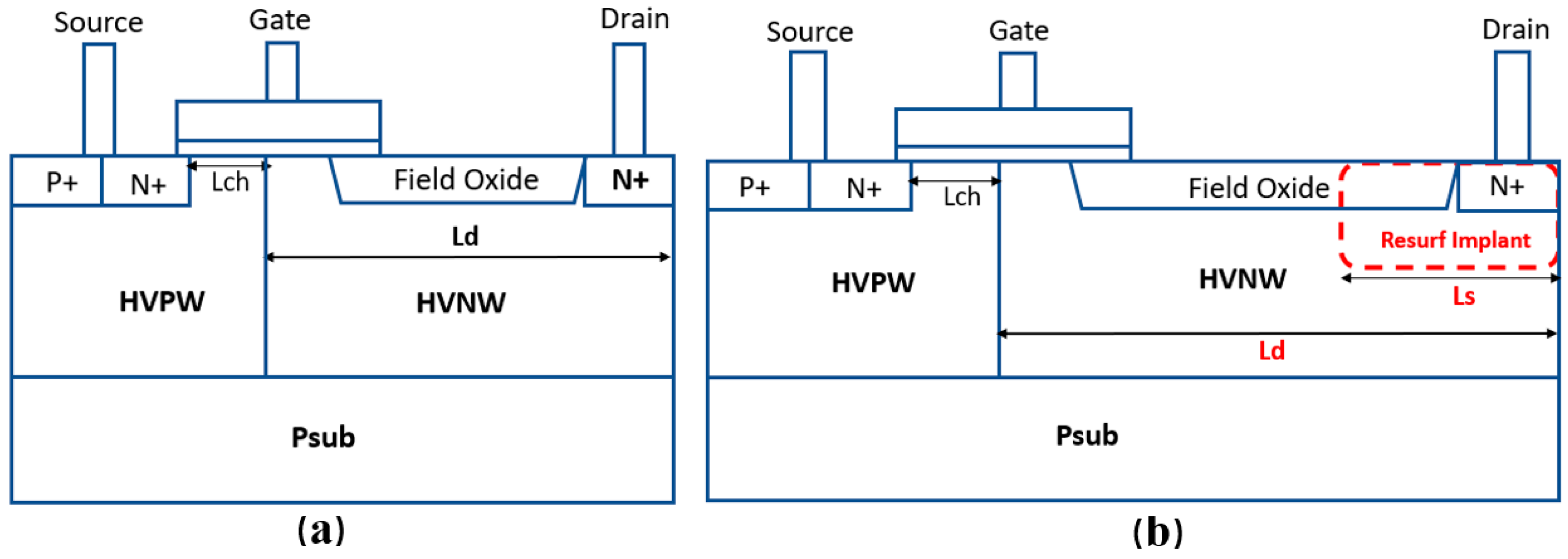

2. Materials and Methods

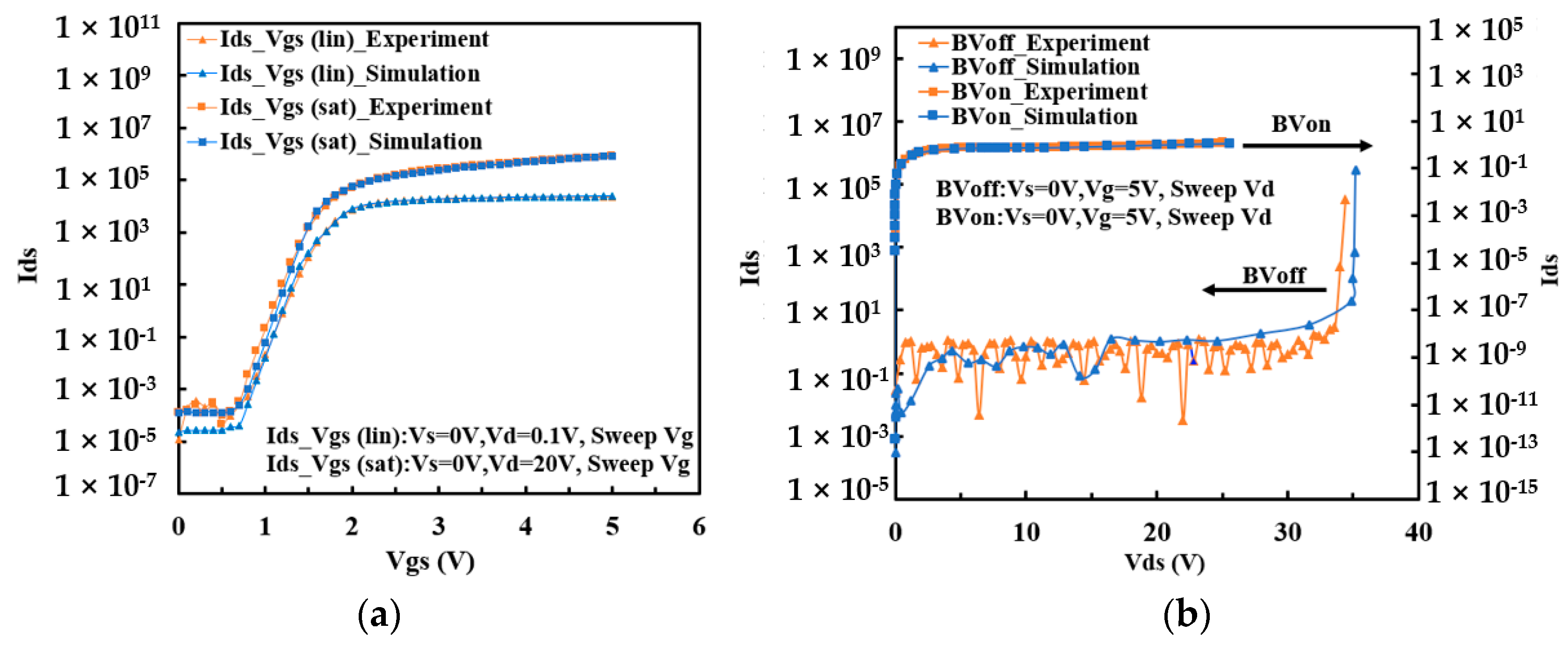

3. Results

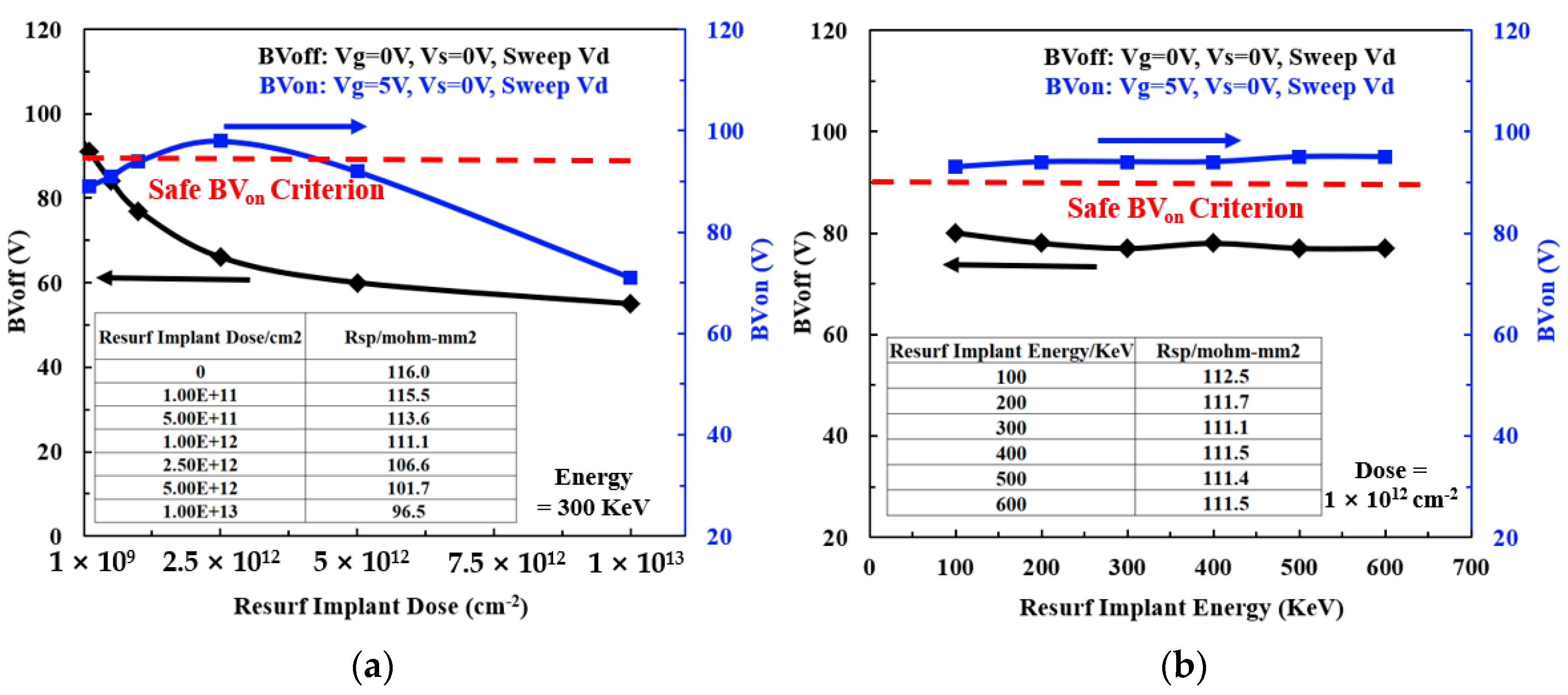

3.1. Effect of Resurf Ion Implantation Dose and Energy on BVon, BVoff, and RON,sp

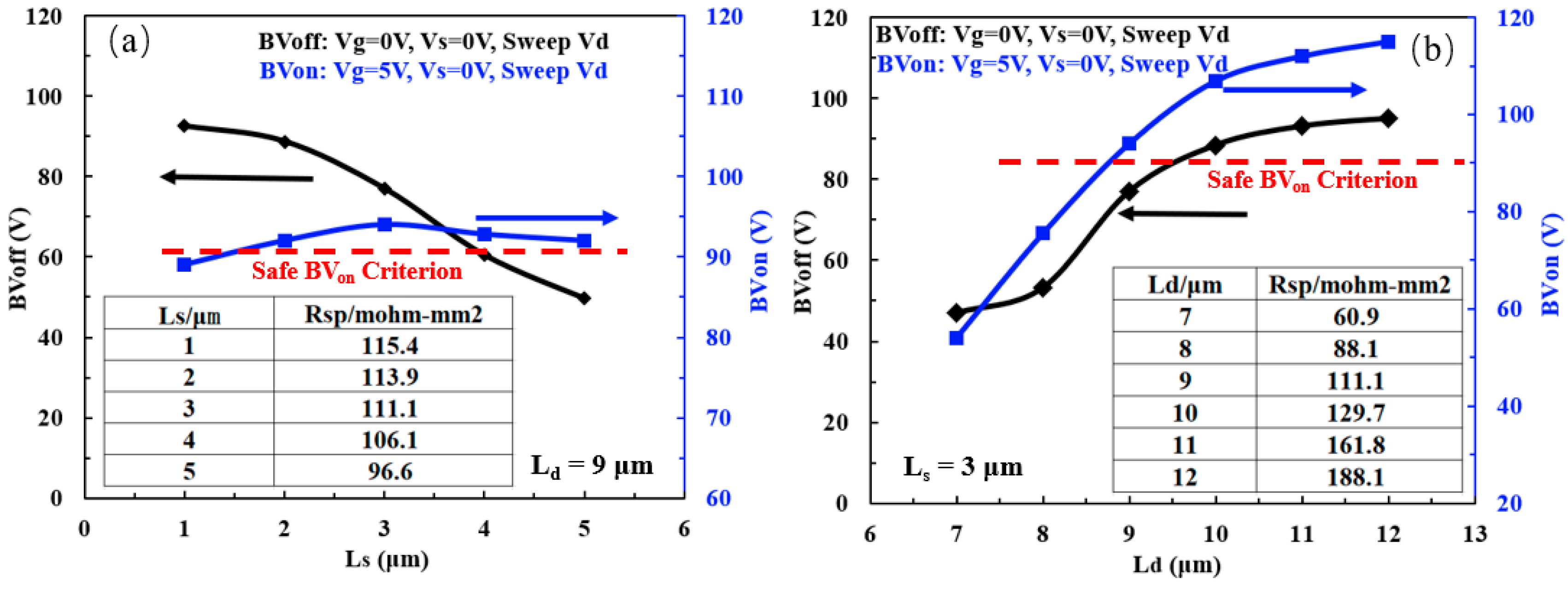

3.2. Effect of Resurf Ion Implantation Length Ls and the n-Drift Region Length Ld on BVon, BVoff, and RON,sp

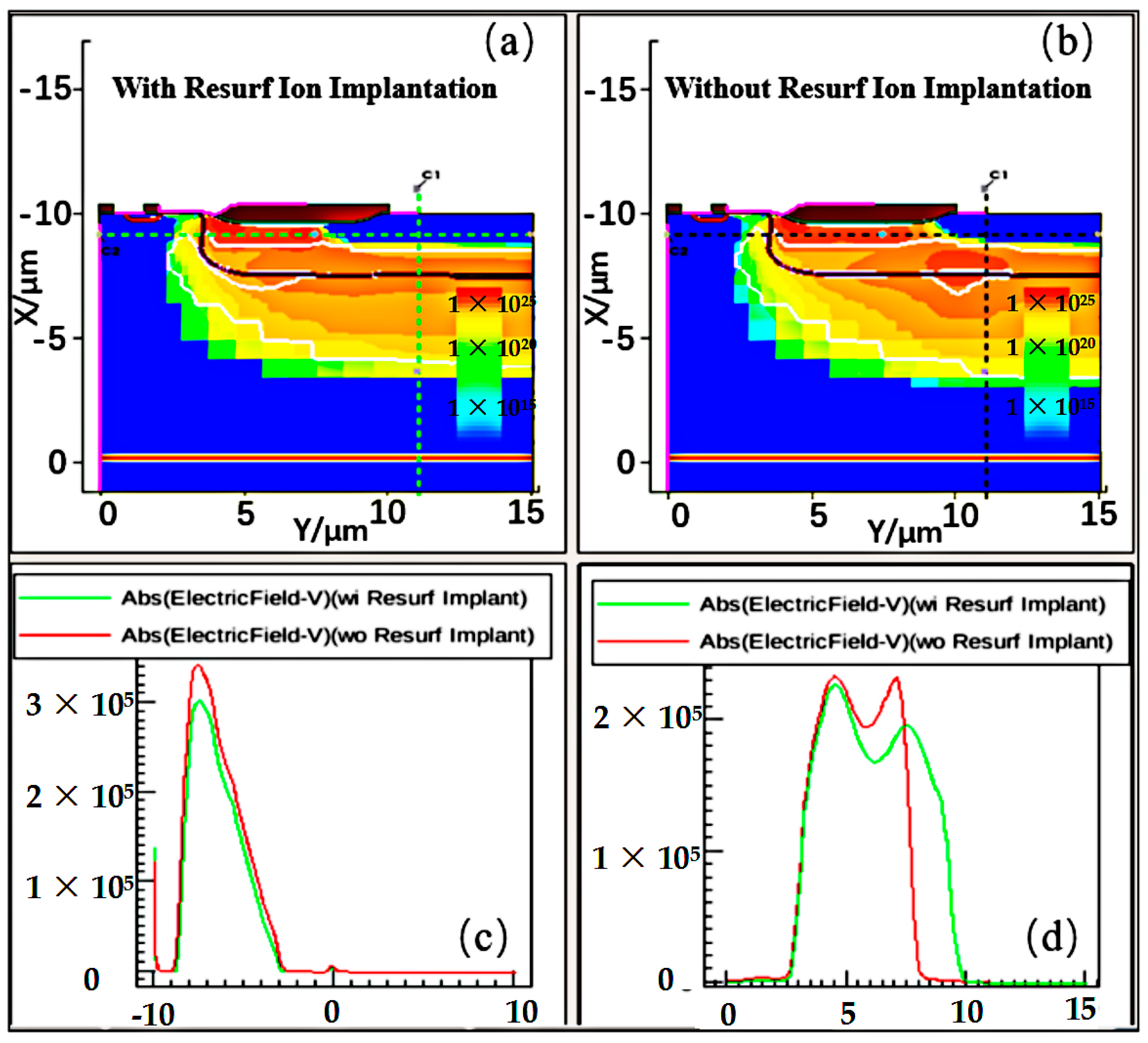

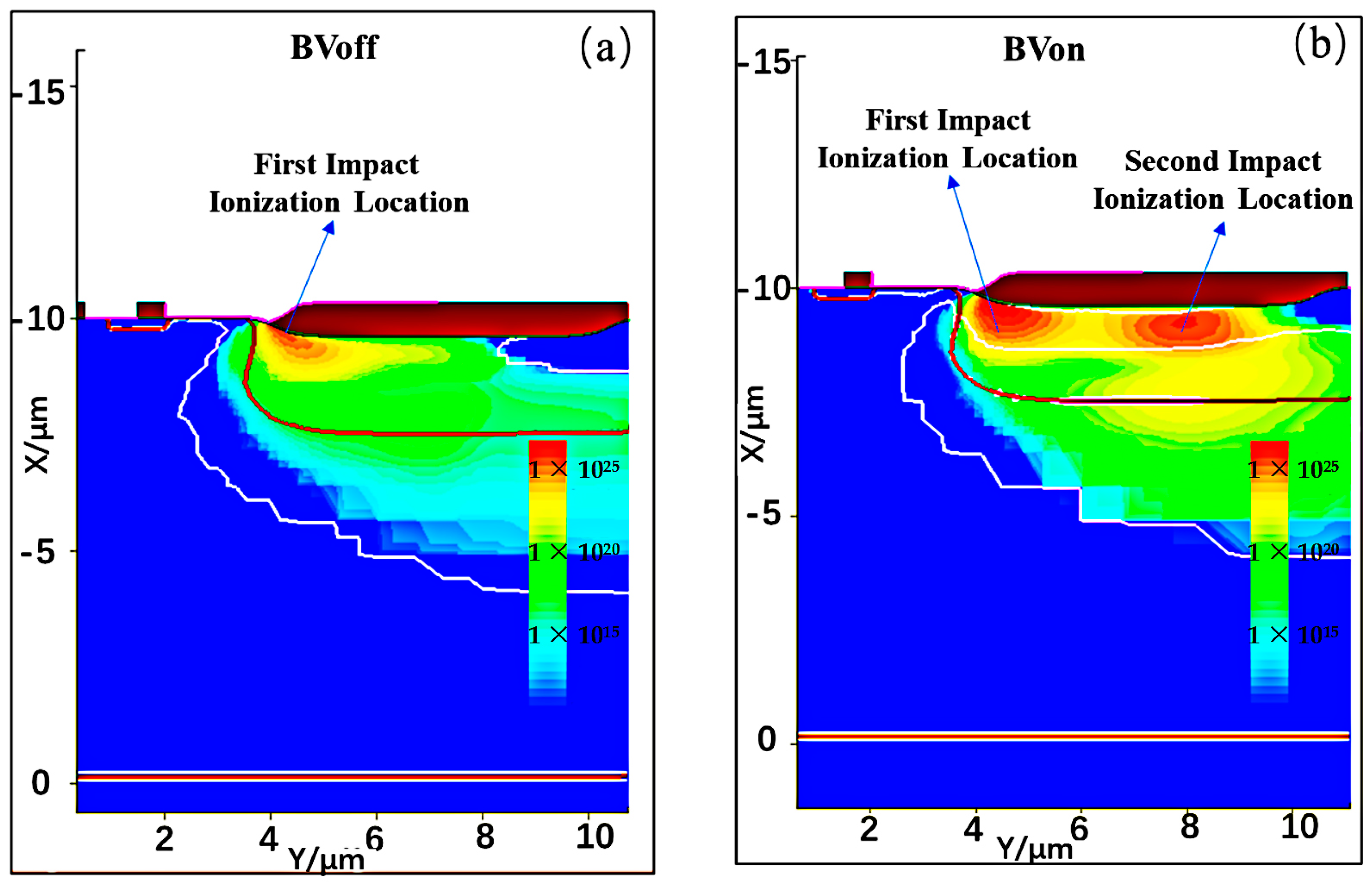

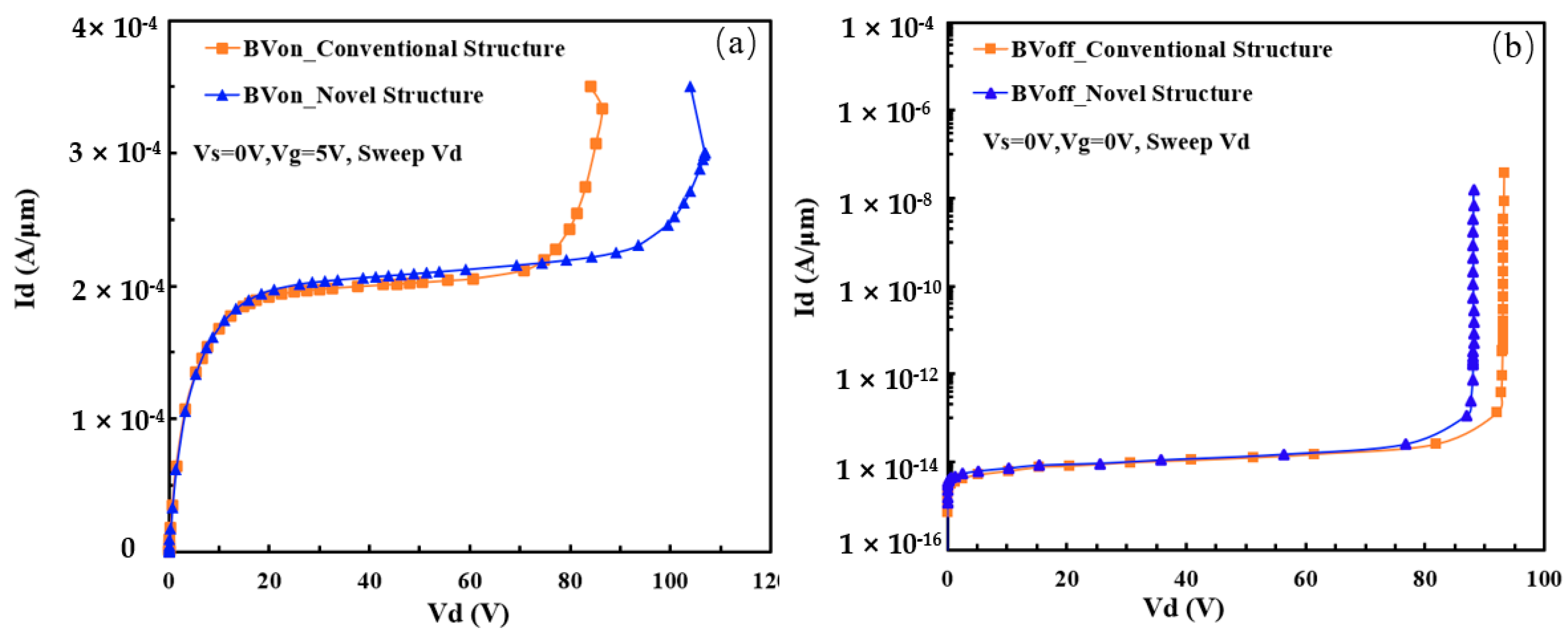

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Antonio, A.; Claudio, C.; Paola, G. A Novel Integrated Silicon Gate Technology Combining Bipolar Linear, CMOS Logic, and DMOS Power Parts. IEEE Trans. Electron Devices 1986, 33, 2025–2030. [Google Scholar]

- Claudio, C.; Antonio, A.; Paola, G. Roadmap Differentiation and Emerging Trends in BCD Technology. In Proceedings of the 32nd European Solid-State Device Research, Firenze, Italy, 17 October 2002. [Google Scholar]

- Norio, Y.; Ken’ichi, M.; Kazuya, N.; Bungo, T.; Shin’ichi, H.; Akio, N.; Kazutoshi, N. Low Gate Charge 30V N-channel LDMOS for DC-DC Converters. In Proceedings of the International Symposium on Power Semiconductor Devices ICs, Cambridge, UK, 14–17 April 2003. [Google Scholar]

- Park, M.Y.; Kim, J.; Lee, D.W.; Park, J.S.; Cho, K.I.; Cho, H.J. A 100 V, 10 mA High-Voltage Driver ICs for Field Emission Display Applications. In Proceedings of the First IEEE Asia Pacific Conference on ASICs, Seoul, Republic of Korea, 23–25 August 1999. [Google Scholar]

- Rosario, P.; Michael, B.; Russell, E. A 0.18 μm Monolithic Li-Ion Battery Charger for Wireless Devices Based on Partial Current Sensing and Adaptive Reference Voltage. IEEE Electron Device Lett. 2011, 33, 471–473. [Google Scholar]

- Elizabeth, K.C.T.; Norhuzaimin, J.; Hu, Y.H.; Deb, K.P.; Tia, S.H. Design of 0.18 μm High Voltage LDMOS for Automotive Application. In Proceedings of the 2008 IEEE International Conference on Semiconductor Electronics, Johor Bahru, Malaysia, 25–27 November 2008. [Google Scholar]

- Hower, P.; Lin, J.; Pendharkar, S.; Hu, B.; Arch, J.; Smith, J.; Efland, T. A Rugged NLDMOS for LBC5 Technology. In Proceedings of the 17 International Symposium on Power Semiconductor Devices & IC’s, Santa Barbara, CA, USA, 23–26 May 2005. [Google Scholar]

- Kocon, C.; Zeng, J.; Stokes, R. Implant Spacer Optimization for the Improvement of Power MOSFETs’ Unclamped Inductive Switching (UIS) and High Temperature Breakdown. In Proceedings of the 12th International Symposium on Power Semiconductor Devices & ICs, Toulouse, France, 22–25 May 2000. [Google Scholar]

- Zhou, X.; Jacky, C.W.N.; Johnny, K.O.S. A Novel SONOS Gate Power MOSFET with Excellent UIS Capability. IEEE Electron Device Lett. 2011, 32, 1415–1417. [Google Scholar] [CrossRef]

- Kawamoto, K.; Takahashi, S.; Fujino, S.; Shirakawa, I. A No-Snapback LDMOSFET with Automotive ESD Endurance. IEEE Trans. Electron Devices 2002, 49, 2047–2053. [Google Scholar] [CrossRef]

- Khan, T.; Khemka, V.; Zhu, R.H.; Bose, A. Rugged Dotted-Channel NLDMOS Structure. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008. [Google Scholar]

- Kobori, E.; Izumi, N.; Kumamoto, N.; Hamazawa, Y. Efficiency of Power Devices Using Full Cu Metallization Technologies. In Proceedings of the 11th International Symposium on Power Semiconductor Devices and ICs, Toronto, ON, Canada, 26–28 May 1999. [Google Scholar]

- Khemka, V.; Parthasarathy, V.; Zhu, R.H.; Bose, A.; Roggenbauer, T. Detection and Optimization of Temperature Distribution Across Large-Area Power MOSFETs to Improve Energy Capability. IEEE Trans. Electron Devices 2004, 51, 1025–1032. [Google Scholar] [CrossRef]

- Hower, P.L.; Merchant, S. Snapback and Safe Operating Area of NLDMOS Transistors. In Proceedings of the IEEE International Electron Devices Meeting 1999, Washington, DC, USA, 5–8 December 1999. [Google Scholar]

- Kinoshita, K.; Kawaguchi, Y.; Nakagawa, A. A New Adaptive Resurf Concept for 20 V LDMOS without Breakdown Voltage Degradation at High Current. In Proceedings of the 10th International Symposium on Power Semiconductor Devices and ICs, Kyoto, Japan, 3–6 June 1998. [Google Scholar]

- Hower, P.; Lin, J.; Merchant, S.; Paiva, S. Using Adaptive Resurf to Improve the SOA of NLDMOS Transistors. In Proceedings of the 12th International Symposium on Power Semiconductor Devices & ICs, Toulouse, France, 22–25 May 2000. [Google Scholar]

- Bakeroot, B.; Moens, P.; Vermandel, M.; Doutreloigne, J. Using Adaptive Resurf Technique and Field Plate Working to Improve the Safe Operating Area of N-type Drain Extended MOS Transistors. In Proceedings of the International Conference on Modeling & Simulation of Microsystems, Head Island, SC, USA, 19–21 March 2001. [Google Scholar]

- Parthasarathy, V.; Khemka, V.; Zhu, R.; Whitfield, J.; Ida, R.; Bose, A. Drain Profile Engineering of Resurf LDMOS Devices for ESD Ruggedness. In Proceedings of the 14th International Symposium on Power Semiconductor Devices and Ics, Sante Fe, NM, USA, 7 June 2002. [Google Scholar]

- Parthasarathy, V.; Khemka, V.; Zhu, R.; Whitfield, J.; Ida, R.; Bose, A. A Double Resurf LDMOS with Drain Profile Engineering for Improved ESD Robustness. IEEE Electron Device Lett. 2002, 23, 212–214. [Google Scholar] [CrossRef]

- Chen, W.Y.; Ker, M.D. Characterization of SOA in Time Domain and the Improvement Techniques for Using in High-Voltage Integrated Circuits. IEEE Trans. Device Mater. Reliab. 2012, 12, 382–390. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, L.; Zhu, B.; Wu, X.; Ding, S. Enhancement of Electrical Safe Operation Area of 60 V nLDMOS by Engineering of Reduced Surface Electrical Field in the Drift Region. Micromachines 2024, 15, 815. https://doi.org/10.3390/mi15070815

Li L, Zhu B, Wu X, Ding S. Enhancement of Electrical Safe Operation Area of 60 V nLDMOS by Engineering of Reduced Surface Electrical Field in the Drift Region. Micromachines. 2024; 15(7):815. https://doi.org/10.3390/mi15070815

Chicago/Turabian StyleLi, Lianjie, Bao Zhu, Xiaohan Wu, and Shijin Ding. 2024. "Enhancement of Electrical Safe Operation Area of 60 V nLDMOS by Engineering of Reduced Surface Electrical Field in the Drift Region" Micromachines 15, no. 7: 815. https://doi.org/10.3390/mi15070815