A V-Band Wideband Power Amplifier with High Gain in a 130 nm SiGe BiCMOS Process

Abstract

1. Introduction

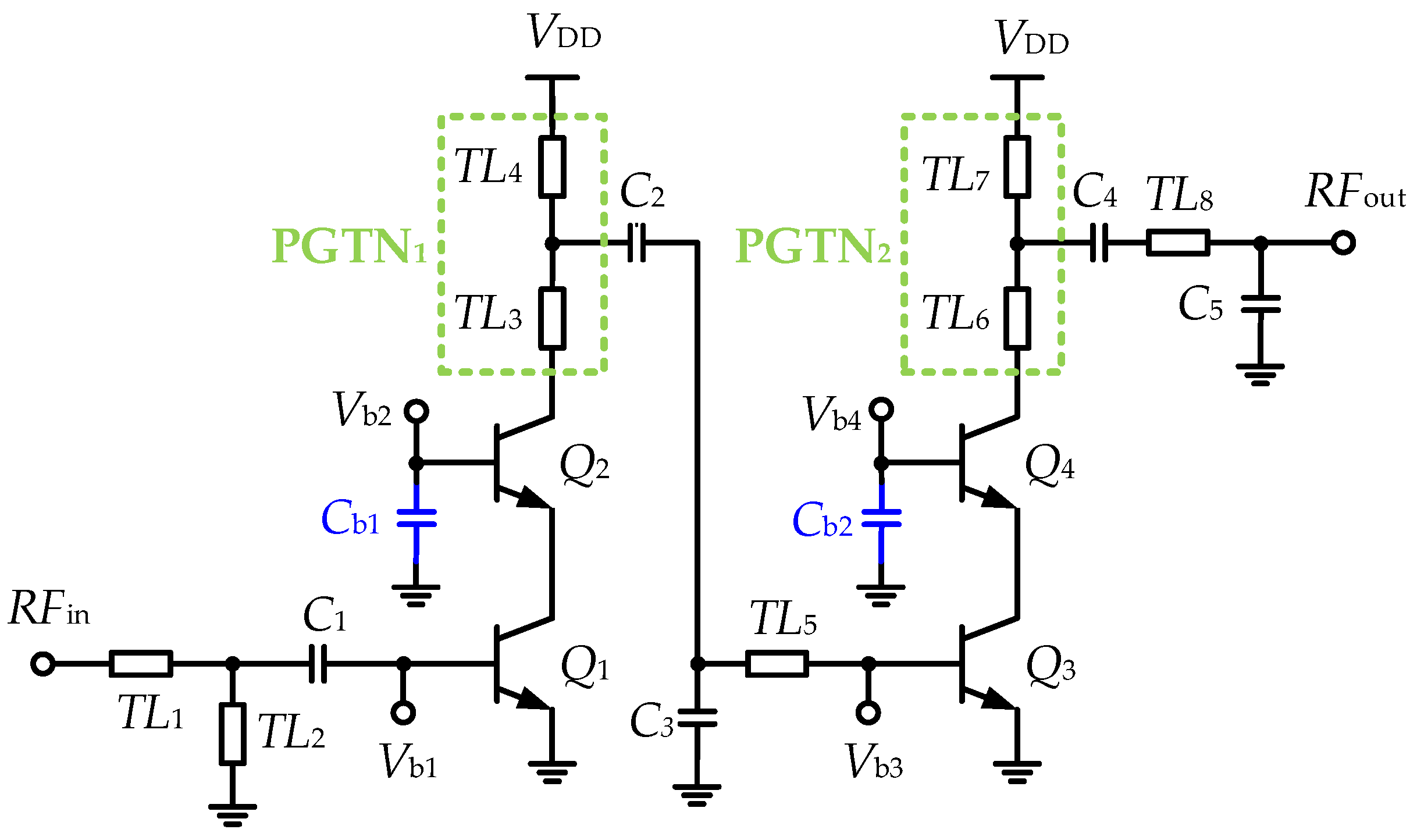

2. Circuit Analysis and Design

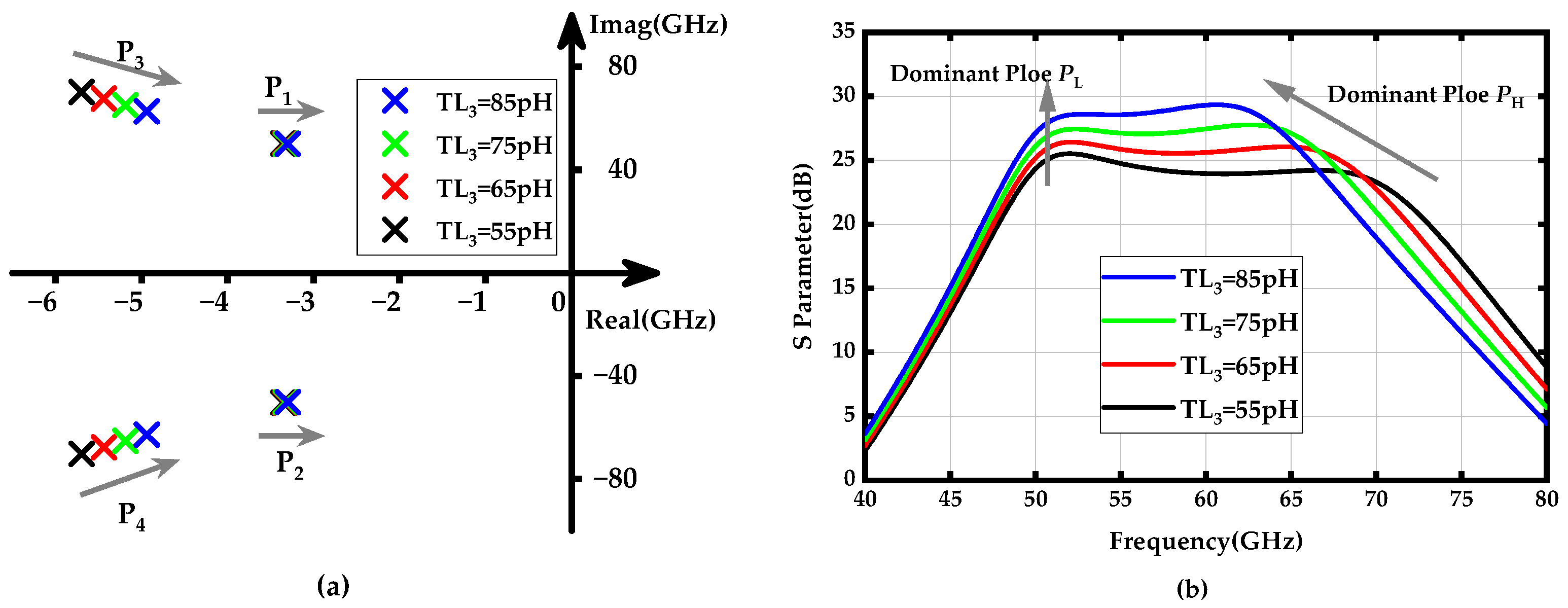

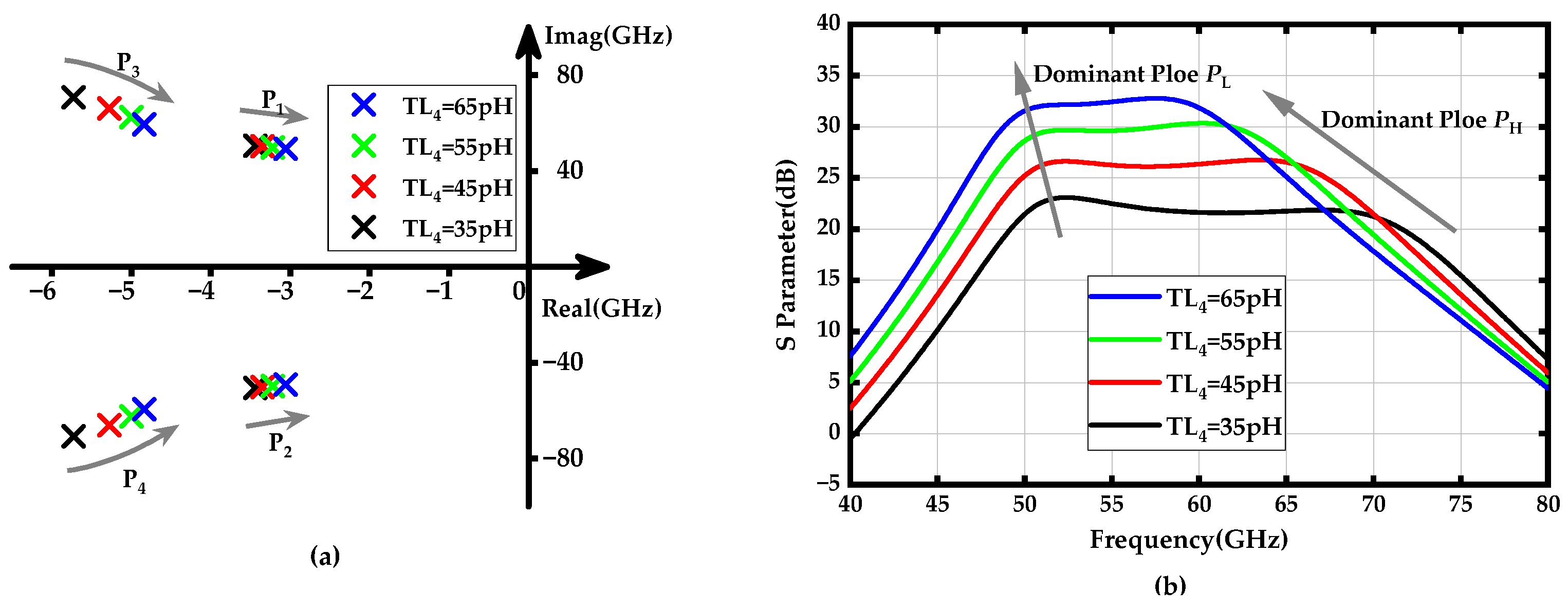

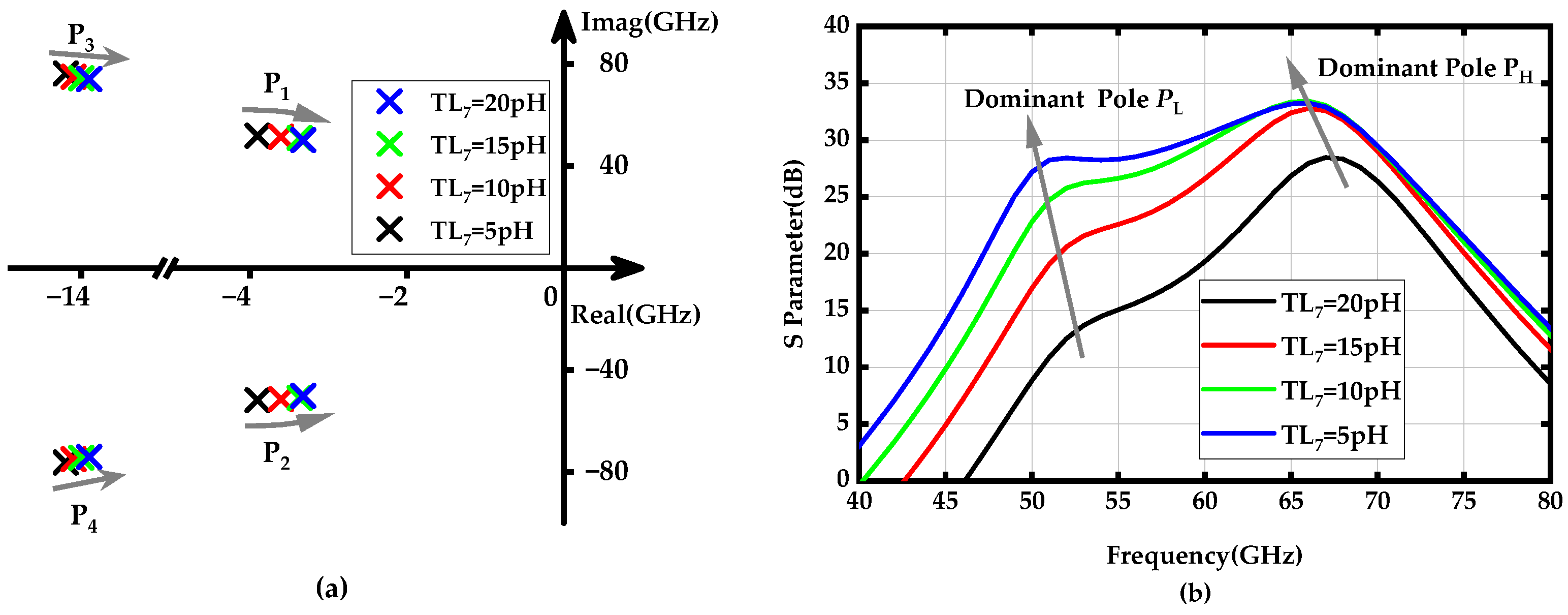

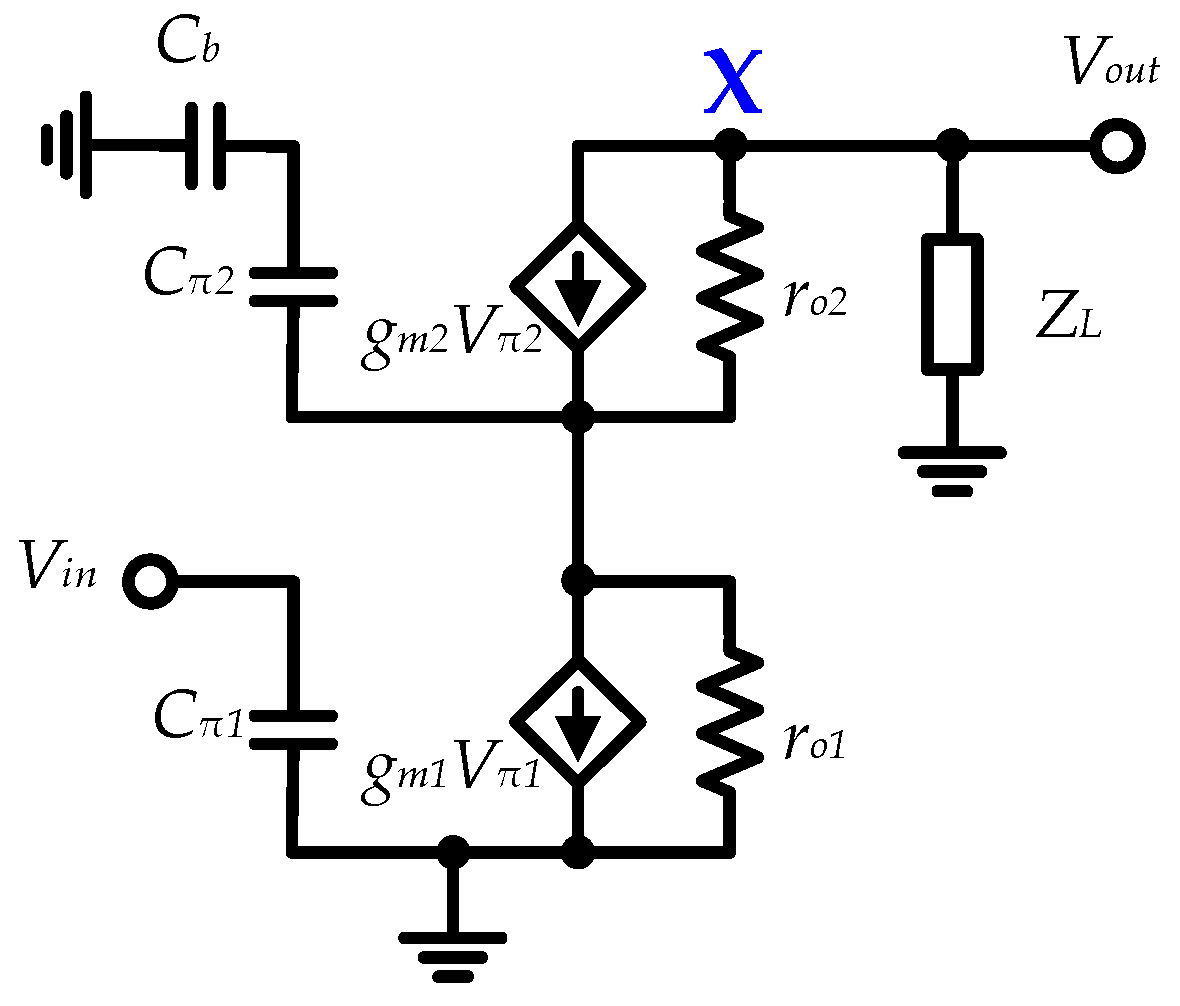

2.1. Bandwidth Extension with Pole-Gain Tuning

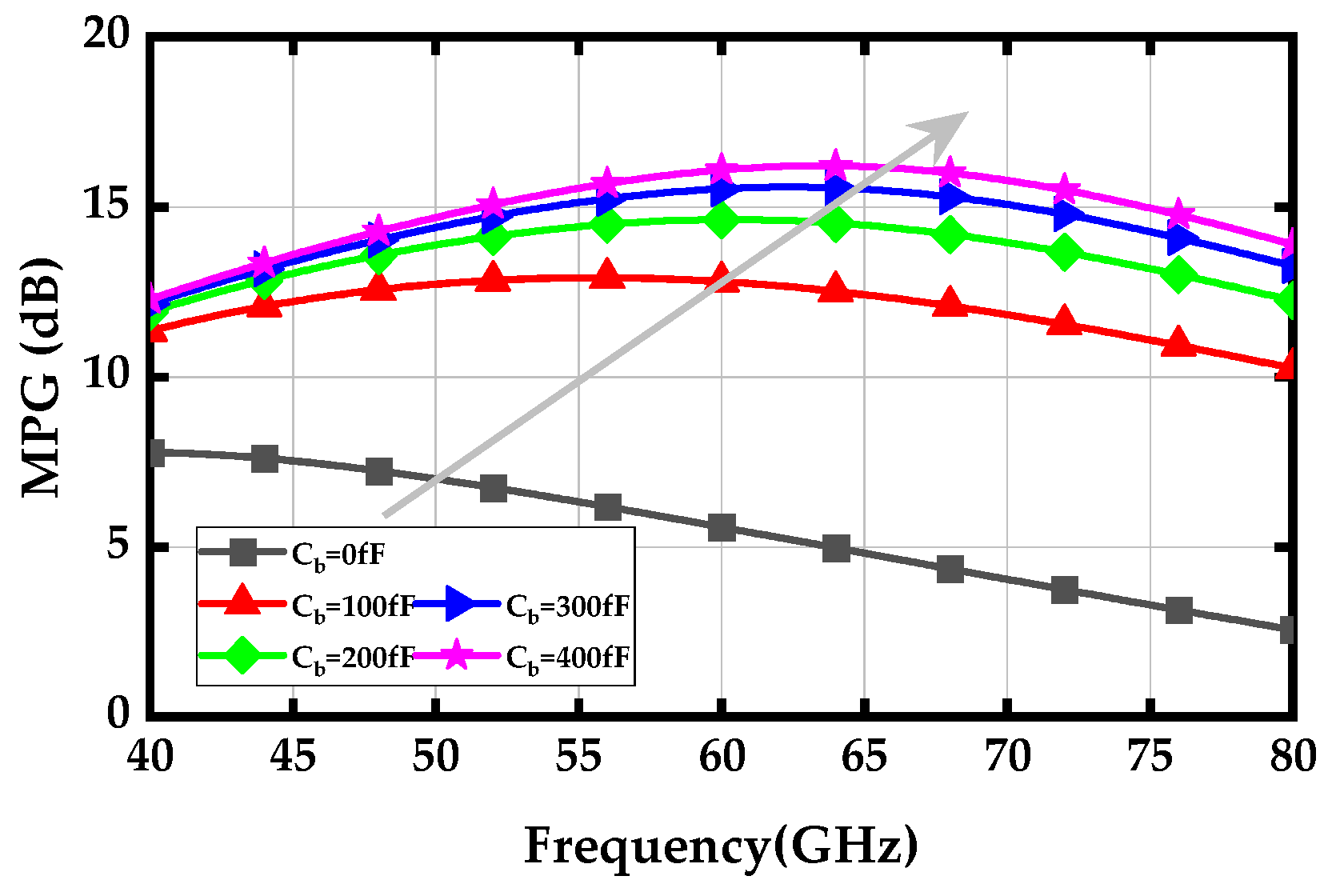

2.2. Common-Base Capacitive Peaking Technique

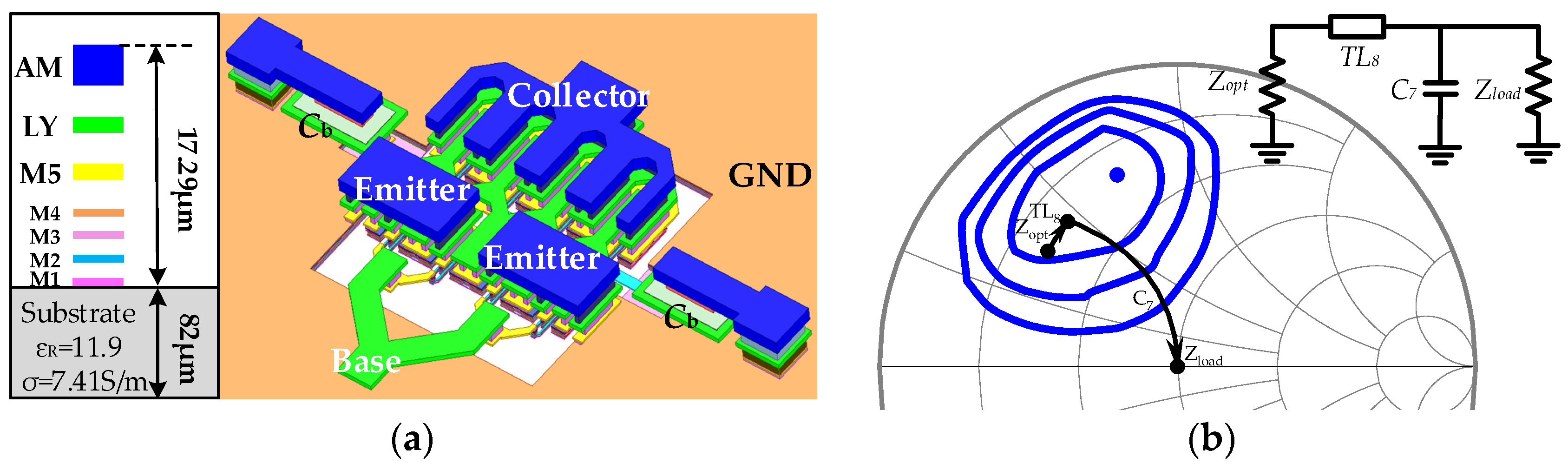

2.3. Layout Configuration of Power Stage Transistors

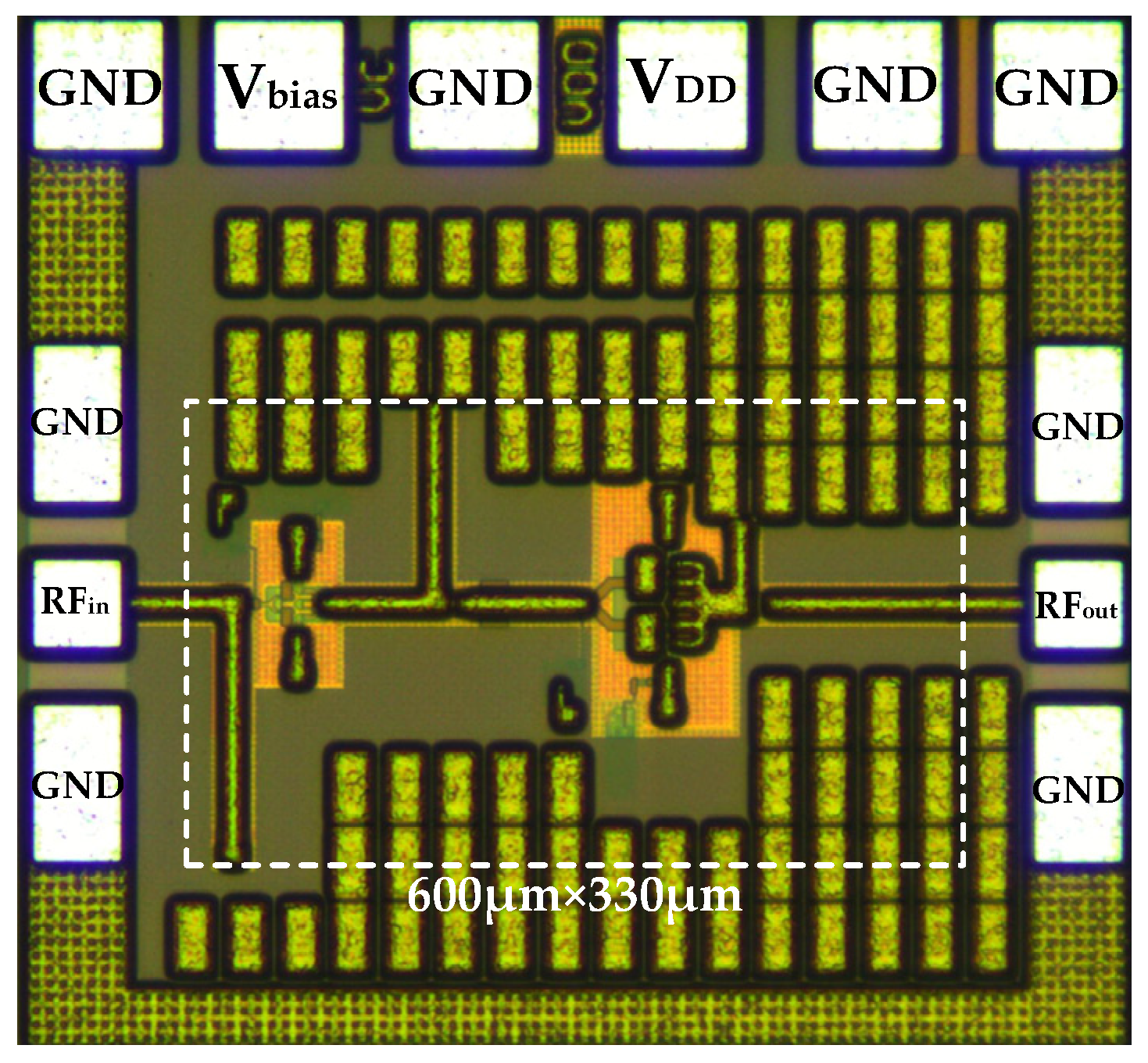

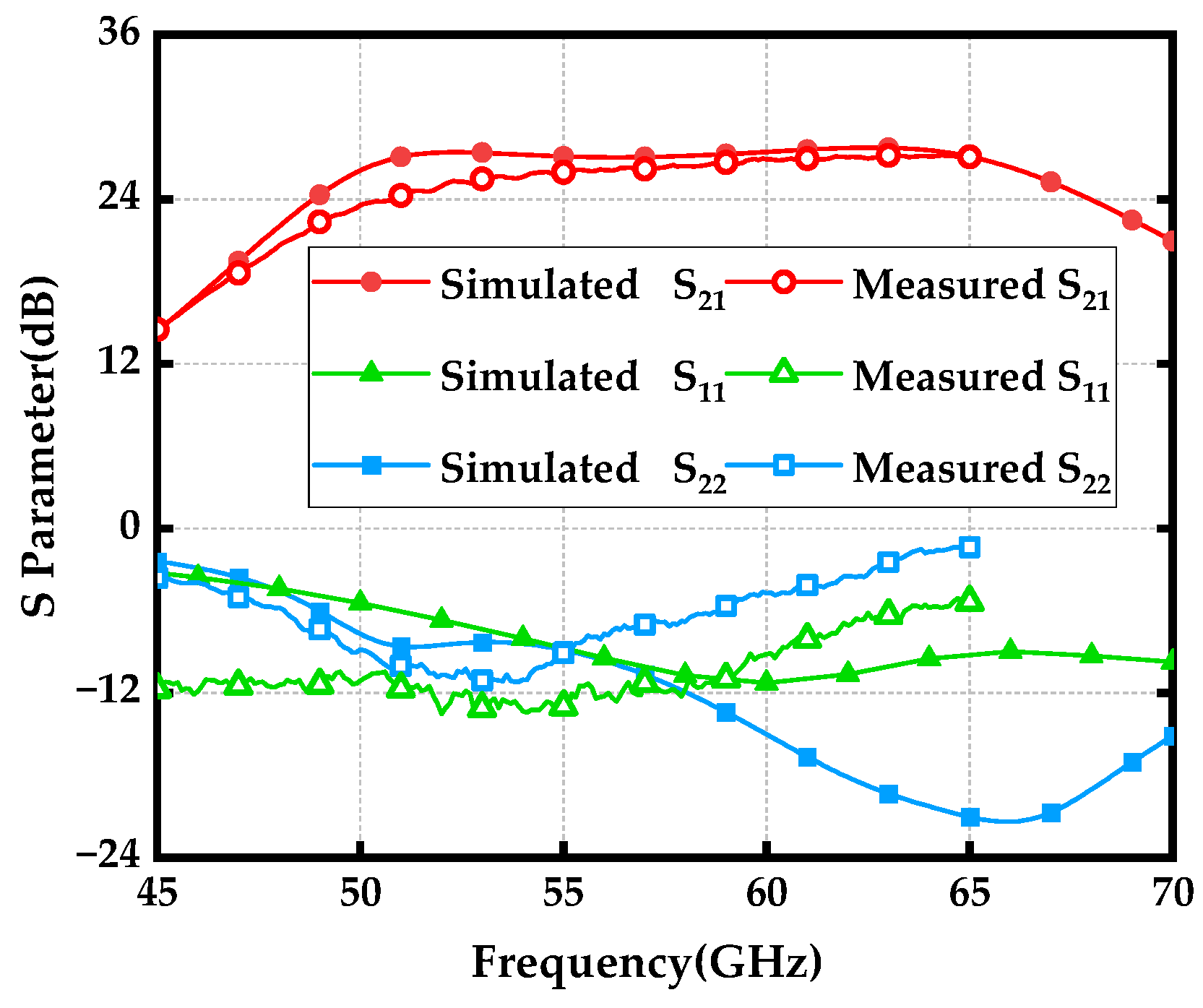

3. Experimental Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- So, C.; Sung, E.-T.; Hong, S. A V-Band Four-Channel Phased Array Transmitter Front-End With 0.7 Phase Step and 20 dB Gain Dynamic Range. IEEE Trans. Microw. Theory Tech. 2024, 72, 2799–2808. [Google Scholar] [CrossRef]

- Sutbas, B.; Ng, H.J.; Eissa, M.H.; Kahmen, G. A low-power V-band radar transceiver front-end chip using 1.5 V supply in 130-nm SiGe BiCMOS. IEEE Trans. Microw. Theory Tech. 2023, 71, 4855–4868. [Google Scholar] [CrossRef]

- Gadallah, A.; Franzese, A.; Eissa, M.H.; Drenkhahn, K.E.; Kissinger, D.; Malignaggi, A. A 4-channel V-band beamformer featuring a switchless PALNA for scalable phased array systems. In Proceedings of the 2021 IEEE MTT-S International Microwave Symposium (IMS), Atlanta, GA, USA, 7–25 June 2021; pp. 839–841. [Google Scholar]

- Gadallah, A.; Eissa, M.H.; Kissinger, D.; Malignaggi, A. A V-band miniaturized bidirectional switchless PALNA in SiGe: C BiCMOS technology. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 786–789. [Google Scholar] [CrossRef]

- Sarkar, A.; Aryanfar, F.; Floyd, B.A. A 28-GHz SiGe BiCMOS PA with 32% efficiency and 23-dBm output power. IEEE J. Solid-State Circuits 2017, 52, 1680–1686. [Google Scholar] [CrossRef]

- Yin, T.; Pappu, A.M.; Apsel, A.B. Low-cost, high-efficiency, and high-speed SiGe phototransistors in commercial BiCMOS. IEEE Photonics Technol. Lett. 2005, 18, 55–57. [Google Scholar] [CrossRef]

- Ding, R.; Xuan, Z.; Yao, P.; Baehr-Jones, T.; Prather, D.; Hochberg, M. Power-efficient low-noise 86 GHz broadband Amplifier in 130 nm SiGe BiCMOS. Electron. Lett. 2014, 50, 741–743. [Google Scholar] [CrossRef]

- Zhao, J.; Bassi, M.; Bevilacqua, A.; Ghilioni, A.; Mazzanti, A.; Svelto, F. A 40–67GHz power amplifier with 13 dBm PSAT and 16% PAE in 28 nm CMOS LP. In Proceedings of the ESSCIRC 2014-40th European Solid State Circuits Conference (ESSCIRC), Venice Lido, Italy, 22–26 September 2014; pp. 179–182. [Google Scholar]

- Zhou, P.; Yan, P.; Chen, J.; Chen, Z.; Hong, W. A 77 GHz Power Amplifier with 19.1 dBm Peak Output Power in 130 nm SiGe Process. Micromachines 2023, 14, 2238. [Google Scholar] [CrossRef] [PubMed]

- Wang, L.; Chen, J.; Hou, D.; Hong, W. A 45 GHz Low-Voltage Cascode Power Amplifier Based on Capacitor Coupling Technology. In Proceedings of the 2021 IEEE MTT-S International Wireless Symposium (IWS), Nanjing, China, 23–26 May 2021; pp. 1–3. [Google Scholar]

- Ferchichi, A.; Rehman, S.U.; Carta, C.; Ellinger, F. 60-GHz SiGe-BiCMOS power amplifier with 14.7 dBm output power and 18 dB power gain. In Proceedings of the 2019 12th German Microwave Conference (GeMiC), Stuttgart, Germany, 25–27 March 2019; pp. 229–231. [Google Scholar]

- Lee, S.; Ju, I.; Gong, Y.; Cardoso, A.S.; Connor, J.D.; Cho, M.-K.; Cressler, J.D. Design of an 18–50 GHz SiGe HBT cascode non-uniform distributed power amplifier. In Proceedings of the 2020 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Monterey, CA, USA, 16–19 November 2020; pp. 1–4. [Google Scholar]

- Schoepfel, J.; Rücker, H.; Pohl, N. A Differential SiGe HBT Doherty Power Amplifier for Automotive Radar at 79 GHz. In Proceedings of the 2023 IEEE 23rd Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, Las Vegas, NV, USA, 22–25 January 2023; pp. 44–46. [Google Scholar]

- Chen, J.-C.; Chang, T.-Y.; Chiang, Y.-C. A V-band power amplifier using Marchand balun for power combining in 90n-nm CMOS process. In Proceedings of the 2017 IEEE Wireless Power Transfer Conference (WPTC), Taipei, Taiwan, 10–12 May 2017; pp. 1–3. [Google Scholar]

- Chou, C.-F.; Hsiao, Y.-H.; Wu, Y.-C.; Lin, Y.-H.; Wu, C.-W.; Wang, H. Design of a $ V $-Band 20-dBm wideband power amplifier using transformer-based radial power combining in 90-nm CMOS. IEEE Trans. Microw. Theory Tech. 2016, 64, 4545–4560. [Google Scholar] [CrossRef]

- Liu, J.Y.-C.; Tang, A.; Wang, N.-Y.; Gu, Q.J.; Berenguer, R.; Hsieh, H.-H.; Wu, P.-Y.; Jou, C.; Chang, M.-C.F. A V-band self-healing power amplifier with adaptive feedback bias control in 65 nm CMOS. In Proceedings of the 2011 IEEE Radio Frequency Integrated Circuits Symposium, Baltimore, MD, USA, 5–7 June 2011; pp. 1–4. [Google Scholar]

- Cui, M.; Tibenszky, Z.; Carta, C.; Ellinger, F. Design of a Compact Power Amplifier with 18.6 dBm 60 GHz 20.5% PAE in 22 nm FD-SOI. In Proceedings of the 2020 15th European Microwave Integrated Circuits Conference (EuMIC), Utrecht, The Netherlands, 10–15 January 2021; pp. 141–144. [Google Scholar]

- Wang, Y.; Chen, T.; Wu, L. A 60-GHz Two-Way Transformer-Coupled Power Amplifier in 65-nm CMOS. In Proceedings of the 2022 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Guangzhou, China, 27–29 November 2022; pp. 1–3. [Google Scholar]

- Feng, G.; Boon, C.C.; Meng, F.; Yi, X.; Yang, K.; Li, C.; Luong, H.C. Pole-converging intrastage bandwidth extension technique for wideband amplifiers. IEEE J. Solid-State Circuits 2017, 52, 769–780. [Google Scholar] [CrossRef]

- Luo, J.; He, J.; Feng, G.; Apriyana, A.; Fang, Y.; Xue, Z.; Huang, Q.; Yu, H. A D-band amplifier in 65 nm bulk CMOS for short-distance data center communication. IEEE Access 2018, 6, 53191–53200. [Google Scholar] [CrossRef]

| Ref. | Technology | Bandwidth (GHz) | FBW (%) | Gain (dB) | P1dB (dBm) | Psat (dBm) | Pdc (mw) | Size (mm2) |

|---|---|---|---|---|---|---|---|---|

| [17] | 22 nm SOI CMOS | 56.5–63.5 (7) | 11.7 | 22@60 GHz | 15.7 | 18.6 | 351 | 0.43 |

| [18] | 65 nm CMOS | 50.2–59.4 (9.2) | 16.78 | 20.8@54.4 GHz | 5.9 | 13.0 | - | 0.3 |

| [8] | 28 nm CMOS | 40–67 (27) | 51 | 13@50 GHz | 12 | 13 | - | 0.33 |

| [11] | 130 nm SiGe BiCMOS | 54–66 (12) | 20.0 | 18@61.5 GHz | 12 | 14.7 | - | 0.30 |

| [10] | 130 nm SiGe BiCMOS | 42–48.5 (6.5) | 14.36 | 29.5@44 GHz * | 14.8 | 16.2 * | - | 1.00 |

| [9] | 130 nm SiGe BiCMOS | 52–83.4 * (31.4) | 46.38 * | 17.5@77 GHz | >16 | 19.1 | - | 0.68 |

| This work | 130 nm SiGe BiCMOS | 52–65 (>13) | >22.2 | 27.3@64 GHz | 18 | 19.7 | 115.5 | 0.57 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hu, J.; Wan, J.; Shen, Y.; Zhao, W.; Luo, J. A V-Band Wideband Power Amplifier with High Gain in a 130 nm SiGe BiCMOS Process. Micromachines 2024, 15, 1077. https://doi.org/10.3390/mi15091077

Hu J, Wan J, Shen Y, Zhao W, Luo J. A V-Band Wideband Power Amplifier with High Gain in a 130 nm SiGe BiCMOS Process. Micromachines. 2024; 15(9):1077. https://doi.org/10.3390/mi15091077

Chicago/Turabian StyleHu, Jianing, Jialong Wan, Yi Shen, Wei Zhao, and Jiang Luo. 2024. "A V-Band Wideband Power Amplifier with High Gain in a 130 nm SiGe BiCMOS Process" Micromachines 15, no. 9: 1077. https://doi.org/10.3390/mi15091077

APA StyleHu, J., Wan, J., Shen, Y., Zhao, W., & Luo, J. (2024). A V-Band Wideband Power Amplifier with High Gain in a 130 nm SiGe BiCMOS Process. Micromachines, 15(9), 1077. https://doi.org/10.3390/mi15091077