A High-Density 4H-SiC MOSFET Based on a Buried Field Limiting Ring with Low Qgd and Ron

Abstract

1. Introduction

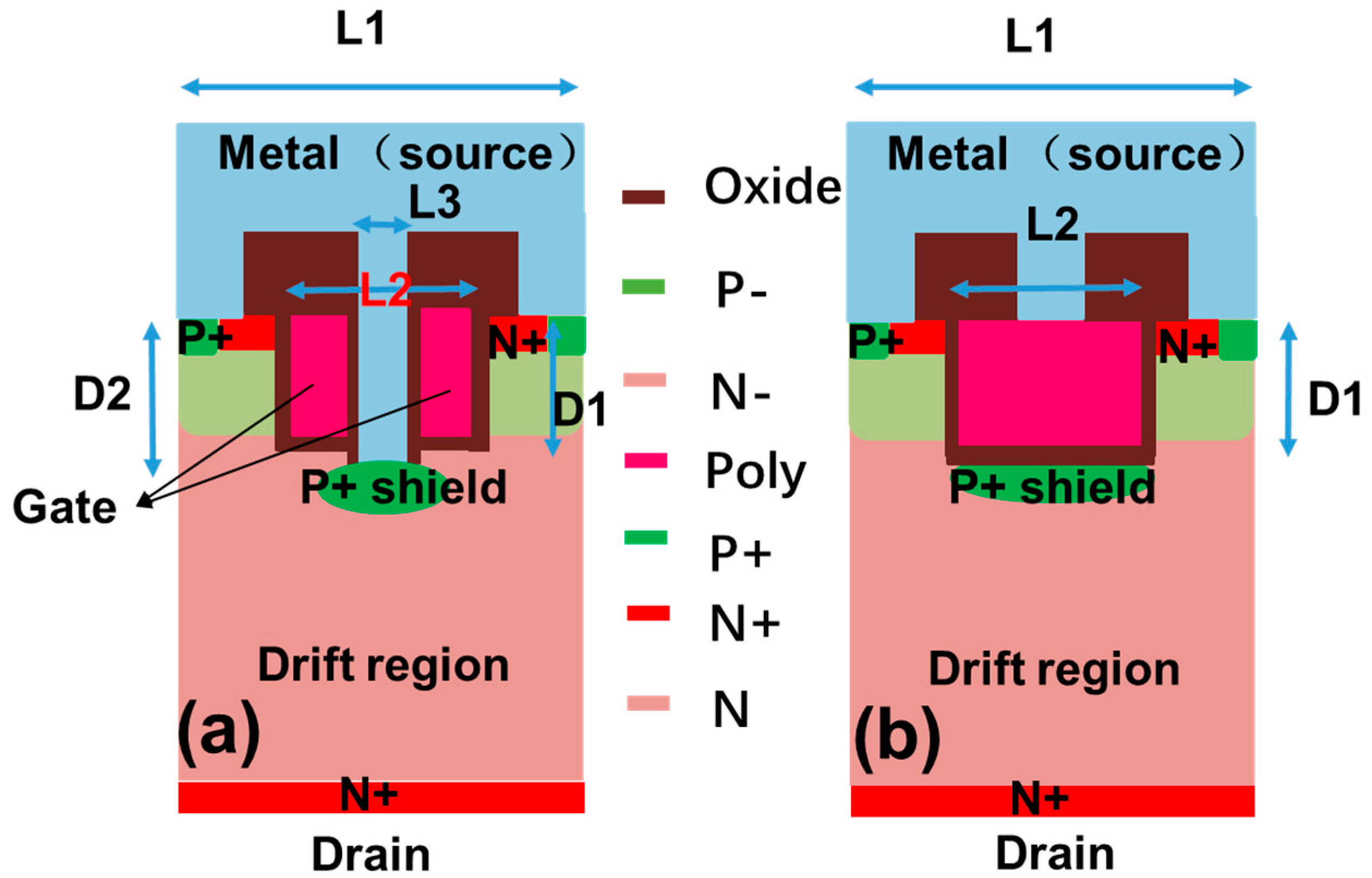

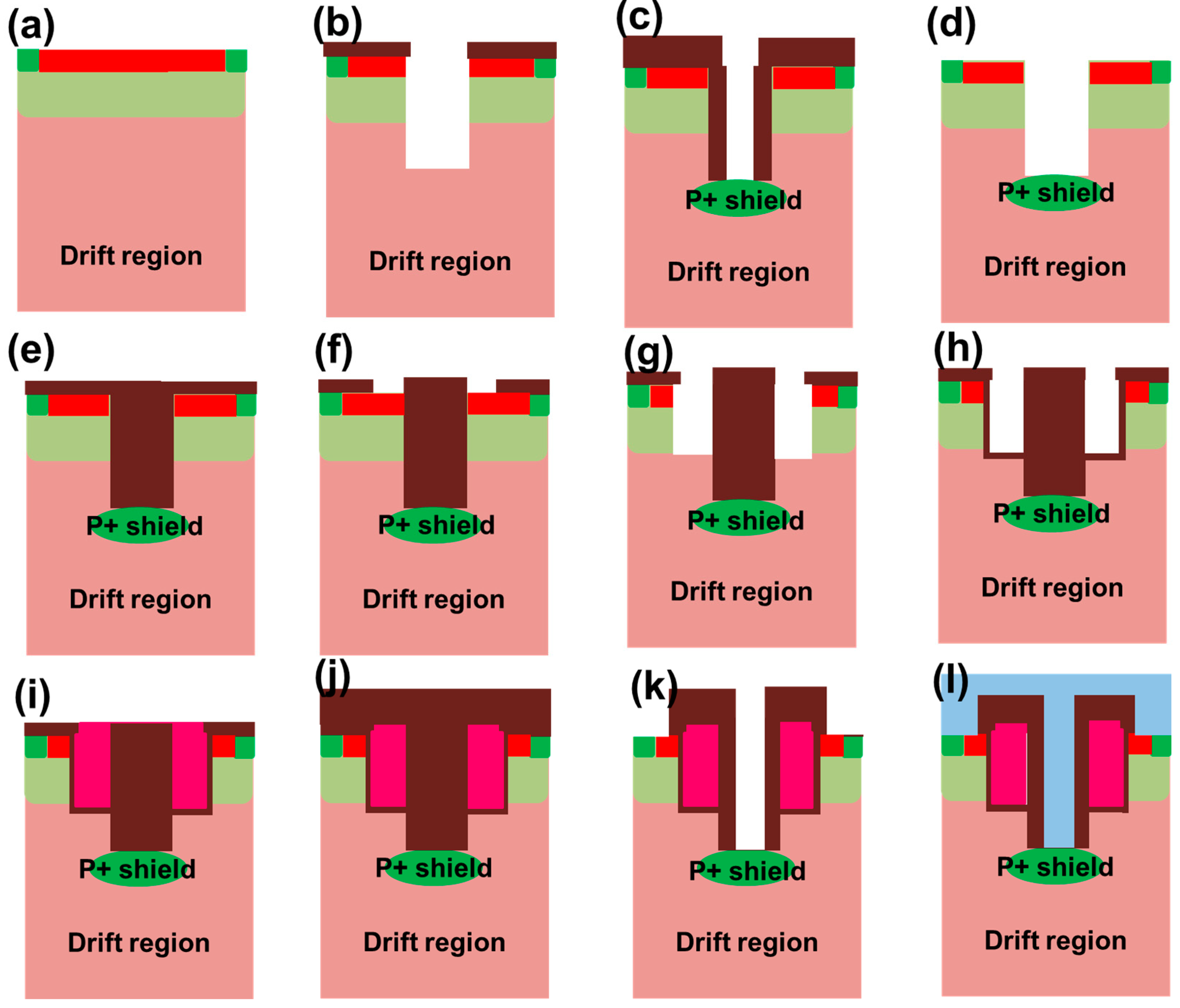

2. Structure Design and Fabrication Process

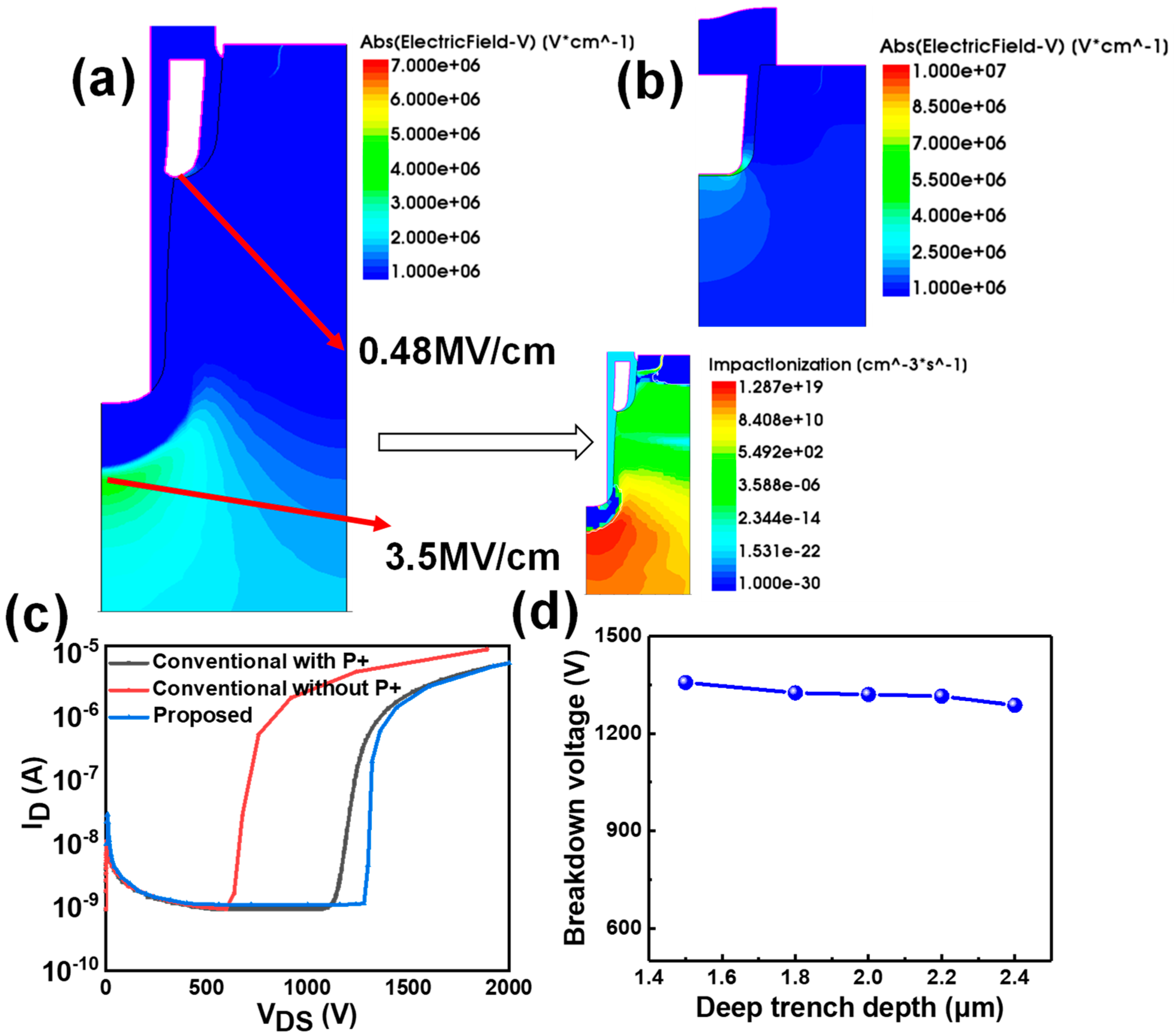

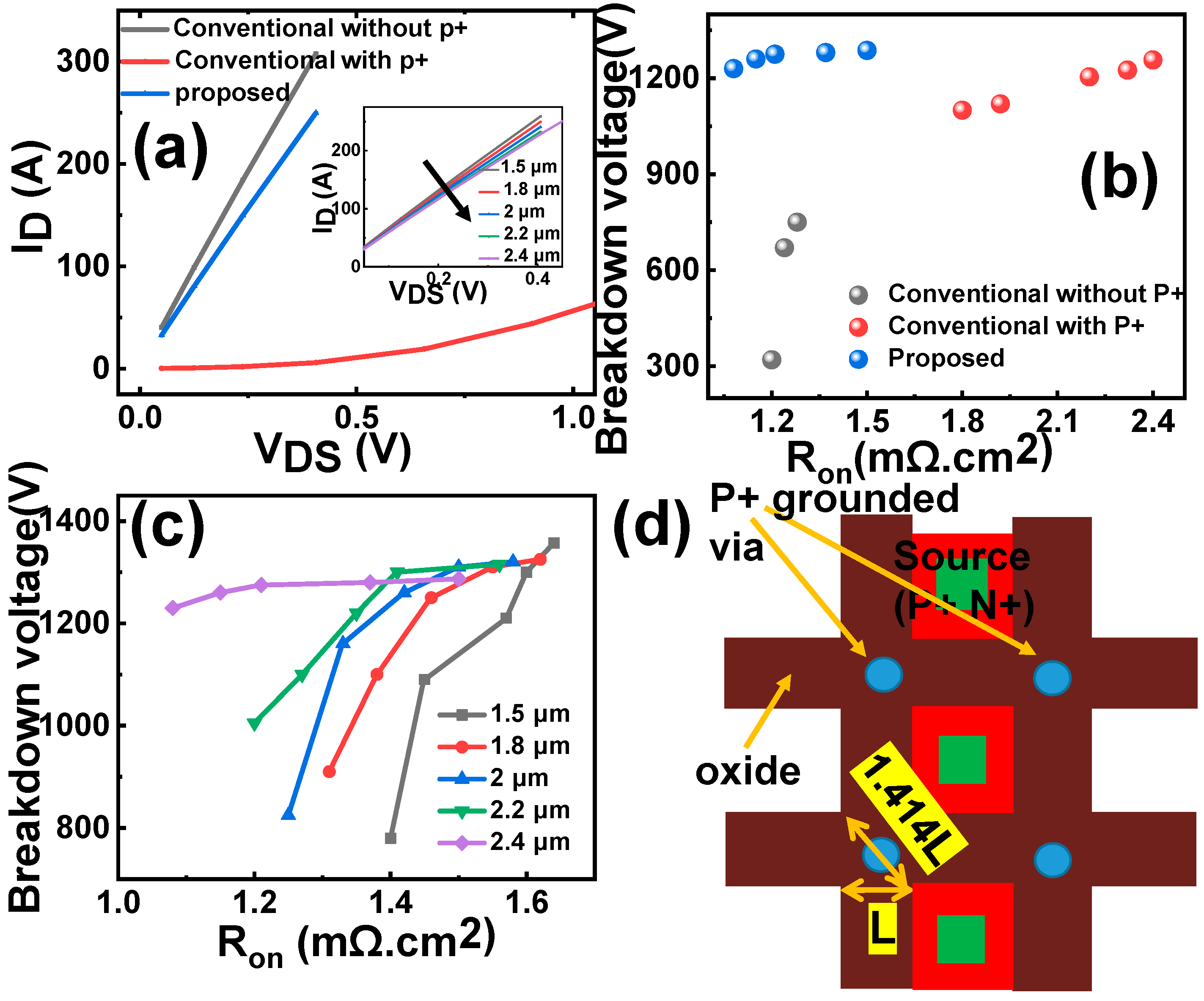

3. Simulation Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Elasser, A.; Chow, T.P. Silicon carbide benefits and advantages for power electronics circuits and systems. Proc. IEEE 2002, 90, 969–986. [Google Scholar] [CrossRef]

- Millan, J.; Godignon, P.; Perpina, X.; Perez-Tomas, A.; Rebollo, J. A survey of wide bandgap power semiconductor devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Palmour, J.W.; Cheng, L.; Pala, V.; Brunt, E.V.; Lichtenwalner, D.J.; Wang, G.-Y.; Richmond, J.; O’Loughlin, M.; Ryu, S.; Allen, S.T.; et al. Silicon carbide power MOSFETs: Breakthrough performance from 900 V up to 15 kV. In Proceedings of the 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 79–82. [Google Scholar] [CrossRef]

- Mikamura, Y.; Hiratsuka, K.; Tsuno, T.; Michikoshi, H.; Tanaka, S.; Masuda, T.; Sekiguchi, T. Novel designed SiC devices for high power and high efficiency systems. IEEE Trans. Electron Devices 2015, 62, 382–389. [Google Scholar] [CrossRef]

- Kim, D.; Yun, N.; Jang, S.Y.; Morgan, A.J.; Sung, W. An Inclusive Structural Analysis on the Design of 1.2kV 4H-SiC Planar MOSFETs. IEEE J. Electron Devices Soc. 2021, 9, 804–812. [Google Scholar] [CrossRef]

- Nakamura, T.; Nakano, Y.; Aketa, M.; Nakamura, R.; Mitani, S.; Sakairi, H.; Yokotsuji, Y. High performance SiC trench devices with ultra-low ron. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 26.5.1–26.5.3. [Google Scholar] [CrossRef]

- Yun, N.; Sung, W. Design and Fabrication Approaches of 400–600 V 4H-SiC Lateral MOSFETs for Emerging Power ICs Application. IEEE Trans. Electron Devices 2020, 67, 5005–5011. [Google Scholar] [CrossRef]

- Wei, J.; Zhang, M.; Jiang, H.; Cheng, C.-H.; Chen, K.J. Low ON-resistance SiC trench/planar MOSFET with reduced OFF-state oxide field and low gate charges. IEEE Electron Device Lett. 2016, 37, 1458–1461. [Google Scholar] [CrossRef]

- Peters, D.; Siemieniec, R.; Aichinger, T.; Basler, T.; Esteve, R.; Bergner, W.; Kueck, D. Performance and ruggedness of 1200 V SiC—Trench—MOSFET. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 239–242. [Google Scholar] [CrossRef]

- Han, K.; Baliga, B.J.; Sung, W. Split-gate 1.2-kV 4H-SiC MOSFET: Analysis and experimental validation. IEEE Electron Device Lett. 2017, 38, 1437–1440. [Google Scholar] [CrossRef]

- Harada, S.; Kobayashi, Y.; Ariyoshi, K.; Kojima, T.; Senzaki, J.; Tanaka, Y. 3.3kV-class 4H-SiC MeV-implanted UMOSFET with reduced gate oxide field. IEEE Electron Device Lett. 2016, 37, 314–316. [Google Scholar] [CrossRef]

- Song, Q.; Yang, S.; Tang, G.; Han, C.; Zhang, Y.; Tang, X.; Zhang, Y.; Zhang, Y. 4H-SiC Trench MOSFET with L-Shaped Gate. IEEE Electron Device Lett. 2016, 37, 463–466. [Google Scholar] [CrossRef]

- Wang, H.; Wang, B.; Kong, L.; Liu, L.; Chen, H.; Long, T.; Udrea, F.; Sheng, K. 4H-SiC Trench Gate Lateral MOSFET with Dual Source Trenches for Improved Performance and Reliability. IEEE Trans. Device Mater. Reliab. 2023, 23, 2–8. [Google Scholar] [CrossRef]

- Tanaka, R.; Kagawa, Y.; Fujiwara, N.; Sugawara, K.; Fukui, Y.; Miura, N.; Yamakawa, S. Impact of grounding the bottom oxide protection layer on the short-circuit ruggedness of 4H-SiC trench MOSFETs. In Proceedings of the 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 75–78. [Google Scholar] [CrossRef]

- Wang, Y.; Tian, K.; Hao, Y.; Yu, C.-H.; Liu, Y.-J. 4H–SiC Step Trench Gate Power Metal–Oxide–Semiconductor Field-Effect Transistor. IEEE Electron Device Lett. 2016, 37, 633–635. [Google Scholar] [CrossRef]

- Guo, J.; Li, P.; Jiang, J.; Zeng, W.; Wang, R.; Wu, H.; Gan, P.; Lin, Z.; Hu, S.; Tang, F. A New 4H-SiC Trench MOSFET With Improved Reverse Conduction, Breakdown, and Switching Characteristics. IEEE Trans. Electron Devices 2023, 70, 172–177. [Google Scholar] [CrossRef]

- Zhou, X.; Gong, H.; Jia, Y.; Hu, D.; Wu, Y.; Xia, T.; Pang, H.; Zhao, Y. SiC Planar MOSFETs With Built-In Reverse MOS-Channel Diode for Enhanced Performance. IEEE J. Electron Devices Soc. 2020, 8, 619–625. [Google Scholar] [CrossRef]

- Shen, Z.; Zhang, F.; Yan, G.; Wen, Z.; Zhao, W.; Wang, L.; Liu, X.; Sun, G.; Zeng, Y. High-Frequency Switching Properties and Low Oxide Electric Field and Energy Loss in a Reverse-Channel 4H-SiC UMOSFET. IEEE Trans. Electron Devices 2020, 67, 4046–4053. [Google Scholar] [CrossRef]

- Wang, H.; Wang, B.; Hu, B.; Kong, L.; Udrea, F.; Long, T. 4H-SiC Trench Gate Lateral MOSFET with Deep-Shallow Source Trench for Improved RESURF Dose Window and Reduced Oxide Field. In Proceedings of the 2022 IEEE Workshop on Wide Bandgap Power Devices and Applications in Europe (WiPDA Europe), Coventry, UK, 18–20 September 2022; pp. 1–4. [Google Scholar] [CrossRef]

- Yang, T.; Wang, Y.; Yue, R. SiC Trench MOSFET With Reduced Switching Loss and Increased Short-Circuit Capability. IEEE Trans. Electron Devices 2020, 67, 3685–3690. [Google Scholar] [CrossRef]

- Xu, H.; Yang, Y.; Tan, J.; Zhu, H.; Sun, Q.-Q.; Zhang, D.W. Carrier Stored Trench-Gate Bipolar Transistor With Stepped Split Trench-Gate Structure. IEEE Trans. Electron Devices 2022, 69, 5450–5455. [Google Scholar] [CrossRef]

- Fu, H.; Wei, J.; Wei, Z.; Liu, S.; Ni, L.; Yang, Z.; Sun, W. Quasisaturation Effect and Optimization for 4H-SiC Trench MOSFET With P+ Shielding Region. IEEE Trans. Electron Devices. 2021, 68, 4550–4556. [Google Scholar] [CrossRef]

- Wei, J.; Zhang, M.; Jiang, H.; Wang, H.; Chen, K.J. Dynamic Degradation in SiC Trench MOSFET With a Floating p-Shield Revealed With Numerical Simulations. IEEE Trans. Electron Devices 2017, 64, 2592–2598. [Google Scholar] [CrossRef]

- Peters, D.; Aichinger, T.; Basler, T.; Bergner, W.; Kueck, D.; Esteve, R. 1200V SiC Trench-MOSFET optimized for high reliability and high performance. Mater. Sci. Forum 2016, 897, 489–492. [Google Scholar] [CrossRef]

- Jiang, H.; Wei, J.; Dai, X.; Ke, M.; Deviny, I.; Mawby, P. SiC Trench MOSFET With Shielded Fin-Shaped Gate to Reduce Oxide Field and Switching Loss. IEEE Electron Device Lett. 2016, 37, 1324–1327. [Google Scholar] [CrossRef]

- Ding, R.; Dou, Z.; Qi, Y.; Mei, W.; Liu, G. Analysis on characteristic of 3.3-kV full SiC device and railway traction converter design. IET Power Electron. 2022, 15, 978–988. [Google Scholar] [CrossRef]

- Yang, X.; Li, J.W.; Ding, Y.F.; Xu, M.W.; Zhu, X.F.; Zhu, J. Observation of Transient Parity-Time Symmetry in Electronic Systems. Phys. Rev. Lett. 2022, 128, 06571. [Google Scholar] [CrossRef] [PubMed]

| Parameter | Proposed | Conventional |

|---|---|---|

| Gate oxide thickness (nm) | 50 | 50 |

| Trench gate depth D1 (μm) | 1.0 | 1.0 |

| D2 (μm) | 1.2 | |

| N-JFET doping (cm−3) | ||

| N-drift doping (cm−3) | ||

| N-drift thickness (μm) | 10 | 10 |

| Cell pitch L1 (μm) | 2.4 | 2.4 |

| Trench gate width L2 (μm) | 1.6 | 1.6 |

| L3 (μm) | 0.3 |

| Proposed | Con with +P | Con Without +P | |

|---|---|---|---|

| Ron (mΩ·cm2) | 1.08 | 1.8 | 1.28 |

| BV (V) | 1230 | 1100 | 750 |

| FoM (MW·cm2) | 1.4 | 0.672 | 0.43 |

| Qgd (nC/cm2) | 67 | 330 | 336 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cui, W.; Guo, J.; Xu, H.; Zhang, D.W. A High-Density 4H-SiC MOSFET Based on a Buried Field Limiting Ring with Low Qgd and Ron. Micromachines 2025, 16, 447. https://doi.org/10.3390/mi16040447

Cui W, Guo J, Xu H, Zhang DW. A High-Density 4H-SiC MOSFET Based on a Buried Field Limiting Ring with Low Qgd and Ron. Micromachines. 2025; 16(4):447. https://doi.org/10.3390/mi16040447

Chicago/Turabian StyleCui, Wenrong, Jianbin Guo, Hang Xu, and David Wei Zhang. 2025. "A High-Density 4H-SiC MOSFET Based on a Buried Field Limiting Ring with Low Qgd and Ron" Micromachines 16, no. 4: 447. https://doi.org/10.3390/mi16040447

APA StyleCui, W., Guo, J., Xu, H., & Zhang, D. W. (2025). A High-Density 4H-SiC MOSFET Based on a Buried Field Limiting Ring with Low Qgd and Ron. Micromachines, 16(4), 447. https://doi.org/10.3390/mi16040447