Normally Off AlGaN/GaN MIS-HEMTs with Self-Aligned p-GaN Gate and Non-Annealed Ohmic Contacts via Gate-First Fabrication

Abstract

:1. Introduction

2. Device Structure and Fabrication

3. Results and Discussion

3.1. Self-Terminated Etching of GaN over AlGaN

3.2. Non-Annealed Ohmic Contacts

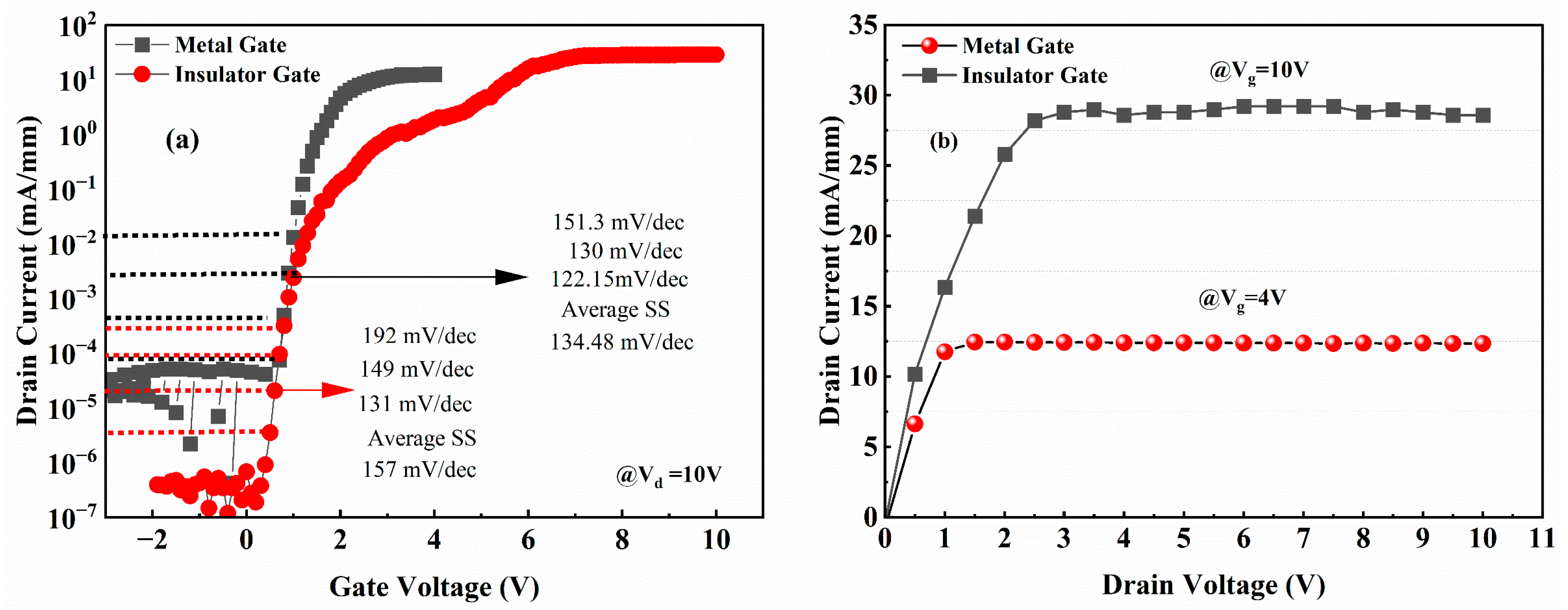

3.3. Device Performance

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Pu, T.; Wang, X.; Huang, Q.; Zhang, T.; Li, X.; Li, L.; Ao, J.-P. Normally-Off AlGaN/GaN Heterojunction Metal-Insulator-Semiconductor Field-Effect Transistors With Gate-First Process. IEEE Electron Device Lett. 2019, 40, 185–188. [Google Scholar] [CrossRef]

- Hu, Q.; Hu, B.; Gu, C.; Li, T.; Li, S.; Li, S.; Li, X.; Wu, Y. Improved Current Collapse in Recessed AlGaN/GaN MOS-HEMTs by Interface and Structure Engineering. IEEE Trans. Electron Devices 2019, 66, 4591–4596. [Google Scholar] [CrossRef]

- Xu, Z.; Wang, J.; Liu, J.; Jin, C.; Cai, Y.; Yang, Z.; Wang, M.; Yu, M.; Xie, B.; Wu, W.; et al. Demonstration of Normally-Off Recess-Gated AlGaN/GaN MOSFET Using GaN Cap Layer as Recess Mask. IEEE Electron Device Lett. 2014, 35, 1197–1199. [Google Scholar] [CrossRef]

- Chiu, H.-C.; Liu, C.-H.; Kao, H.-L.; Wang, H.-C.; Huang, C.-R.; Chiu, C.-W.; Chen, C.-T.; Chang, K.-J. Low-Mg out-diffusion of a normally off p-GaN gate high-electron-mobility transistor by using the laser activation technique. Mater. Sci. Semicond. Process. 2020, 117, 105166. [Google Scholar] [CrossRef]

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo, H.; Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate injection transistor (GIT)—A normally-off AlGaN/GaN power transistor using conductivity modulation. IEEE Trans. Electron Devices 2007, 54, 3393–3399. [Google Scholar] [CrossRef]

- Tang, Z.; Jiang, Q.; Lu, Y.; Huang, S.; Yang, S.; Tang, X.; Chen, K.J. 600-V normally off SiNx/AlGaN/GaN MIS-HEMT with large gate swing and low current collapse. IEEE Electron Device Lett. 2013, 34, 1373–1375. [Google Scholar] [CrossRef]

- Zhang, Z.; Fu, K.; Deng, X.; Zhang, X.; Fan, Y.; Sun, S.; Song, L.; Xing, Z.; Huang, W.; Yu, G.; et al. Normally Off AlGaN/GaN MIS-High-Electron Mobility Transistors Fabricated by Using Low Pressure Chemical Vapor Deposition Si3N4 Gate Dielectric and Standard Fluorine Ion Implantation. IEEE Electron Device Lett. 2015, 36, 1128–1131. [Google Scholar] [CrossRef]

- Cho, M.-H.; Moon, D.W.; Park, S.A.; Kim, Y.K.; Jeong, K.; Kang, S.K.; Ko, D.-H.; Doh, S.J.; Lee, J.H.; Lee, N.I. Interfacial characteristics of N-incorporated HfAlO high-k thin films. Appl. Phys. Lett. 2004, 84, 5243–5245. [Google Scholar] [CrossRef]

- Marron, T.; Takashima, S.; Li, Z.; Chow, T.P. Impact of annealing on ALD Al2O3 gate dielectric for GaN MOS devices. Phys. Status Solidi C 2012, 9, 907–910. [Google Scholar] [CrossRef]

- Wang, Q.; Jiang, Y.; Miyashita, T.; Motoyama, S.-i.; Li, L.; Wang, D.; Ohno, Y.; Ao, J.-P. Process dependency on threshold voltage of GaN MOSFET on AlGaN/GaN heterostructure. Solid-State Electron. 2014, 99, 59–64. [Google Scholar] [CrossRef]

- Wang, Q.; Jiang, Y.; Zhang, J.; Li, L.; Kawaharada, K.; Wang, D.; Ao, J.-P. Gate-first GaN MOSFET based on dry-etching-assisted non-annealing ohmic process. Appl. Phys. Express 2015, 8, 046501. [Google Scholar] [CrossRef]

- Lin, Y.-K.; Bergsten, J.; Leong, H.; Malmros, A.; Chen, J.-T.; Chen, D.-Y.; Kordina, O.; Zirath, H.; Chang, E.Y.; Rorsman, N.; et al. A versatile low-resistance ohmic contact process with ohmic recess and low-temperature annealing for GaN HEMTs. Semicond. Sci. Technol. 2018, 33, 095019. [Google Scholar] [CrossRef]

- Lee, F.; Su, L.-Y.; Wang, C.-H.; Wu, Y.-R.; Huang, J. Impact of gate metal on the performance of p-GaN/AlGaN/GaN high electron mobility transistors. IEEE Electron Device Lett. 2015, 36, 232–234. [Google Scholar] [CrossRef]

- Sugiyama, T.; Iida, D.; Iwaya, M.; Kamiyama, S.; Amano, H.; Akasaki, I. Threshold voltage control using SiNx in normally off AlGaN/GaN HFET with p-GaN gate. Phys. Status Solidi C 2010, 7, 1980–1982. [Google Scholar] [CrossRef]

- Lükens, G.; Hahn, H.; Kalisch, H.; Vescan, A. Self-aligned process for selectively etched p-GaN-gated AlGaN/GaN-on-Si HFETs. IEEE Trans. Electron Devices 2018, 65, 3732–3738. [Google Scholar] [CrossRef]

- Buttari, D.; Chini, A.; Palacios, T.; Coffie, R.; Shen, L.; Xing, H.; Heikman, S.; McCarthy, L.; Chakraborty, A.; Keller, S.; et al. Origin of etch delay time in Cl 2 dry etching of AlGaN/GaN structures. Appl. Phys. Lett. 2003, 83, 4779–4781. [Google Scholar] [CrossRef]

- Zhong, Y.; Zhou, Y.; Gao, H.; Dai, S.; He, J.; Feng, M.; Sun, Q.; Zhang, J.; Zhao, Y.; An, D.; et al. Self-terminated etching of GaN with a high selectivity over AlGaN under inductively coupled Cl2/N2/O2 plasma with a low-energy ion bombardment. Appl. Surf. Sci. 2017, 420, 817–824. [Google Scholar] [CrossRef]

- Han, Y.; Xue, S.; Guo, W.; Luo, Y.; Hao, Z.; Sun, C. Highly selective dry etching of GaN over AlGaN using inductively coupled Cl2/N2/O2 plasmas. Jpn. J. Appl. Phys. 2003, 42, L1139. [Google Scholar] [CrossRef]

- Schuette, M.L.; Lu, W. Highly selective zero-bias plasma etching of GaN over AlGaN. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. Process. Meas. Phenom. 2007, 25, 1870–1874. [Google Scholar] [CrossRef]

- Hilt, O.; Brunner, F.; Cho, E.; Knauer, A.; Bahat-Treidel, E.; Würfl, J. Normally-off high-voltage p-GaN gate GaN HFET with carbon-doped buffer. In Proceedings of the 2011 IEEE 23rd International Symposium on Power Semiconductor Devices and ICs, San Diego, CA, USA, 23–26 May 2011; pp. 239–242. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yin, Y.; Fan, Q.; Ni, X.; Guo, C.; Gu, X. Normally Off AlGaN/GaN MIS-HEMTs with Self-Aligned p-GaN Gate and Non-Annealed Ohmic Contacts via Gate-First Fabrication. Micromachines 2025, 16, 473. https://doi.org/10.3390/mi16040473

Yin Y, Fan Q, Ni X, Guo C, Gu X. Normally Off AlGaN/GaN MIS-HEMTs with Self-Aligned p-GaN Gate and Non-Annealed Ohmic Contacts via Gate-First Fabrication. Micromachines. 2025; 16(4):473. https://doi.org/10.3390/mi16040473

Chicago/Turabian StyleYin, Yinmiao, Qian Fan, Xianfeng Ni, Chao Guo, and Xing Gu. 2025. "Normally Off AlGaN/GaN MIS-HEMTs with Self-Aligned p-GaN Gate and Non-Annealed Ohmic Contacts via Gate-First Fabrication" Micromachines 16, no. 4: 473. https://doi.org/10.3390/mi16040473

APA StyleYin, Y., Fan, Q., Ni, X., Guo, C., & Gu, X. (2025). Normally Off AlGaN/GaN MIS-HEMTs with Self-Aligned p-GaN Gate and Non-Annealed Ohmic Contacts via Gate-First Fabrication. Micromachines, 16(4), 473. https://doi.org/10.3390/mi16040473