A Flexible FPGA-Based Channel Emulator for Non-Stationary MIMO Fading Channels

Abstract

:1. Introduction

- Based on the improved GBSM with the accurate channel fading phase and Doppler frequency in [27], this paper proposes a discrete non-stationary MIMO channel model, which is suitable to implement on the FPGA-based hardware platforms. Meanwhile, a flexible hardware architecture tailored for the proposed model is developed, in which the channel size and parameters can easily be reconfigured.

- An improved emulation method of channel fading, namely, sum-of-frequency-modulated-signals (SoFM), is employed to guarantee the accurate channel fading and phase. In addition, the architectures of other key modules, i.e., the delay module, fading generation module, and interpolator module, are developed and implemented on a single Xilinx XC7VX690T FPGA.

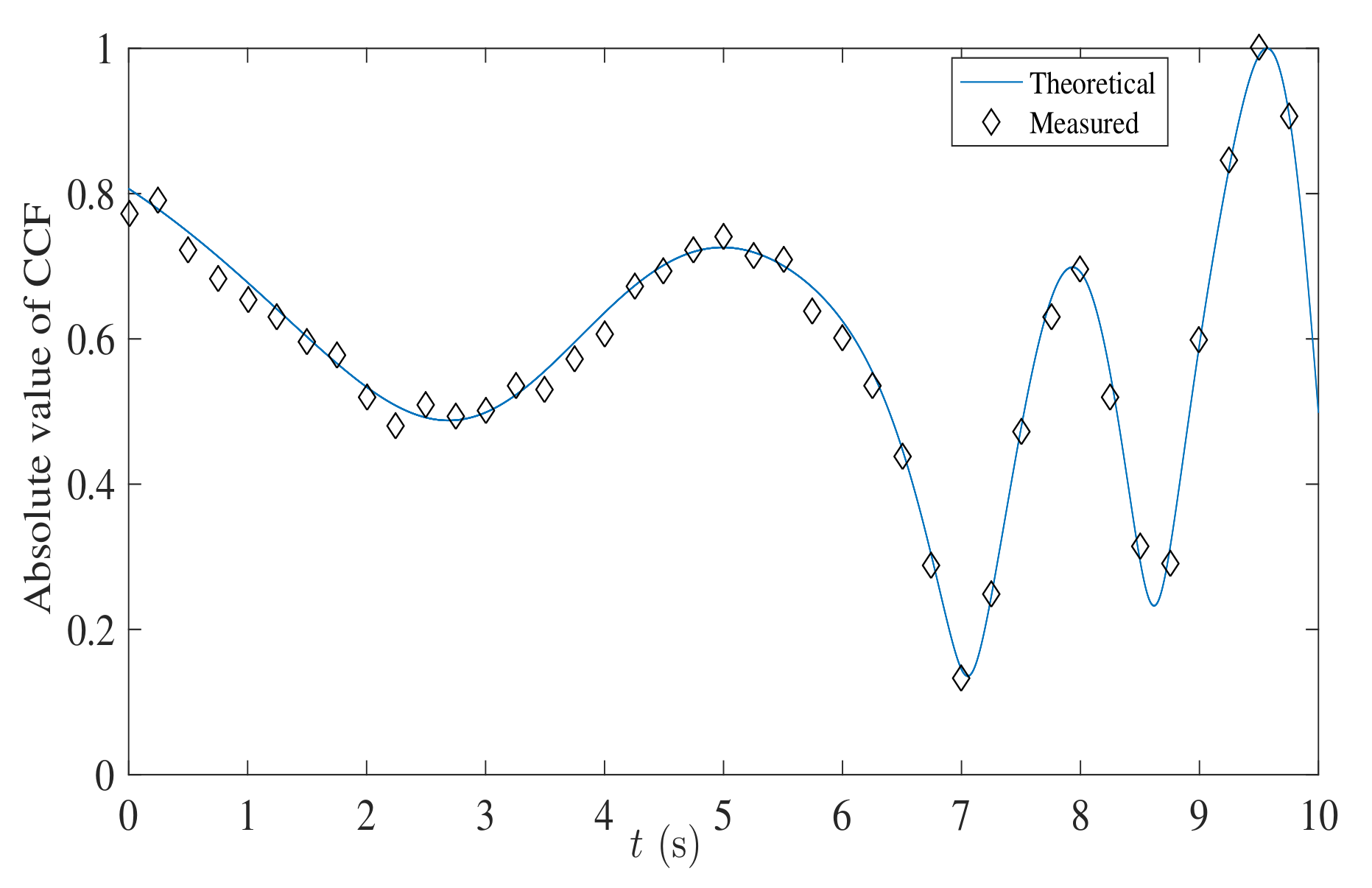

- For the developed channel emulator, the output statistical properties, i.e., the probability density function (PDF), cross-correlation function (CCF), and DPSD are tested and verified by the theoretical results. The power delay profile (PDP) is also validated by the measurement data.

2. Discrete Non-Stationary MIMO Channel Model

3. Flexible Hardware Architecture and Implementation

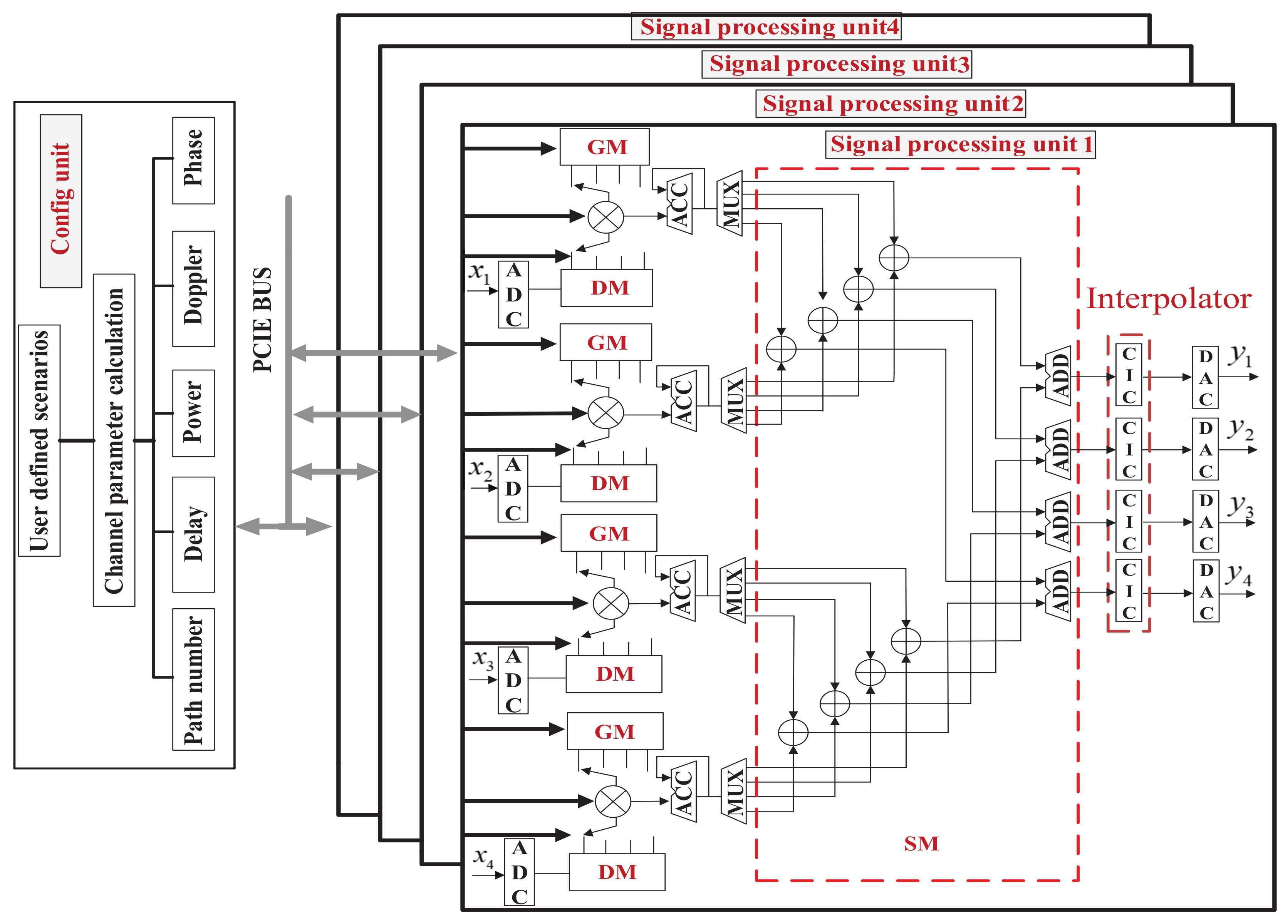

3.1. System Architecture

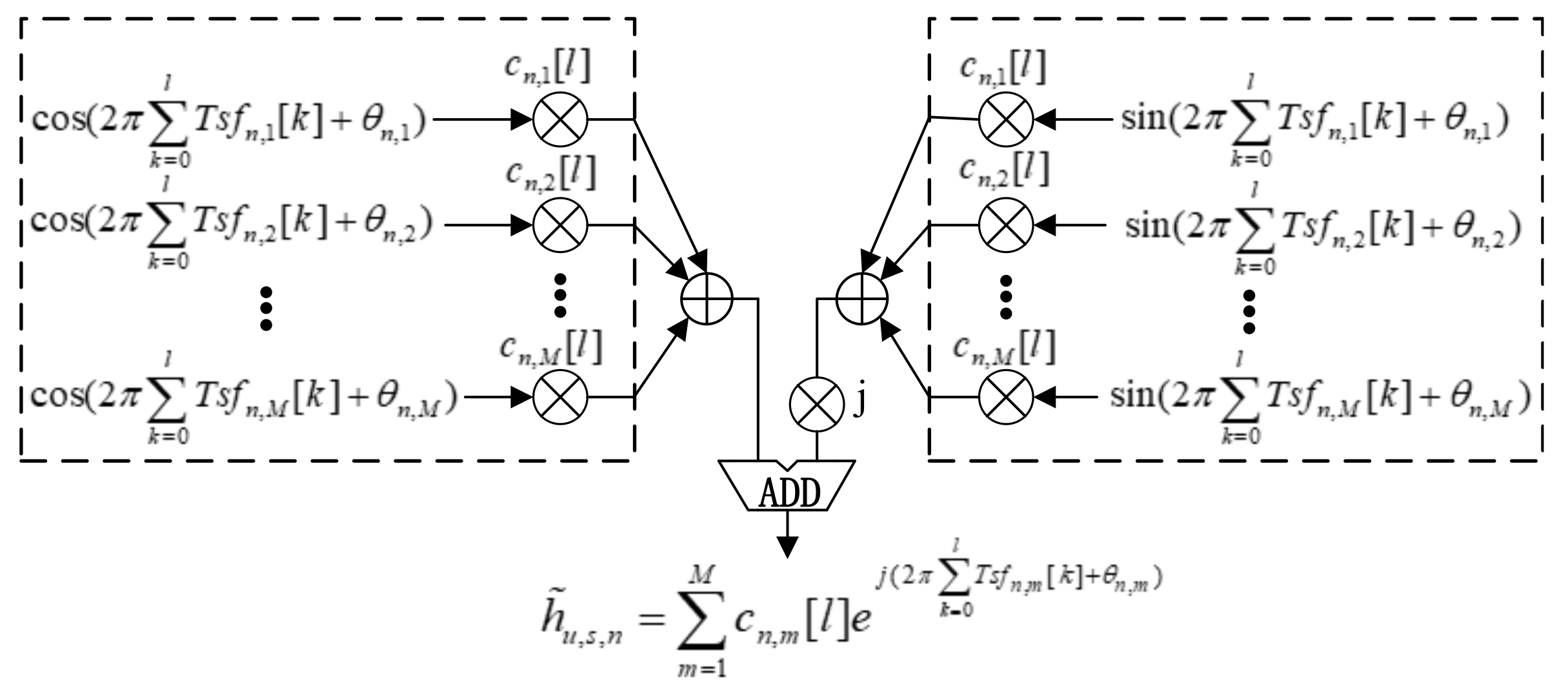

3.2. Channel Fading Generation

3.3. FPGA-Based Implementation

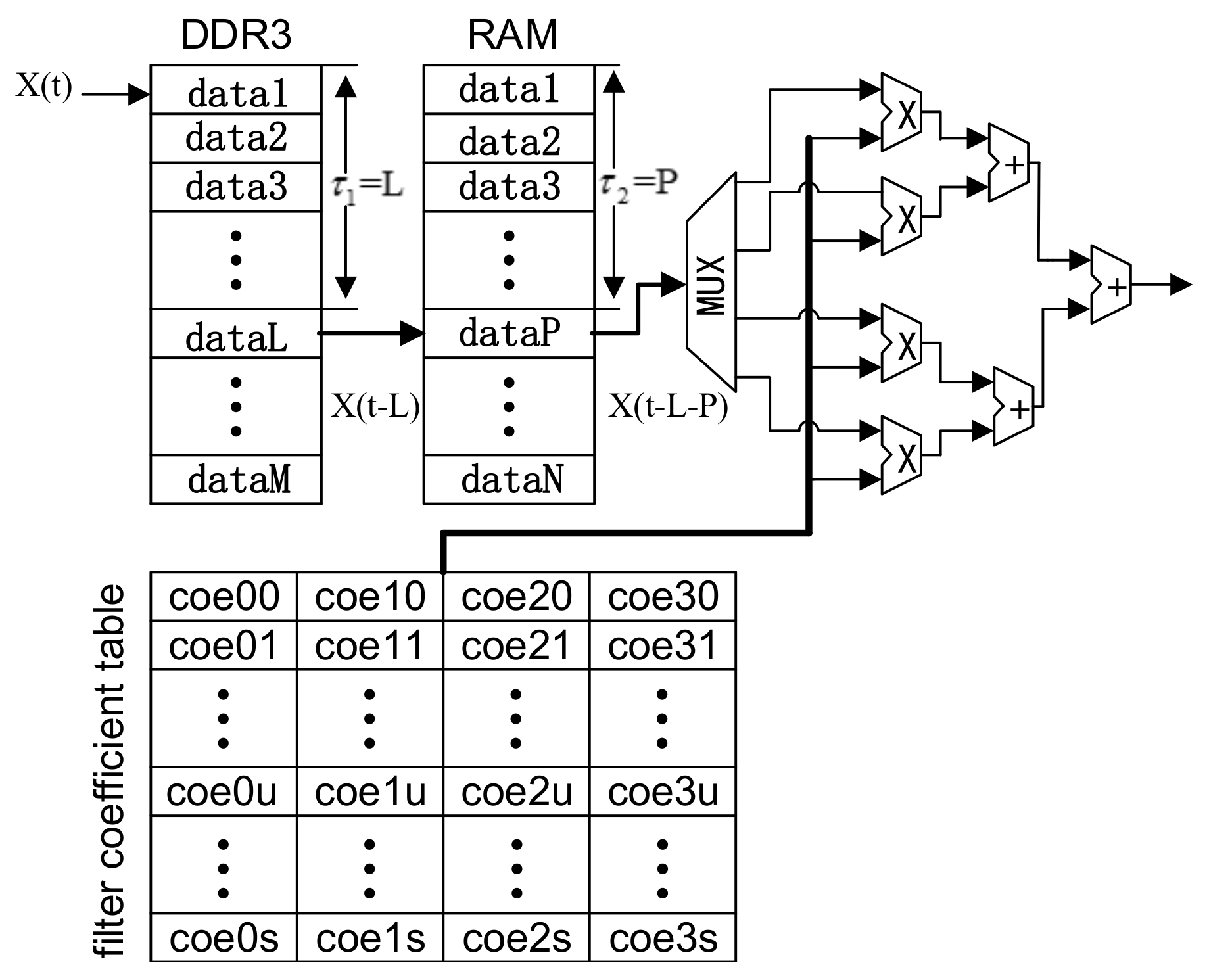

3.3.1. Delay Module

3.3.2. Fading Generation Module

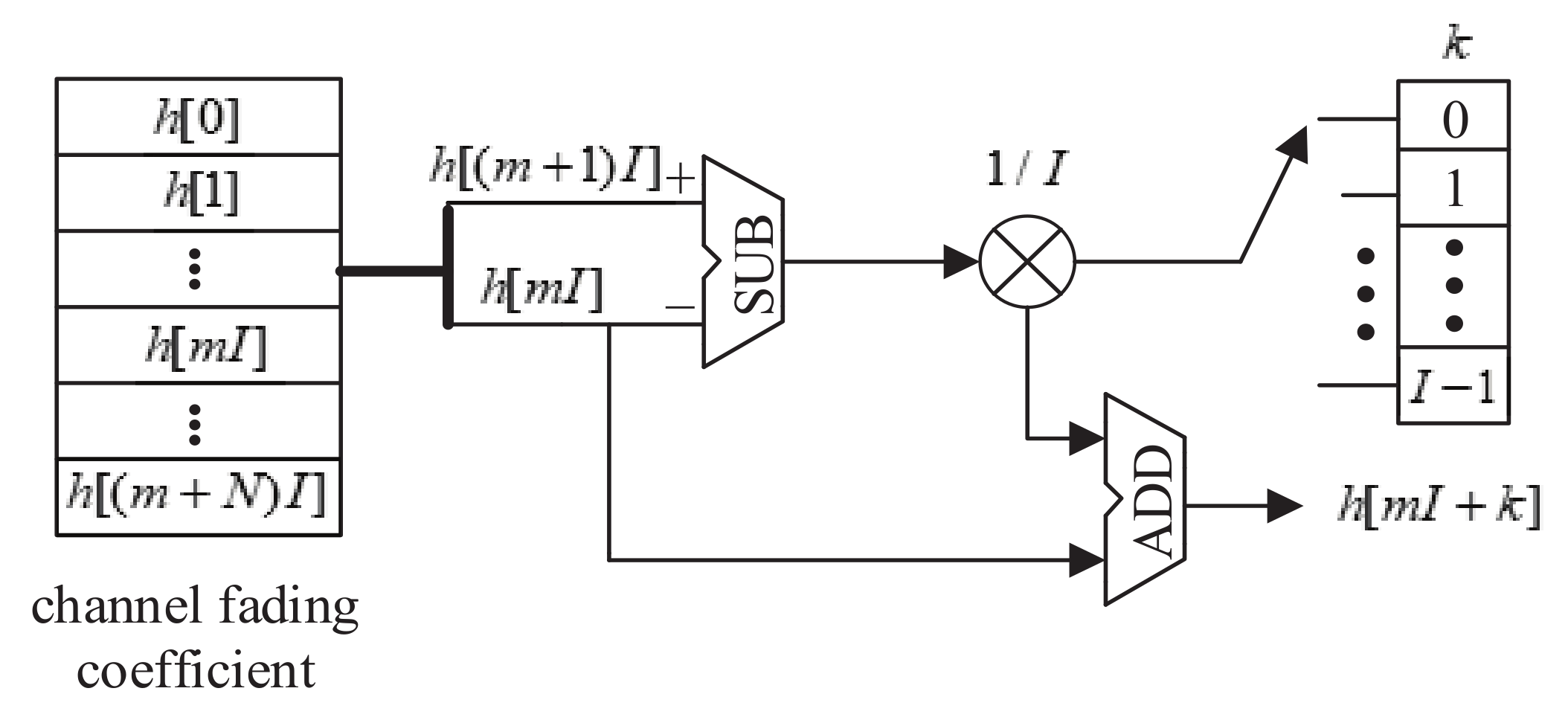

3.3.3. Interpolator Module

4. Resource Consumption and Measurements

4.1. Resource Consumption

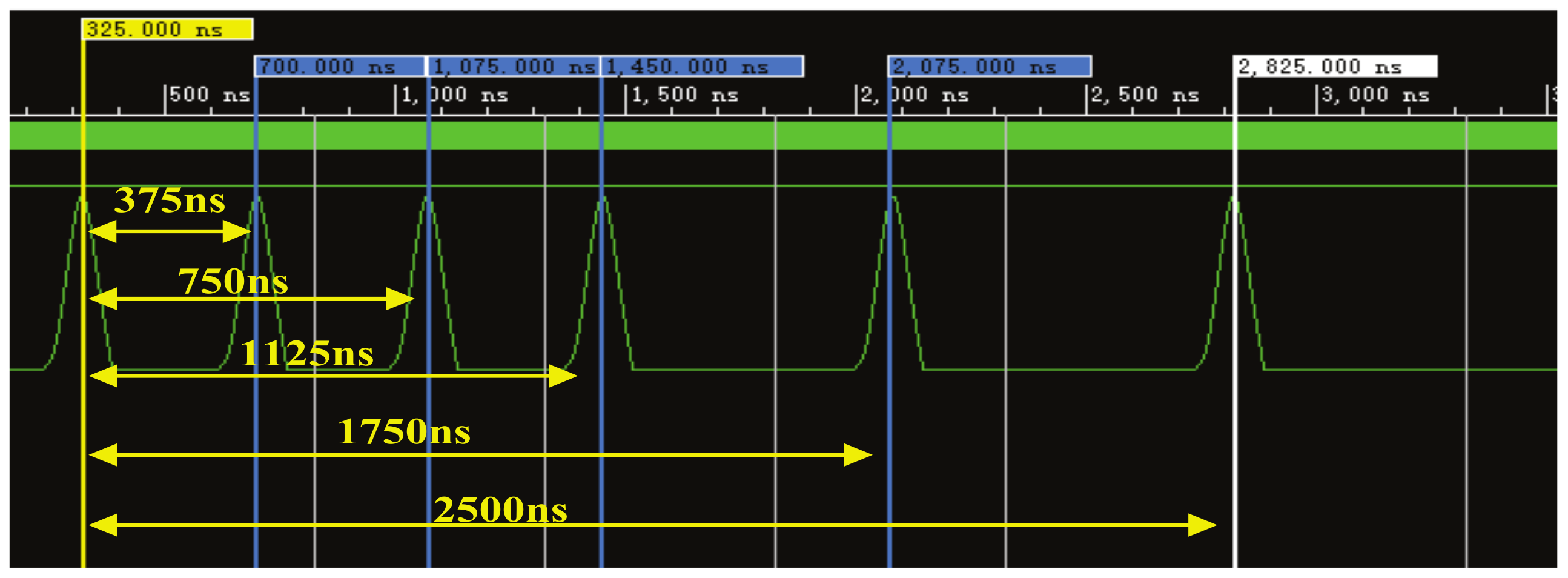

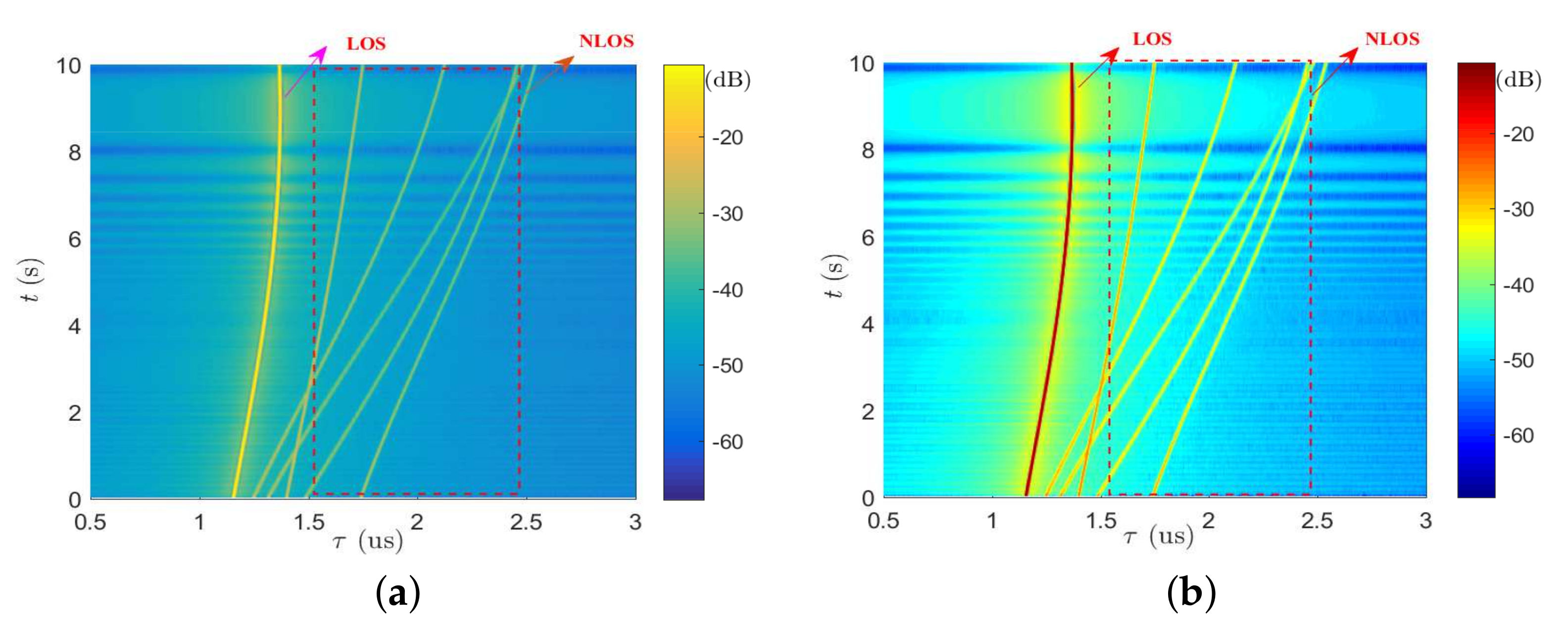

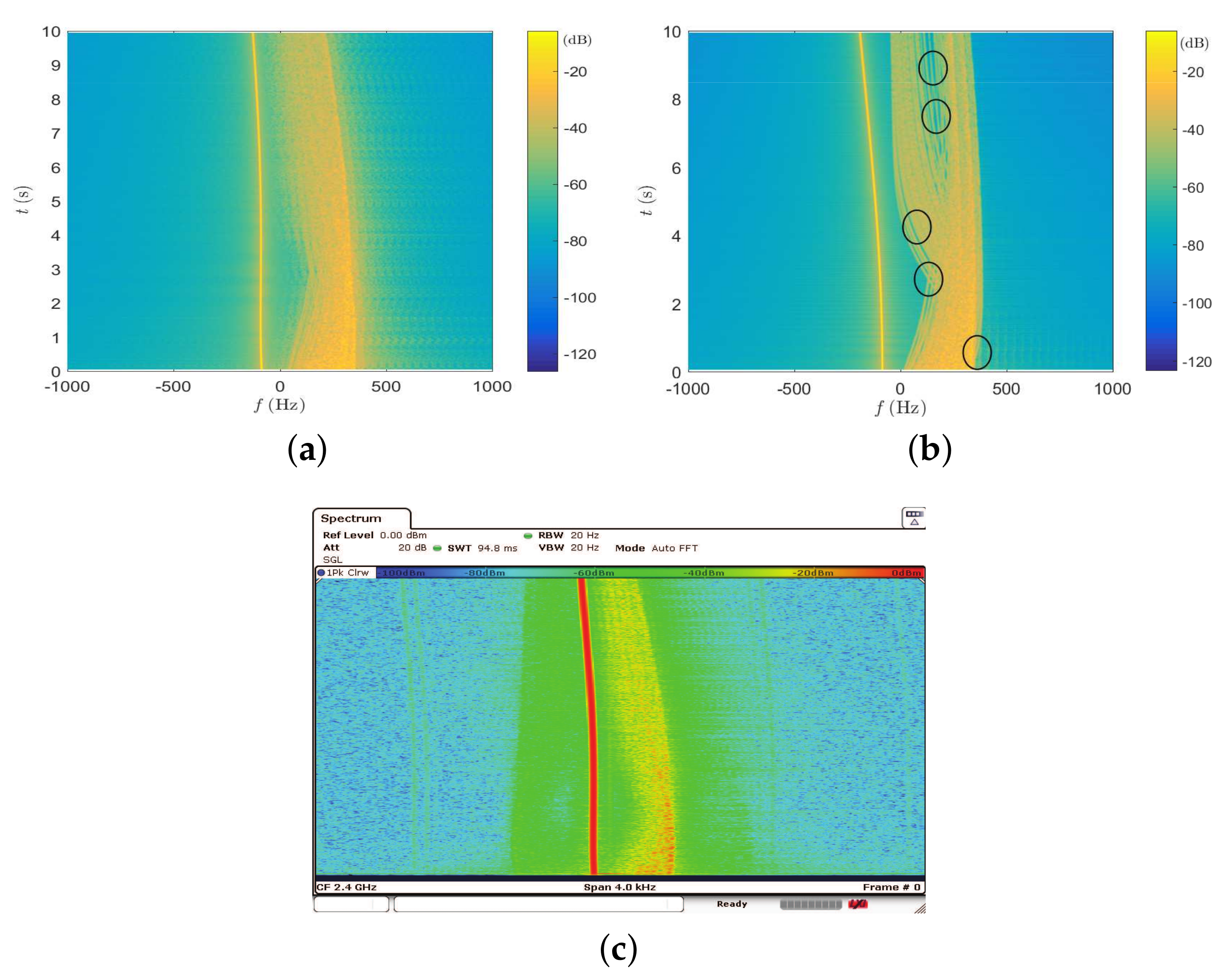

4.2. Measured Results and Analysis

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Agiwal, M.; Roy, A.; Saxena, N. Next generation 5G wireless networks: A comprehensive survey. Commun. Surv. 2016, 18, 1617–1655. [Google Scholar] [CrossRef]

- Wang, C.X.; Bian, J.; Sun, J. A survey of 5G channel measurements and models. Commun. Surv. 2018, 20, 3142–3168. [Google Scholar] [CrossRef]

- Zhang, J.; Shafi, M.; Molisch, A.F.; Tufvesson, F.; Wu, S.; Kitao, K. Channel models and measurements for 5G. IEEE Commun. Mag. 2018, 56, 12–13. [Google Scholar] [CrossRef]

- Kamga, G.; Xia, M.; Aissa, S. Channel modeling and capacity analysis of large MIMO in real propagation environments. In Proceedings of the IEEE International Conference on Communications, London, UK, 8–12 June 2015; pp. 1447–1452. [Google Scholar]

- Li, J.; Jiang, D.; Zhang, X. DOA estimation based on combined unitary ESPRIT for coprime MIMO radar. IEEE Commun. Lett. 2017, 21, 96–99. [Google Scholar] [CrossRef]

- Fan, W.; Carton, I.; Kyosti, P.; Karstensen, A.; Jamsa, T.; Gustafsson, M.; Pedersen, G. A step toward 5G in 2020: Low-cost OTA performance evaluation of massive MIMO base stations. IEEE Antennas Propag. Mag. 2017, 59, 38–47. [Google Scholar] [CrossRef]

- N5106A PXB Channel Emulator. Available online: https://www.keysight.com (accessed on 13 June 2020).

- Azimuth ACE 400WB Channel Emulator. Available online: https://cdn.thomasnet.com (accessed on 13 June 2020).

- Ghiaasi, G.; Ashury, M.; Vlastaras, D.; Hofer, M.; Xu, Z.; Zemen, T. Real-time vehicular channel emulator for future conformance tests of wireless ITS modems. In Proceedings of the 2016 10th European Conference on Antennas and Propagation (EuCAP), Davos, Switzerland, 10–15 April 2016; pp. 1–5. [Google Scholar]

- Fard, S.F.; Alimohammad, A.; Cockburn, B.F. Single-field programmable gate array simulator for geometric multiple-input multiple-output fading channel models. IET Commun. 2011, 5, 1246–1254. [Google Scholar] [CrossRef]

- Huang, P.; Du, Y.; Li, Y. Stability analysis and hardware resource optimization in channel emulator design. IEEE Trans. Circ. Syst. 2016, 63, 1089–1100. [Google Scholar] [CrossRef]

- Alimohammad, A.; Fard, S.F. A compact architecture for simulation of spatial-temporally correlated MIMO fading channels. IEEE Trans. Circ. Syst. 2014, 61, 1089–1100. [Google Scholar]

- Dahech, W.; Patzold, M.; Gutierrez, C.A.; Youssef, N. A nonstationary mobile-to-mobile channel model allowing for velocity and trajectory variations of the mobile stations. IEEE Trans. Wirel. Commun. 2017, 16, 1987–2000. [Google Scholar] [CrossRef]

- Liang, X.; Zhao, X.; Li, Y.; Wang, Q. A non-stationary geometry-based street scattering model for vehicle-to-vehicle wideband MIMO channels. IEEE Wirel. Commun. 2016, 90, 325–338. [Google Scholar] [CrossRef]

- Zhu, Q.; Li, W.; Yang, Y.; Xu, D. A general 3D nonstationary vehicle-to-vehicle channel model allowing 3D arbitrary trajectory and 3D-shaped antenna array. Int. J. Antennas Propag. 2019, 2019, 8708762. [Google Scholar] [CrossRef] [Green Version]

- Ghazal, A.; Wang, C.X.; Ai, B.; Yuan, D.F.; Hass, H. A nonstationary wideband MIMO channel model for high-mobility intelligent transportation systems. IEEE Trans. Intell. Transp. Syst. 2015, 16, 885–897. [Google Scholar] [CrossRef] [Green Version]

- Ghazal, A.; Yuan, Y.; Wang, C.X. A non-stationary IMT-advanced MIMO channel model for high-mobility wireless communication systems. IEEE Trans. Wirel. Commun. 2016, 16, 2057–2068. [Google Scholar] [CrossRef] [Green Version]

- Zhu, Q.; Wang, Y.; Jiang, K.; Chen, X.; Zhong, W.; Ahmed, N. 3D non-stationary geometry-based MIMO channel model for UAV-Ground communication systems. IET Microw. Antennas Propag. 2019, 13, 1104–1112. [Google Scholar] [CrossRef]

- Ren, F.; Zheng, Y.R. A novel emulator for discrete-time MIMO triply selective fading channels. IEEE Trans. Circ. Syst. 2010, 57, 2542–2551. [Google Scholar] [CrossRef]

- Habib, B.; Zaharia, G.; Zein, G.E. Hardware Simulator for MIMO Propagation Channels: Time Domain Versus Frequency Domain Architectures. Sci. J. Circ. Syst. Signal Proc. 2013, 2, 37–55. [Google Scholar] [CrossRef]

- Habib, B.; Zaharia, G.; Zein, G.E. MIMO hardware simulator design for outdoor time-varying heterogeneous channels. In Proceedings of the International Symposium on Signals, Circuits and Systems, Lasi, Romania, 11–12 July 2013; pp. 1–4. [Google Scholar]

- Zhang, N.; Yang, G.; Zhai, J. Design and implementation of flexible 4M × 4N MIMO channel emulator. In Proceedings of the IEEE Antennas and Propagation Society International Symposium, Memphis, TN, USA, 6–11 July 2014; pp. 713–714. [Google Scholar]

- Tien, T.V.; Tien, T.M.; Khai, L.D. Hardware Implementation of a MIMO Channel Emulator for high speed WLAN 802.11 ac. In Proceedings of the 2018 5th NAFOSTED Conference on Information and Computer Science, Ho Chi Minh City, Vietnam, 23–24 November 2018; pp. 183–188. [Google Scholar]

- Habib, B.; Baz, B. Digital architecture of 8 × 8 MIMO Hardware channel simulator for time-varying heterogeneous systems with LTE-A, 802.11 ac and VLC signals. In Proceedings of the 2016 3rd International Conference on Advances in Computational Tools for Engineering Applications (ACTEA), Beirut, Lebanon, 13–15 July 2016; pp. 195–200. [Google Scholar]

- Hofer, M.; Xu, Z.; Vlastaras, D.; Schrenk, B.; Tufvesson, F.; Zemen, T. Real-time geometry-based wireless channel emulation. IEEE Trans. Veh. Technol. 2019, 68, 1631–1645. [Google Scholar] [CrossRef]

- Ruiz, A.E.; Gutierrez, C.A.; Castillo, J.V.; Cortez, J. SDR-Based channel emulator for vehicular communications. In Proceedings of the 2019 IEEE Colombian Conference on Communication and Computing (COLCOM), Barranquilla, Colombia, 5–7 June 2019; pp. 1–6. [Google Scholar]

- Zhu, Q.; Li, H.; Fu, Y.; Wang, C.X.; Tan, Y.; Chen, X. A novel 3D non-stationary wireless MIMO channel simulator and hardware emulator. IEEE Trans. Commun. 2018, 66, 3865–3878. [Google Scholar] [CrossRef]

- Zhu, Q.; Liu, X.; Yin, X.; Chen, X.; Xue, C. A novel simulator of nonstationary random MIMO channels in Rayleigh fading scenarios. Int. J. Antennas Propag. 2016, 2016, 3492591. [Google Scholar] [CrossRef] [Green Version]

- Nguyen, T.T.; Lanante, L.; Nagao, Y.; Kurosaki, M.; Ochi, H. MU-MIMO channel emulator with automatic channel sounding feedback for IEEE 802.11 ac. In Proceedings of the Wireless Communications and Networking Conference, Doha, Qatar, 3–6 April 2016; pp. 1–6. [Google Scholar]

- Hua, J.; Yang, J.; Lu, W.; Meng, L.; Yu, X. Design of universal wireless channel generator accounting for the 3-D scatter distribution and hardware output. IEEE Trans. Instrum. Meas. 2014, 64, 2–13. [Google Scholar] [CrossRef]

- Qiu, Z.; Chu, X.; Calvo-Ramirezand, C.; Briso-Rodriguez, C.; Yin, X. Low Altitude UAV Air-to-Ground Channel Measurement and Modeling in Semiurban Environments. Wirel. Commun. Mob. Comput. 2017, 2017, 1587412. [Google Scholar] [CrossRef] [Green Version]

- Jiang, K.; Chen, X.; Zhu, Q.; Chen, L.; Xu, D.; Chen, B. A Novel Simulation Model for Nonstationary Rice Fading Channels. Wirel. Commun. Mob. Comput. 2018, 2018, 8086073. [Google Scholar] [CrossRef] [Green Version]

- Zhu, Q.; Yang, Y.; Wang, C.X.; Tan, Y.; Sun, J.; Chen, X.; Zhong, W. Spatial correlations of a 3-D nonstationary MIMO channel model with 3-D antenna arrays and 3-D arbitrary trajectories. IEEE Wirel. Commun. Lett. 2019, 8, 512–515. [Google Scholar] [CrossRef]

| The Method in [22] | The Proposed Method | |

|---|---|---|

| System sample rate | 100 M | 256 M |

| Slice LUTs | 152,337 | 25,800 |

| Block RAMs | 191 | 116 |

| DSPs | 768 | 160 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhu, Q.; Huang, W.; Mao, K.; Zhong, W.; Hua, B.; Chen, X.; Zhao, Z. A Flexible FPGA-Based Channel Emulator for Non-Stationary MIMO Fading Channels. Appl. Sci. 2020, 10, 4161. https://doi.org/10.3390/app10124161

Zhu Q, Huang W, Mao K, Zhong W, Hua B, Chen X, Zhao Z. A Flexible FPGA-Based Channel Emulator for Non-Stationary MIMO Fading Channels. Applied Sciences. 2020; 10(12):4161. https://doi.org/10.3390/app10124161

Chicago/Turabian StyleZhu, Qiuming, Wei Huang, Kai Mao, Weizhi Zhong, Boyu Hua, Xiaomin Chen, and Zikun Zhao. 2020. "A Flexible FPGA-Based Channel Emulator for Non-Stationary MIMO Fading Channels" Applied Sciences 10, no. 12: 4161. https://doi.org/10.3390/app10124161