DC Converter with Wide Soft Switching Operation, Wide Input Voltage and Low Current Ripple

Abstract

:1. Introduction

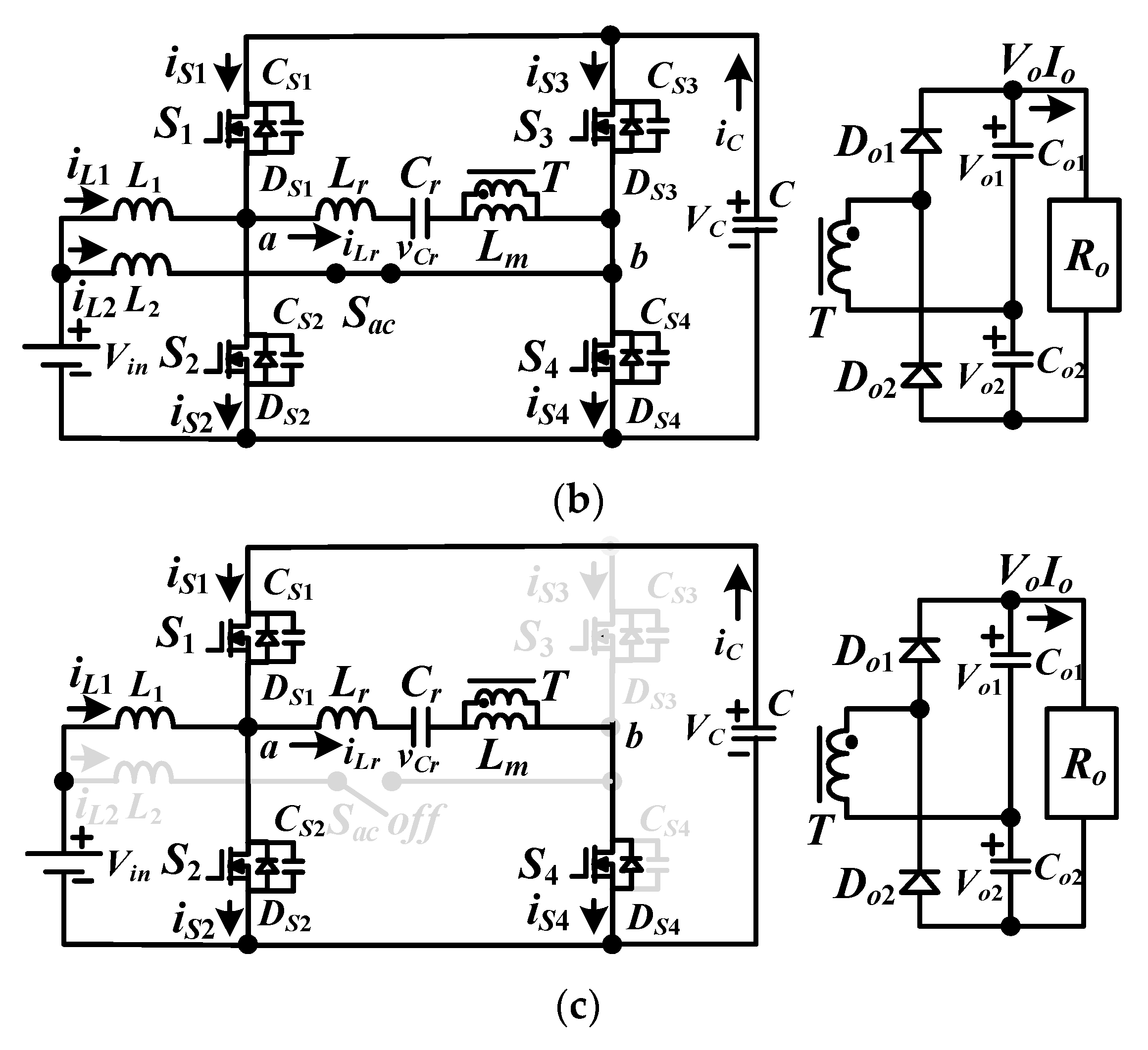

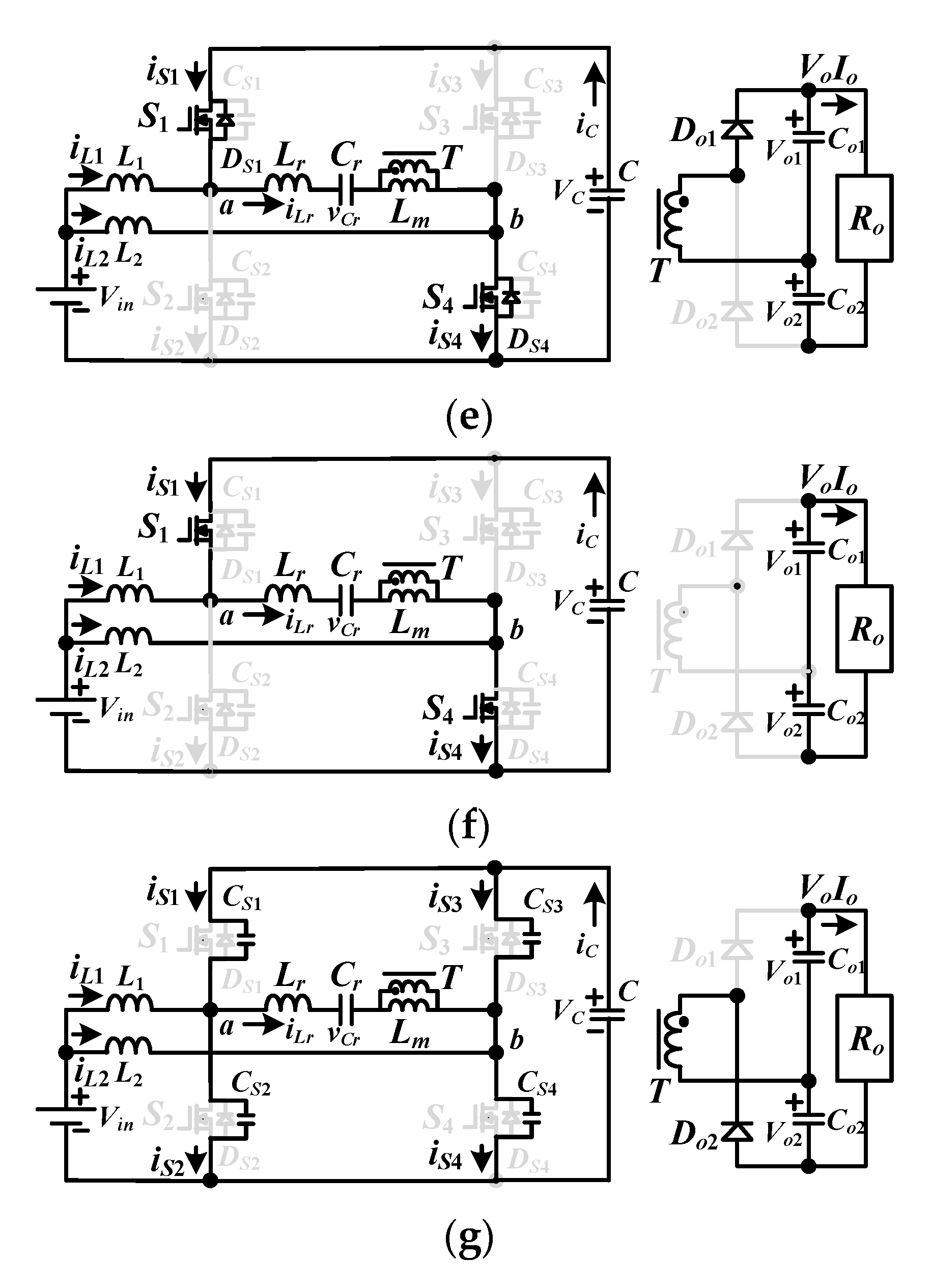

2. Circuit Diagram

3. Principles of Operation

- Step 1 [t0≤t< t1]: At t0, vCS2 and vCS3 are decreased to zero voltage and DS2 and DS3 become on due to iS2(t0) < 0 and iS3(t0) < 0. Active semiconductors S2 and S3 are turned on after time t0 to realize zero-voltage switching. The boost inductor voltages VL1 equals Vin and VL2 = Vin − VC ≈ −Vin. iL1 is increasing and iL2 is decreasing. Voltage VC connects to Lr, Cr and Lm. Due to Do2 is conducting, it can obtain vLm = −nVo2 = −nVo/2. Components Cr and Lr are resonant with the resonant frequency .

- Step2 [t1≤t< t2]: Because of fr > fsw, iLm equals iLr at time t1. Therefore, Do2 is reverse biased. Lm, Cr, Lm and Lr are resonant in step 2 with the other resonant frequency < fr. iL1 is still increasing and iL2 is decreasing in step 2.

- Step 3 [t2≤t< t3]: At half of switching cycle (t2 = Tsw/2), switches S2 and S3 turn off. Since iL1(t2) − iLr1(t2) is greater than zero current and iLr1(t2) + iL2(t2) is less than zero current, capacitors CS1 and CS4 will be discharged at time t2. After time t2, iLr > iLm, Do1 is forward biased and vLm = nVo1 = nVo/2.

- Step 4 [t3≤t< t4]: At t3, the voltages vCS1 and vCS4 are decreased to zero voltage. Owing to the fact that iS1(t3) and iS4(t3) are both less than zero, DS1 and DS4 become on. After t3, S1 and S4 turn on with zero-voltage switching. In this step, iLr > iLm so that Do1 conducts and vLm = nVo/2. Lr and Cr are resonant with resonant frequency fr in this step. Inductor voltages vL1 = Vin − VC ≈ −Vin and vL2 = Vin. Thus, iL1 and iL2 are decreasing and increasing.

- Step5 [t4≤t< t5]: Owing to fsw < fr, iLm equals iLr at time t4 so that Do1 is reverse biased. iL1 and iL2 decrease and increase, respectively.

- Step6 [t5≤t<Tsw+t0]:S1 and S4 turn off at t5. Since iLr(t5) − iL1(t5) > 0 and iLr(t5) + iL2(t5) > 0, the capacitors CS2 and CS3 discharge at time t > t5. Since iLr < iLm, Do2 is forward biased and vLm = −nVo/2. Step 6 ends at t = Tsw + t0 and vCS2 = vCS3 = 0.

- Step 1 [t0≤t< t1]:vCS2 = 0 at t0. Owing to iLr(t0) – iL1(t0) < 0, DS2 is forward bias and S2 turns on after t > t0 to accomplish zero-voltage switching. iL1 increases and Cr and Lr are resonant and vLm = −nVo/2.

- Step2 [t1≤t< t2]:Do2 is reverse biased owing to iLr = iLm at time t1. Thus, Lm, Cr and Lr are resonant and iL1 increases due to VL1 = Vin.

- Step 3 [t2≤ t< t3]: Active device S2 is turned off at t = t2. Due to iL1(t2) – iLr(t2) > 0 and iLr(t2) > iLm(t2), CS1 will be discharged and Do1 becomes on.

- Step 4 [t3≤t< t4]:vCS1 = 0 at time t3. Owing to iL1(t3) > iLr(t3), the body diode DS1 becomes on and S1 can be turned on after t > t3 to achieve soft switching turn-on. iL1 is decreasing in step 4 and Do1 conducts such that vLm = nVo/2.

- Step5 [t4≤t< t5]: At time t4, iLm equals iLr and Do1 becomes off. Lm, Cr and Lr are resonant and iL1 decreases due to VL1 = Vin – VC< 0.

- Step6 [t5≤t<Tsw + t0]: Switch S1 turns off at time t5. Since iLr is less than iLm and iL1 is less than iLr(t5), diode Do2 conducts and CS2 is discharged. When the voltage of CS2 is decreased to zero voltage at time Tsw + t0.

4. Circuit Analysis

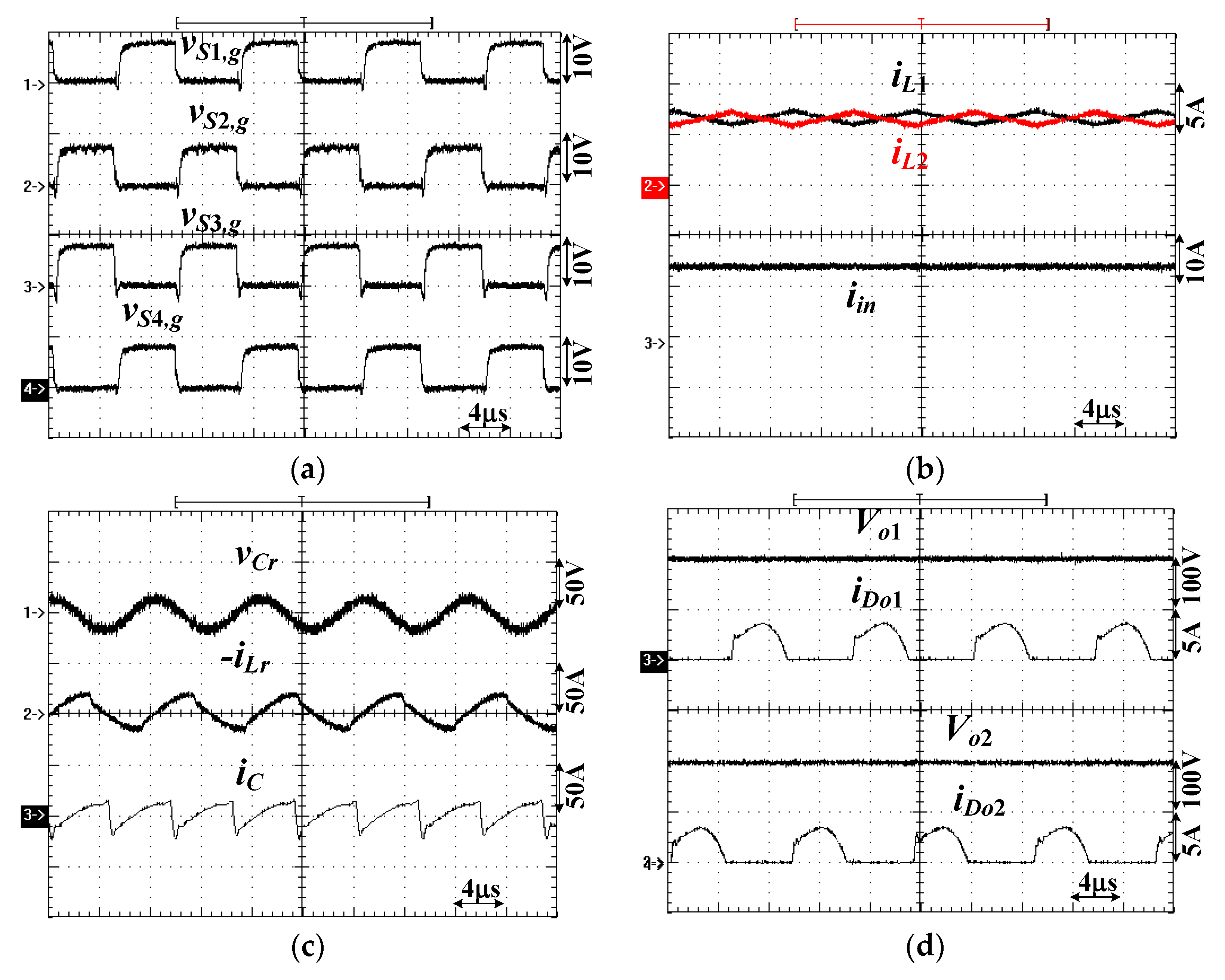

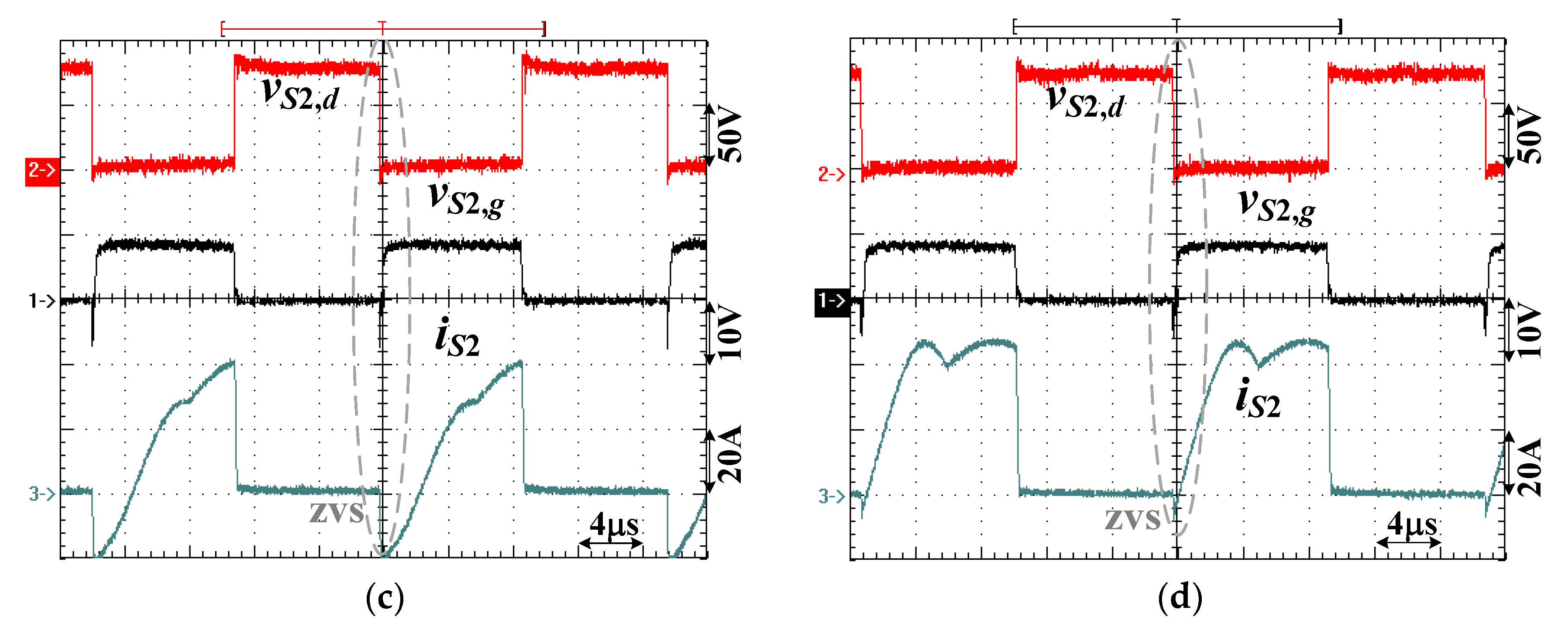

5. Design Steps and Experimental Verifications

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Sangwongwanich, A.; Yang, Y.; Blaabjerg, F. High-performance constant power generation in grid-connected PV systems. IEEE Trans. Power Electron. 2016, 31, 1822–1825. [Google Scholar] [CrossRef] [Green Version]

- Prasanna, U.R.; Rathore, A.K. Extended range ZVS active-clamped current-fed full-bridge isolated dc/dc converter for fuel cell applications: Analysis, design and experimental results. IEEE Trans. Ind. Electron. 2013, 60, 2661–2672. [Google Scholar]

- Moon, D.; Park, J.; Choi, S. New interleaved current-fed resonant converter with significantly reduced high current side output filter for EV and HEV applications. IEEE Trans. Power Electron. 2015, 30, 4264–4271. [Google Scholar] [CrossRef]

- Yuan, Y.; Wu, Q. One zero-voltage-switching three-transistor push–pull converter. IET Power Electron. 2013, 6, 1270–1278. [Google Scholar] [CrossRef]

- Zhang, Z.; Thomsen, O.C.; Andersen, M.A.E. Soft-switched dual-input DC–DC converter combining a boost-half-bridge cell and a voltage-fed full-bridge cel. IEEE Trans. Power Electron. 2013, 28, 4897–4902. [Google Scholar] [CrossRef]

- Perrin, R.; Quentin, N.; Allard, B.; Martin, C.; Ali, M. High temperature GaN active-clamped flyback converter with resonant operation mode. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 1077–1085. [Google Scholar] [CrossRef]

- Choi, W.Y.; Yoo, J.S. A bridgeless single-stage half-bridge ac/dc converter. IEEE Trans. Power Electron. 2011, 26, 3884–3895. [Google Scholar] [CrossRef]

- Lin, B.R.; Chao, C.H. A new zvs dc/dc converter with three APWM circuits. IEEE Trans. Ind. Electron. 2013, 60, 4351–4358. [Google Scholar] [CrossRef]

- Lin, B.R.; Huang, K.; Wang, D. Analysis and implementation of full-bridge converter with current doubler rectifier. IEE Electr. Power Appl. 2005, 152, 1193–1202. [Google Scholar] [CrossRef]

- Kanamarlapudi, V.R.K.; Wang, B.; Kandasamy, N.K.; So, P.L. A new zvs full-bridge dc-dc converter for battery charging with reduced losses over full-load range. IEEE Ind. Appl. 2018, 54, 571–579. [Google Scholar] [CrossRef]

- Li, Z.; Wu, T.; Zhang, G.; Yang, R. Hybrid modulation method combing variable frequency and double phase-shift for a 10kW LLC resonant converter. IET Power Electron. 2018, 11, 2161–2169. [Google Scholar] [CrossRef]

- Wu, H.N.; Choi, W. A novel dual full-bridge LLC resonant converter for CC and CV charges of batteries for electric vehicles. IEEE Trans. Ind. Electron. 2018, 65, 2212–2225. [Google Scholar]

- Lin, B.R.; Wu, S.F. Implementation of s series resonant converter with series-parallel transformers. IET Power Electron. 2011, 4, 919–926. [Google Scholar] [CrossRef]

- Wu, H.; Li, Y.; Xing, Y. LLC resonant converter with semiactive variable-structure rectifier (SA-VSR) for wide output voltage range application. IEEE Trans. Power Electron. 2016, 31, 3389–3394. [Google Scholar] [CrossRef]

- Xu, G.; Sha, D.; Xu, Y.; Liao, X. Dual-transformer-based DAB converter with wide zvs range for wide voltage conversion gain application. IEEE Trans. Ind. Electron. 2018, 65, 3306–3316. [Google Scholar] [CrossRef]

- Steigerwald, R.L. A comparison of half-bridge resonant converter topologies. IEEE Trans. Power Electron. 1988, 3, 174–182. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, B.-R.; Lin, G.-H. DC Converter with Wide Soft Switching Operation, Wide Input Voltage and Low Current Ripple. Appl. Sci. 2020, 10, 4672. https://doi.org/10.3390/app10134672

Lin B-R, Lin G-H. DC Converter with Wide Soft Switching Operation, Wide Input Voltage and Low Current Ripple. Applied Sciences. 2020; 10(13):4672. https://doi.org/10.3390/app10134672

Chicago/Turabian StyleLin, Bor-Ren, and Guan-Hong Lin. 2020. "DC Converter with Wide Soft Switching Operation, Wide Input Voltage and Low Current Ripple" Applied Sciences 10, no. 13: 4672. https://doi.org/10.3390/app10134672

APA StyleLin, B.-R., & Lin, G.-H. (2020). DC Converter with Wide Soft Switching Operation, Wide Input Voltage and Low Current Ripple. Applied Sciences, 10(13), 4672. https://doi.org/10.3390/app10134672