Area-Efficient Short-Time Fourier Transform Processor for Time–Frequency Analysis of Non-Stationary Signals

Abstract

:1. Introduction

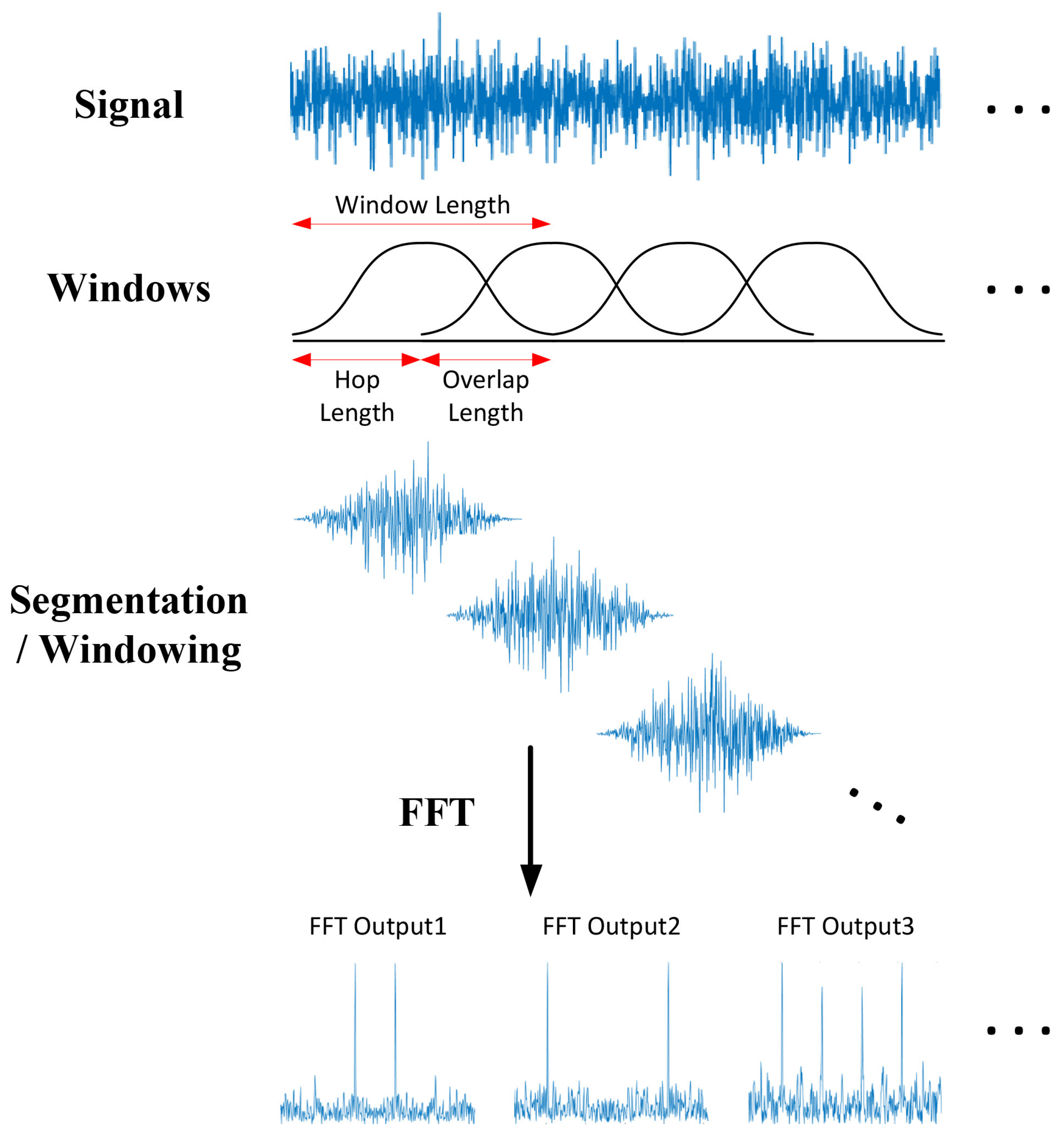

2. STFT Algorithm and Hardware Architecture

3. Hardware Architecture of the Proposed STFT Processor

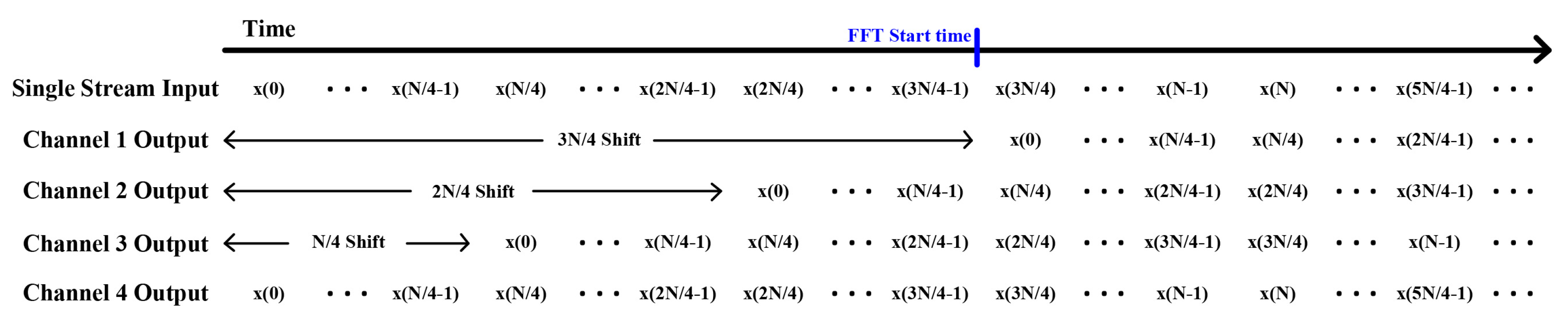

3.1. Variable Overlap Ratio of the Proposed STFT Processor

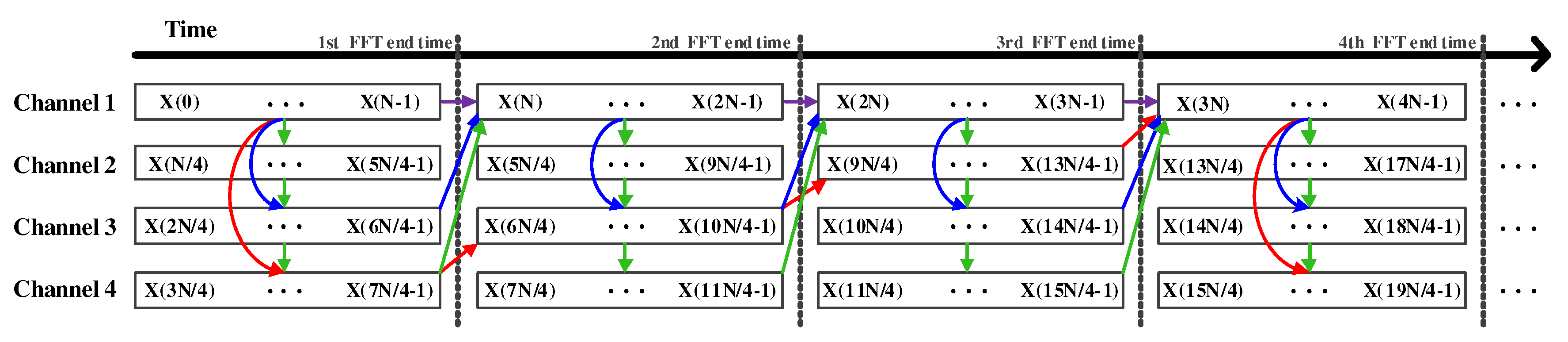

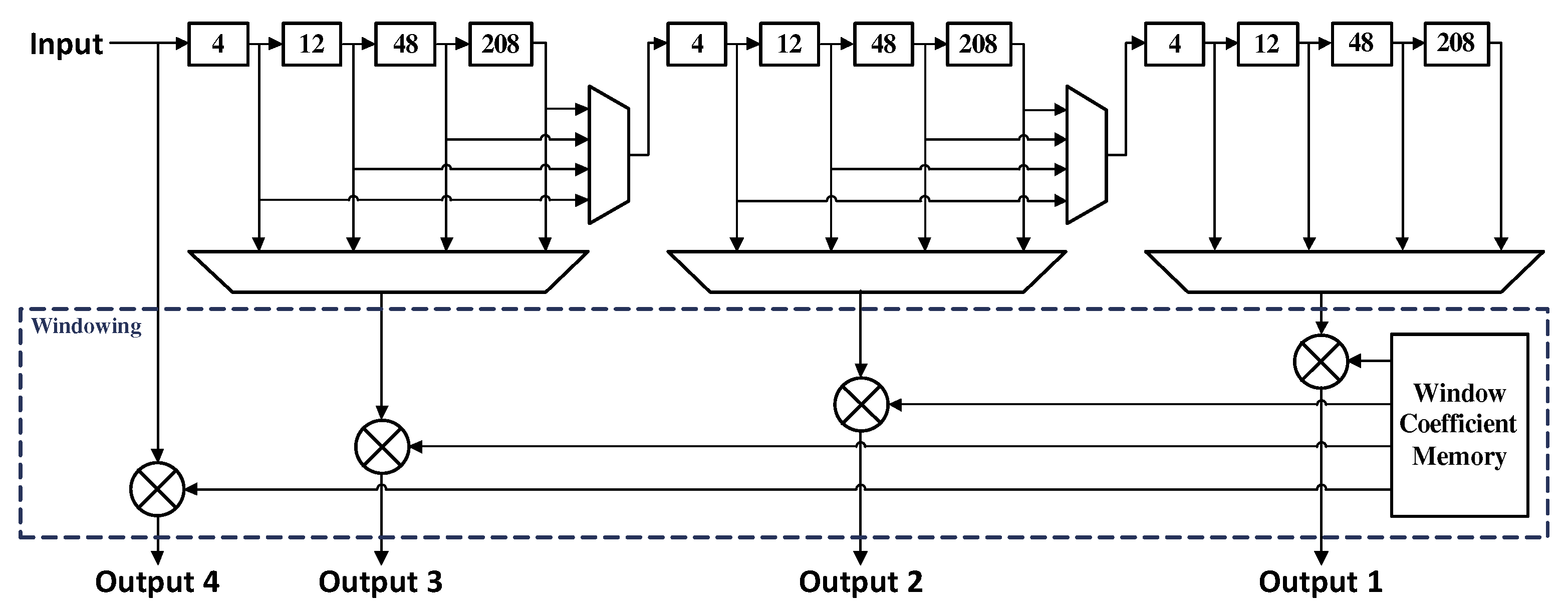

3.2. Hardware Architecture of the Proposed STFT Processor

3.2.1. Windowing Module (WM)

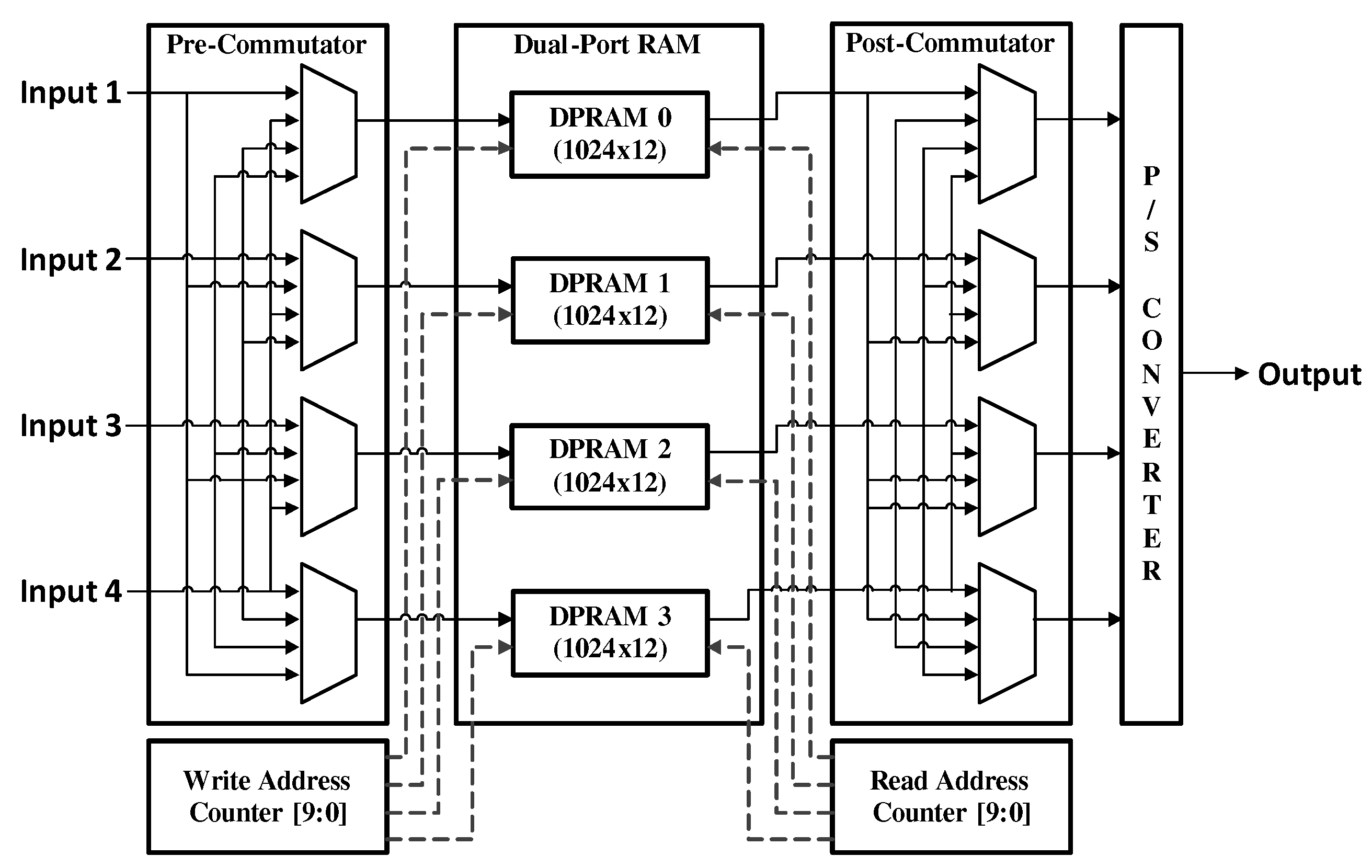

3.2.2. Data Reordering Module (DRM)

4. Implementation Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Ashouri, M.; Silva, F.F.; Bak, C.L. Application of short-time Fourier transform for harmonic-based protection of meshed VSC-MTDC grids. J. Eng. 2019, 16, 1439–1443. [Google Scholar] [CrossRef]

- Brito, N.S.D.; de Souza, B.A.; dos Santos, W.C.; de Andrade Fortunato, L.M. Analysis of the influence of the window used in the Short-Time Fourier Transform for High Impedance Fault detection. In Proceedings of the 2016 17th International Conference on Harmonics and Quality of Power (ICHQP), Belo Horizonte, Brazil, 16–19 October 2016; pp. 350–355. [Google Scholar]

- Zhang, K.; Xu, G.; Han, Z.; Ma, K.; Zheng, X.; Chen, L.; Duan, N.; Zhang, S. Data Augmentation for Motor Imagery Signal Classification Based on a Hybrid Neural Network. Sensors 2020, 20, 4485. [Google Scholar] [CrossRef] [PubMed]

- Liu, L.; McLernon, D.; Ghogho, M.; Hu, W.; Huang, J. Ballistic missile detection via micro-Doppler frequency estimation from radar return. Digit. Signal Process. 2012, 22, 87–95. [Google Scholar] [CrossRef]

- Cui, K.; Wu, W.; Huang, J. DOA estimation of LFM signals based on STFT and multiple invariance ESPRIT. AEU-Int. J. Electron. Commun. 2017, 77, 10–17. [Google Scholar] [CrossRef]

- Zhang, Y.; Dai, S.; Song, W.; Zhang, L.; Li, D. Exposing Speech Resampling Manipulation by Local Texture Analysis on Spectrogram Images. Electronics 2019, 9, 23. [Google Scholar] [CrossRef] [Green Version]

- Elbir, A.; İlhan, H.O.; Serbes, G.; Aydın, N. Short Time Fourier Transform based music genre classification. In Proceedings of the Electric Electronics, Computer Science, Biomedical Engineerings’ Meeting (EBBT), Istanbul, Turkey, 18–19 April 2018; pp. 1–4. [Google Scholar]

- Wang, H.; Shi, W.; Choy, C.S. Hardware design of real time epileptic seizure detection based on STFT and SVM. IEEE Access 2018, 6, 67277–67290. [Google Scholar] [CrossRef]

- Fujiwara, N.; Shimasaki, K.; Jiang, M.; Takaki, T.; Ishii, I. A Real-time Drone Surveillance System Using Pixel-level Short-time Fourier Transform. In Proceedings of the 2019 IEEE International Symposium on Safety, Security, and Rescue Robotics (SSRR), Würzburg, Germany, 2–4 September 2019; pp. 303–308. [Google Scholar]

- Gong, P.; Luo, M.; Zhou, L.; Jiang, L.; Chen, X. An Image Processing Method for Extraction of the Stress Wave Reflection Period. Appl. Sci. 2020, 10, 3486. [Google Scholar] [CrossRef]

- Lee, S.; Park, S. Modified SDF Architecture for Mixed DIF/DIT FFT. In Proceedings of the 2007 IEEE International Symposium on Circuits and Systems (ISCAS), New Orleans, LA, USA, 27–30 May 2007; pp. 2590–2593. [Google Scholar]

- Sansaloni, T.; Perez-Pascual, A.; Torres, V.; Valls, J. Efficient pipeline FFT processors for WLAN MIMO-OFDM systems. IET Electorn. Lett. 2005, 41, 1043–1044. [Google Scholar] [CrossRef]

- Khan, N.A.; Jafri, M.N.; Qazi, S.A. Improved resolution short time Fourier transform. In Proceedings of the 2011 7th International Conference on Emerging Technologies (ICET), Islamabad, Pakistan, 5–6 September 2011; pp. 1–3. [Google Scholar]

- Mateo, C.; Talavera, J.A. Short-time Fourier transform with the window size fixed in the frequency domain. Digit. Signal Process. 2018, 77, 13–21. [Google Scholar] [CrossRef]

- Yin, Q.; Shen, L.; Lu, M.; Wang, X.; Liu, Z. Selection of optimal window length using STFT for quantitative SNR analysis of LFM signal. J. Syst. Eng. Elect. 2013, 24, 26–35. [Google Scholar] [CrossRef]

- Nisar, S.; Khan, O.U.; Tariq, M. An Efficient Adaptive Window Size Selection Method for Improving Spectrogram Visualization. Comput. Intell. Neurosci. 2016, 2016. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Spectrum and Spectral Density Estimation by the Discrete Fourier Transform (DFT), Including a Comprehensive List of Window Functions and Some New at-Top Windows. Available online: https://pure.mpg.de/pubman/faces/ViewItemOverviewPage.jsp?itemId=item_152164 (accessed on 8 October 2020).

- Zhang, S.; Yu, D.; Sheng, S. A discrete STFT processor for real-time spectrum analysis. In Proceedings of the 2006 Asia Pacific Conference on Circuits and Systems (APCCAS), Singapore, 4–7 December 2006; pp. 1943–1946. [Google Scholar]

- Srinivas, N.; Kumar, P.K.; Pradhan, G. Low latency architecture design and implementation for short-time fourier transform algorithm on FPGA. In Proceedings of the IEEE International Conference on Microwaves, Antennas, Communications and Electronic Systems (COMCAS), Tel Aviv, Israel, 13–15 November 2017; pp. 1–5. [Google Scholar]

- Shi, L.Z.; Guo, J.M. Design of an 8-channel FFT processor for IEEE 802.11 ac MIMO-OFDM WLAN system. Circuits Syst. Signal Process. 2016, 35, 3759–3769. [Google Scholar] [CrossRef]

- Yu, C.; Yen, M.H. Area-Efficient 128- to 2048/1536-Point Pipeline FFT Processor for LTE and Mobile WiMAX Systems. IEEE Trans. VLSI Syst. 2015, 23, 1793–1800. [Google Scholar] [CrossRef]

- Wu, G.D.; Lei, Y. Low power pipelined radix-2 FFT processor for speech recognition. In Proceedings of the IEEE/SMC International Conference on System of Systems Engineering, Los Angeles, CA, USA, 24–26 April 2006; pp. 299–303. [Google Scholar]

- Locharla, G.R.; Mahapatra, K.K.; Ari, S. Variable length mixed radix MDC FFT/IFFT processor for MIMO-OFDM application. IET Comput. Digit. Tech. 2018, 12, 9–19. [Google Scholar] [CrossRef]

- Yang, K.J.; Tsai, S.H.; Chuang, G.C. MDC FFT/IFFT processor with variable length for MIMO-OFDM systems. IEEE Trans. Large Scale Integr. (VLSI) Syst. 2012, 21, 720–731. [Google Scholar] [CrossRef]

- Lee, T.Y.; Huang, C.H.; Chen, W.C.; Liu, M.J. A low-area dynamic reconfigurable MDC FFT processor design. Microprocess. Microsyst. 2016, 42, 227–234. [Google Scholar] [CrossRef]

- Yoshizawa, S.; Orikasa, A.; Miyanaga, Y. An area and power efficient pipeline FFT processor for 8 × 8 MIMO-OFDM systems. In Proceedings of the IEEE International Symposium on Circuits and System (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 2705–2708. [Google Scholar]

- Design Compiler Graphical. Available online: https://www.synopsys.com/implementation-and-signoff/rtl-synthesis-test/design-compiler-graphical.html (accessed on 8 October 2020).

| Block Name | R2SDF Based | R4MDC Based | Proposed | Reduction (%) | |

|---|---|---|---|---|---|

| R2SDF | R4MDC | ||||

| Butterfly Unit | 30,072 | 15,036 | 15,036 | 50 | 0 |

| Multiplier | 141,138 | 47,046 | 47,046 | 67 | 0 |

| Delay Elements | 369,360 | 369,360 | 135,888 | 63 | 63 |

| Total | 540,670 | 431,442 | 197,970 | 63 | 54 |

| Circuit | Tech (nm) | FFT Architecture | Window Length (N) | Overlap Ratio | Frequency (MHz) | Operating Time (ns) | Area (mm) | A |

|---|---|---|---|---|---|---|---|---|

| [18] | 180 | R2SDF | 32 | max. 94 | 180 | N.A. | 7.74 | 2.15 |

| Proposed | 65 | R4MDC | 16/64/ 256/1024 | 0/25/ 50/75 | 200 | 175/665/ 2596/10,285 | 0.27 | 0.93 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jeon, H.; Jung, Y.; Lee, S.; Jung, Y. Area-Efficient Short-Time Fourier Transform Processor for Time–Frequency Analysis of Non-Stationary Signals. Appl. Sci. 2020, 10, 7208. https://doi.org/10.3390/app10207208

Jeon H, Jung Y, Lee S, Jung Y. Area-Efficient Short-Time Fourier Transform Processor for Time–Frequency Analysis of Non-Stationary Signals. Applied Sciences. 2020; 10(20):7208. https://doi.org/10.3390/app10207208

Chicago/Turabian StyleJeon, Hohyub, Yongchul Jung, Seongjoo Lee, and Yunho Jung. 2020. "Area-Efficient Short-Time Fourier Transform Processor for Time–Frequency Analysis of Non-Stationary Signals" Applied Sciences 10, no. 20: 7208. https://doi.org/10.3390/app10207208

APA StyleJeon, H., Jung, Y., Lee, S., & Jung, Y. (2020). Area-Efficient Short-Time Fourier Transform Processor for Time–Frequency Analysis of Non-Stationary Signals. Applied Sciences, 10(20), 7208. https://doi.org/10.3390/app10207208