Enhanced Efficient EMT-Type Model of the MMCs Based on Arm Equivalence

Abstract

:1. Introduction

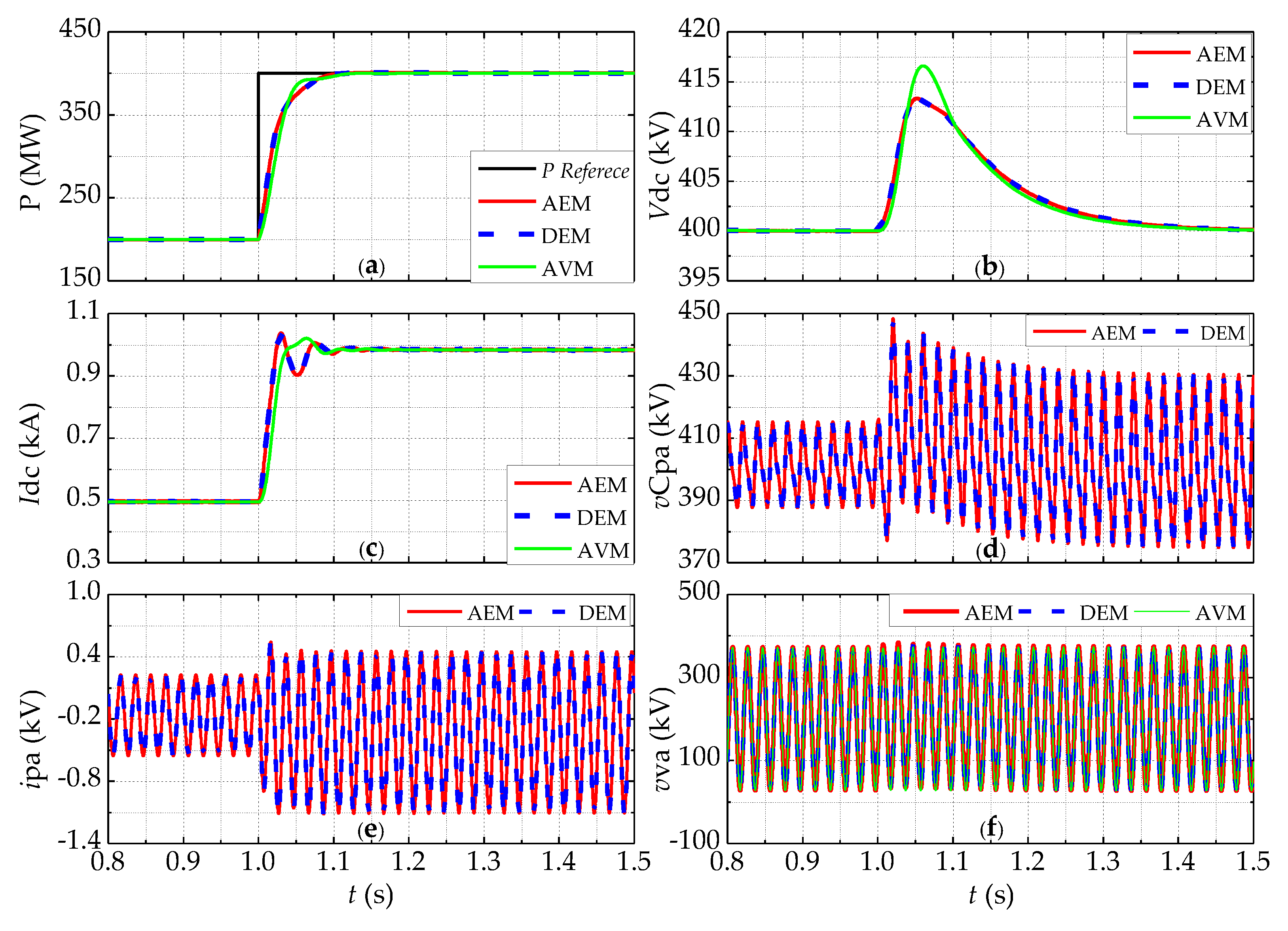

- The proposed AEM can more accurately reproduce the dynamics of the arm currents and the SM capacitor voltages compared to AVMs. The proposed AEM can reproduce the dynamic behaviors of the DEM under different scenarios very accurately, and is more computationally efficient with no loss of accuracy.

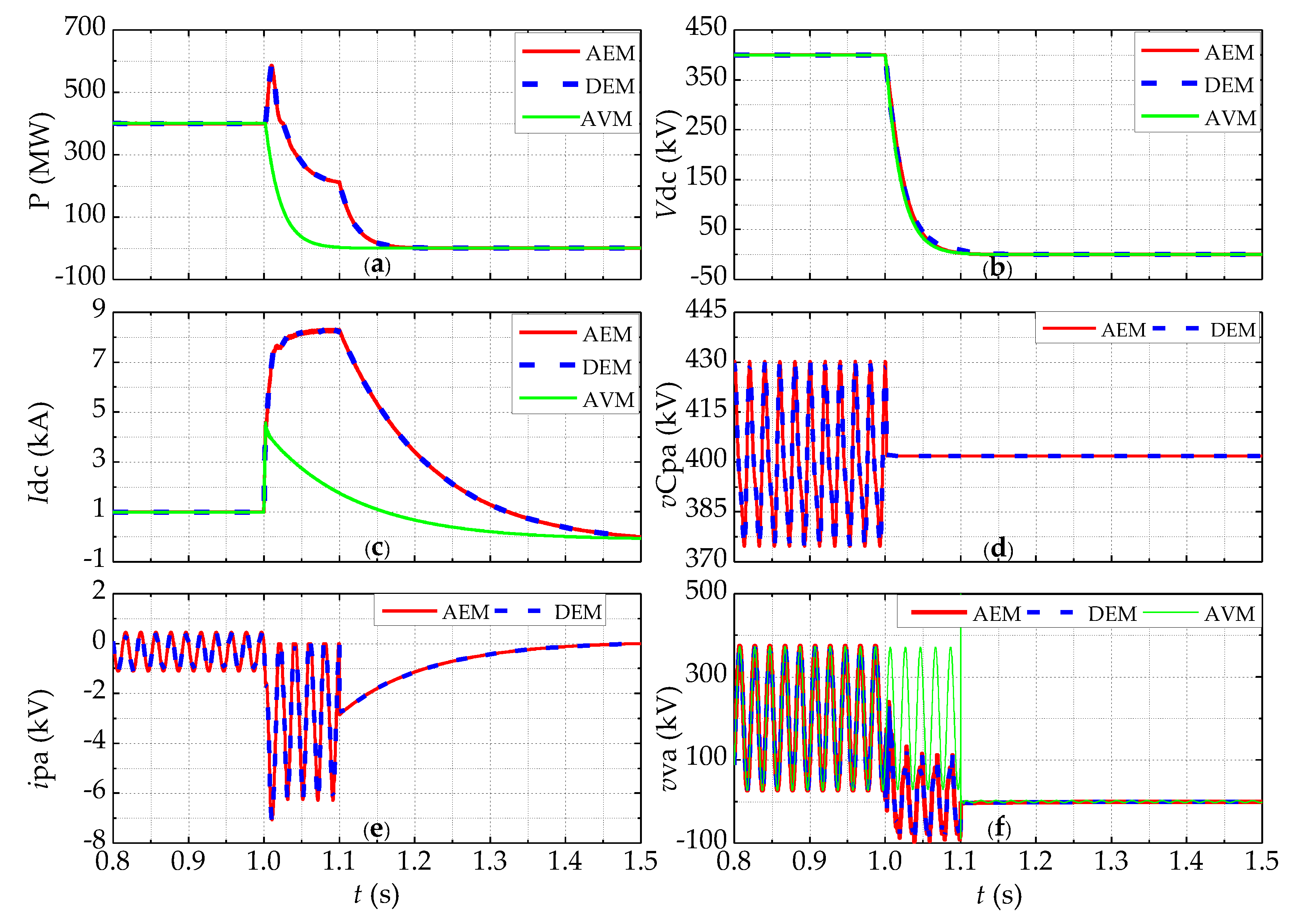

- The proposed AEM can accurately represent the dynamic responses in both de-blocked and blocked modes. Meanwhile, the ON-state and OFF-state resistances of the IGBT and its anti-parallel diodes in the SMs are accurately represented.

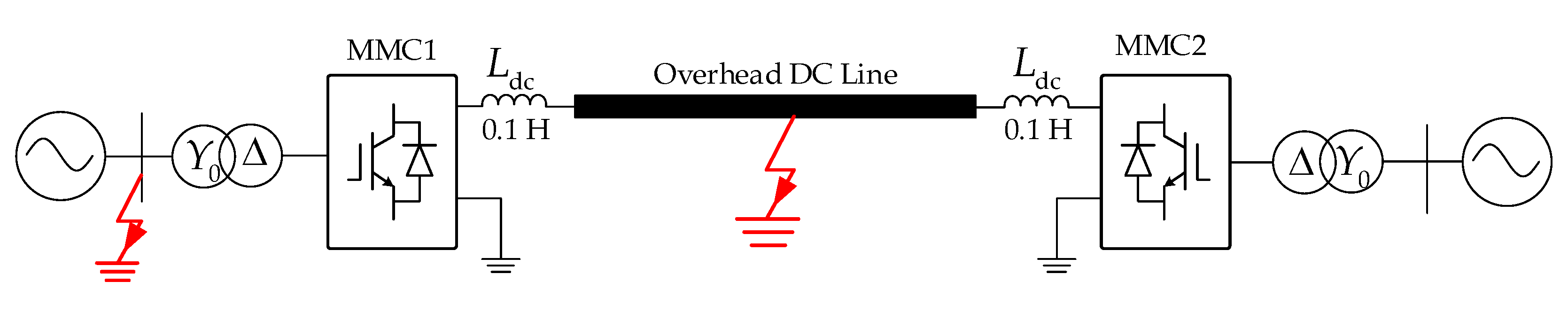

- The proposed AEM is verified against the DEM and AVM in a two-terminal MMC-HVDC system. The simulation results demonstrate the accuracy and computational efficiency of the proposed model in both de-blocked and blocked modes. Moreover, the simulation speed of the AEM is irrespective of the SM number.

- Except for the dynamics of individual SMs, the proposed AEM could be suitable for various simulation scenarios with no loss of accuracy, especially for large-scale MMC-HVDC grids.

2. General Structure, Control Scheme, and Previous Models of the MMC

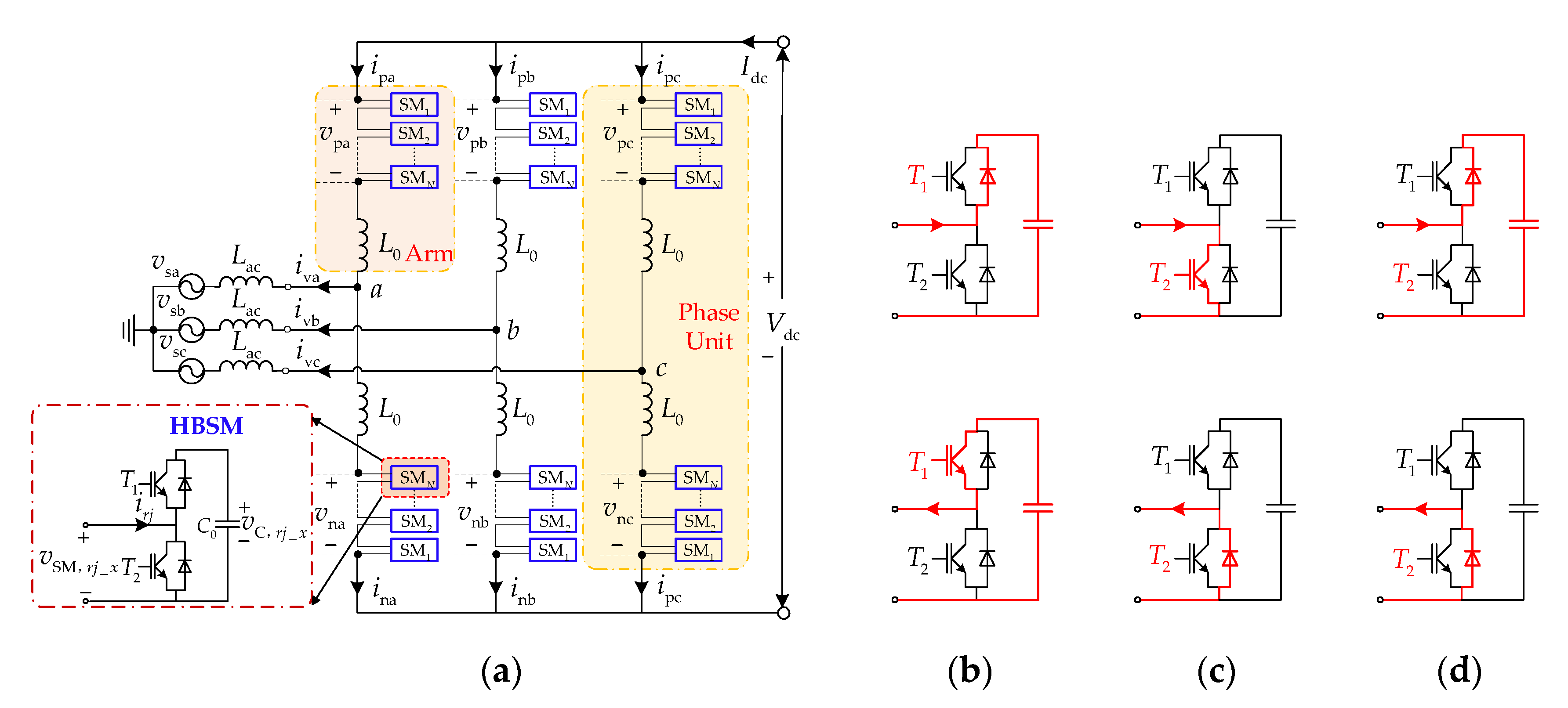

2.1. General Structure

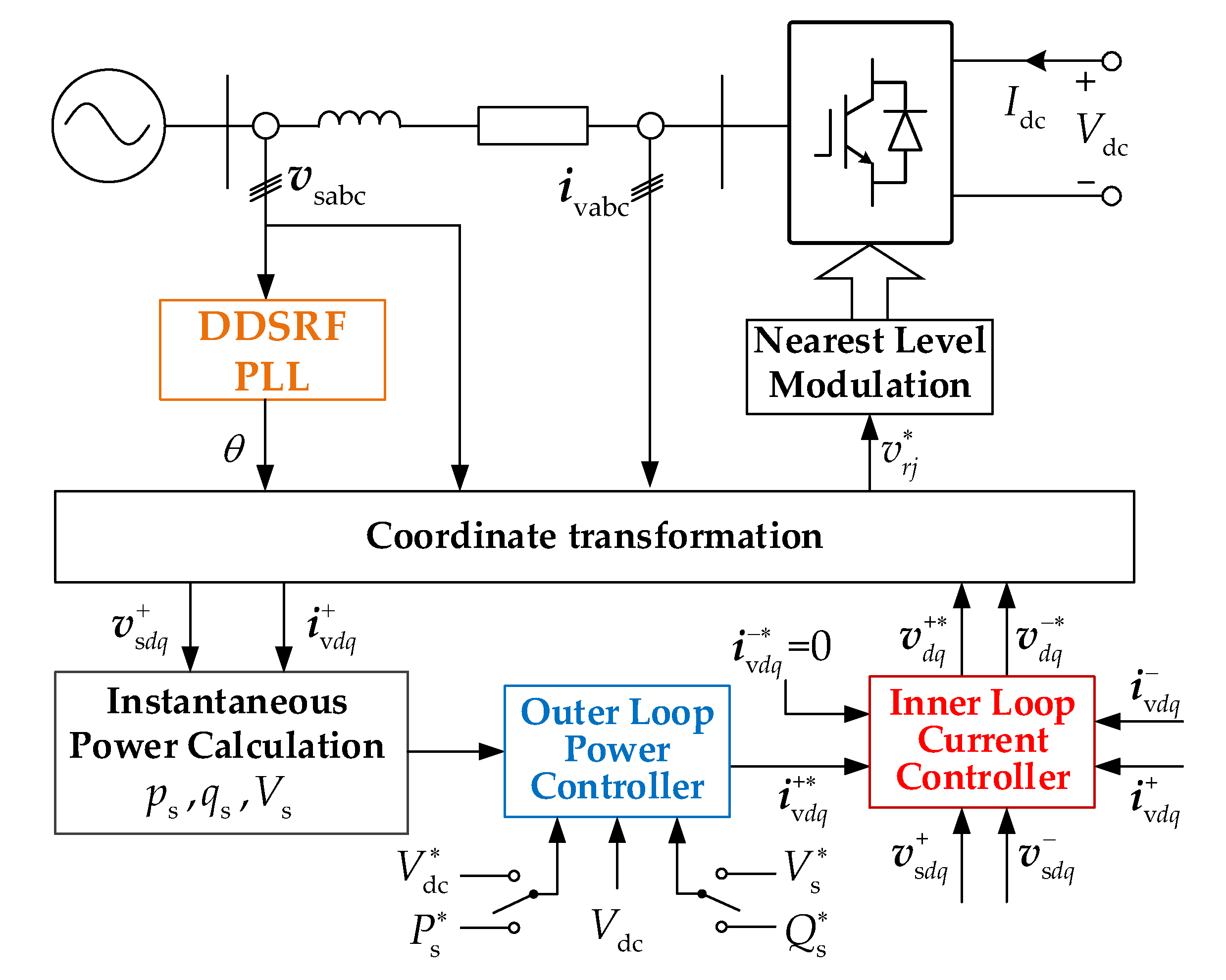

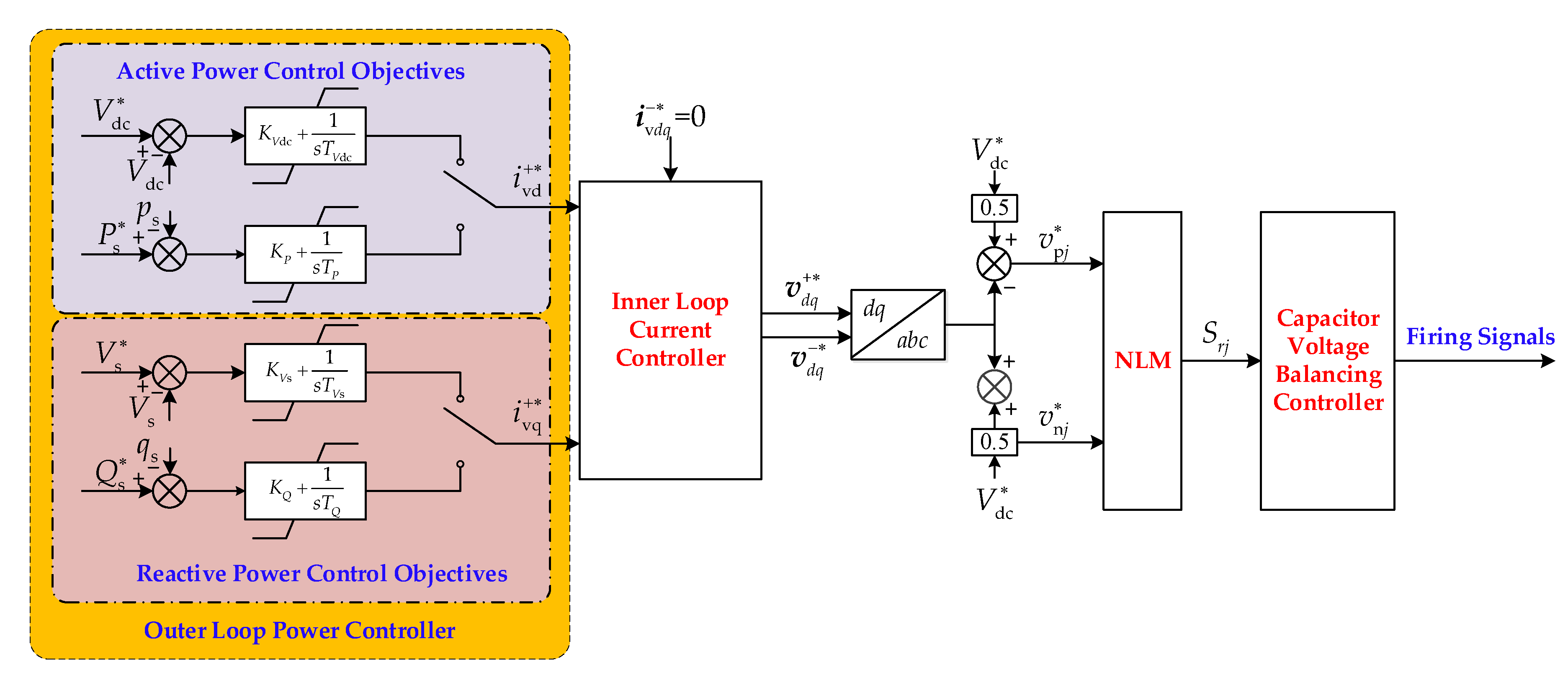

2.2. Control Scheme

2.3. Previous Models

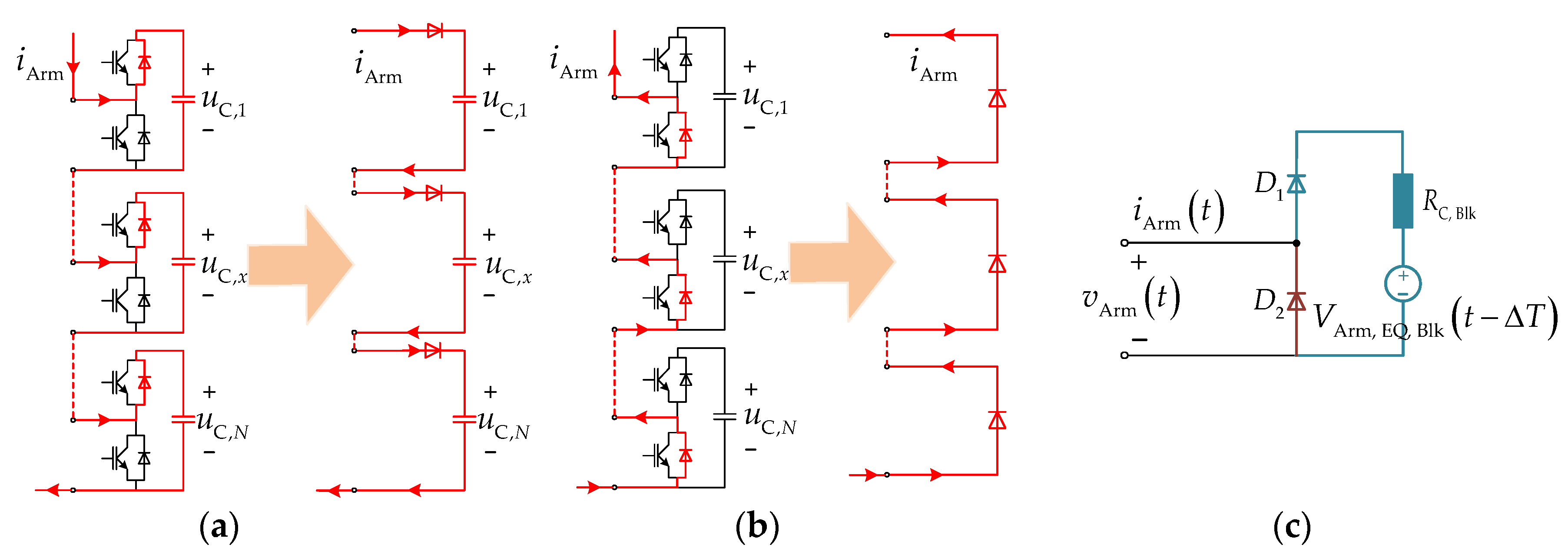

2.3.1. Type A: Detailed Equivalent Models (DEMs)

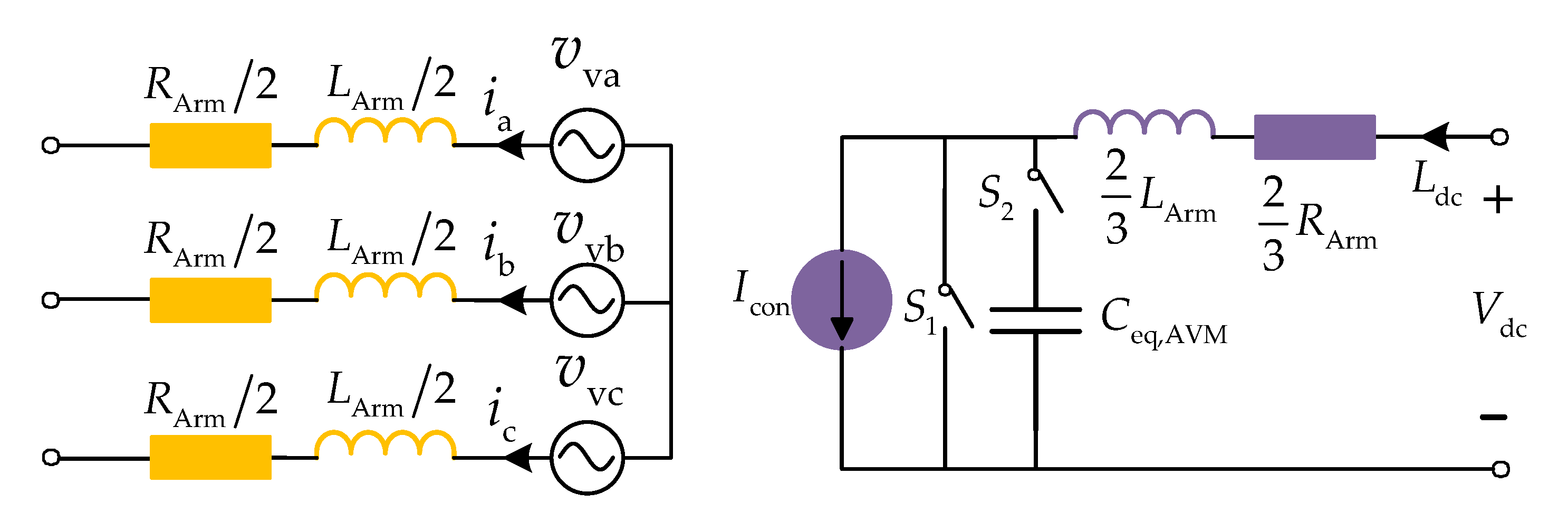

2.3.2. Type B: Average Value Models (AVMs)

3. Equivalent Circuit of the MMC

3.1. Average Capacitor Current of the SMs

3.2. Equivalent Voltage of the Arm

3.3. Equivalent Voltage of the Arm

3.4. Values of Resistances R1 and R2

4. Modelling Process of the Proposed AEM

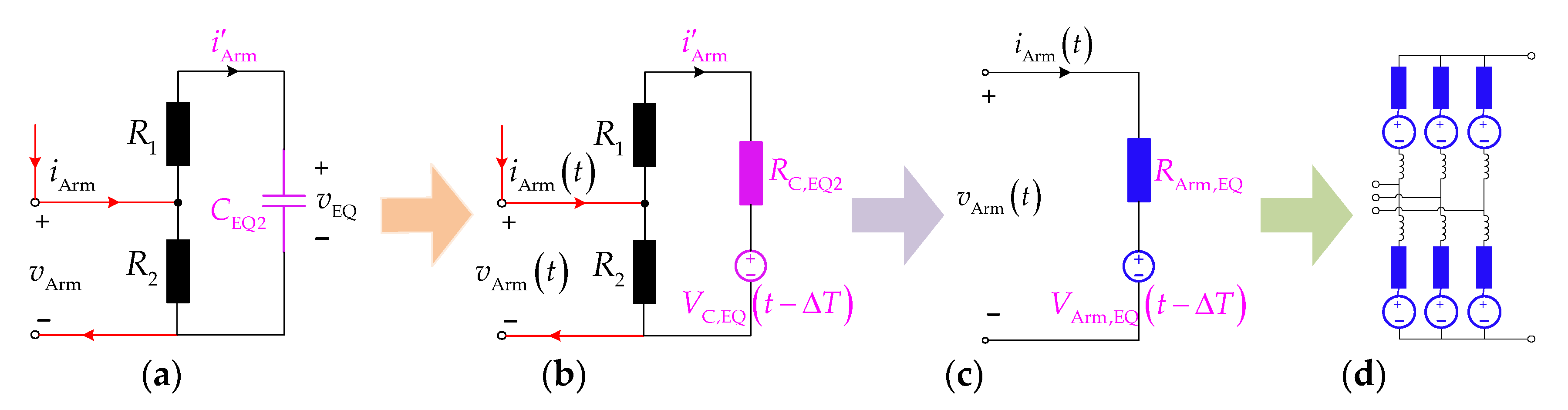

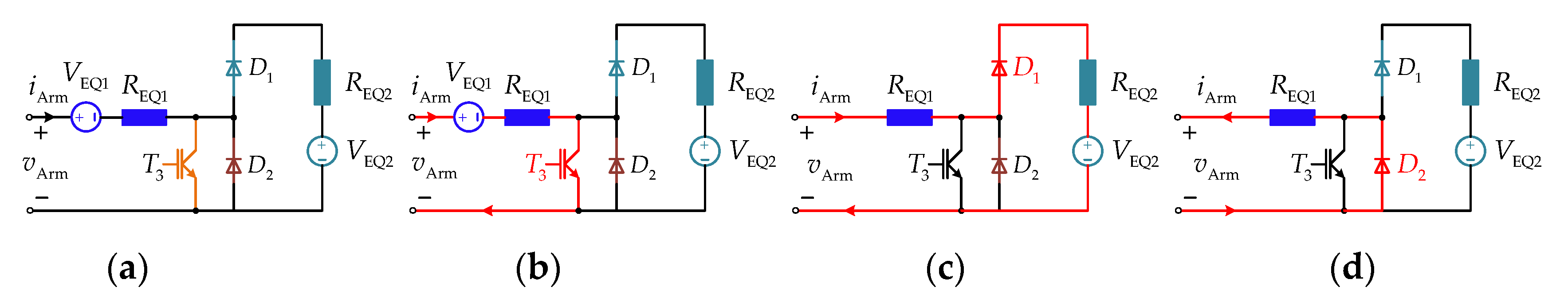

4.1. Thévenin Equivalent Circuit for the Arm on De-Blocked Model

4.2. Solution for the Equivalent Capacitor Voltage on De-Blocked Model

4.3. Thévenin Equivalent Circuit for the Arm on Blocked Model

4.4. Thévenin Equivalent Circuit for Full States

5. Simulation Studies

5.1. Steady State

5.2. DC-Side Pole-to-Ground Fault

5.3. AC-Side Three-Phase-to-Ground Fault

5.4. Computational Performance

6. Conclusions

- The proposed model can accurately represent the dynamics of the arm currents and SM capacitor voltages compared to AVM. In terms of simulation efficiency, the proposed AEM is only about 45% slower than the AVM, and is more than three times faster than the DEM.

- Compared to the DEM, the proposed AEM very accurately reproduces the dynamic behaviors of the DEM under different scenarios, and affords a substantial acceleration in simulation speed, with no loss of accuracy. Except for the dynamics of individual SMs, the proposed AEM could be suitable for various simulation scenarios with no loss of accuracy.

- The proposed AEM consumes the same amount of execution time regardless of the number of the SMs per arm, thus it can be efficiently adopted for large-scale MMC-HVDC grids with high computational speed.

- Although the simulation efficiency of AVMs is satisfactory, they lose accuracy compared to DEMs, especially for the blocked mode. Thus, the AVMs are suitable for system-level studies, which mainly focus on the steady-state dynamics and responses of AC fault.

Author Contributions

Funding

Conflicts of Interest

References

- Qin, B.; Liu, W.; Zhang, R.; Liu, J.; Li, H. Review on short-circuit current analysis and suppression techniques for MMC-HVDC transmission systems. Appl. Sci. 2020, 10, 6769. [Google Scholar] [CrossRef]

- Diaz, M.; Cárdenas Dobson, R.; Ibaceta, E.; Mora, A.; Urrutia, M.; Espinoza, M.; Rojas, F.; Wheeler, P. An overview of applications of the modular multilevel matrix converter. Energies 2020, 13, 5546. [Google Scholar] [CrossRef]

- Wang, Z.; Lin, H.; Ma, Y. A control strategy of modular multilevel converter with integrated battery energy storage system based on battery side capacitor voltage control. Energies 2019, 12, 2151. [Google Scholar] [CrossRef] [Green Version]

- Liu, G.; Xu, F.; Xu, Z.; Zhang, Z.; Tang, G. Assembly HVDC breaker for HVDC grids with modular multilevel converters. IEEE Trans. Power Electron. 2017, 32, 931–941. [Google Scholar] [CrossRef]

- Zhang, Z.; Xu, Z.; Xu, T. Calculating current and temperature fields of HVDC grounding electrodes. J. Mod. Power Syst. Clean Energy 2016, 4, 300–307. [Google Scholar] [CrossRef]

- Qin, B.; Li, H.; Zhou, X.; Li, J.; Liu, W. Low-voltage ride-through techniques in DFIG-based wind Turbines: A review. Appl. Sci. 2020, 10, 2154. [Google Scholar] [CrossRef] [Green Version]

- Debnath, S.; Qin, J.; Bahrani, B.; Saeedifard, M.; Barbosa, P. Operation, control, and applications of the modular multilevel converter: A review. IEEE Trans. Power Electron. 2015, 30, 37–53. [Google Scholar] [CrossRef]

- Cigre Working Group B4-57. Guide for the Development of Models for HVDC Converters in a HVDC Grid: TB-604; Cigre Working Group B4-57: Paris, France, 2014. [Google Scholar]

- Diaz, M.; Cardenas, R.; Ibaceta, E.; Mora, A.; Urrutia, M.; Espinoza, M.; Rojas, F.; Wheeler, P. An overview of modelling techniques and control strategies for modular multilevel matrix converters. Energies 2020, 13, 4678. [Google Scholar] [CrossRef]

- Peralta, J.; Saad, H.; Dennetière, S.; Mahseredjian, J.; Nguefeu, S. Detailed and averaged models for a 401-level MMC-HVDC system. IEEE Trans. Power Deliv. 2012, 27, 1501–1508. [Google Scholar] [CrossRef]

- Tu, Q.; Xu, Z. Impact of sampling frequency on harmonic distortion for modular multilevel converter. IEEE Trans. Power Deliv. 2011, 26, 298–306. [Google Scholar] [CrossRef]

- Gnanarathna, U.N.; Gole, A.M.; Jayasinghe, R.P. Efficient modeling of modular multilevel HVDC converters (MMC) on electromagnetic transient simulation programs. IEEE Trans. Power Deliv. 2011, 26, 316–324. [Google Scholar] [CrossRef] [Green Version]

- Ajaei, F.B.; Iravani, R. Enhanced equivalent model of the modular multilevel converter. IEEE Trans. Power Deliv. 2015, 30, 666–673. [Google Scholar] [CrossRef]

- Xu, J.; Gole, A.M.; Zhao, C. The use of averaged-value model of modular multilevel converter in DC grid. IEEE Trans. Power Deliv. 2015, 30, 519–528. [Google Scholar] [CrossRef]

- Beddard, A.; Sheridan, C.E.; Barnes, M.; Green, T.C. Improved accuracy average value models of modular multilevel converters. IEEE Trans. Power Deliv. 2016, 31, 2260–2269. [Google Scholar] [CrossRef]

- Song, Q.; Liu, W.; Li, X.; Rao, H.; Xu, S.; Li, L. A steady-state analysis method for a modular multilevel converter. IEEE Trans. Power Electron. 2013, 28, 3702–3713. [Google Scholar] [CrossRef]

- Liu, M.; Li, Z.; Yang, X. A universal mathematical model of modular multilevel converter with half-bridge. Energies 2020, 13, 4464. [Google Scholar] [CrossRef]

- Corazza, G.; Someda, C.; Longo, G. Generalized thevenin’s theorem for linear N-port networks. IEEE Trans. Circuit Theory 1969, 16, 564–566. [Google Scholar] [CrossRef]

- Strunz, K.; Carlson, E. Nested fast and simultaneous solution for time-domain simulation of integrative power-electric and electronic systems. IEEE Trans. Power Deliv. 2007, 22, 277–287. [Google Scholar] [CrossRef]

- Tu, Q.; Xu, Z.; Xu, L. Reduced switching-frequency modulation and circulating current suppression for modular multilevel converters. IEEE Trans. Power Deliv. 2011, 26, 2009–2017. [Google Scholar]

- Rodriguez, P.; Pou, J.; Bergas, J.; Candela, J.I.; Burgos, R.P.; Boroyevich, D. Decoupled double synchronous reference frame PLL for power converters control. IEEE Trans. Power Electron. 2007, 22, 584–592. [Google Scholar] [CrossRef]

- Akagi, H.; Watanbe, E.H.; Aredes, M. Instantaneous Power Theory and Applications to Power Conditioning; IEEE Press/Wiley-Interscience: Piscataway, NJ, USA, 2007. [Google Scholar]

- Xu, L.; Andersen, B.; Cartwright, P. VSC transmission operating under unbalanced AC conditions–Analysis and control design. IEEE Trans. Power Deliv. 2005, 20, 427–434. [Google Scholar] [CrossRef]

- Guan, M.; Xu, Z. Modeling and control of a modular multilevel converter-based HVDC system under unbalanced grid conditions. IEEE Trans. Power Electron. 2012, 27, 4858–4867. [Google Scholar] [CrossRef]

- Manitoba Hydro International Ltd. PSCAD User’s Guide v4.6. 2018. Available online: https://www.pscad.com/knowledge-base/article/160 (accessed on 10 October 2020).

- Xiao, H.; Xu, Z.; Tang, G.; Xue, Y. Complete mathematical model derivation for modular multilevel converter based on successive approximation approach. IET Power Electron. 2015, 8, 2396–2410. [Google Scholar] [CrossRef]

- Liu, G.; Xu, Z.; Xue, Y.; Tang, G. Optimized control strategy based on dynamic redundancy for the modular multilevel converter. IEEE Trans. Power Electron. 2015, 30, 339–348. [Google Scholar] [CrossRef]

- Nguyen, M.H.; Kwak, S. Improved indirect model predictive control for enhancing dynamic performance of modular multilevel converter. Electronics 2020, 9, 1405. [Google Scholar] [CrossRef]

- Dommel, H.W. Digital computation of electromagnetic transients in single and multi-phase networks. IEEE Trans. Power App. Syst. 1969, PAS-88, 388–399. [Google Scholar] [CrossRef]

- Xu, Z.; Xiao, H.; Xiao, L.; Zhang, Z. DC fault analysis and clearance solutions of MMC-HVDC systems. Energies 2018, 11, 941. [Google Scholar] [CrossRef] [Green Version]

- Wang, S.; Alsokhiry, F.S.; Adam, G.P. Impact of submodule faults on the performance of modular multilevel converters. Energies 2020, 13, 4089. [Google Scholar] [CrossRef]

| State | Current Direction | T3 | D1 | D2 | VEQ1 | REQ1 | VEQ2 | REQ2 |

|---|---|---|---|---|---|---|---|---|

| De-blocked | Positive | ON | OFF | OFF | Equation (32) | Equation (31) | 0 | 0 |

| Negative | ON | OFF | ON | Equation (32) | Equation (31) | 0 | 0 | |

| Blocked | Positive | OFF | ON | OFF | 0 | NRon | Equation (39) | Equation (38) |

| Negative | OFF | OFF | ON | 0 | NRon | 0 | 0 |

| MMC Converter | |||||

|---|---|---|---|---|---|

| Items | Values | Items | Values | ||

| Rated capacity (MV·A) | 400 | Interface transformer | Rated capacity (MV·A) | 480 | |

| AC system rated voltage RMS (kV) | 230 | Radio (kV/kV) | 230/210 | ||

| Rated DC voltage Vdc (kV) | 400 | Leakage reactance (p.u.) | 0.15 | ||

| Rated voltage of HBSM vC (kV) | 2 | Number of SMs per arm | 200 | ||

| HBSM capacitance C0 (mF) | 6.67 | Arm inductance L0 (mH) | 33.77 | ||

| Ron (Ω) | 0.01 | Roff (Ω) | 1,000,000 | ||

| Overhead DC Line | |||||

| Items | Length (km) | + ve Sequence R (Ω/km) | + ve Sequence L (H/km) | + ve Sequence C (F/km) | |

| Value | 100 | 9.735 × 10−3 | 8.489 × 10−4 | 1.367 × 10−8 | |

| Number of SMs per Arm | CPU Time (s) | ||

|---|---|---|---|

| AEM | DEM | AVM | |

| 150 | 8.1 | 18.4 | 5.6 |

| 200 | 8.1 | 21.7 | 5.5 |

| 250 | 8.2 | 25.1 | 5.5 |

| 300 | 8.2 | 28.5 | 5.6 |

| 350 | 8.1 | 31.8 | 5.5 |

| 400 | 8.2 | 35.5 | 5.6 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, X.; Xu, Z. Enhanced Efficient EMT-Type Model of the MMCs Based on Arm Equivalence. Appl. Sci. 2020, 10, 8421. https://doi.org/10.3390/app10238421

Li X, Xu Z. Enhanced Efficient EMT-Type Model of the MMCs Based on Arm Equivalence. Applied Sciences. 2020; 10(23):8421. https://doi.org/10.3390/app10238421

Chicago/Turabian StyleLi, Xiaodong, and Zheng Xu. 2020. "Enhanced Efficient EMT-Type Model of the MMCs Based on Arm Equivalence" Applied Sciences 10, no. 23: 8421. https://doi.org/10.3390/app10238421

APA StyleLi, X., & Xu, Z. (2020). Enhanced Efficient EMT-Type Model of the MMCs Based on Arm Equivalence. Applied Sciences, 10(23), 8421. https://doi.org/10.3390/app10238421