Solution-Processed Memristor Devices Using a Colloidal Quantum Dot-Polymer Composite

Abstract

:1. Introduction

2. Materials and Methods

3. Results

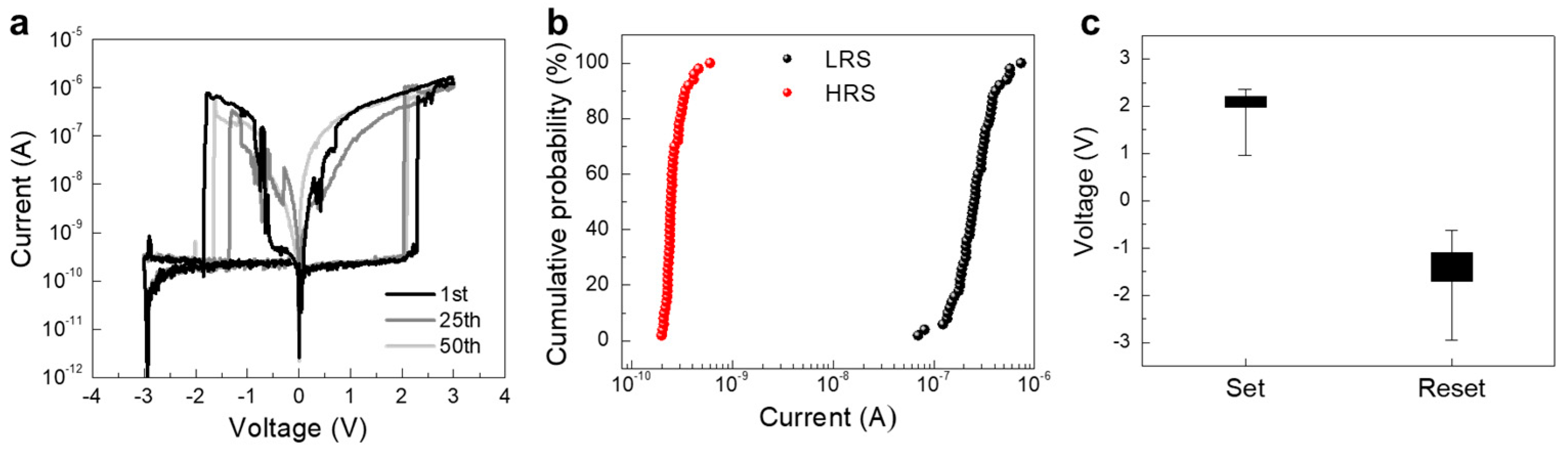

3.1. Device Structure and Electrical Characteristics

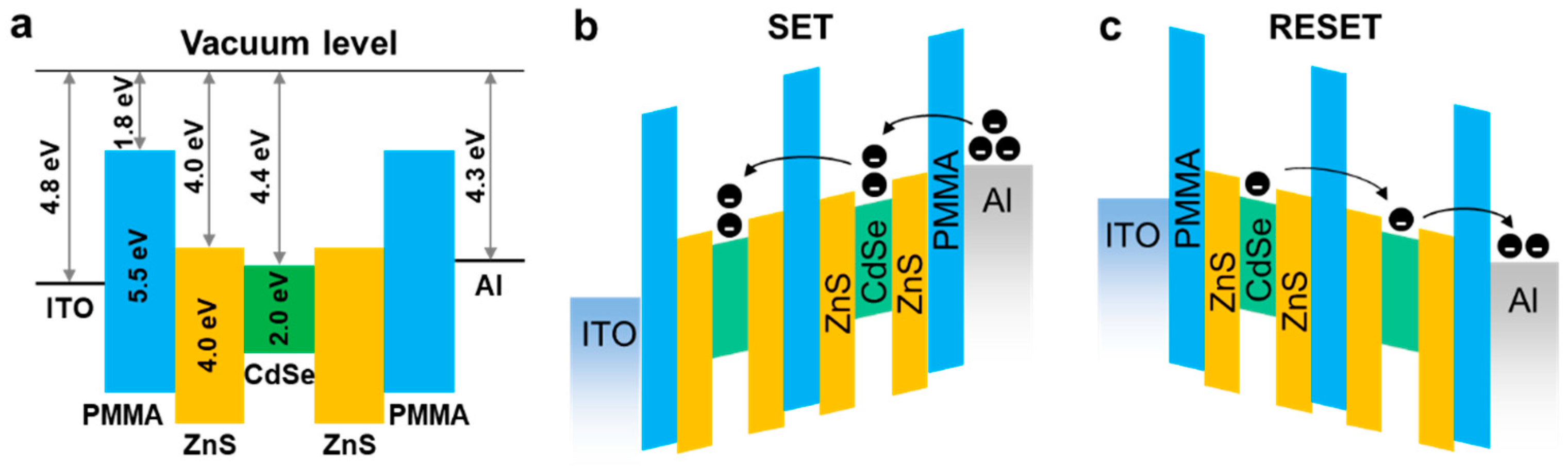

3.2. Operation Mechanism of CdSe/ZnS QD-PMMA Memristors

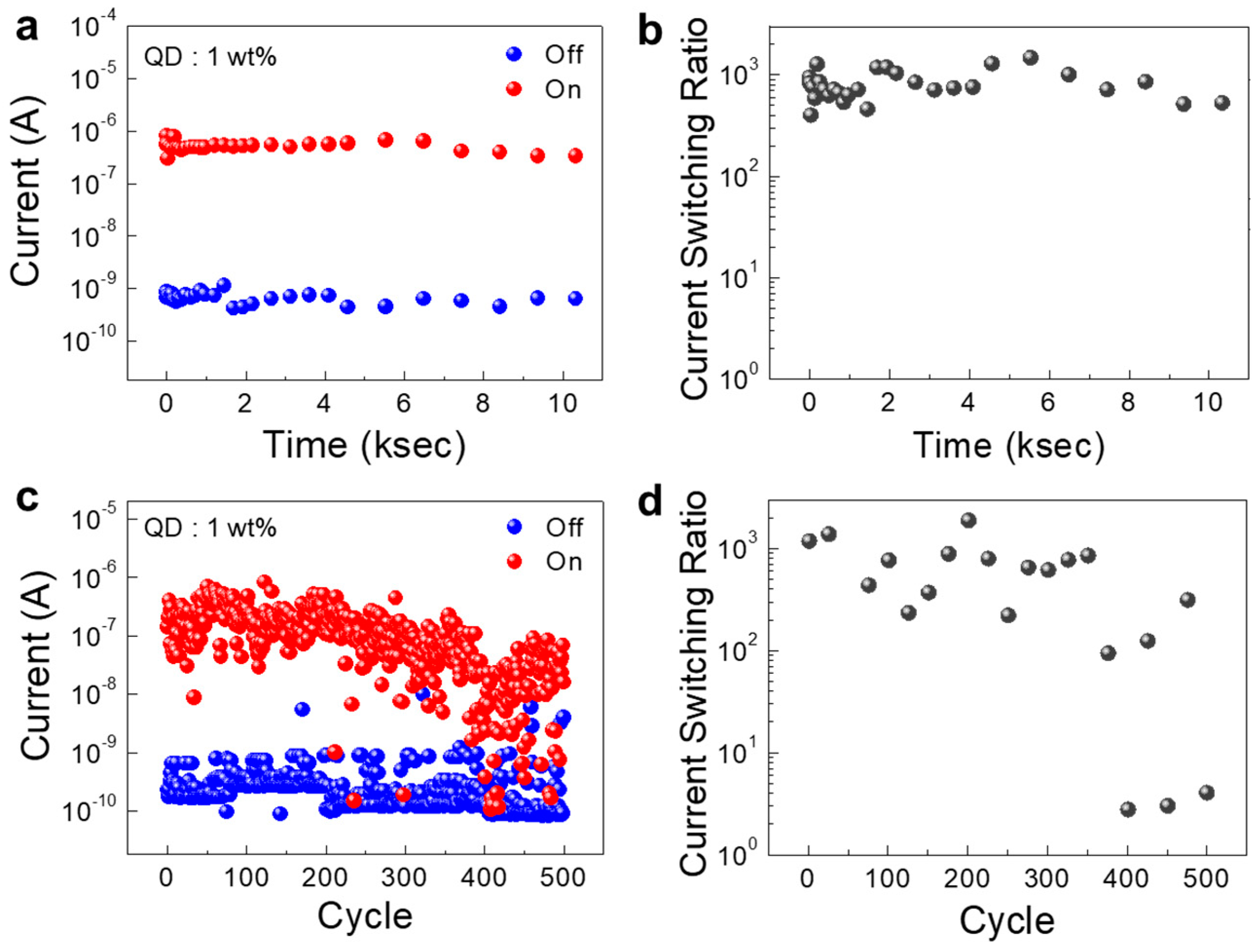

3.3. Operation Stability of CdSe/ZnS QD-PMMA Memristors

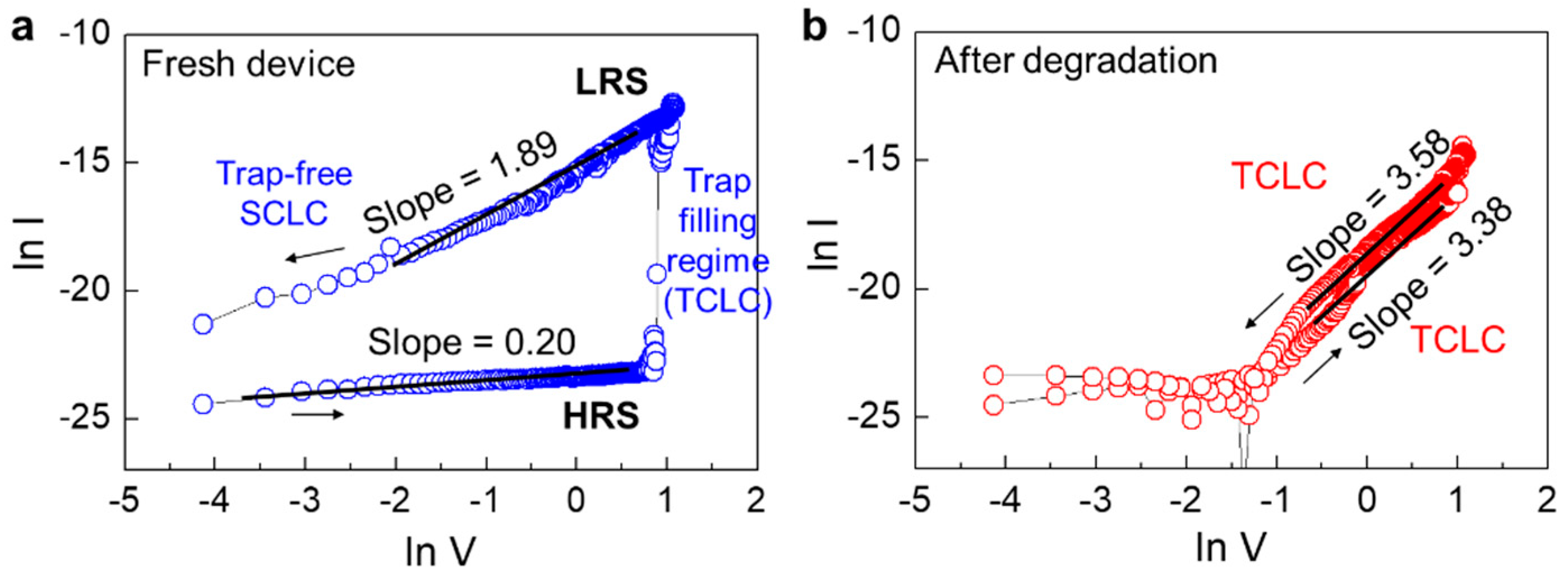

3.4. Degradation Mechanisms

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Conflicts of Interest

References

- Jeong, D.S.; Kim, I.; Ziegler, M.; Kohlstedt, H. Towards artificial neurons and synapses: A materials point of view. RSC Adv. 2013, 3, 3169–3183. [Google Scholar] [CrossRef]

- Hu, S.G.; Liu, Y.; Liu, Z.; Chen, T.P.; Wang, J.J.; Yu, Q.; Deng, L.J.; Yin, Y.; Hosaka, S. Associative memory realized by a reconfigurable memristive Hopfield neural network. Nat. Commun. 2015, 6, 7522. [Google Scholar] [CrossRef] [Green Version]

- Pi, S.; Li, C.; Jiang, H.; Xia, W.; Xin, H.; Yang, J.J.; Xia, Q. Memristor crossbar arrays with 6-nm half-pitch and 2-nm critical dimension. Nat. Nanotechnol. 2019, 14, 35–39. [Google Scholar] [CrossRef] [PubMed]

- Ielmini, D.; Wong, H.S.P. In-memory computing with resistive switching devices. Nat. Electron. 2018, 1, 333–343. [Google Scholar] [CrossRef]

- Sheng, X.; Graves, C.E.; Kumar, S.; Li, X.; Buchanan, B.; Zheng, L.; Lam, S.; Li, C.; Strachan, J.P. Low-Conductance and Multilevel CMOS-Integrated Nanoscale Oxide Memristors. Adv. Electron. Mater. 2019, 5, 1800876. [Google Scholar] [CrossRef]

- Jang, B.C.; Nam, Y.; Koo, B.J.; Choi, J.; Im, S.G.; Park, S.-H.K.; Choi, S.-Y. Memristive Logic-in-Memory Integrated Circuits for Energy-Efficient Flexible Electronics. Adv. Funct. Mater. 2018, 28, 1704725. [Google Scholar] [CrossRef]

- Lipatov, A.; Li, T.; Vorobeva, N.S.; Sinitskii, A.; Gruverman, A. Nanodomain Engineering for Programmable Ferroelectric Devices. Nano Lett. 2019, 19, 3194–3198. [Google Scholar] [CrossRef]

- Krestinskaya, O.; Ibrayev, T.; James, A.P. Hierarchical Temporal Memory Features with Memristor Logic Circuits for Pattern Recognition. IEEE TCAD 2018, 37, 1143–1156. [Google Scholar] [CrossRef]

- Wang, Z.; Joshi, S.; Savel’ev, S.E.; Jiang, H.; Midya, R.; Lin, P.; Hu, M.; Ge, N.; Strachan, J.P.; Li, Z.; et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 2017, 16, 101–108. [Google Scholar] [CrossRef] [Green Version]

- Lanza, M.; Wong, H.-S.P.; Pop, E.; Ielmini, D.; Strukov, D.; Regan, B.C.; Larcher, L.; Villena, M.A.; Yang, J.J.; Goux, L.; et al. Recommended methods to study resistive switching devices. Adv. Elect. Mater. 2019, 5, 1800143. [Google Scholar] [CrossRef] [Green Version]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef] [PubMed]

- Sharma, P.; Zhang, Q.; Sando, D.; Lei, C.H.; Liu, Y.; Li, J.; Nagarajan, V.; Seidel, J. Nonvolatile ferroelectric domain wall memory. Sci. Adv. 2017, 3, e1700512. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Kent, A.D.; Worledge, D.C. A new spin on magnetic memories. Nat. Nanotechnol. 2015, 10, 187–191. [Google Scholar] [CrossRef]

- Wuttig, M.; Bhaskaran, H.; Taubner, T. Phase-change materials for non-volatile photonic applications. Nat. Photonics 2017, 11, 465–476. [Google Scholar] [CrossRef]

- Wu, C.; Kim, T.W.; Choi, H.Y.; Strukov, D.B.; Yang, J.J. Flexible three-dimensional artificial synapse networks with correlated learning and trainable memory capability. Nat. Commun. 2017, 8, 752. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- van de Burgt, Y.; Melianas, A.; Keene, S.T.; Malliaras, G.; Salleo, A. Organic electronics for neuromorphic computing. Nat. Electron. 2018, 1, 386–397. [Google Scholar] [CrossRef]

- Son, D.I.; Kim, T.W.; Shim, J.H.; Jung, J.H.; Lee, D.U.; Lee, J.M.; Park, W.I.; Choi, W.K. Flexible Organic Bistable Devices Based on Graphene Embedded in an Insulating Poly(methyl methacrylate) Polymer Layer. Nano Lett. 2010, 10, 2441–2447. [Google Scholar] [CrossRef]

- Sun, Y.; Wen, D.; Bai, X.; Lu, J.; Ai, C. Ternary Resistance Switching Memory Behavior Based on Graphene Oxide Embedded in a Polystyrene Polymer Layer. Sci. Rep. 2017, 7, 3938. [Google Scholar] [CrossRef]

- Li, X.; Zhao, Y.-B.; Fan, F.; Levina, L.; Liu, M.; Quintero-Bermudez, R.; Gong, X.; Quan, L.N.; Fan, J.; Yang, Z.; et al. Bright colloidal quantum dot light-emitting diodes enabled by efficient chlorination. Nat. Photonics 2018, 12, 159–164. [Google Scholar] [CrossRef]

- Ma, Z.; Ooi, P.C.; Li, F.; Yun, D.Y.; Kim, T.W. Electrical Bistabilities and Conduction Mechanisms of Nonvolatile Memories Based on a Polymethylsilsesquioxane Insulating Layer Containing CdSe/ZnS Quantum Dots. J. Electron. Mater. 2015, 44, 3962–3966. [Google Scholar] [CrossRef]

- Nayak, D.; Choudhary, R.B. Augmented optical and electrical properties of PMMA-ZnS nanocomposites as emissive layer for OLED applications. Opt. Mater. 2019, 91, 470–481. [Google Scholar] [CrossRef]

- Koo, B.M.; Sung, S.; Wu, C.; Song, J.-W.; Kim, T.W. Flexible organic synaptic device based on poly (methyl methacrylate):CdSe/CdZnS quantum-dot nanocomposites. Sci. Rep. 2019, 9, 9755. [Google Scholar] [CrossRef]

- Zhou, Z.; Mao, H.; Wang, X.; Sun, T.; Chang, Q.; Chen, Y.; Xiu, F.; Liu, Z.; Liu, J.; Huang, W. Transient and flexible polymer memristors utilizing full-solution processed polymer nanocomposites. Nanoscale 2018, 10, 14824–14829. [Google Scholar] [CrossRef]

- Son, D.-I.; Park, D.-H.; Ie, S.-Y.; Choi, W.-K.; Choi, J.-W.; Li, F.; Kim, T.-W. Single active-layer structured dual-function devices using hybrid polymer–quantum dots. Nanotechnology 2008, 19, 395201. [Google Scholar] [CrossRef] [PubMed]

- Kim, D.H.; Wu, C.; Park, D.H.; Kim, W.K.; Seo, H.W.; Kim, S.W.; Kim, T.W. Flexible Memristive Devices Based on InP/ZnSe/ZnS Core–Multishell Quantum Dot Nanocomposites. ACS Appl. Mater. Interfaces 2018, 10, 14843–14849. [Google Scholar] [CrossRef] [PubMed]

- Alibart, F.; Zamanidoost, E.; Strukov, D.B. Pattern classification by memristive crossbar circuits using ex situ and in situ training. Nat. Commun. 2013, 4, 2072. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Kim, D.H.; Kim, W.K.; Woo, S.J.; Wu, C.; Kim, T.W. Highly-reproducible nonvolatile memristive devices based on polyvinylpyrrolidone: Graphene quantum-dot nanocomposites. Org. Electron. 2017, 51, 156–161. [Google Scholar] [CrossRef]

- Shim, J.H.; Jung, J.H.; Lee, M.H.; Kim, T.W.; Son, D.I.; Han, A.N.; Kim, S.W. Memory mechanisms of nonvolatile organic bistable devices based on colloidal CuInS2/ZnS core–shell quantum dot—Poly(N-vinylcarbazole) nanocomposites. Org. Electron. 2011, 12, 1566–1570. [Google Scholar] [CrossRef]

- Ko, S.H.; Yoo, C.H.; Kim, T.W. Electrical Bistabilities and Memory Stabilities of Organic Bistable Devices Utilizing C60Molecules Embedded in a Polymethyl Methacylate Matrix with an Al2O3 Blocking Layer. J. Electrochem. Soc. 2012, 159, G93–G96. [Google Scholar] [CrossRef]

- Son, D.I.; Park, D.H.; Choi, W.K.; Cho, S.H.; Kim, W.T.; Kim, T.W. Carrier transport in flexible organic bistable devices of ZnO nanoparticles embedded in an insulating poly(methyl methacrylate) polymer layer. Nanotechnology 2009, 20, 195203. [Google Scholar] [CrossRef]

- Ling, Q.-D.; Liaw, D.-J.; Zhu, C.; Chan, D.S.-H.; Kang, E.-T.; Neoh, K.-G. Polymer electronic memories: Materials, devices and mechanisms. Prog. Polym. Sci. 2008, 33, 917–978. [Google Scholar] [CrossRef]

- Voznyy, O.; Thon, S.M.; Ip, A.H.; Sargent, E.H. Dynamic Trap Formation and Elimination in Colloidal Quantum Dots. J. Phys. Chem. Lett. 2013, 4, 987–992. [Google Scholar] [CrossRef] [PubMed]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, M.; Oh, S.; Song, S.; Kim, J.; Kim, Y.-H. Solution-Processed Memristor Devices Using a Colloidal Quantum Dot-Polymer Composite. Appl. Sci. 2021, 11, 5020. https://doi.org/10.3390/app11115020

Kim M, Oh S, Song S, Kim J, Kim Y-H. Solution-Processed Memristor Devices Using a Colloidal Quantum Dot-Polymer Composite. Applied Sciences. 2021; 11(11):5020. https://doi.org/10.3390/app11115020

Chicago/Turabian StyleKim, Minho, Seongkeun Oh, Seungho Song, Jiwan Kim, and Yong-Hoon Kim. 2021. "Solution-Processed Memristor Devices Using a Colloidal Quantum Dot-Polymer Composite" Applied Sciences 11, no. 11: 5020. https://doi.org/10.3390/app11115020