Architecture and Process Integration Overview of 3D NAND Flash Technologies

Abstract

:1. Introduction

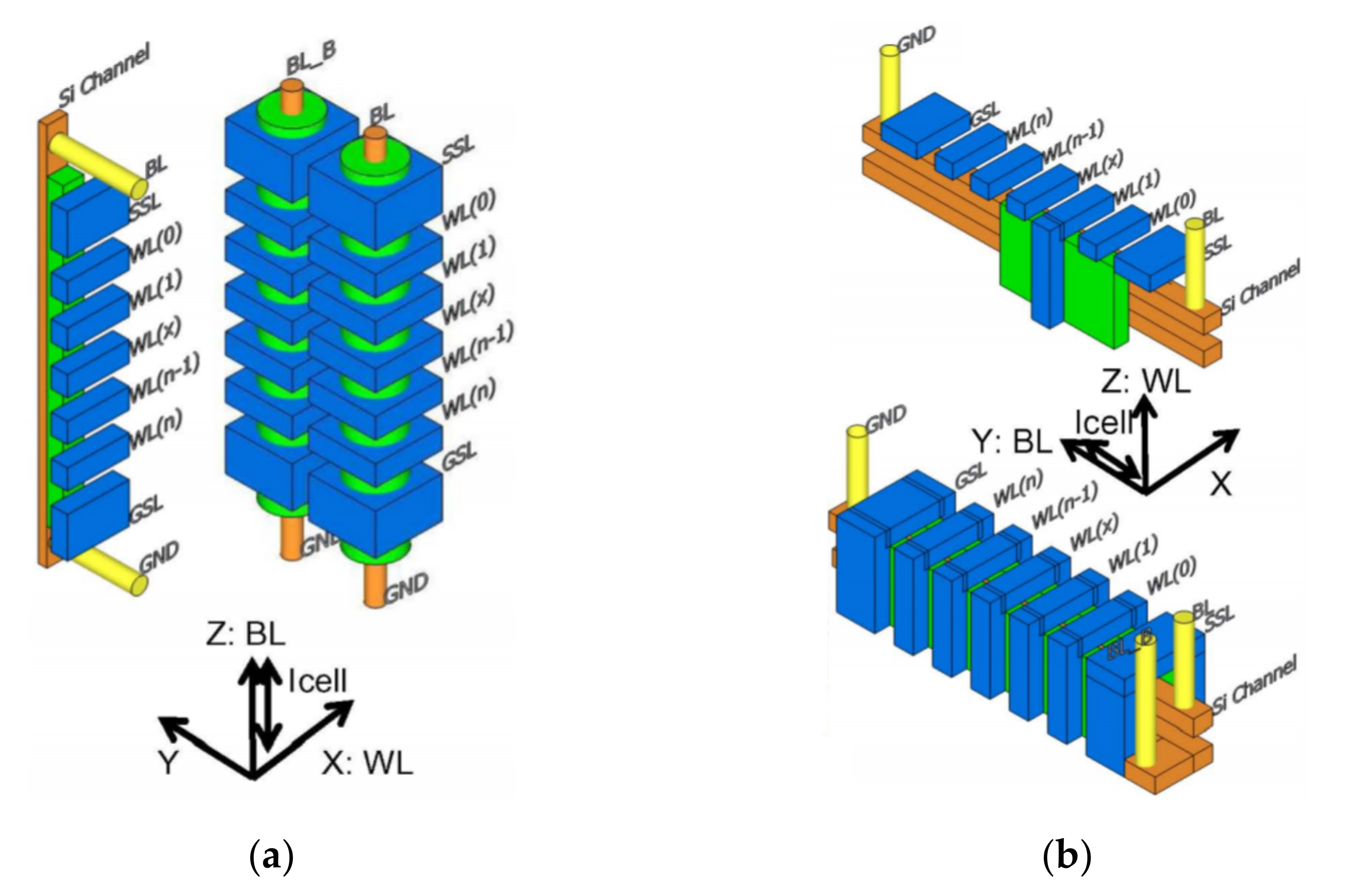

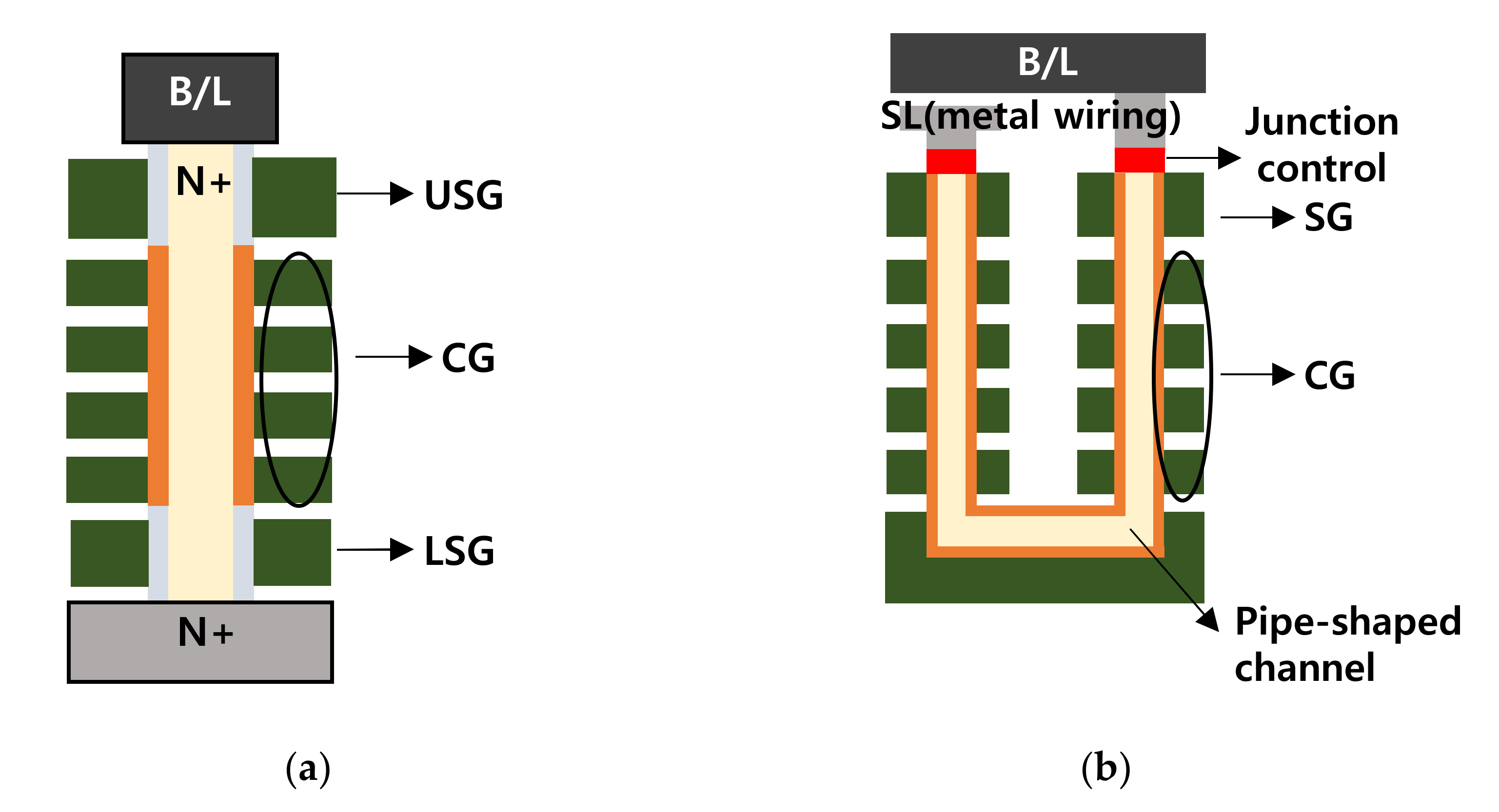

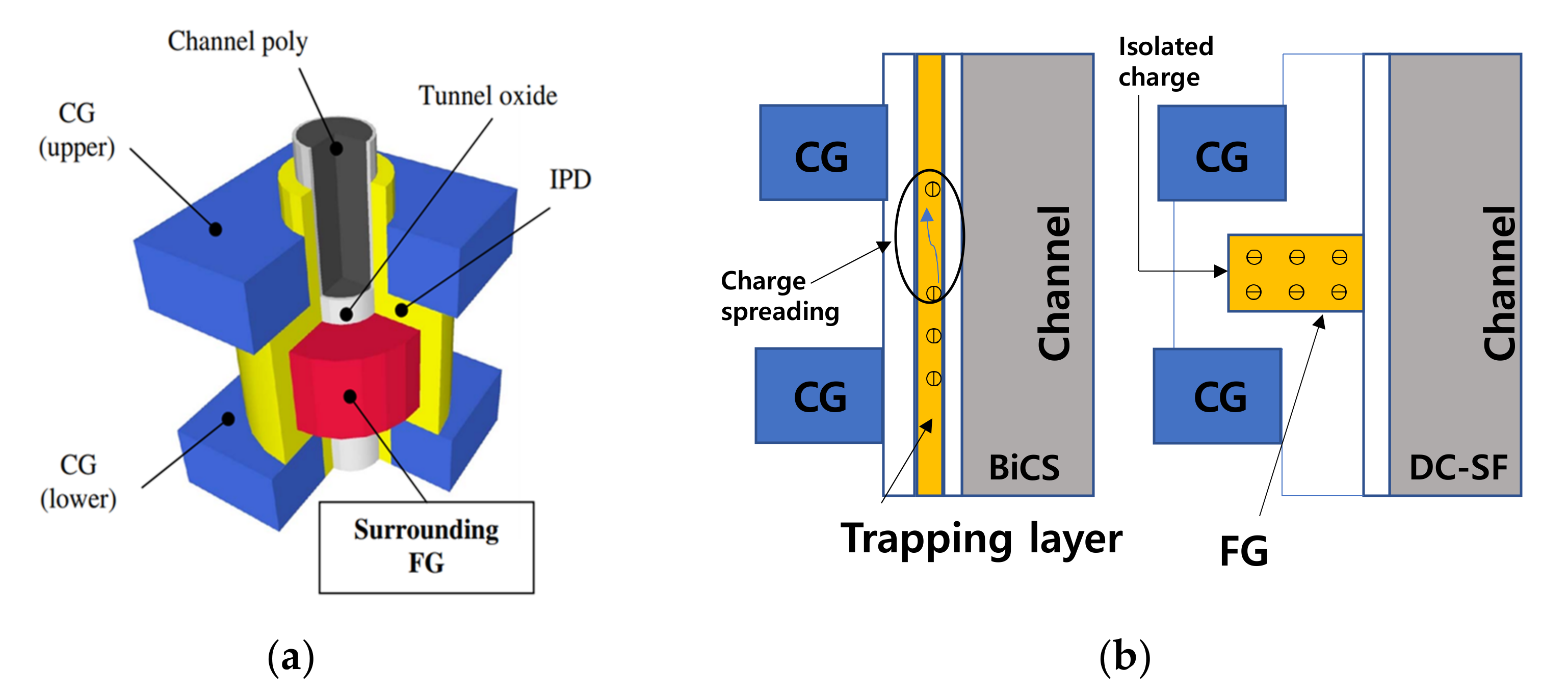

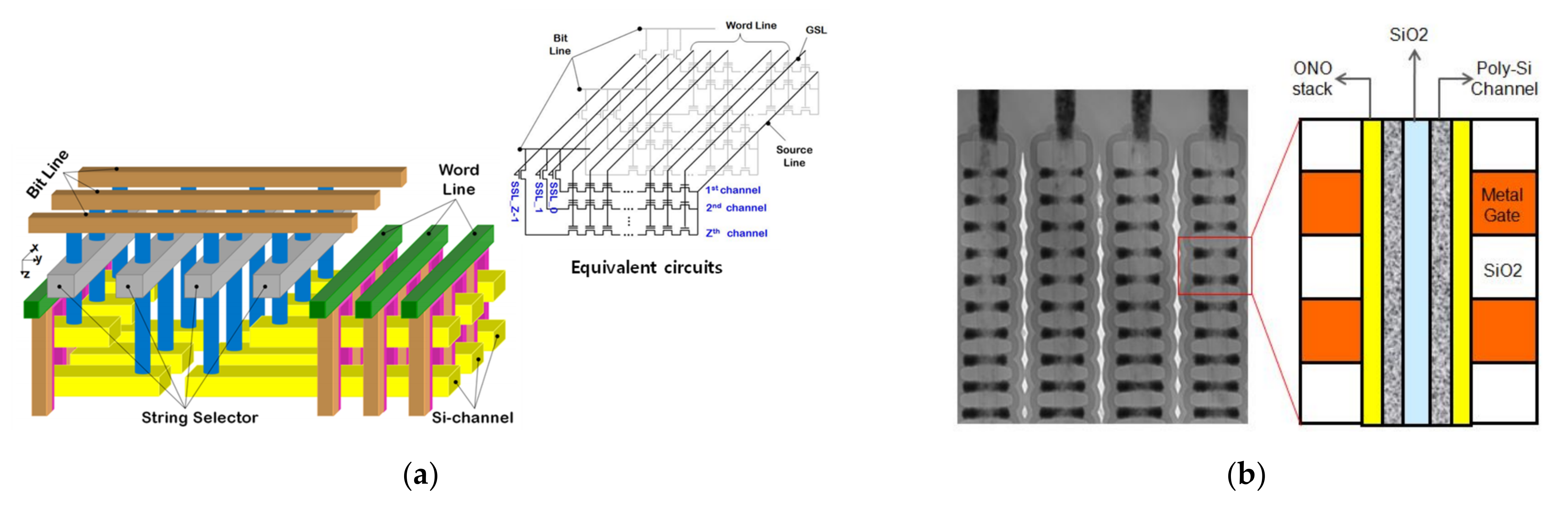

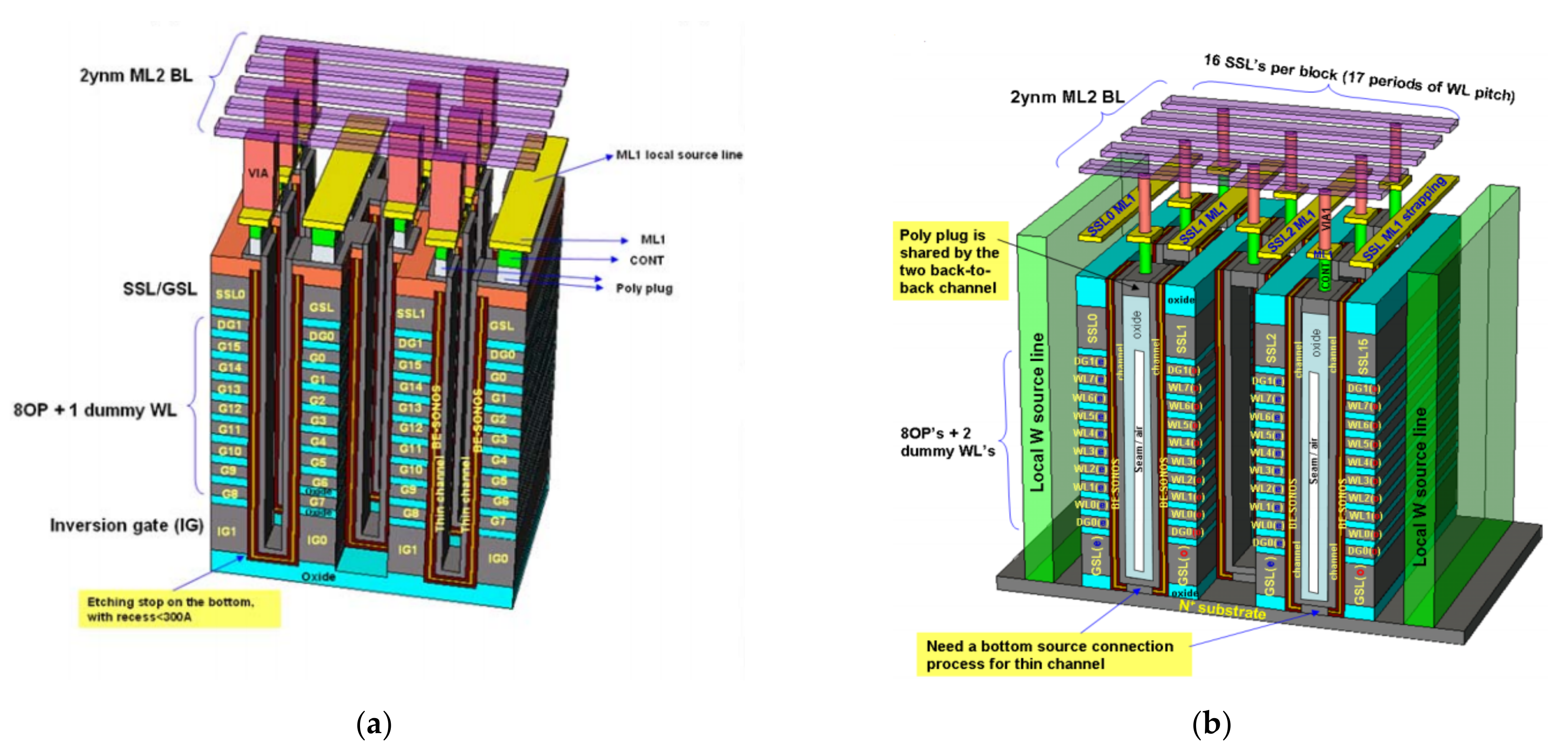

2. Three-Dimensional NAND Flash Architectures

3. Fabrication Methods of 3D NAND Flash

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Komori, Y.; Kido, M.; Kito, M.; Katsumata, R.; Fukuzumi, Y.; Tanaka, H.; Nagata, Y.; Ishiduki, M.; Aochi, H.; Nitayama, A. Disturbless flash memory due to high boost efficiency on BiCS structure and optimal memory film stack for ultra high density storage device. In Proceedings of the 2008 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 851–854. [Google Scholar]

- Katsumata, R.; Kito, M.; Fukuzumi, Y.; Kido, M.; Tanaka, H.; Komori, Y.; Ishiduki, M.; Matsunami, J.; Fujiwara, T.; Nagata, Y.; et al. Pipe-shaped BiCS flash memory with 16 stacked layers and multi-level-cell operation for ultra high density storage devices. In Proceedings of the 2009 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2009; pp. 136–137. [Google Scholar]

- Sakuma, K.; Kusai, H.; Fujii, S.; Koyama, M. Highly Scalable Horizontal Channel 3-D NAND Memory Excellent in Compatibility with Conventional Fabrication Technology. IEEE Electron. Device Lett. 2013, 34, 1142–1144. [Google Scholar] [CrossRef]

- Jang, J.; Kim, H.-S.; Cho, W.; Cho, H.; Kim, J.; Shim, S.I.; Jang, Y.; Jeong, J.-H.; Son, B.-K.; Kim, D.W.; et al. Vertical cell array using TCAT (Terabit Cell Array Transistor) technology for ultra high density NAND flash memory. In Proceedings of the 2009 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2009; pp. 192–193. [Google Scholar]

- Kim, J.; Hong, A.J.; Kim, S.M.; Song, E.B.; Park, J.H.; Han, J.; Choi, S.; Jang, D.; Moon, J.-T.; Wang, K.L. Novel Vertical-Stacked-Array-Transistor (VSAT) for ultra-high-density and cost-effective NAND flash memory devices and SSD (Solid State Drive). In Proceedings of the 2009 Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009; pp. 186–187. [Google Scholar]

- Kim, W.; Choi, S.; Sung, J.; Lee, T.; Park, C.; Ko, H.; Jung, J.; Yoo, I.; Park, Y. Multi-layered vertical gate NAND flash overcoming stacking limit for terabit density storage. In Proceedings of the 2009 Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009; pp. 188–189. [Google Scholar]

- Park, K.-T.; Nam, S.; Kim, D.; Kwak, P.; Lee, D.; Choi, Y.-H.; Choi, M.-H.; Kwak, D.-H.; Kim, D.-H.; Kim, M.-S.; et al. Three-Dimensional 128 Gb MLC Vertical nand Flash Memory With 24-WL Stacked Layers and 50 MB/s High-Speed Programming. IEEE J. Solid State Circuits 2015, 50, 204–213. [Google Scholar] [CrossRef]

- Whang, S.; Lee, K.; Shin, D.; Kim, B.Y.; Kim, M.; Bin, J.; Han, J.; Kim, S.; Lee, B.; Jung, Y.; et al. Novel 3-dimensional Dual Control-gate with Surrounding Floating-gate (DC-SF) NAND flash cell for 1Tb file storage application. In Proceedings of the 2010 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010; pp. 29.7.1–29.7.4. [Google Scholar]

- Choi, E.-S.; Yoo, H.-S.; Joo, H.-S.; Cho, G.-S.; Park, S.-K.; Lee, S.-K. A Novel 3D Cell Array Architecture for Terra-bit NAND Flash Memory. In Proceedings of the IEEE International Memory Workshop (IMW), Monterey, CA, USA, 22–25 May 2011; pp. 1–4. [Google Scholar]

- Choi, E.-S.; Park, S.-K. Device considerations for high density and highly reliable 3D NAND flash cell in near future. In Proceedings of the 2012 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 10–13 December 2012; pp. 9.4.1–9.4.4. [Google Scholar]

- Noh, Y.; Ahn, Y.; Yoo, H.; Han, B.; Chung, S.; Shim, K.; Lee, K.; Kwak, S.; Shin, S.; Choi, I.; et al. A New Metal Control Gate Last process (MCGL process) for high performance DC-SF (Dual Control gate with Surrounding Floating gate) 3D NAND flash memory. In Proceedings of the 2012 Symposium on VLSI Technology, Honolulu, HI, USA, 12–14 June 2012; pp. 19–20. [Google Scholar]

- Lue, H.-T.; Hsu, T.-H.; Hsiao, Y.-H.; Hong, S.P.; Wu, M.T.; Hsu, F.H.; Lien, N.Z.; Wang, S.-Y.; Hsieh, J.-Y.; Yang, L.-W.; et al. A highly scalable 8-layer 3D vertical-gate (VG) TFT NAND Flash using junction-free buried channel BE-SONOS device. In Proceedings of the 2010 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; pp. 131–132. [Google Scholar]

- Hung, C.-H.; Lue, H.-T.; Chang, K.-P.; Chen, C.-P.; Hsiao, Y.-H.; Chen, S.-H.; Shih, Y.-H.; Hsieh, K.-Y.; Yang, M.; Lee, J.; et al. A highly scalable vertical gate (VG) 3D NAND Flash with robust program disturb immunity using a novel PN diode decoding structure. In Proceedings of the 2011 Symposium on VLSI Technology, Kyoto, Japan, 14–16 June 2011; pp. 68–69. [Google Scholar]

- Chang, K.-P.; Lue, H.-T.; Chen, C.-P.; Chen, C.-F.; Chen, Y.-R.; Hsiao, Y.-H.; Hsieh, C.-C.; Shih, Y.-H.; Yang, T.; Chen, K.-C.; et al. Memory Architecture of 3D Vertical Gate (3DVG) NAND Flash Using Plural Island-Gate SSL Decoding Method and Study of It’s Program Inhibit Characteristics. In Proceedings of the IEEE International Memory Workshop (IMW), Milan, Italy, 20–23 May 2012; pp. 1–4. [Google Scholar]

- Chen, S.H.; Lue, H.T.; Shih, Y.H.; Chen, C.F.; Hsu, T.H.; Chen, Y.R.; Hsiao, Y.H.; Huang, S.C.; Chang, K.P.; Hsieh, C.C.; et al. A highly scalable 8-layer Vertical Gate 3D NAND with split-page bit line layout and efficient binary-sum MiLC (Minimal Incremental Layer Cost) staircase contacts. In Proceedings of the 2012 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 10–13 December 2012; pp. 2.3.1–2.3.4. [Google Scholar]

- Lue, H.-T.; Du, P.-Y.; Chen, W.-C.; Yeh, T.-H.; Chang, K.-P.; Hsiao, Y.-H.; Shih, Y.-H.; Hung, C.-H.; Lu, C.-Y. A novel dual-channel 3D NAND flash featuring both N-channel and P-channel NAND characteristics for bit-alterable Flash memory and a new opportunity in sensing the stored charge in the WL space. In Proceedings of the 2013 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 9–11 December 2013; pp. 3.7.1–3.7.4. [Google Scholar]

- Yun, J.-G.; Kim, G.; Lee, J.-E.; Kim, Y.; Shim, W.B.; Lee, J.-H.; Shin, H.; Lee, J.D.; Park, B.-G. Single-Crystalline Si STacked ARray (STAR) NAND Flash Memory. IEEE Trans. Electron. Devices 2011, 58, 1006–1014. [Google Scholar]

- Kim, C.; Kim, D.-H.; Jeong, W.; Kim, H.-J.; Park, I.H.; Park, H.-W.; Lee, J.; Park, J.; Ahn, Y.-L.; Lee, J.Y.; et al. A 512-Gb 3-b/Cell 64-Stacked WL 3-D-NAND Flash Memory. IEEE J. Solid State Circuits 2018, 53, 124–133. [Google Scholar] [CrossRef]

- Yamashita, R.; Magia, S.; Higuchi, T.; Yoneya, K.; Yamamura, T.; Mizukoshi, H.; Zaitsu, S.; Yamashita, M.; Toyama, S.; Kamae, N.; et al. A 512 Gb 3b/cell flash memory on 64-word-line-layer BiCS technology. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 196–197. [Google Scholar]

- Kang, D.; Kim, M.; Jeon, S.C.; Jung, W.; Park, J.; Choo, G.; Shim, D.-K.; Kavala, A.; Kim, S.-B.; Kang, K.-M.; et al. A 512 Gb 3-bit/Cell 3D 6th-Generation V-NAND Flash Memory with 82 MB/s Write Throughput and 1.2 Gb/s Interface. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 216–217. [Google Scholar]

- Shibata, N.; Kanda, K.; Shimizu, T.; Nakai, J.; Nagao, O.; Kobayashi, N.; Miakashi, M.; Nagadomi, Y.; Nakano, T.; Kawabe, T.; et al. A 1.33-Tb 4-Bit/Cell 3-D Flash Memory on a 96-Word-Line-Layer Technology. IEEE J. Solid State Circuits 2019, 55, 178–188. [Google Scholar] [CrossRef]

- Cho, J.; Kang, D.C.; Park, J.; Nam, S.-W.; Song, J.-H.; Jung, B.-K.; Lyu, J.; Lee, H.; Kim, W.-T.; Jeon, H.; et al. A 512 Gb 3b/Cell 7th-Generation 3D-NAND Flash Memory with 184 MB/s Write Throughput and 2.0 Gb/s Interface. In Proceedings of the 2021 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 426–427. [Google Scholar]

- Park, J.-W.; Kim, D.; Ok, S.; Park, J.; Kwon, T.; Lee, H.; Lim, S.; Jung, S.-Y.; Choi, H.; Kang, T.; et al. A 176-Stacked 512 Gb 3b/Cell 3D-NAND Flash with 10.8 Gb/mm2 Density with a Peripheral Circuit Under Cell Array Architecture. In Proceedings of the 2021 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 422–423. [Google Scholar]

- Lue, H.-T.; Du, P.-Y.; Chen, W.-C.; Lee, Y.-C.; Hsu, T.-H.; Yeh, T.-H.; Chang, K.-P.; Hsieh, C.-C.; Huang, C.; Lee, G.-R.; et al. A 128 Gb (MLC)/192 Gb (TLC) single-gate vertical channel (SGVC) architecture 3D NAND using only 16 layers with robust read disturb, long-retention and excellent scaling capability. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 19.1.1–19.1.4. [Google Scholar]

- Lue, H.-T.; Chen, S.-H.; Shih, Y.-H.; Hsieh, K.-Y.; Lu, C.-Y. Overview of 3D NAND Flash and progress of vertical gate (VG) architecture. In Proceedings of the IEEE International Conference on Solid-State and Integrated Circuit Technology, Xi’an, China, 29 October–1 November 2012; pp. 1–4. [Google Scholar]

- Du, P.-Y.; Lue, H.-T.; Shih, Y.-H.; Hsieh, K.-Y.; Lu, C.-Y. Overview of 3D NAND Flash and progress of split-page 3D vertical gate (3DVG) NAND architecture. In Proceedings of the IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Guilin, China, 28–31 October 2014; pp. 1–4. [Google Scholar]

- Nitayama, A.; Aochi, H. Bit Cost Scalable (BiCS) technology for future ultra high density storage memories. In Proceedings of the 2013 Symposium on VLSI Technology, Kyoto, Japan, 11–13 June 2013; pp. 60–61. [Google Scholar]

- Fukuzumi, Y.; Katsumata, R.; Kito, M.; Kido, M.; Sato, M.; Tanaka, H.; Nagata, Y.; Matsuoka, Y.; Iwata, Y.; Aochi, H.; et al. Optimal Integration and Characteristics of Vertical Array Devices for Ultra-High Density, Bit-Cost Scalable Flash Memory. In Proceedings of the 2007 IEEE International Conference on Electron Devices Meeting (IEDM), Washington, DC, USA, 10–12 December 2007; pp. 449–452. [Google Scholar]

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y.; et al. Bit Cost Scalable Technology with Punch and Plug Process for Ultra High Density Flash Memory. In Proceedings of the 2007 Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 14–15. [Google Scholar]

- Aochi, H. BiCS Flash as a Future 3D Non-Volatile Memory Technology for Ultra High Density Storage Devices. In Proceedings of the IEEE International Memory Workshop (IMW), Monterey, CA, USA, 10–14 May 2009; pp. 1–2. [Google Scholar]

- Ishiduki, M.; Fukuzumi, Y.; Katsumata, R.; Kito, M.; Kido, M.; Tanaka, H.; Komori, Y.; Nagata, Y.; Fujiwara, T.; Maeda, T.; et al. Optimal device structure for Pipe-shaped BiCS Flash memory for ultra high density storage device with excellent performance and reliability. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 27.3.1–27.3.4. [Google Scholar]

- Maeda, T.; Itagaki, K.; Hishida, T.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Kido, M.; Tanaka, H.; Komori, Y.; Ishiduki, M.; et al. Multi-stacked 1G cell/layer Pipe-shaped BiCS flash memory. In Proceedings of the 2009 Symposium on VLSI Circuits, Kyoto, Japan, 16–18 August 2009; pp. 22–23. [Google Scholar]

- Micheloni, R.; Crippa, L.; Zambelli, C.; Olivo, P. Architectural and Integration Options for 3D NAND Flash Memories. Computers 2017, 6, 27. [Google Scholar] [CrossRef]

- Kim, J.; Hong, A.J.; Kim, S.M.; Shin, K.-S.; Song, E.B.; Hwang, Y.; Xiu, F.; Galatsis, K.; Chui, C.O.; Candler, R.N.; et al. A stacked memory device on logic 3D technology for ultra-high-density data storage. Nanotechnology 2011, 22, 254006. [Google Scholar] [CrossRef]

- Kim, J.; Hong, A.J.; Ogawa, M.; Ma, S.; Song, E.B.; Lin, Y.-S.; Han, J.; Chung, U.-I.; Wang, K.L. Novel 3-D structure for ultra high density flash memory with VRAT (Vertical-Recess-Array-Transistor) and PIPE (Planarized Integration on the same PlanE). In Proceedings of the 2008 Symposium on VLSI Technology, Honolulu, HI, USA, 17–19 June 2008; pp. 122–123. [Google Scholar]

- Chen, C.-P.; Lue, H.-T.; Chang, K.-P.; Hsiao, Y.-H.; Hsieh, C.-C.; Chen, S.-H.; Shih, Y.-H.; Hsieh, K.-Y.; Yang, T.; Chen, K.C.; et al. A highly pitch scalable 3D vertical gate (VG) NAND flash decoded by a novel self-aligned independently controlled double gate (IDG) string select transistor (SSL). In Proceedings of the 2012 Symposium on VLSI Technology, Honolulu, HI, USA, 12–14 June 2012; pp. 91–92. [Google Scholar]

- Lue, H.-T.; Wang, S.-Y.; Lai, E.-K.; Shih, Y.-H.; Lai, S.-C.; Yang, L.-W.; Chen, K.-C.; Ku, J.; Hsieh, K.-Y.; Liu, R.; et al. BE-SONOS: A bandgap engineered SONOS with excellent performance and reliability. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5 December 2005; pp. 547–550. [Google Scholar]

- Lue, H.-T.; Hsu, T.-H.; Wu, C.-J.; Chen, W.-C.; Yeh, T.-H.; Chang, K.-P.; Hsieh, C.-C.; Du, P.-Y.; Hsiao, Y.-H.; Jiang, Y.-W.; et al. A novel double-density, single-gate vertical channel (SGVC) 3D NAND Flash that is tolerant to deep vertical etching CD variation and possesses robust read-disturb immunity. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 3.2.1–3.2.4. [Google Scholar]

- Wu, C.-J.; Lue, H.-T.; Hsu, T.-H.; Hsieh, C.-C.; Chen, W.-C.; Du, P.-Y.; Chiu, C.-J.; Lu, C.-Y. Device Characteristics of Single-Gate Vertical Channel (SGVC) 3D NAND Flash Architecture. In Proceedings of the IEEE International Memory Workshop (IMW), Paris, France, 15–18 May 2016; pp. 1–4. [Google Scholar]

- Lai, S.-C.; Lue, H.-T.; Hsu, T.-H.; Wu, C.-J.; Liang, L.-Y.; Du, P.-Y.; Chiu, C.-J.; Lu, C.-Y. A Bottom-Source Single-Gate Vertical Channel (BS-SGVC) 3D NAND Flash Architecture and Studies of Bottom Source Engineering. In Proceedings of the IEEE International Memory Workshop (IMW), Paris, France, 15–18 May 2016; pp. 1–4. [Google Scholar]

- Chiu, C.-J.; Lue, H.-T.; Hsieh, K.-Y.; Lu, C.-Y. A novel double-density single-gate vertical-channel (SGVC) 3D NAND flash utilizing a flat-channel thin-body device. In Proceedings of the IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Hangzhou, China, 25–28 October 2016; pp. 1–4. [Google Scholar]

- Lue, H.-T.; Chiu, C.-J.; Lu, C.-Y. A novel double-density single-gate vertical-channel (SGVC) 3D NAND flash featuring a flat-channel device with excellent layer uniformity. In Proceedings of the 2016 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), Hsinchu, Taiwan, 25–27 April 2016; pp. 1–4. [Google Scholar]

- Kim, Y.; Yun, J.-G.; Park, S.H.; Kim, W.; Seo, J.Y.; Kang, M.; Ryoo, K.-C.; Oh, J.-H.; Lee, J.-H.; Shin, H.; et al. Three-Dimensional nand Flash Architecture Design Based on Single-Crystalline STacked ARray. IEEE Trans. Electron. Devices 2012, 59, 35–45. [Google Scholar] [CrossRef]

- Lee, C.H.; Choi, K.I.; Cho, M.K.; Song, Y.H.; Park, K.C.; Kim, K. A Novel SONOS structure of SiO2/SiN/Al2O3 with TaN Metal Gate for Multi-Giga Bit Flash Memories. In Proceedings of the 2003 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 8–10 December 2003; pp. 26.5.1–26.5.4. [Google Scholar]

- Cho, W.-S.; Shim, S.I.; Jang, J.; Cho, H.-S.; You, B.-K.; Son, B.-K.; Kim, K.-H.; Shim, J.-J.; Park, C.-M.; Lim, J.-S.; et al. Highly reliable vertical NAND technology with biconcave shaped storage layer and leakage controllable offset structure. In Proceedings of the 2010 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; pp. 173–174. [Google Scholar]

- Park, K.-T.; Byeon, D.-S.; Kim, D.-H. A world’s first product of three-dimensional vertical NAND Flash memory and beyond. In Proceedings of the 2014 14th Annual Non-Volatile Memory Technology Symposium (NVMTS), Jeju Island, Korea, 27–29 October 2014; pp. 1–5. [Google Scholar]

- Jeong, W.; Im, J.-W.; Kim, D.-H.; Nam, S.-W.; Shim, D.-K.; Choi, M.-H.; Yoon, H.-J.; Kim, D.-H.; Kim, Y.-S.; Park, H.-W.; et al. A 128 Gb 3b/cell V-NAND Flash Memory With 1 Gb/s I/O Rate. IEEE J. Solid State Circuits 2016, 51, 204–212. [Google Scholar]

- Kang, D.; Jeong, W.; Kim, C.; Kim, D.-H.; Cho, Y.S.; Kang, K.-T.; Ryu, J.; Kang, K.-M.; Lee, S.; Kim, W.; et al. 256 Gb 3 b/Cell V-nand Flash Memory With 48 Stacked WL Layers. IEEE J. Solid State Circuits 2017, 52, 210–217. [Google Scholar] [CrossRef]

- Lee, S.; Kim, C.; Kim, M.; Joe, S.-M.; Jang, J.; Kim, S.; Lee, K.; Kim, J.; Park, J.; Lee, H.-J.; et al. A 1 Tb 4b/cell 64-stacked-WL 3D NAND flash memory with 12 MB/s program throughput. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 340–341. [Google Scholar]

- Ielmini, D.; Ambrogio, S. Emerging neuromorphic devices. Nanotechnology 2019, 31, 092001. [Google Scholar] [CrossRef] [PubMed]

- Kim, H.; Nili, H.; Mahmoodi, M.; Strukov, D. 4K-memristor analog-grade passive crossbar circuit. arXiv 2019, arXiv:1906.12045. [Google Scholar]

- Qi, M.; Cao, S.; Yang, L.; You, Q.; Shi, L.; Wu, Z. Uniform multilevel switching of graphene oxide-based RRAM achieved by embedding with gold nanoparticles for image pattern recognition. Appl. Phys. Lett. 2020, 116, 163503. [Google Scholar] [CrossRef]

- Chen, J.; Wu, H.; Gao, B.; Tang, J.; Hu, X.S.; Qian, H. A parallel multibit programing scheme with high precision for RRAM-based neuromorphic systems. IEEE Trans. Electron. Devices 2020, 67, 2213–2217. [Google Scholar] [CrossRef]

- Kim, T.-H.; Nili, H.; Kim, M.-H.; Min, K.K.; Park, B.-G.; Kim, H. Reset-voltage-dependent precise tuning operation of TiOx/Al2O3 memristive crossbar array. Appl. Phys. Lett. 2020, 117, 152103. [Google Scholar] [CrossRef]

- Kim, S.; Kim, T.-H.; Kim, H.; Park, B.-G. Current suppressed self-compliance characteristics of oxygen rich TiOy inserted Al2O3/TiOx based RRAM. Appl. Phys. Lett. 2020, 117, 202106. [Google Scholar] [CrossRef]

- Wang, Y.; Liu, X.; Chen, Y.; Xu, W.; Liang, D.; Gao, F.; Zhang, M.; Samanta, S.; Gong, X.; Lian, X. Manipulation of the electrical behaviors of Cu/MXene/SiO2/W memristor. Appl. Phys. Express 2019, 12, 106504. [Google Scholar] [CrossRef]

- Kim, T.-H.; Lee, J.; Kim, S.; Park, J.; Park, B.-G.; Kim, H. 3-bit multilevel operation with accurate programming scheme in TiOx/Al2O3 memristor crossbar array for quantized neuromorphic system. Nanotechnology 2021, 32, 295201. [Google Scholar] [CrossRef] [PubMed]

- Jang, J.T.; Min, J.; Hwang, Y.; Choi, S.-J.; Kim, D.M.; Kim, H.; Kim, D.H. Digital and analog switching characteristics of InGaZnO memristor depending on top electrode material for neuromorphic system. IEEE Access 2020, 8, 192304–192311. [Google Scholar] [CrossRef]

- Mahmoodi, M.; Kim, H.; Fahimi, Z.; Nili, H.; Sedov, L.; Polishchuk, V.; Strukov, D. An Analog Neuro-Optimizer with Adaptable Annealing Based on 64 × 64 0T1R Crossbar Circuit. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 14.7.1–14.7.4. [Google Scholar]

- Joshi, V.; Le Gallo, M.; Haefeli, S.; Boybat, I.; Nandakumar, S.R.; Piveteau, C.; Dazzi, M.; Rajendran, B.; Sebastian, A.; Eleftheriou, E. Accurate deep neural network inference using computational phase-change memory. Nat. Commun. 2020, 11, 2473. [Google Scholar] [CrossRef] [PubMed]

- Saito, Y.; Kolobov, A.V.; Fons, P.; Mitrofanov, K.V.; Makino, K.; Tominaga, J.; Robertson, J. Origin of resistivity contrast in interfacial phase-change memory: The crucial role of Ge/Sb intermixing. Appl. Phys. Lett. 2019, 114, 132102. [Google Scholar] [CrossRef]

- Neumann, C.M.; Okabe, K.L.; Yalon, E.; Grady, R.W.; Wong, H.-S.P.; Pop, E. Engineering thermal and electrical interface properties of phase change memory with monolayer MoS2. Appl. Phys. Lett. 2019, 114, 082103. [Google Scholar] [CrossRef] [Green Version]

- Raeis-Hosseini, N.; Rho, J. Dual-functional nanoscale devices using phase-change materials: A reconfigurable perfect absorber with nonvolatile resistance-change memory characteristics. Appl. Sci. 2019, 9, 564. [Google Scholar] [CrossRef] [Green Version]

- Yin, Q.; Chen, L. Crystallization behavior and electrical characteristics of Ga–Sb thin films for phase change memory. Nanotechnology 2020, 31, 215709. [Google Scholar] [CrossRef] [PubMed]

- Anam, M.K.; Ahn, E.C. Understanding the effect of dry etching on nanoscale phase-change memory. Nanotechnology 2019, 30, 495202. [Google Scholar] [CrossRef] [PubMed]

- Oh, S.; Huang, Z.; Shi, Y.; Kuzum, D. The impact of resistance drift of phase change memory (PCM) synaptic devices on artificial neural network performance. IEEE Electron. Device Lett. 2019, 40, 1325–1328. [Google Scholar] [CrossRef]

- Shin, M.; Min, K.; Shim, H.; Kwon, Y. Investigation on phase-change synapse devices for more gradual switching. J. Semicond. Technol. Sci. 2019, 19, 8–17. [Google Scholar] [CrossRef]

- Kim, H.; Hwang, S.; Park, J.; Yun, S.; Lee, J.-H.; Park, B.-G. Spiking neural network using synaptic transistors and neuron circuits for pattern recognition with noisy images. IEEE Electron. Device Lett. 2018, 39, 630–633. [Google Scholar] [CrossRef]

- Shim, W.; Yu, S. Technological design of 3D NAND-based compute-in-memory architecture for GB-scale deep neural network. IEEE Electron. Device Lett. 2021, 42, 160–163. [Google Scholar] [CrossRef]

- Oh, S.; Kim, C.-H.; Lee, S.; Kim, J.S.; Lee, J.-H. Unsupervised online learning of temporal information in spiking neural network using thin-film transistor-type NOR flash memory devices. Nanotechnology 2019, 30, 435206. [Google Scholar] [CrossRef] [PubMed]

- Kim, H.; Hwang, S.; Park, J.; Park, B.-G. Silicon synaptic transistor for hardware-based spiking neural network and neuromorphic system. Nanotechnology 2017, 28, 405202. [Google Scholar] [CrossRef] [PubMed]

- Hwang, S.; Kim, H.; Park, J.; Kwon, M.-W.; Baek, M.-H.; Lee, J.-J.; Park, B.-G. System-level simulation of hardware spiking neural network based on synaptic transistors and I&F neuron circuits. IEEE Electron. Device Lett. 2018, 39, 1441–1444. [Google Scholar]

- Malavena, G.; Filippi, M.; Spinelli, A.S.; Compagnoni, C.M. Unsupervised learning by spike-timing-dependent plasticity in a mainstream NOR flash memory array—Part I: Cell operation. IEEE Trans. Electron. Devices 2019, 66, 4727–4732. [Google Scholar] [CrossRef]

- Kim, H.; Park, J.; Kwon, M.-W.; Lee, J.-H.; Park, B.-G. Silicon-based floating-body synaptic transistor with frequency dependent short-and long-term memories. IEEE Electron. Device Lett. 2016, 37, 249–252. [Google Scholar] [CrossRef]

- Choi, H.-S.; Kim, H.; Lee, J.-H.; Park, B.-G.; Kim, Y. AND flash array based on charge trap flash for implementation of convolutional neural networks. IEEE Electron. Device Lett. 2020, 41, 1653–1656. [Google Scholar] [CrossRef]

- Kim, S.; Baek, M.-H.; Hwang, S.; Jang, T.; Park, K.; Park, B.-G. A novel vector-matrix multiplication (VMM) architecture based on NAND memory array. J. Semicond. Technol. Sci. 2020, 20, 242–248. [Google Scholar] [CrossRef]

- Lee, S.-T.; Kwon, D.; Kim, H.; Yoo, H.; Lee, J.-H. NAND flash based novel synaptic architecture for highly robust and high-density quantized neural networks with binary neuron activation of (1, 0). IEEE Access 2020, 8, 114330–114339. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, G.H.; Hwang, S.; Yu, J.; Kim, H. Architecture and Process Integration Overview of 3D NAND Flash Technologies. Appl. Sci. 2021, 11, 6703. https://doi.org/10.3390/app11156703

Lee GH, Hwang S, Yu J, Kim H. Architecture and Process Integration Overview of 3D NAND Flash Technologies. Applied Sciences. 2021; 11(15):6703. https://doi.org/10.3390/app11156703

Chicago/Turabian StyleLee, Geun Ho, Sungmin Hwang, Junsu Yu, and Hyungjin Kim. 2021. "Architecture and Process Integration Overview of 3D NAND Flash Technologies" Applied Sciences 11, no. 15: 6703. https://doi.org/10.3390/app11156703

APA StyleLee, G. H., Hwang, S., Yu, J., & Kim, H. (2021). Architecture and Process Integration Overview of 3D NAND Flash Technologies. Applied Sciences, 11(15), 6703. https://doi.org/10.3390/app11156703