1. Introduction

Recent, new technologies, such as fifth-generation wireless networks (5G), artificial intelligence (AI), virtual reality (VR), the Internet of things (IoT), and self-driving cars, require a large bandwidth and fast response time. To support the needs of such new technologies, the core network is evolving from 100 GE to 400 GE and the research and development of 400 Gbps optical transceivers continues to progress [

1]. With increased data consumption, increased bandwidth is required. For this purpose, long-distance optical transceivers that use a variety of modulation methods such as polarization-multiplexing and quadrature phase-shift-keying (PM-QPSK or DP-QPSK), and quadrant amplitude modulation (QAM) [

2] have been developed. However, this modulation method requires an expensive photomultiplier and the corresponding sophisticated technology. A commonly used non-return-to-zero (NRZ) modulation scheme can transmit one bit per symbol. A level-four pulse-amplitude modulation (PAM4) is advantageous because it can transmit two bits per symbol, twice that of the traditional NRZ [

3]. However, the PAM4 scheme has a characteristic lower bit error rate (BER) because it is more noise-sensitive than the NRZ method. Therefore, increased caution is required when designing optical transceivers using PAM4.

The Institute of Electrical and Electronics Engineers(IEEE) 802.3 cd standard document defines the physical layer and associated parameter management of 50 Gbps PAM4 optical transmitters and receivers for 50GBASE(Gb/s PHYs)-FR (far reach, 2 km) and LR (long reach, 10 km) [

4]. However, the specification for the longest-distance transmission, which is 40 km for PAM4 signals, has been proposed for some enterprises but have yet to be established as a standard [

5].

Table 1 shows the existing optical receiver solutions for long-distance transmission. Experiments were conducted using an avalanche photodiode (APD) optical receiver for 40 and 60 km long-distance PAM4 signal transmissions [

6,

7,

8]. However, the method using APD receivers requires additional circuitry to drive the APD and the cost of parts is higher than that of positive-intrinsic-negative photo diode (PIN-PD) receivers. The semiconductor optical amplifier (SOA) is another technology that can be used for long-distance transmissions greater than 40 km [

9,

10]. SOA has been applied to the C form-factor pluggable (CFP), specifically the CFP2 optical transceiver, which is a large form-factor type owing to the high cost of parts, the additional thermoelectric cooler (TEC) control, and its slarge size; however, it can amplify the optical signal to be lower than the APD method to the level of the receiver sensitivity. These existing studies have successfully long-distance transfers but have not experimented with packaged transceiver types. The study in [

11] proposed a method for transmitting long distances using a QSFP28-type transceiver. However, it used a method to amplify signals outside the transceiver by adding the erbium-doped fiber amplifier (EDFA) to the transmission system rather than inside the transceiver.

We designed and implemented the QSFP28 optical transceiver using PAM4. This study makes the following contributions: (1) 50 Gbps high-capacity long-distance transmission, only PIN-PD was used to minimize circuit complexity and was implemented at low cost over traditional approaches. To overcome the limitations of the PIN-PD receiver, the PAM4 signal transmitter output BER was minimized to demonstrate that 40 km transmission is feasible. (2) A hardware and firmware design scheme in which the optical transceiver’s function and performance meet standard specifications is proposed. The optical transceiver manufacturers do not publicly share their methodology or techniques. By implementing optical transceiver using the proposed design scheme, quality can be ensured, and cost and development time can be reduced.

The rest of the paper is organized as follows: In

Section 2, the principle of the PAM4 method and the relevant standard are analyzed for the design of the QSFP28 optical transceiver.

Section 3 proposes the hardware and firmware design scheme of the QSFP28 optical transceiver based on the analyzed requirements.

Section 4 analyzes the test bed construction and test results for performance verification.

Section 5 discusses the conclusions and future studies.

3. Proposed Design Scheme

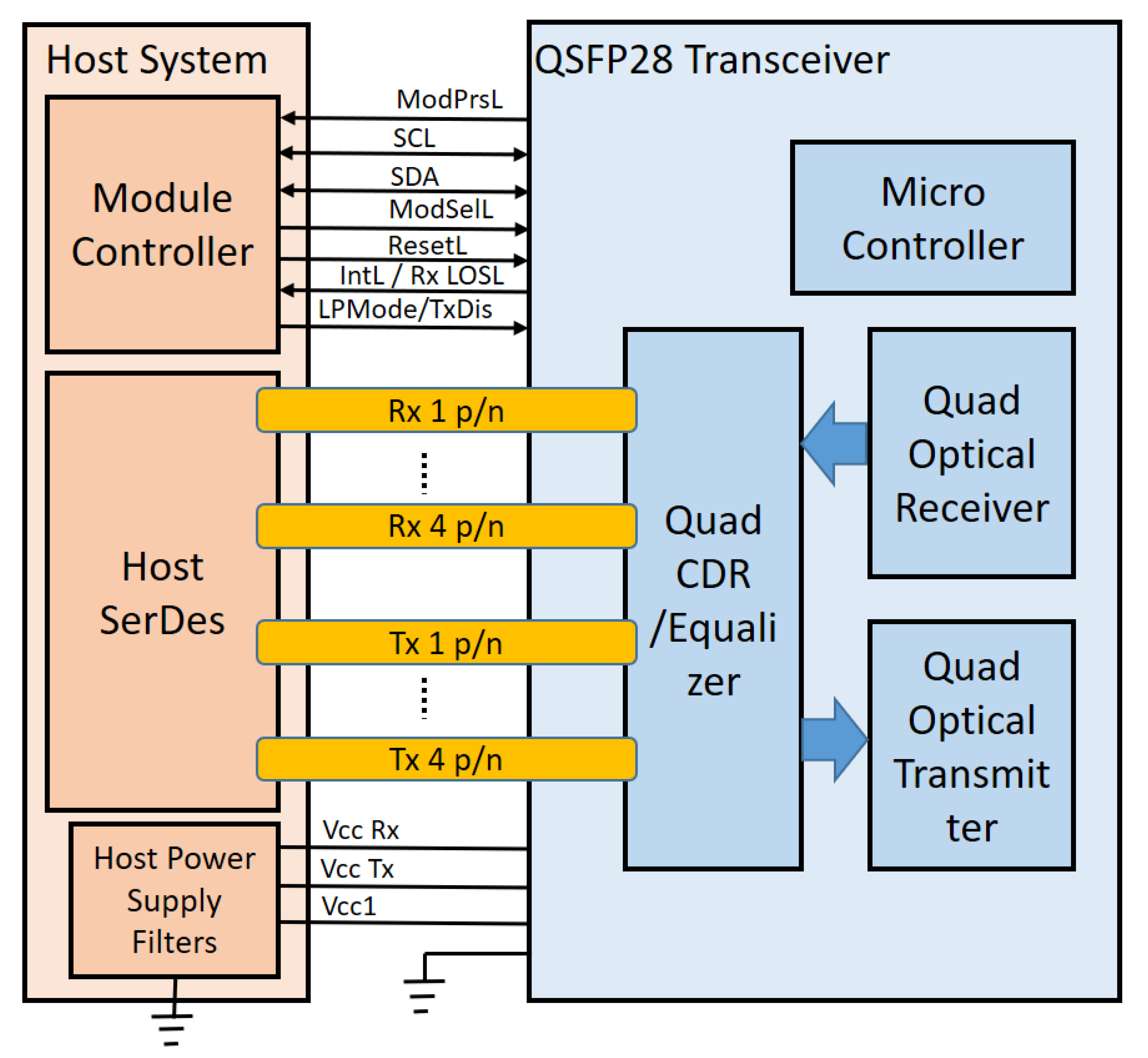

3.1. Hardware Design

Figure 5 shows the complete hardware structure diagram proposed with reference to the standard documentation. The QSFP28 optical transceiver internal hardware of the proposed design scheme consists of PAM4 DSP IC for PAM4 and duplication, electro-absorption-modulated laser (EML)–transmitter optical sub-assemblies (TOSA) for transmission, and PIN-PD receiver optical sub-assemblies (ROSA) for reception. It also consists of a driver IC for driving one TOSA, a TEC controller for controlling optical transmitters wavelengths, and an MCU for overall operation of modules.

The PAM4 DSP IC functions to modulate two 25 Gbps NRZ signals with 50 Gbps PAM4 signals and, vice versa, that is, to convert PAM4 signals to NRZ signals. The EML-TOSA is a 25/28 G single channel TOSA and applies an electro-absorption modulator and distributed feedback laser diode (DFB-LD), monitor photodiode, embedded optical isolator, and TEC to a gold box-type package. The TEC controller is used to control the TEC inside the TOSA. Because the TOSA laser diode has the characteristic that the wavelength varies according to temperature, the internal TEC controls the laser diode to maintain a constant temperature without being affected by external temperature. The linear PIN-PD ROSA for receiving PAM4 optical signals consists of a photodiode of 25 GHz bandwidth and a trans-impedance amplifier (TIA) capable of receiving up to 2.5 mA inputs and is adjustable from 31 to 37 GHz. The MCU controls laser diodes, linear drivers, and linear TIA using a built-in analog-to-digital converter (ADC) and digital-to-analog converter (DAC). The MCU is also responsible for operation of the PAM4 DSP IC and operation of the QSFP28 optical transceiver.

For optical transceivers manufactured with the QSFP28 form-factors, a number of ICs must be integrated in a limited printed circuit board (PCB) area. Therefore, we optimized the PCB design by selecting each IC for the QSFP28 design in consideration of its small size and high-efficiency characteristics. In particular, DC–DC converters for power supply are more than 90% efficient and the inductor is applied with switching converters integrated inside the IC to minimize the area. This can reduce the heat in the power supply and lower the power consumption.

3.2. PCB Design

The circuit design proposed in this study was implemented on a 10-layer PCB to optimize the circuit in a limited area. The parameters that determine high-speed signal loss are the dielectric constant (Dk) and the dissipation factor (Df) for frequency. Although PCB material with less Dk and Df has the advantage of less high-frequency loss, its price is higher. Therefore, an appropriate trade-off design is required considering cost and performance. In this study, we used FR4 substrates, which are primarily used for industrial purposes, and Panasonic MEGTRON6 with relatively lower Dks and lower dielectric losses compared to FR4 substrates. The 25 Gbps NRZ high-speed signal and PAM4 signal transmission lines were placed in the top and bottom planes using the MEGTRON6 substrate, and the remainder was designed with FR4 substrates.

Table 3 shows the PCB layer structures designed by the proposed method and their circuit functionality implemented on each layer.

The design of the transmission line for transmitting 26 giga-baud (GBd) PAM4 signals per channel over the PCB requires a more sophisticated transmission line design than conventional NRZ signals. The PAM4 signals are more susceptible to noise and attenuation than NRZ signals. A signal passing through a transmission line on a PCB designed with differential 100 Ohms results in reflection or radiation of the signal at the point of the characteristic impedance mismatch, thus impacting the signal characteristics. This causes overshoot and undershoot on the signal eye pattern and degrades jitter properties. The main areas where impedance nonconformities occur are IC pads and the flexible PCB assembly. The proposed scheme is used to apply a coplanar waveguide type transmission line on the PCB. The impedance of the area where the transmission line width thickens increases capacitance, and the dielectric substrate thickness below the transmission line decreases capacitance [

18]. The proposed scheme minimizes impedance nonconformity by subtly calculating the impedance characteristics according to the line width, the dielectric thickness, and the gap between the track and the ground (GND) and increases inductance to solve the impedance degradation problem occurring on IC pads on the path through which the signal passes, thereby improving the overall impedance convergence.

3.3. Firmware Design

The QSFP28 optical transceiver firmware design scheme proposed in this study was designed to meet the requirements of standard documents. The DS4830 of Maxim Integrated was used as the MCU for the QSFP28 optical transceiver [

19]. The DS4830 supports optimized control for information monitoring of optical transceivers that meet the SFF-8472 standard. It provides ADC and DAC with 12-bit resolution and I2C slave interface that can operate reliably at a 400 kHz clock speed.

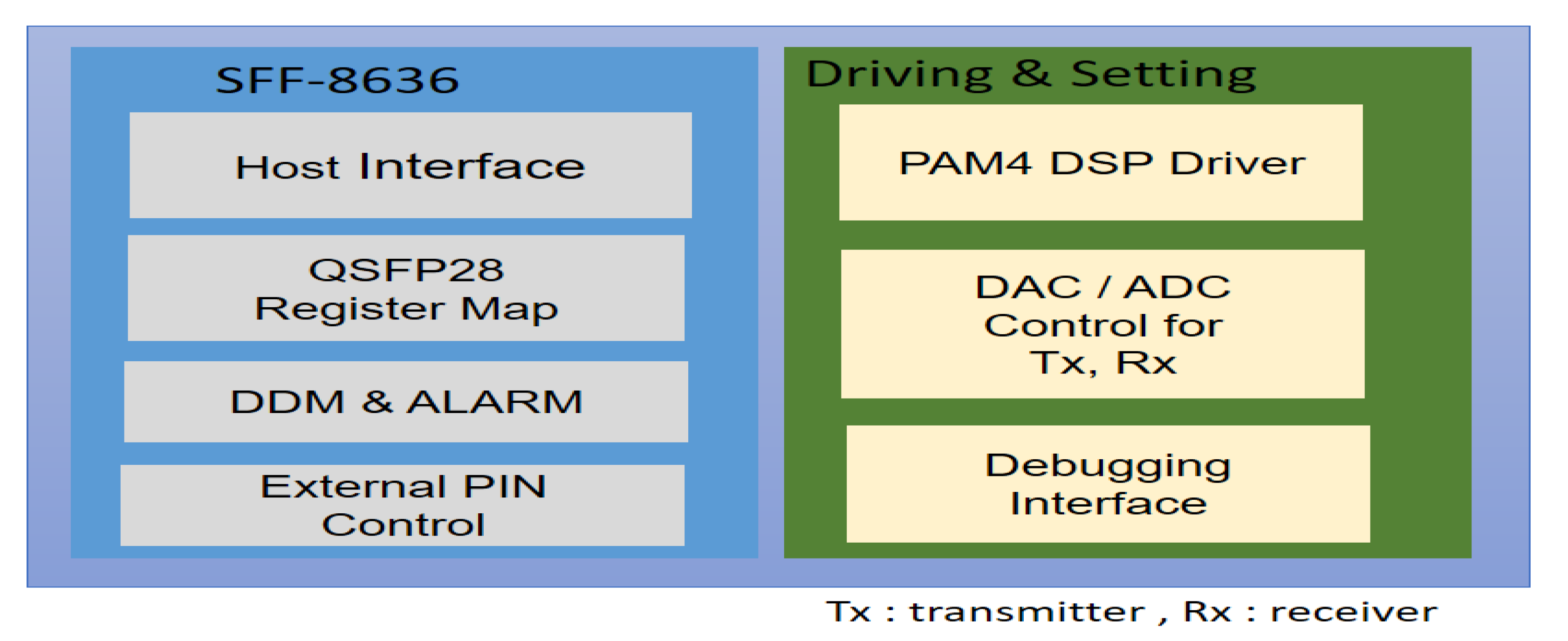

Figure 6 shows the QSFP28 firmware design block diagram.

The QSFP28 optical transceiver defines the internal registers for control and monitoring in the standard and uses I2C as the host access interface. In addition, the firmware implements digital diagnostic monitoring (DDM) and alarm functions to indicate the optical transceiver status and implements external pins functions connected by the connectors described in

Section 2. Moreover, the firmware implements the PAM4 DSP IC drive function for PAM4 processing, the DAC control function to drive transmission IC, the ADC control function to update DDM information, and the debugging interface to help debug and set up the optical transceivers. The debugging interface is not directly implemented but is indirectly designed so that the manufacturer’s area of the QSFP28 register is defined and used for debugging purposes.

Figure 7 shows the firmware sequencing of the QSFP28 PAM4 optical transceiver. The operation is initiated when the optical transceiver is energized or the reset signal is released. First, the MCU initializes the peripherals. The peripherals to be used in the proposed scheme are ADC for temperature, drive voltage, and alarm monitoring; DAC to drive the transmitting optical components such as EML-TOSA; I2C slave functions to be used as host interfaces; and I2C master functions to communicate with the external ADC IC and PAM4 DSP IC. Additionally, the Watchdog timer is initialized for firmware stability and for setting up the General-Purpose Input/Output(GPIO) pin. When the MCU peripheral initialization is complete, the PAM4 DSP IC initialization process is followed. To operate the PAM4 DSP IC, the firmware for DSP IC drive must be downloaded and initialized. The ADC IC is added in this scheme for channel scalability and precise measurement. Thus, the operating program undergoes an initialization process to utilize the external ADC IC. In addition, the process of initializing the global variables required for QSFP28 optical transceiver operation is followed by an infinite polling loop. The operating program checks the status of the LPMode/TxDIS pin and, if enabled, switches the PAM4 DSP IC to a non-operational state and shuts off the transmitting optic components power. If both LPMode/TxDIS pins are inactive, it commands the PAM4 DSP IC to drive and proceed with power activation and optimization settings for the transmission photomultiplier. For operation and optimization of the PAM4 DSP IC, the manufacturer’s datasheet was referenced and the API provided by the manufacturer was ported to the MCU to implement the drive driver. Finally, a function related to alarm monitoring was executed so that the optical transceiver status could be constantly monitored. If a monitoring and control request is received from the external host interface, the MCU generates an I2C request interrupt and performs the processing as requested.

QSFP28 Register Configuration and Control Algorithm

As described in

Section 2.3, the QSFP28 optical transceiver should define the internal register to receive control and monitoring requests from the host system and should configure nonvolatile registers, such as the upper page 0 × 02 area, at the request of the standard document. The proposed scheme allocates a portion of the MCU’s flash memory to store nonvolatile data. For the host to access the upper page 0 × 02 of the QSFP28 optical transceiver, it must first change the page selection address (0 × 7F) value on the lower page. To implement the page access function, the proposed scheme designates that the MCU uploads the value of the flash memory area of the page to the RAM when the host changes the page selection register. In addition, the vendor specific area, page 0 × 04, was used to store nonvolatile values such as the setting values for optimizing the optical component performance of the QSFP28 optical transceiver, calibration values for DDM accuracy, and values for optimizing PAM4 signals.

The QSFP28 requires an algorithm to access and control registers to handle host requests. The standard document defines only the register structure and functions and must be directly implemented by the manufacturer for actual operation. Algorithm 1 shows the QSFP28 register control algorithm that includes page selection when requested by the host system over the I2C interface. The I2C interrupts occur in the MCU when I2C access occurs from the host. The MCU executes the I2C interrupt service function to store the StartAddress, WriteCount, and WriteValue to be written to the I2C. For example, if a write action occurs on the host, the stop signal is checked for I2C communication and the I2C slave stop function is executed as shown in Algorithm 1. If this is a read operation, the register values of the lower and upper pages currently stored in the I2C buffer are sent as output to the host interface. The I2C buffer consists of a LowerBuffer and UpperBuffer, totaling 256 bytes. When the I2C slave stop function is called, access to the first page-selection address is checked, and the values of the flash memory area, where the values of that page are stored, are copied onto the upper page buffer. If not selected, the buffer value with the specific address value is updated to a new value and the processing proceeds according to the function of that address. Finally, if the value of the address must be stored on the EEPROM, the function that stores it in the flash memory must be executed. At this time, all storage units in pages are 128 bytes.

The DDM function monitors the status of the optical transceiver from the ADC IC and updates it to the register. The proposed design is monitored using the internal ADC in the MCU and the external ADC IC. The monitoring values include the optical power, transmission bias current, transmission component temperature, transceiver temperature, and voltage. The monitored values are updated by converting them to values in units defined in the standard document when they are updated in that register. In this design, the DDM-related specifications for the SFP optical transceiver in Standard Document SFF-8472 were implemented to satisfy the DDM-related specifications and were designed to calculate DDM values using higher-order polynomials to increase DDM accuracy [

20]. The DDM formula representing the receiving optical power is shown in Equation (

1):

where

RXPWR is the received optical power DDM value for the receiving channel and

is the coefficient value of the

nth order and performs the calculation up to the

mth difference. The maximum value of m is four.

A is the value monitored from the ADC, and

Offset represents the channel offset. All coefficient values and offsets were assigned to the register so that the coefficient values and offsets for each order could be set and calculated in floating point format (IEEE 754).

![Applsci 11 02803 i001]()

5. Conclusions

In this study, the optical transceiver design technology for building a next-generation communication infrastructure requiring large data transmission was proposed. The optical transceiver, in the proposed scheme, is designed with a QSFP28 form-factor type that can achieve twice the transmission efficiency per symbol using the PAM4 scheme. Moreover, it is compact and consumes less power. Optical transceivers using PAM4 require expensive photoreceptor parts for long-distance transmission, but the proposed scheme used low-cost PIN-PD to increase the economic feasibility and to optimize the transmitting optical components to meet the requirements of long-distance transmission. Hardware and firmware design schemes that satisfy the standards were proposed for the QSFP28 optical transceiver. Furthermore, both the receiver sensitivity and the error performance were experimentally measured and compared to existing solutions. The obtained results indicated that data can be transmitted successfully over a distance of up to 40 km and more. In addition, the test could produce results that meet the standard requirements for industrial use at high, low, and normal temperatures. This proves that the scheme is useful for manufacturing industrial optical transceivers.

Future studies will allow for the data transfer rate to be extended to 200G/400G based on the proposed scheme, while long-distance transmission schemes using PAM4 signals will be used not only for QSFP28 but also for other form-factor types.