A New SEPIC-Based DC-DC Converter with Coupled Inductors Suitable for High Step-Up Applications

Abstract

:1. Introduction

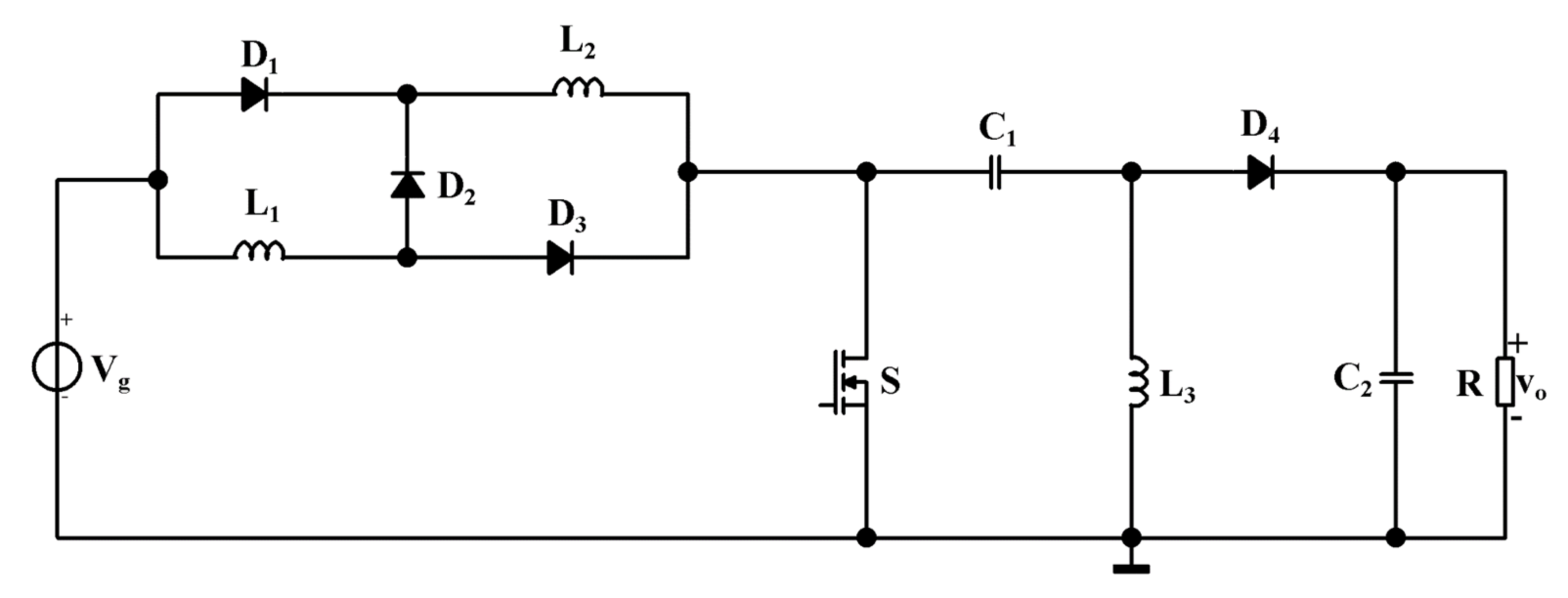

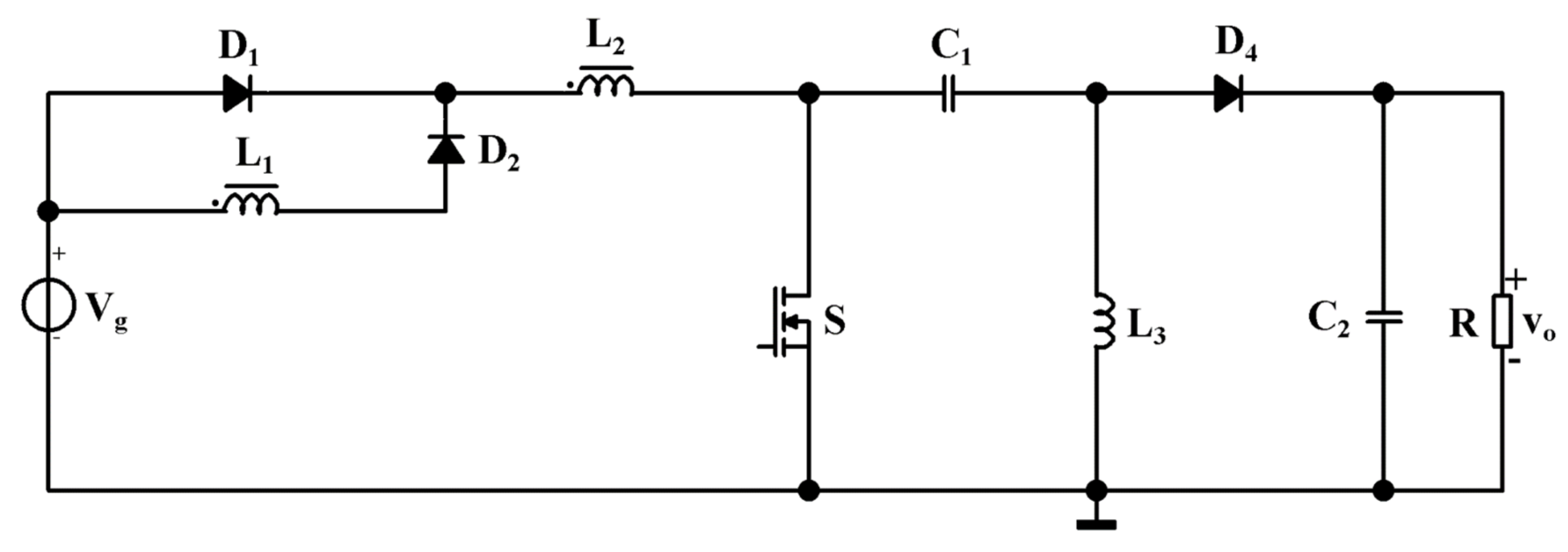

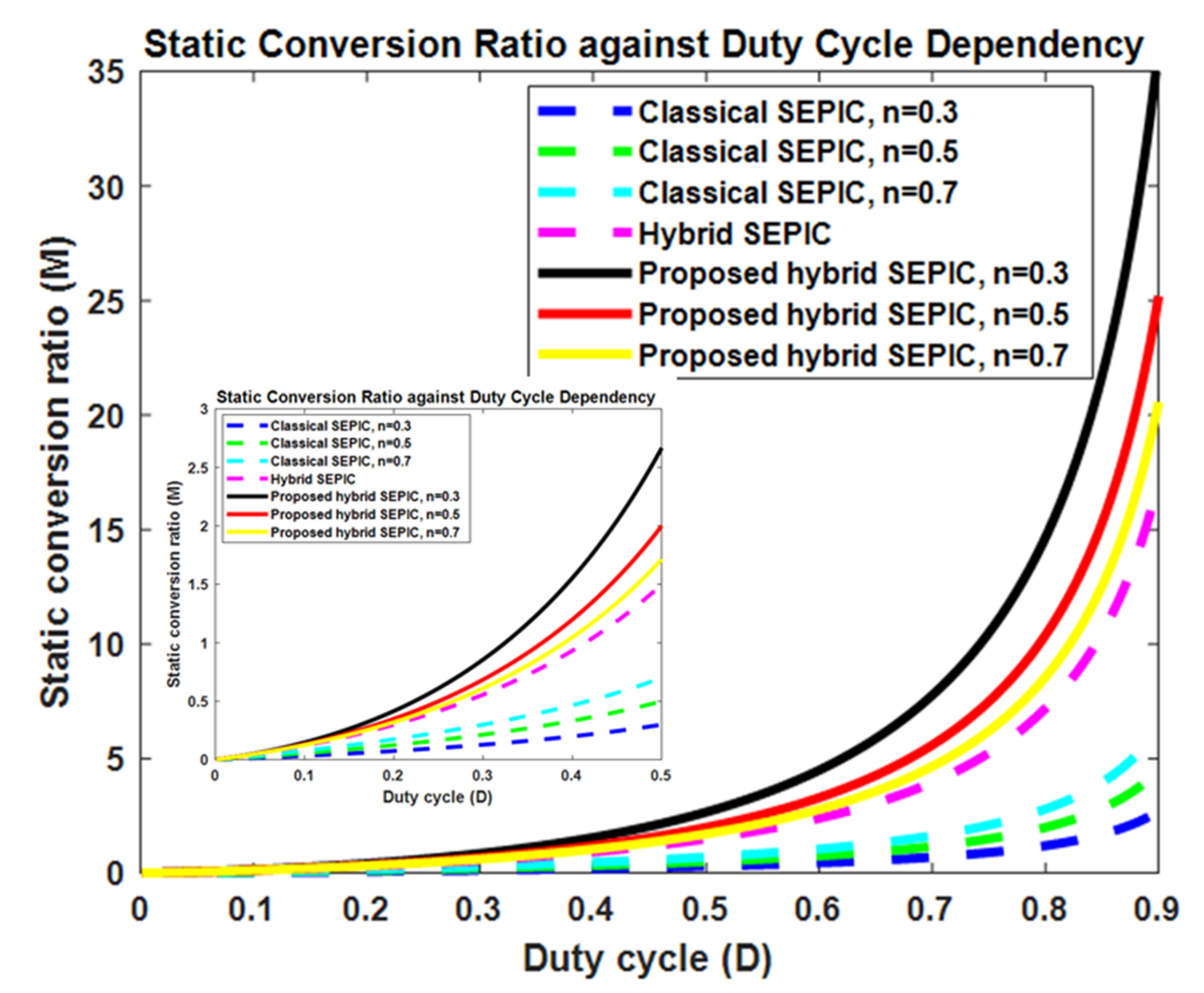

2. Steady State Analysis of the Proposed Hybrid SEPIC-Based Converter with Coupled Inductors

3. Semiconductor Stresses and AC Analysis of the Proposed SEPIC-Based Converter

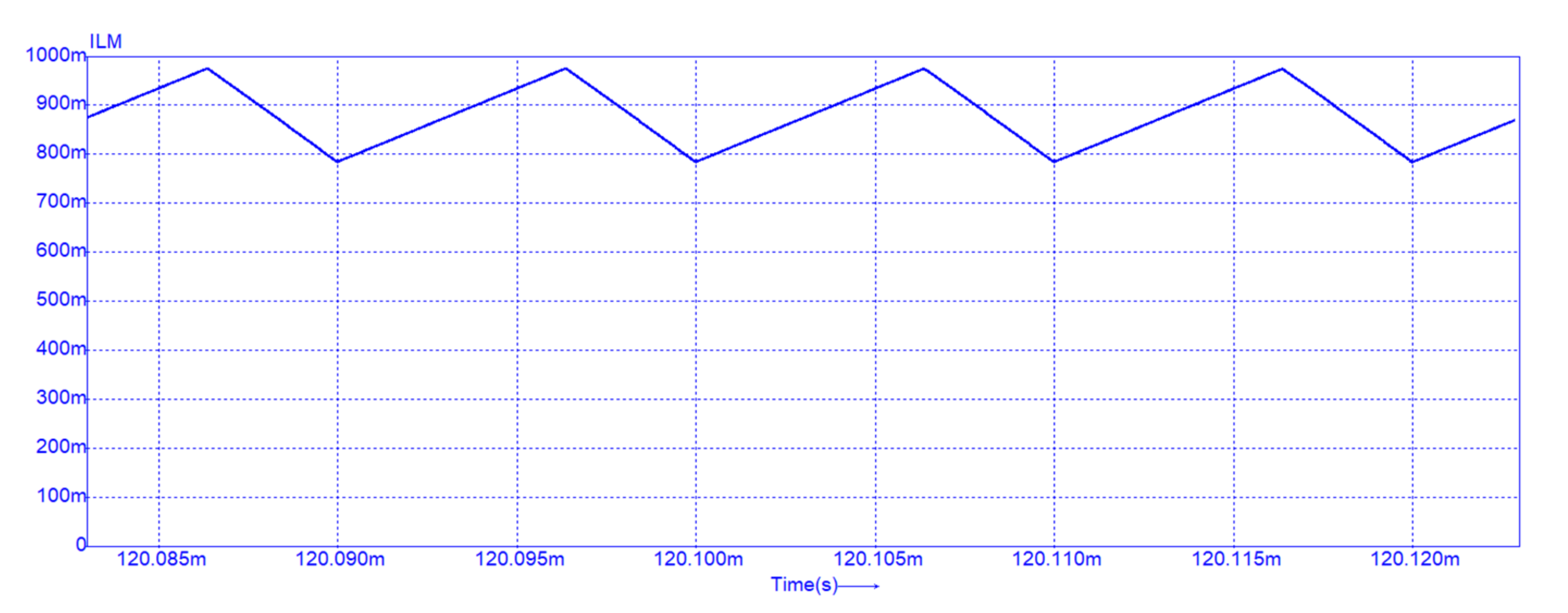

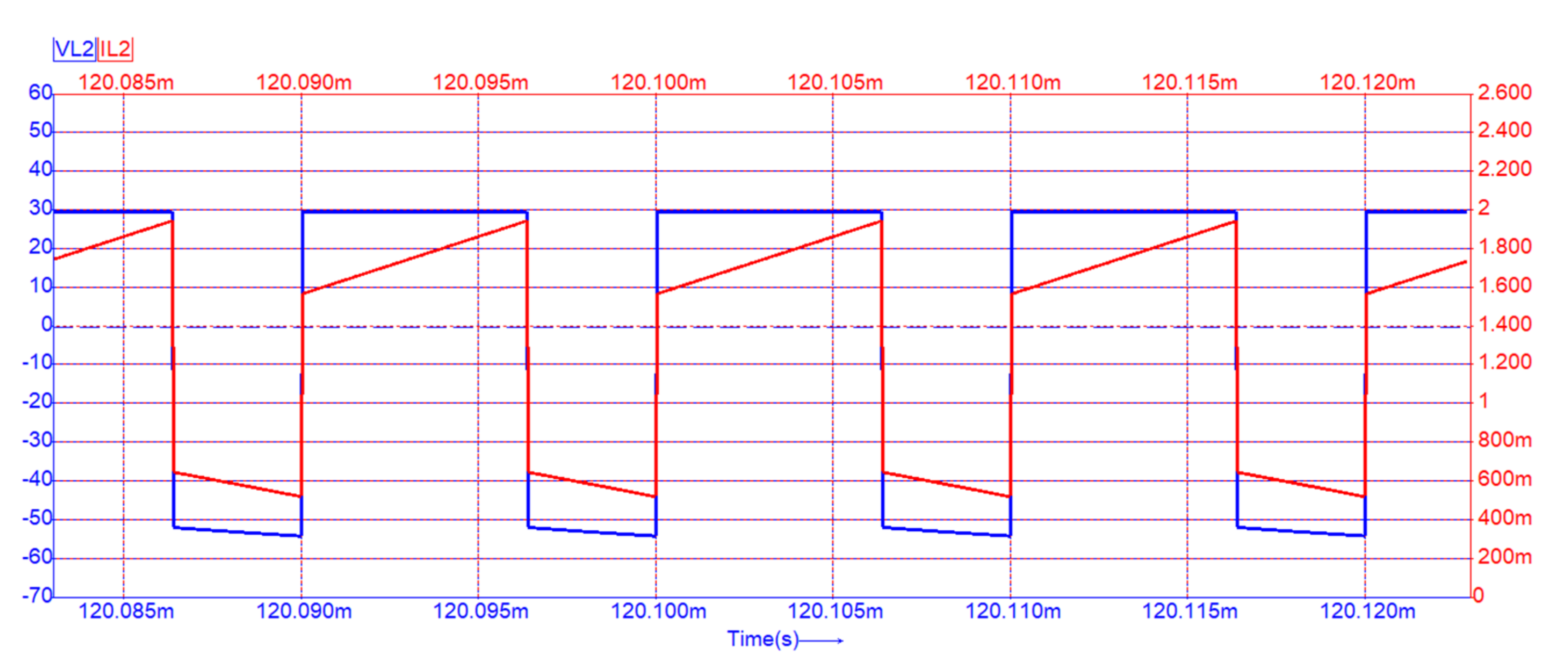

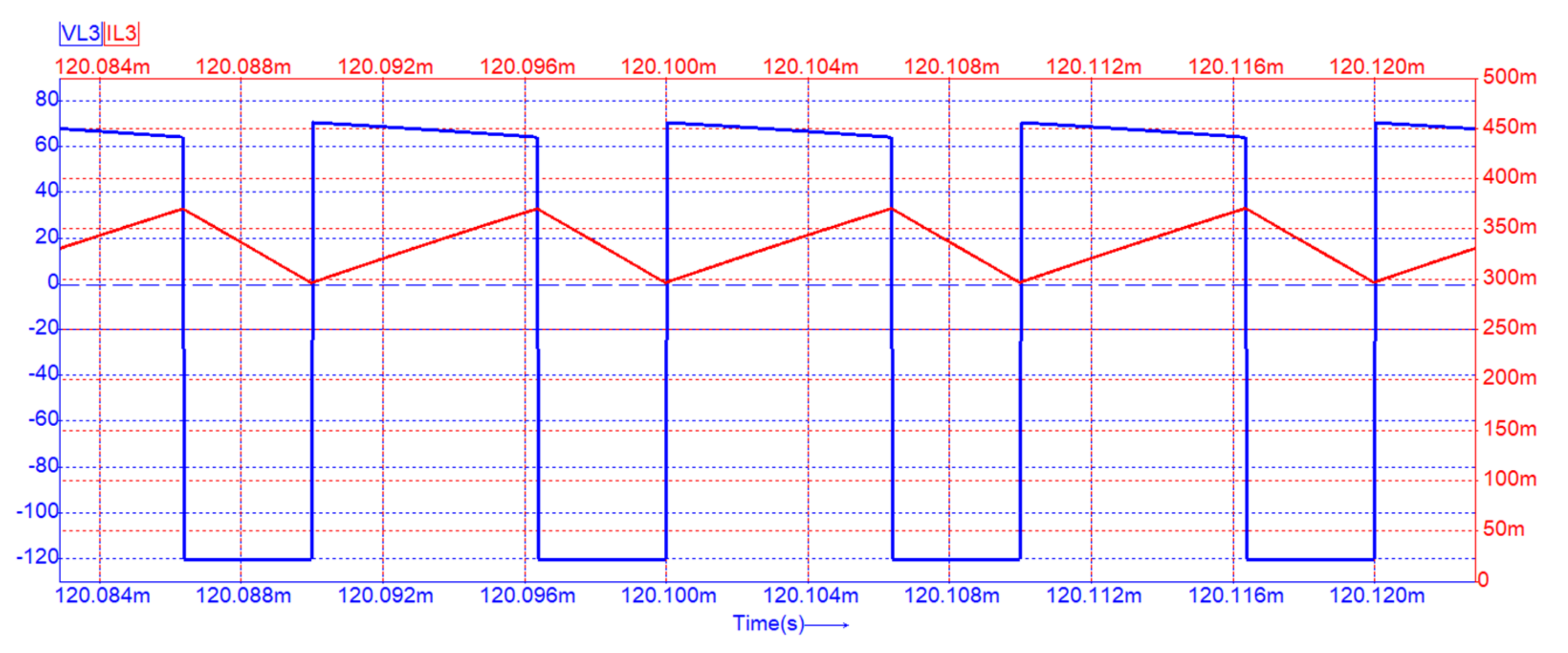

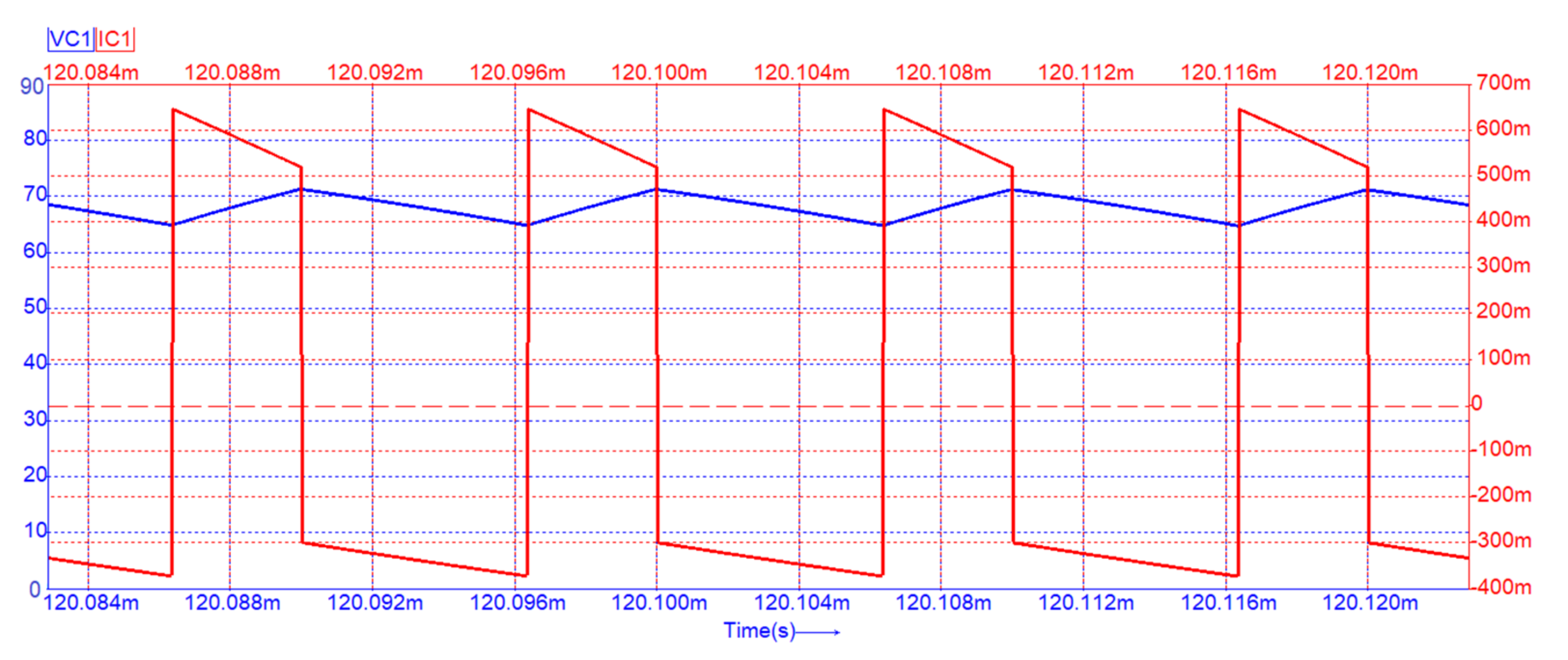

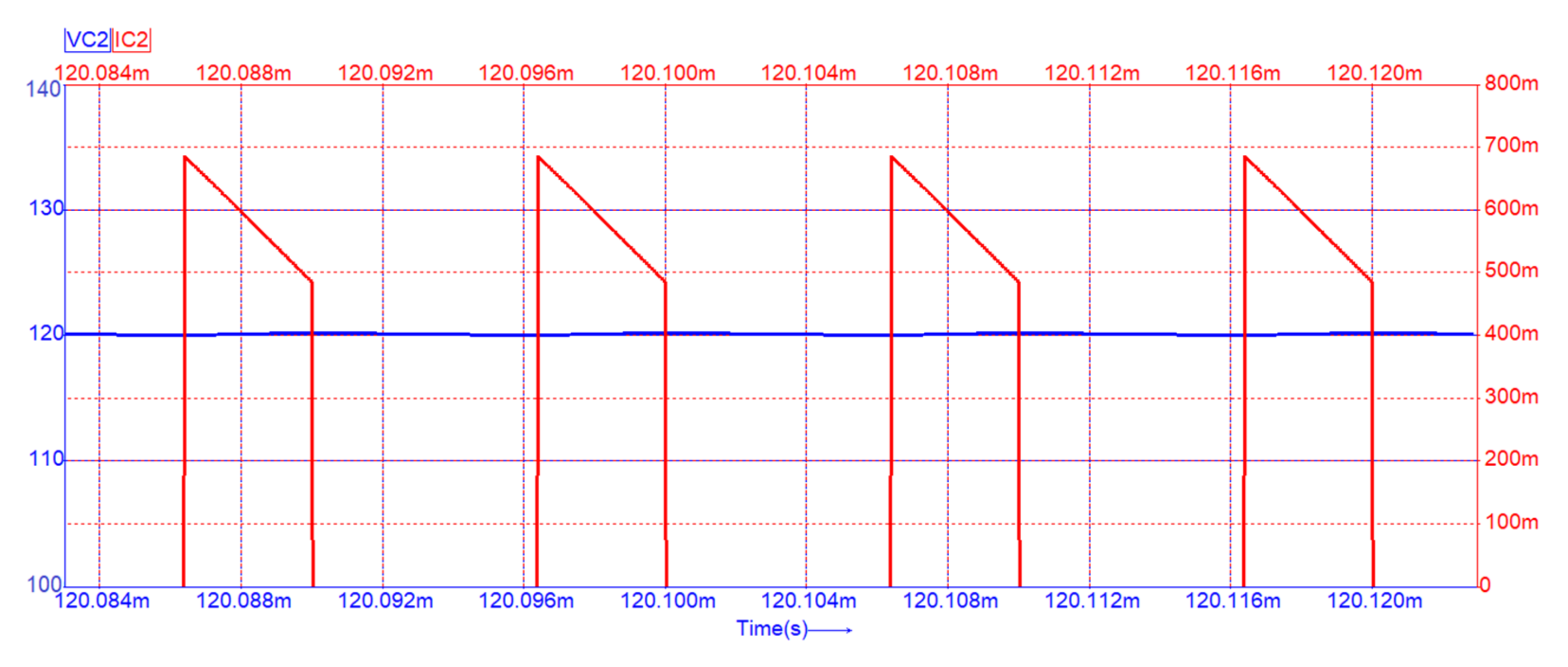

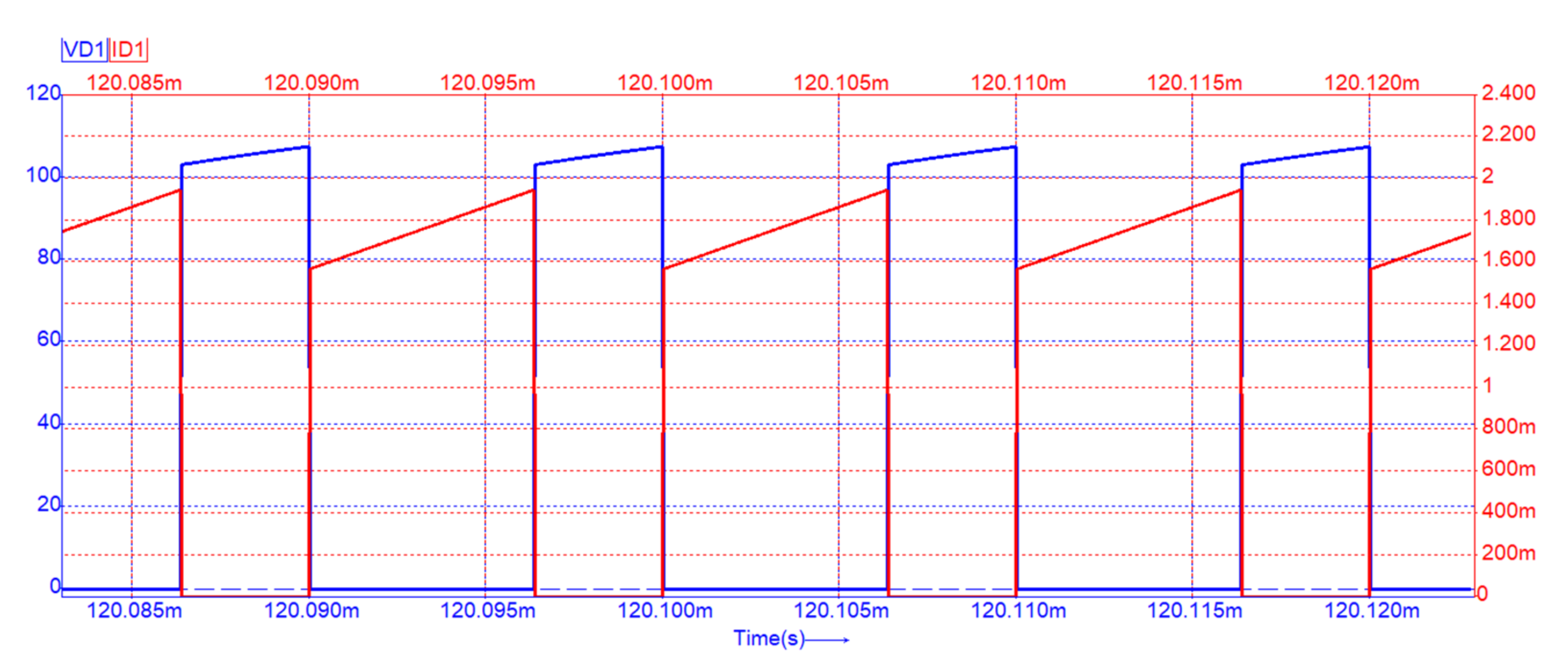

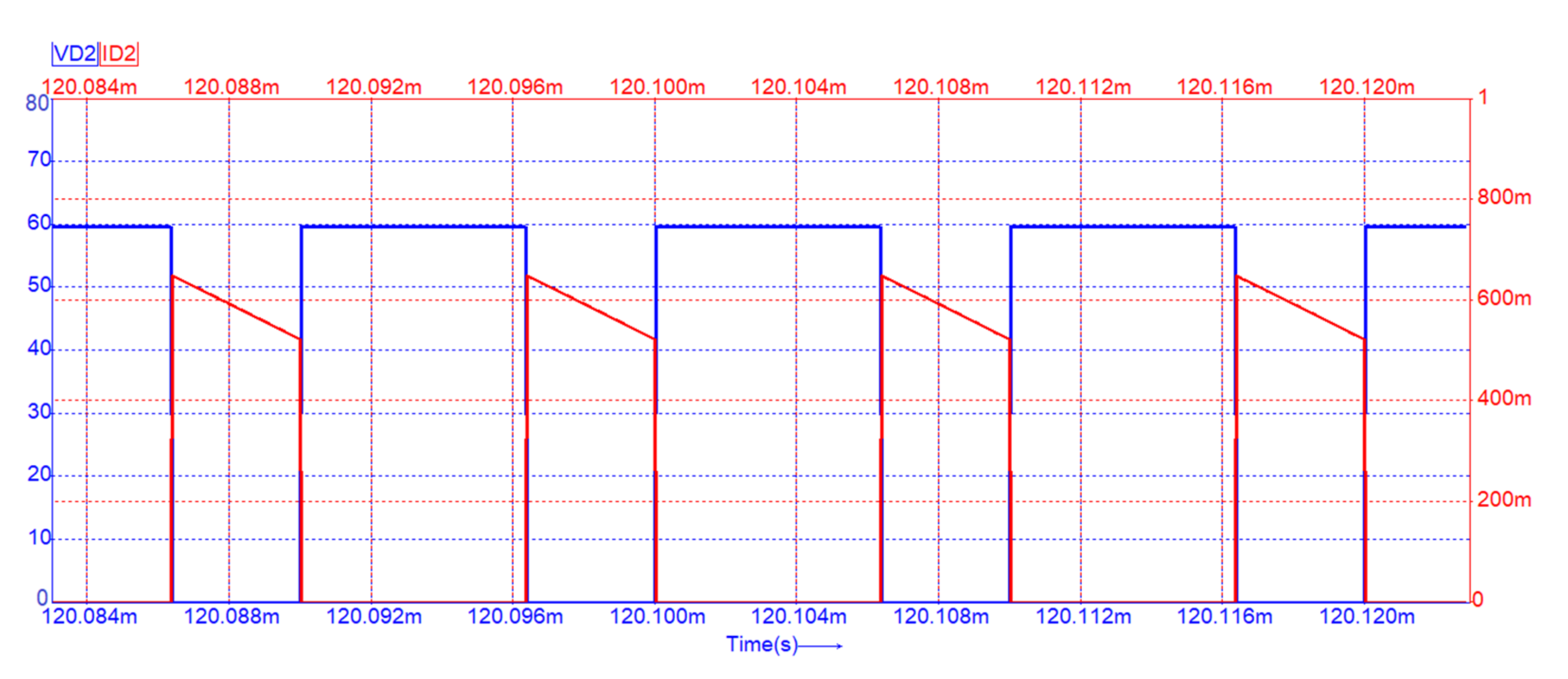

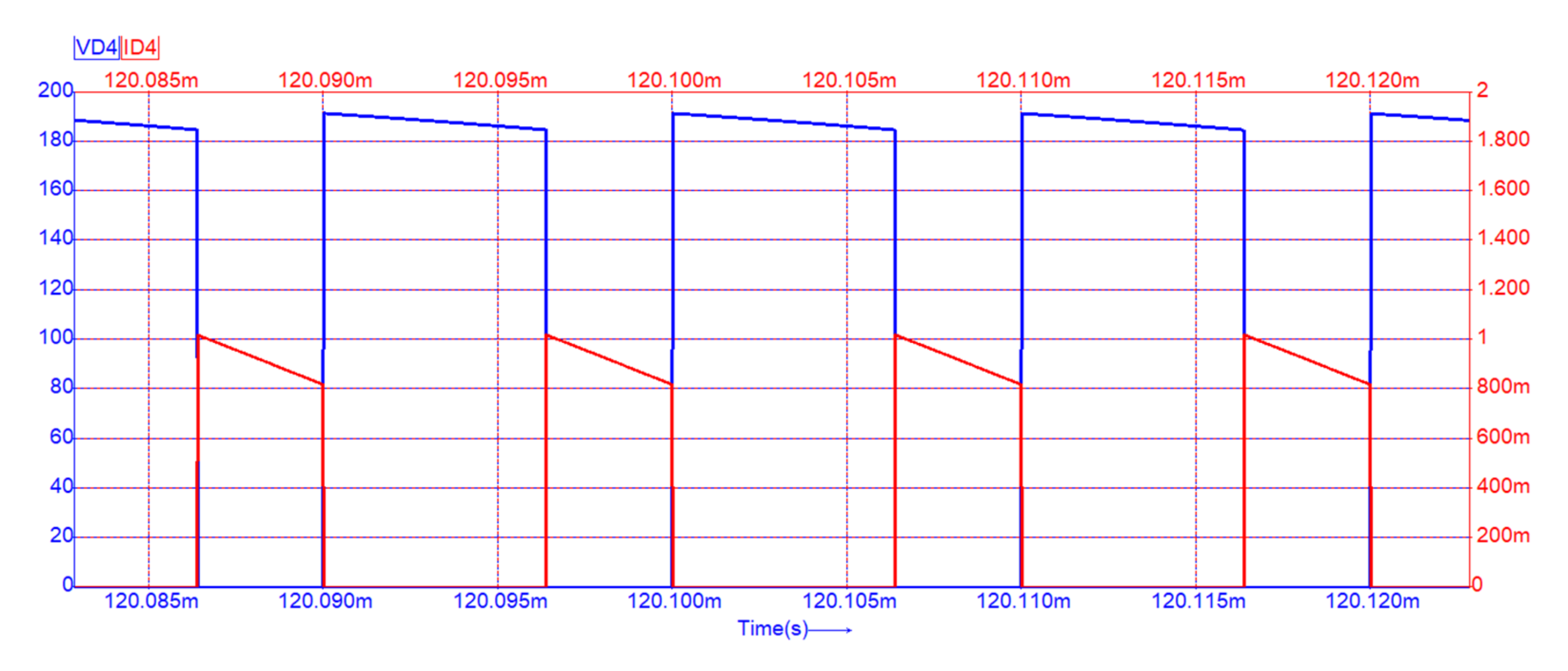

3.1. Semiconductor Stresses and Ripples Calculation

3.2. Steady State Theoretical Waveforms

3.3. Comparative Study to Other Step-Down/Step-Up Topologies

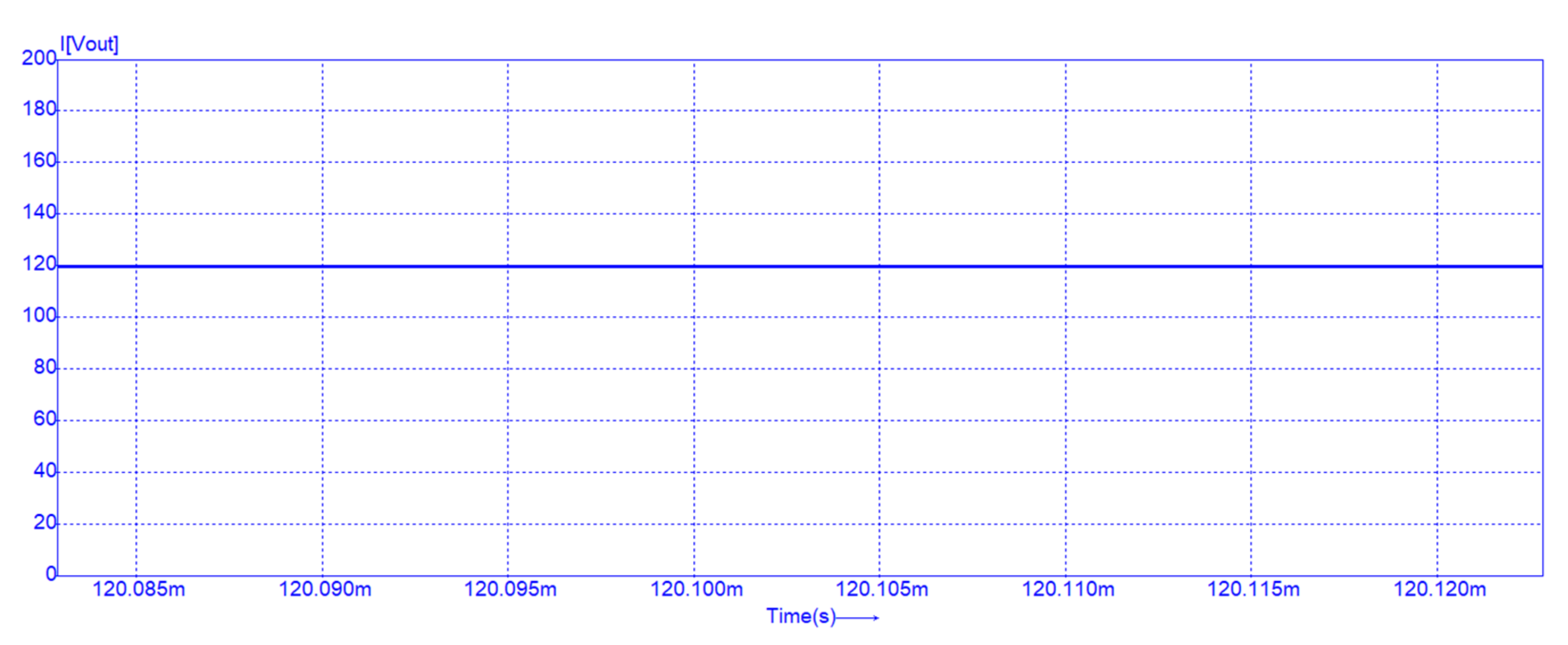

4. Design Example for the Proposed Converter

- Peak power: Pmax = 20 W

- Maximum power point current: Imp = 1.14 A

- Maximum power point voltage: Vmp = 17.49 V

- Short circuit current: Isc = 1.22 A

- Open circuit voltage: Voc = 21.67 V

- The converter was designed according to the following parameters:

- Input voltage range was between: Vg = 30 ÷ 35 V − correlated to Vmp

- Maximum output power: Po = 40 W

- Switching frequency: fs = 100 kHz

- Output voltage: Vo = 120 V

- Output voltage peak-to-peak ripple: ΔVC2 = 300 mV

- Transformer ratio: n = 0.5

5. Simulations and Experimental Results

5.1. Simulation Results

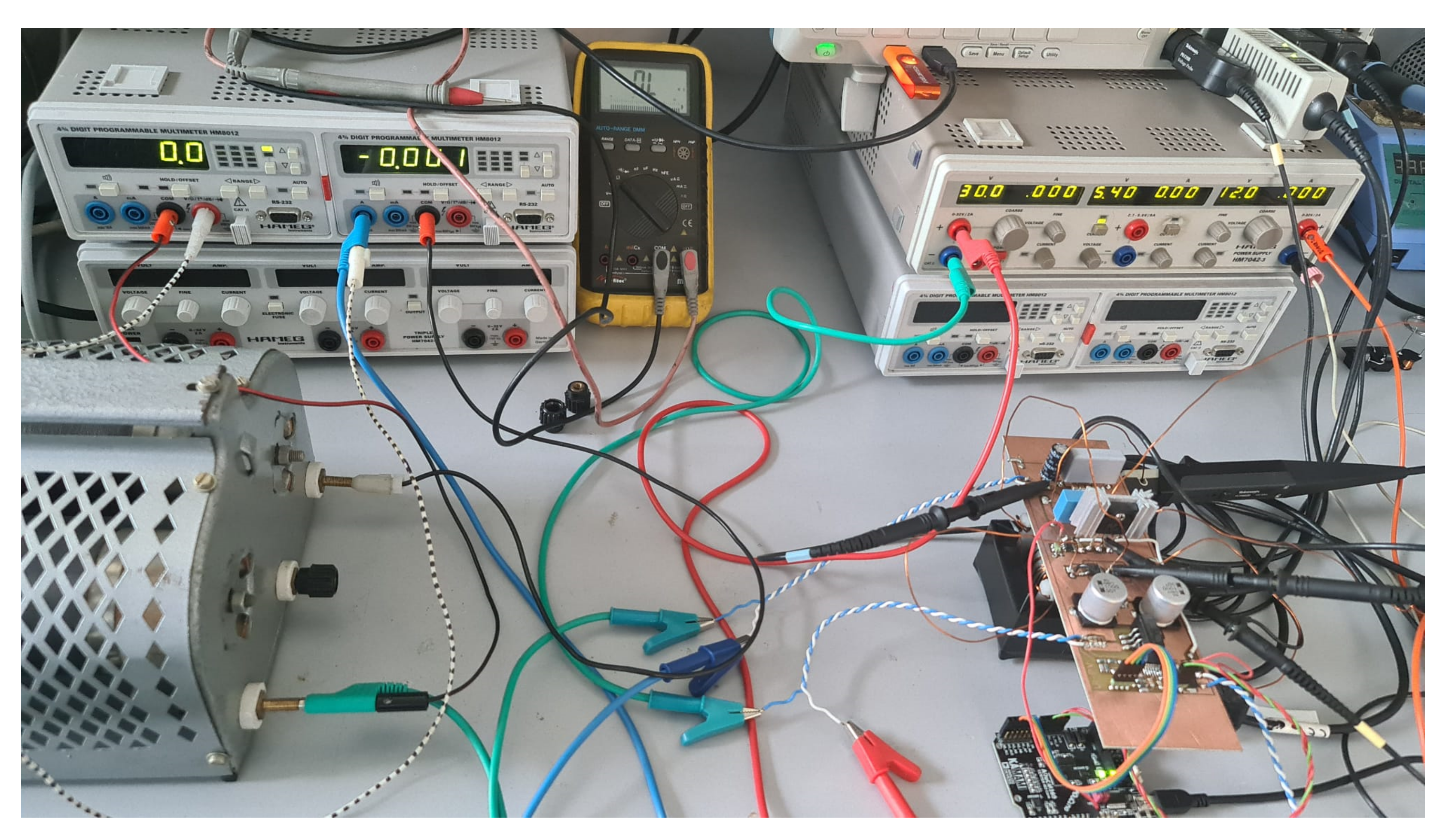

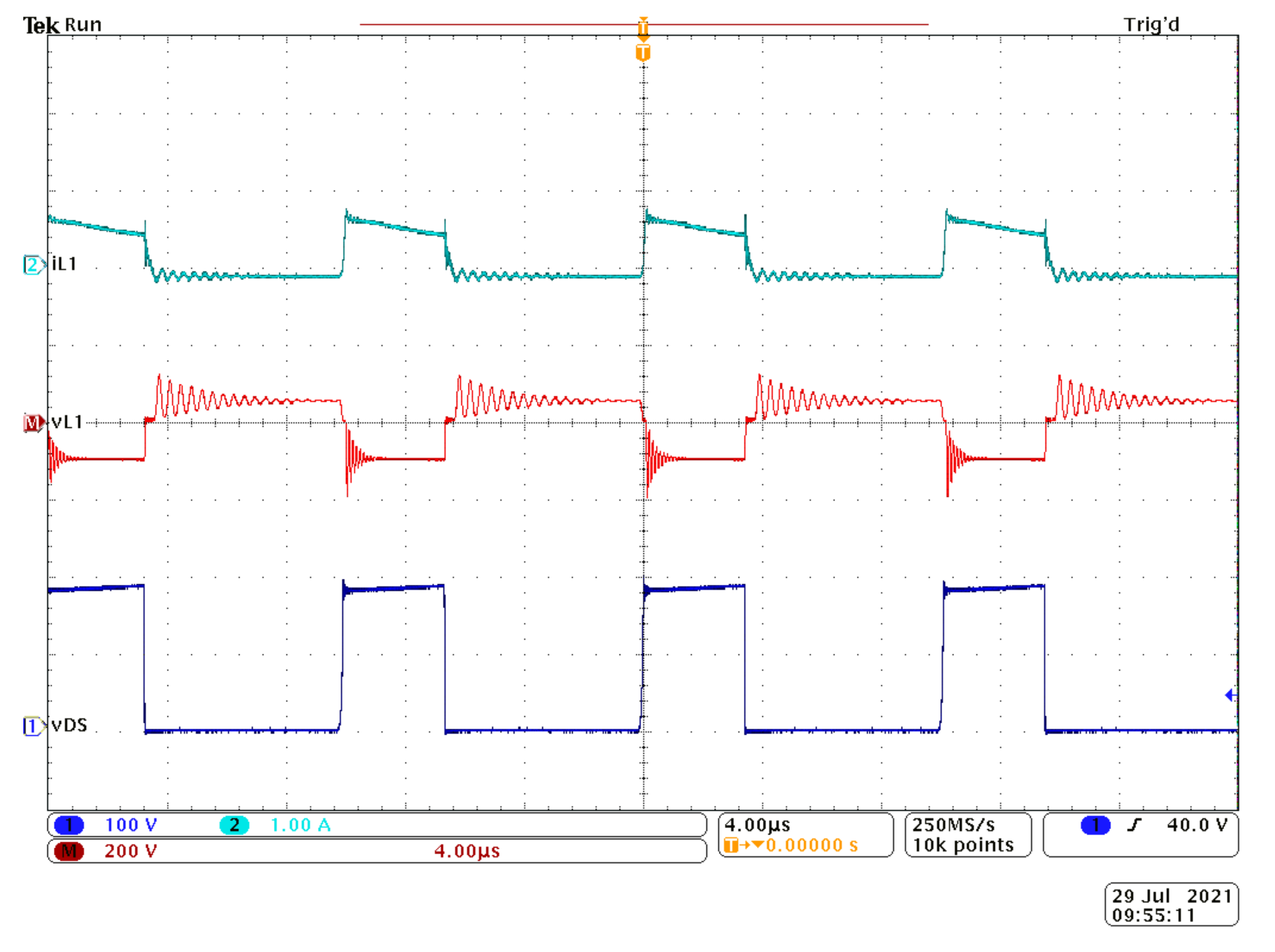

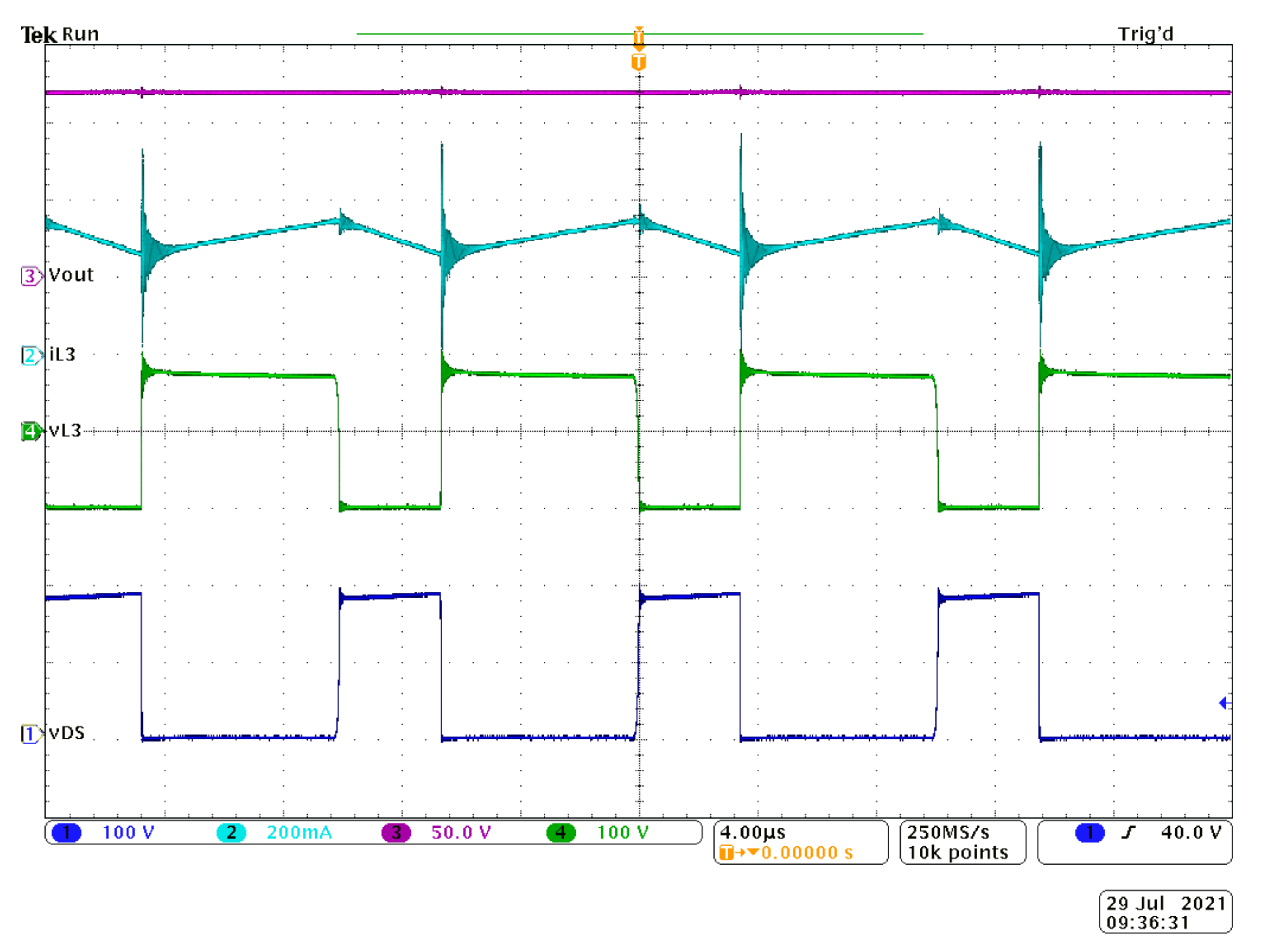

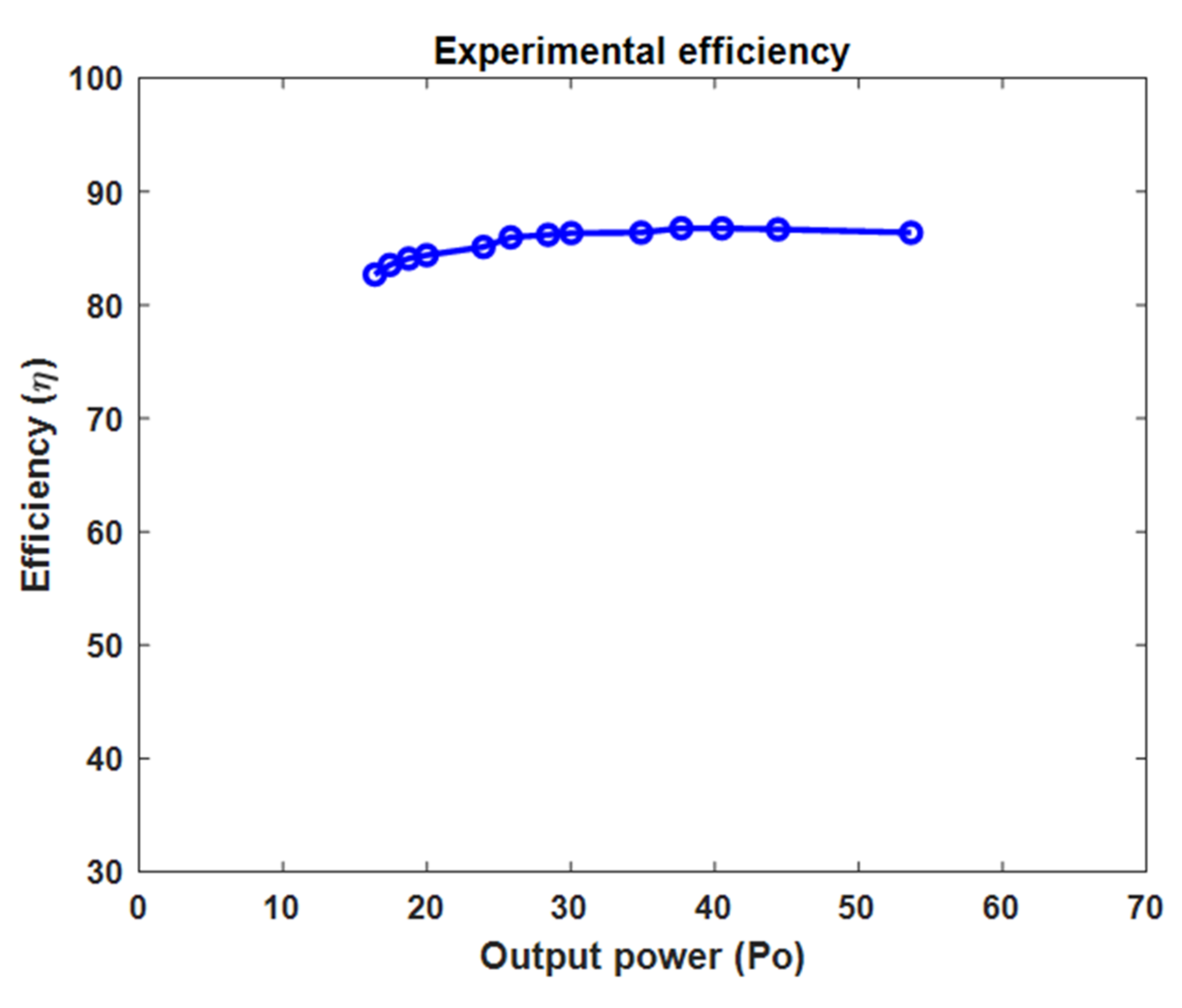

5.2. Experimental Results

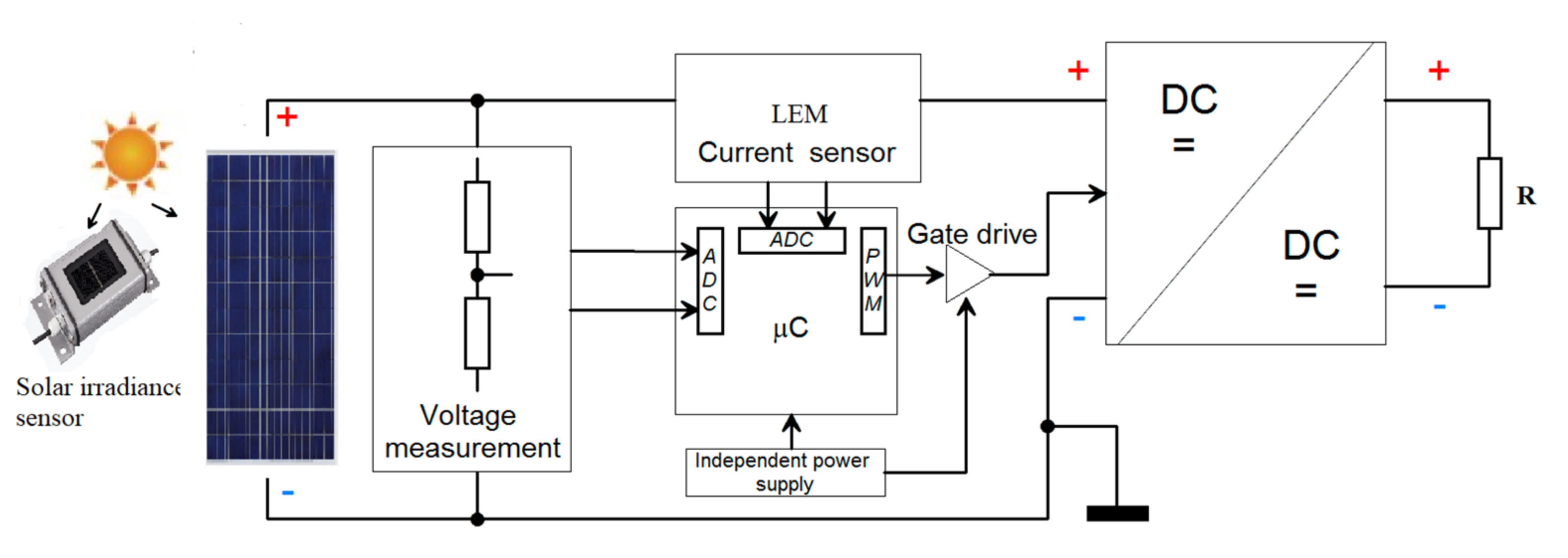

6. Applicability of the Proposed SEPIC Converter in a PV System

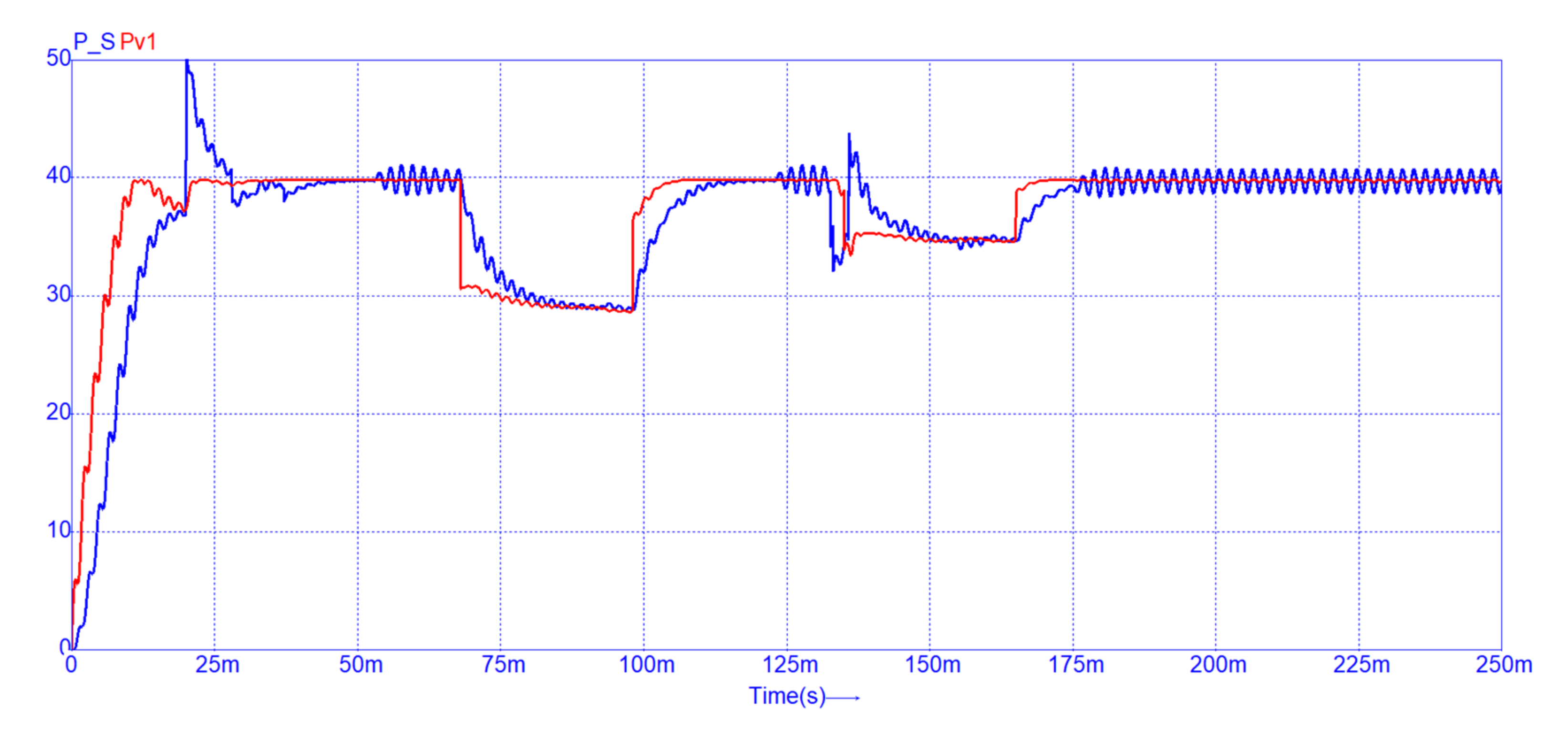

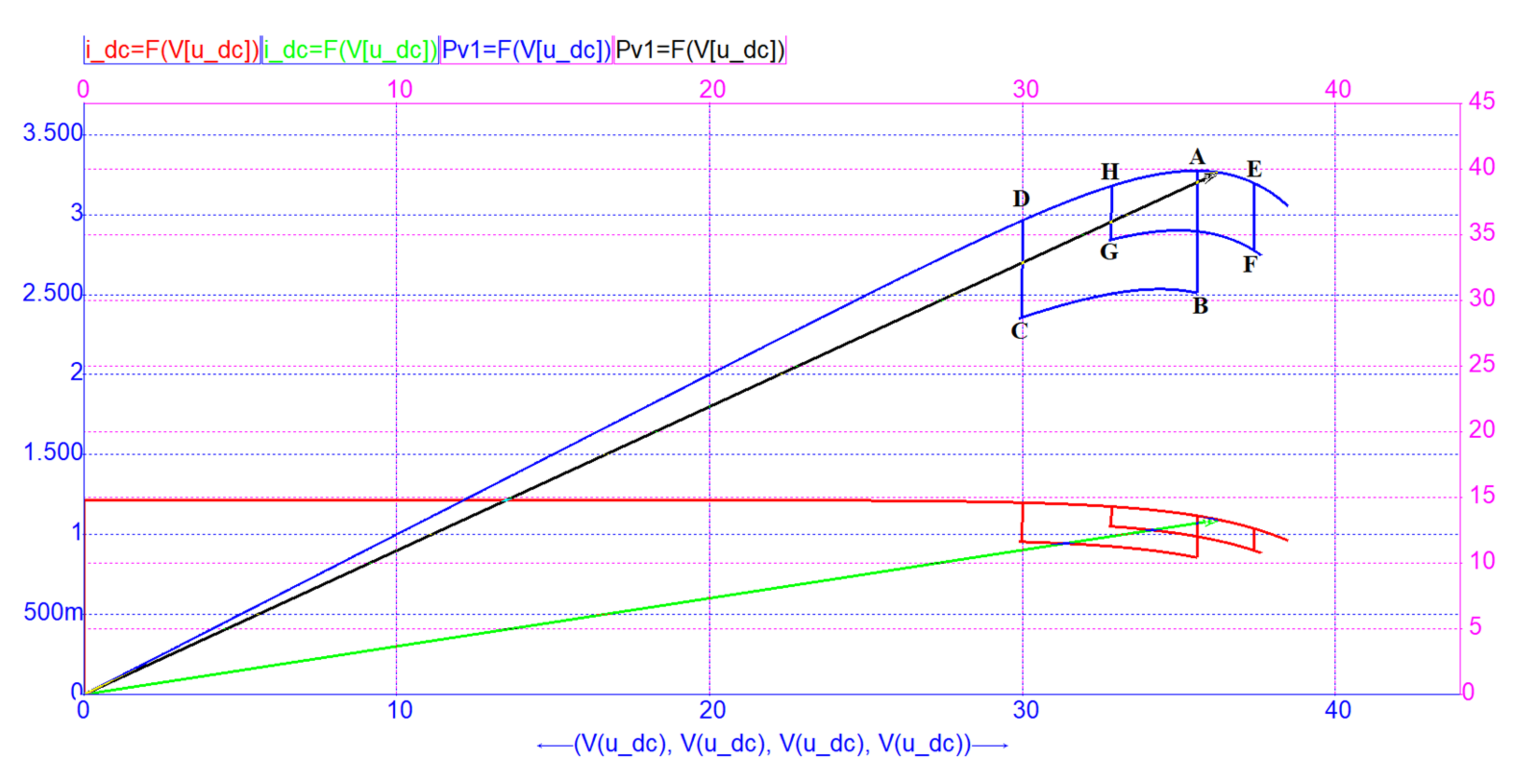

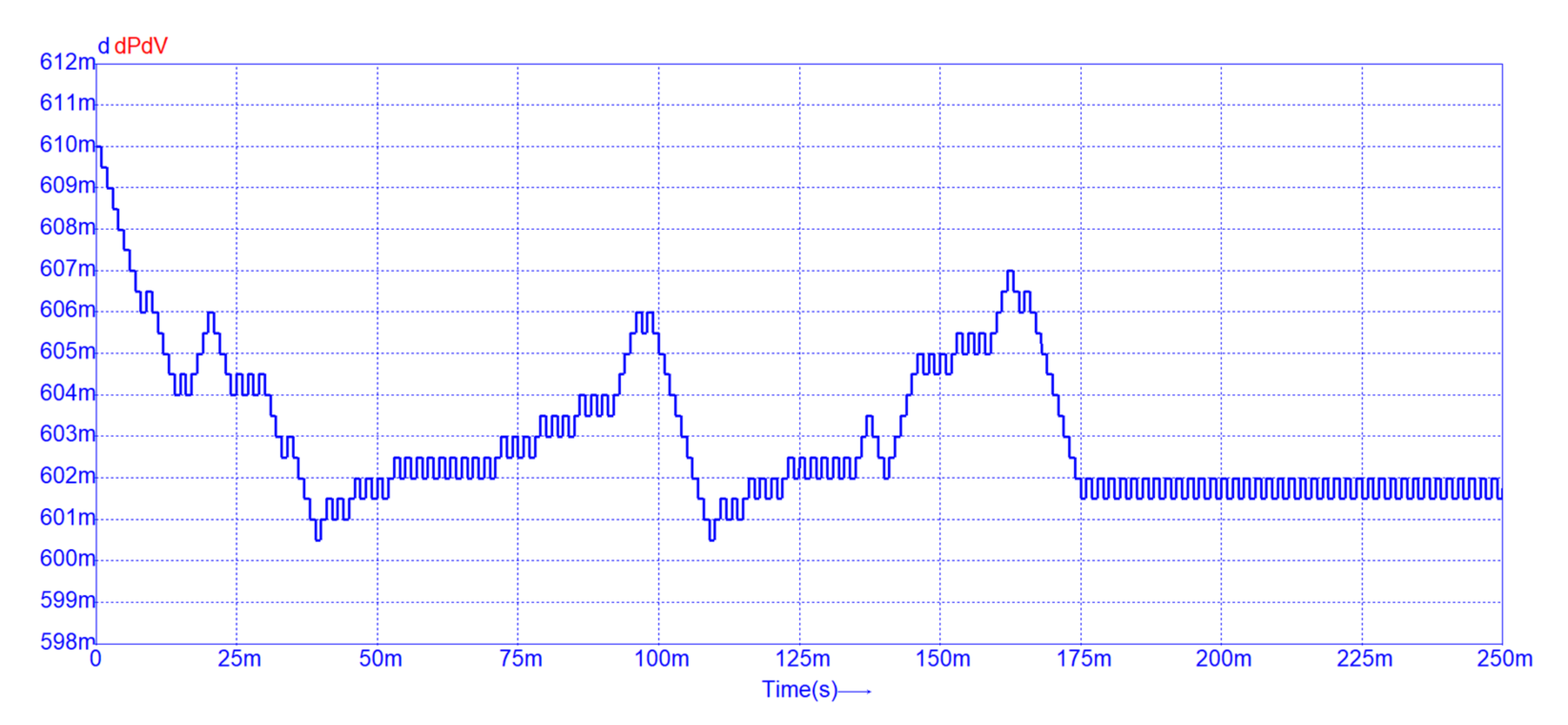

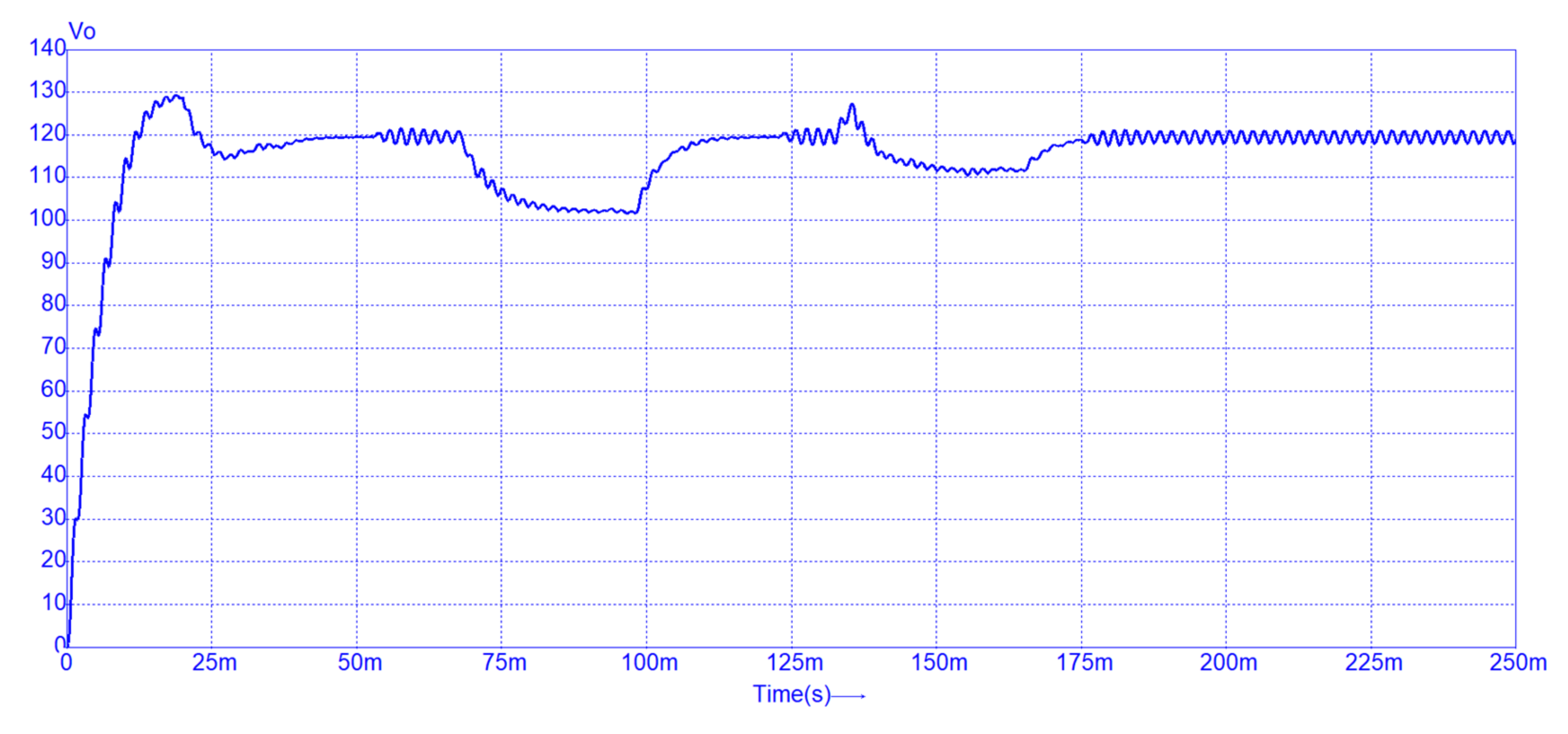

6.1. Simulation Results of the PV System Using the Proposed SEPIC Converter

- -

- at start-up T1 = 0 ms, the irradiance was set to G1 = 1000 W/m2, and the load resistance was R = 450 Ω;

- -

- at T2 = 20 ms, the load resistance suffered a change to R = 325 Ω;

- -

- at T3 = 28 ms, the load resistance was changed to R = 350 Ω;

- -

- at T4 = 37 ms, the load resistance was modified to R = 360 Ω;

- -

- at T5 = 68 ms, the irradiance was suddenly modified from G1 = 1000 W/m2 to G2 = 800 W/m2;

- -

- at T6 = 98 ms, the irradiance was set back to G3 = 1000 W/m2;

- -

- at T7 = 133 ms, the output resistance was changed to R = 460 Ω;

- -

- at T8 = 135 ms, the irradiance was set from G3 = 1000 W/m2 to G4 = 900 W/m2;

- -

- at T9 = 136 ms, the output resistance was changed back R = 360 Ω;

- -

- the last change was at T10 = 165 ms, when the irradiance was modified from G4 = 900 W/m2 to G5 = 1000 W/m2.

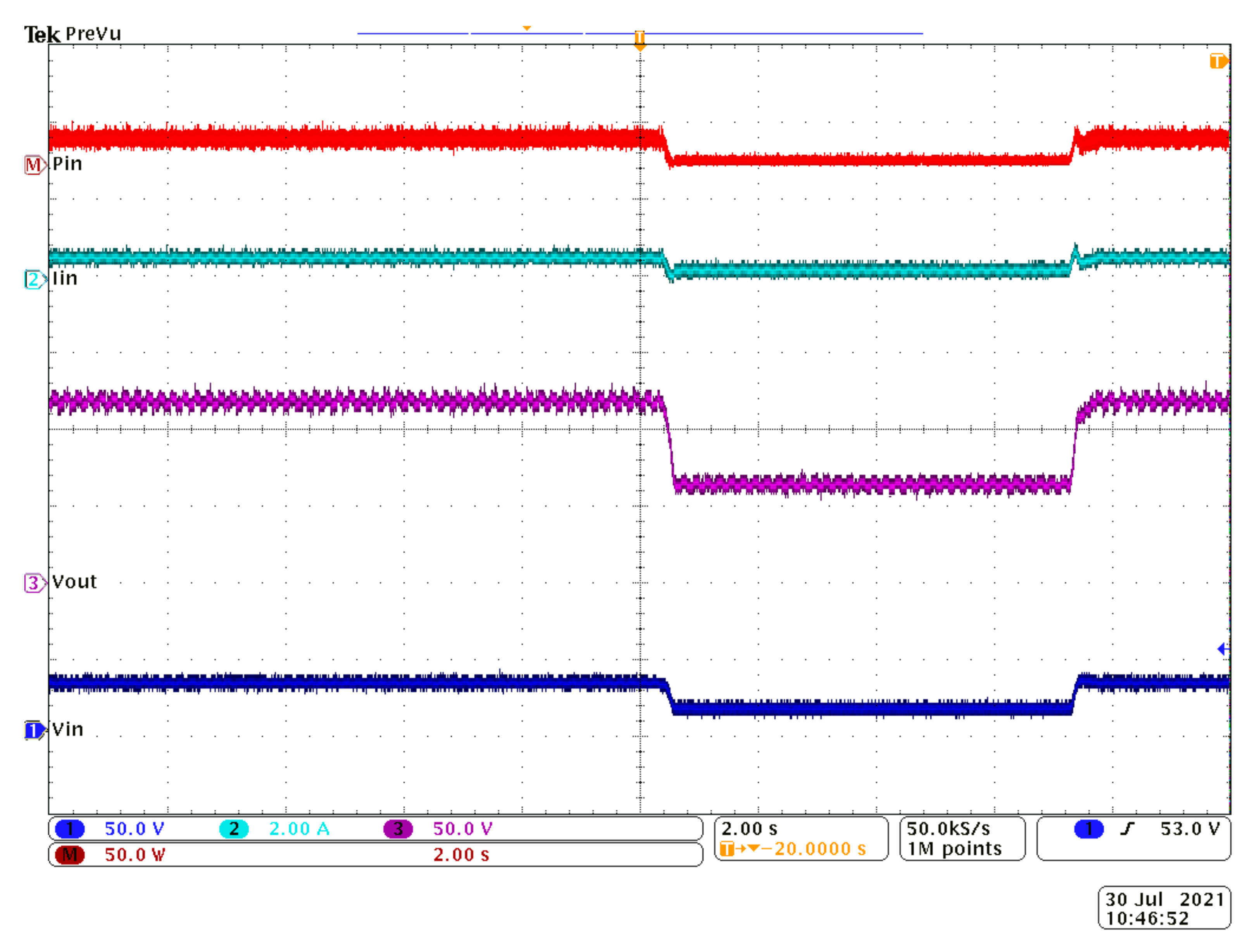

6.2. Experimental Results of the PV System Using the Proposed SEPIC-Based Converter

7. Discussion

Author Contributions

Funding

Conflicts of Interest

References

- IRENA. Global Energy Transformation: A Roadmap to 2050; International Renewable Energy Agency: Abu Dhabi, United Arab Emirates, 2018. [Google Scholar]

- IEA. Net Zero by 2050. A Roadmap for the Global Energy Sector IEA; IEA: Paris, France, 2021; Available online: https://www.iea.org/reports/net-zero-by-2050 (accessed on 1 October 2021).

- WWF—World Wide Fund for Nature (Formerly World Wildlife Fund). 100% Renewable Energy Report; WWF: Gland, Switzerland, 2011; Available online: http://awsassets.panda.org/downloads/the_energy_report_lowres_111110.pdf (accessed on 1 October 2021).

- Koç, Y.; Birbir, Y.; Bodur, H. Non-isolated high step-up DC/DC converters—An overview. Alex. Eng. J. 2021, 61, 1091–1132. [Google Scholar] [CrossRef]

- Raghavendra, K.V.G.; Zeb, K.; Muthusamy, A.; Krishna, T.N.V.; Prabhudeva Kumar, S.V.S.V.; Kim, D.-H.; Kim, M.-S.; Cho, H.-G.; Kim, H.-J. A Comprehensive Review of DC–DC Converter Topologies and Modulation Strategies with Recent Advances in Solar Photovoltaic Systems. Electronics 2020, 9, 31. [Google Scholar] [CrossRef] [Green Version]

- Affam, A.; Buswig, Y.M.; Othman, A.-K.B.H.; Bin Julai, N.; Qays, O. A review of multiple input DC-DC converter topologies linked with hybrid electric vehicles and renewable energy systems. Renew. Sustain. Energy Rev. 2020, 135, 110186. [Google Scholar] [CrossRef]

- Wu, X.; Wang, J.; Zhang, Y.; Du, J.; Liu, Z.; Chen, Y. Review of DC-DC Converter Topologies Based on Impedance Network with Wide Input Voltage Range and High Gain for Fuel Cell Vehicles. Automot. Innov. 2021, 4, 351–372. [Google Scholar] [CrossRef]

- Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications. IEEE Trans. Power Electron. 2017, 32, 9143–9178. [Google Scholar] [CrossRef]

- Ismail, E.M.; Abdulbaq, I.M.; Majeed, A.I. High Step up DC-DC Converter Fed. Photovolt. Syst. Int. J. Comput. Appl. 2016, 139, 6–13. [Google Scholar]

- Padhee, S.; Pati, U.C.; Mahapatra, K. Overview of High-Step-Up DC–DC Converters for Renewable Energy Sources. IETE Tech. Rev. 2016, 35, 99–115. [Google Scholar] [CrossRef]

- Wang, H.; Huang, X.; Wang, Y.; Xu, H. Series-connected PV MVDC Converter for Large Scale PV System. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019—ECCE Asia), Busan, Korea, 27–30 May 2019; pp. 1246–1251. [Google Scholar] [CrossRef]

- Saravanan, S.; Babu, N.R. A modified high step-up non-isolated DC-DC converter for PV application. J. Appl. Res. Technol. 2017, 15, 242–249. [Google Scholar] [CrossRef]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics, 2nd ed.; Kluwer Academic Publishers: New York, NY, USA, 2001. [Google Scholar]

- Genc, N.; Koc, Y. Experimental verification of an improved soft-switching cascade boost converter. Electr. Power Syst. Res. 2017, 149, 1–9. [Google Scholar] [CrossRef]

- Fu, J.; Zhang, B.; Qiu, D.; Xiao, W. A novel single-switch cascaded DC-DC converter of Boost and Buck-boost converters. In Proceedings of the 2014 16th European Conference on Power Electronics and Applications, Lappeenranta, Finland, 26–28 August 2014; pp. 1–9. [Google Scholar] [CrossRef]

- Totonchi, N.; Gholizadeh, H.; Mahdizadeh, S.; Afjei, E. A High Step up DC-DC Converter Based on the Cascade Boost, Voltage Multiplier Cell and Self Lift Luo Converter. In Proceedings of the 2020 10th Smart Grid Conference (SGC), Kashan, Iran, 16–17 December 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Makarim, F.H.; Antares, B.; Rizqiawan, A.; Dahono, P.A. Optimization of Multiphase Cascaded DC-DC Boost Converters. In Proceedings of the 2019 6th International Conference on Electric Vehicular Technology (ICEVT), Bali, Indonesia, 18–21 November 2019; pp. 285–289. [Google Scholar] [CrossRef]

- Hasanpour, S.; Siwakoti, Y.P.; Mostaan, A.; Blaabjerg, F. New Semiquadratic High Step-Up DC/DC Converter for Renewable Energy Applications. IEEE Trans. Power Electron. 2020, 36, 433–446. [Google Scholar] [CrossRef]

- Boujelben, N.; Masmoudi, F.; Djemel, M.; Derbel, N. Design and comparison of quadratic boost and double cascade boost converters with boost converter. In Proceedings of the 2017 14th International Multi-Conference on Systems, Signals & Devices (SSD), Marrakech, Morocco, 28–31 March 2017; pp. 245–252. [Google Scholar] [CrossRef]

- Balal, A.; Shahabi, F. Ltspice Analysis of Double-Inductor Quadratic Boost Converter in Comparison with Quadratic Boost and Double Cascaded Boost Converter. In Proceedings of the 2021 12th International Conference on Computing Communication and Networking Technologies (ICCCNT), Kharagpur, India, 6–8 July 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Boujelben, N.; Djemel, M.; Derbel, N. Analysis of a Quadratic Boost Converter using Sliding Mode Controller. In Proceedings of the 2020 17th International Multi-Conference on Systems, Signals & Devices (SSD), Monastir, Tunisia, 20–23 July 2020; pp. 969–973. [Google Scholar] [CrossRef]

- Lica, S.; Pop-Călimanu, I.M.; Lascu, D.; Cireşan, A.; Gurbina, M. A new stacked step-up converter. In Proceedings of the 2017 40th International Conference on Telecommunications and Signal Processing (TSP), Barcelona, Spain, 5–7 July 2017; pp. 315–319. [Google Scholar] [CrossRef]

- Lica, S.; Vătău, V.; Lascu, D.; Tomoroga, M. A Generalized Model for Stacked Boost Single-Switch Converters. In Proceedings of the 2020 IEEE 26th International Symposium for Design and Technology in Electronic Packaging (SIITME), Pitesti, Romania, 21–24 October 2020; pp. 386–389. [Google Scholar] [CrossRef]

- Axelrod, B.; Berkovich, Y.; Ioinovici, A. Switched-Capacitor/Switched-Inductor Structures for Getting Transformerless Hybrid DC–DC PWM Converters. IEEE Trans. Circ. Syst. I Regul. Pap. 2008, 55, 687–696. [Google Scholar] [CrossRef]

- Axelrod, B.; Berkovich, Y.; Ioinovici, A. Switched-capacitor (SC)/switched inductor (SL) structures for getting hybrid step-down Cuk/Sepic/Zeta converters. In Proceedings of the IEEE International Symposium on Circuits and Systems, Island of Kos, Greece, 21–24 May 2006; p. 4. [Google Scholar]

- Axelrod, B.; Berkovich, Y.; Ioinovici, A. Hybrid switched-capacitor-Cuk/Zeta/Sepic converters in step-up mode. In Proceedings of the IEEE International Symposium on Circuits and Systems, Kobe, Japan, 23–26 May 2005; Volume 2, pp. 1310–1313. [Google Scholar]

- Axelrod, B.; Berkovich, Y.; Tapuchi, S.; Ioinovici, A. Steep conversion ration Cuk, Zeta, and Sepic converters based on a switched coupled-inductor cell. In Proceedings of the IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 3009–3014. [Google Scholar]

- Khwan-On, S.; Kongkanjana, K. A Multi-input High Step-up Converter for Renewable Energy-Drive Systems. In Proceedings of the 2019 IEEE 2nd International Conference on Power and Energy Applications (ICPEA), Singapore, 27–30 April 2019; pp. 212–216. [Google Scholar] [CrossRef]

- Renken, F.; Pop-Calimanu, I.-M.; Schürmann, U. Novel multiphase hybrid boost converter with wide conversion ratio. In Proceedings of the 2014 16th European Conference on Power Electronics and Application, Lappeenranta, Finland, 26–28 August 2014; pp. 1–10. [Google Scholar] [CrossRef]

- Yang, L.; Zhang, J.; Yu, W.; Tong, X.; Wu, X. Analysis of isolated high boost quasi-two switch boosting switched-capacitor converter. In Proceedings of the 2018 13th IEEE Conference on Industrial Electronics and Applications (ICIEA), Wuhan, China, 31 May–2 June 2018; pp. 281–286. [Google Scholar] [CrossRef]

- Aguilar-Najar, R.; Perez-Pinal, F.; Lara-Salazar, G.; Herrera-Ramirez, C.; Barranco-Gutierrez, A. Cascaded buck converter: A reexamination. In Proceedings of the 2016 IEEE Transportation Electrification Conference and Expo (ITEC), Busan, Korea, 1–4 June 2016; pp. 1–5. [Google Scholar] [CrossRef]

- Veerachary, M. Modeling of cascade buck converters. In Proceedings of the 2003 International Symposium on Circuits and Systems 2003, Bangkok, Thailand, 25–28 May 2003; p. III. [Google Scholar] [CrossRef]

- Ayachit, A.; Kazimierczuk, M.K. Power losses and efficiency analysis of the quadratic buck converter in CCM. In Proceedings of the 2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS), College Station, TX, USA, 3–6 August 2014; pp. 463–466. [Google Scholar] [CrossRef]

- Ishwarya, M.; Dhanalakshmi, R. Investigations on multiphase modified interleaved buck converters for high step down voltage. In Proceedings of the 2017 International Conference on Innovative Mechanisms for Industry Applications (ICIMIA), Bengaluru, India, 21–23 February 2017; pp. 491–496. [Google Scholar] [CrossRef]

- Paul, A.K.; Paul, S.; Paul, B. Transformerless Buck-Boost Converter with Positive Output Voltage and Feedback. Int. J. Eng. Res. Technol. (IJERT) 2017, 6, 656–661. [Google Scholar]

- Wu, Y. Novel High Efficiency Three-Port Bidirectional Step-up/Step-down DC/DC Converter for Photovoltaic Systems. In Proceedings of the 2020 IEEE 3rd International Conference on Electronics Technology (ICET), Chengdu, China, 8–12 May 2020; pp. 289–296. [Google Scholar] [CrossRef]

- Wu, H.; Sun, K.; Chen, L.; Zhu, L.; Xing, Y. High Step-Up/Step-Down Soft-Switching Bidirectional DC–DC Converter with Coupled-Inductor and Voltage Matching Control for Energy Storage Systems. IEEE Trans. Ind. Electron. 2016, 63, 2892–2903. [Google Scholar] [CrossRef]

- Chen, M.M.; Cheng, K.W.E. A new bidirectional DC-DC converter with a high step-up/down conversion ratio for renewable energy applications. In Proceedings of the 2016 International Symposium on Electrical Engineering (ISEE), Hong Kong, China, 16–18 March 2016; pp. 1–6. [Google Scholar]

- Siouane, S.; Jovanović, S.; Poure, P.; Jamshidpour, E. An Efficient Fault Tolerant Cascaded Step-Up Step-Down Converter for Solar PV Modules. In Proceedings of the 2018 IEEE International Conference on Environment and Electrical Engineering and 2018 IEEE Industrial and Commercial Power Systems Europe (EEEIC/I&CPS Europe), Palermo, Italy, 12–15 June 2018; pp. 1–5. [Google Scholar]

- Gholizadeh, H.; Sarikhani, A.; Hamzeh, M. A Transformerless Quadratic Buck-Boost Converter Suitable for Renewable Applications. In Proceedings of the 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), Shiraz, Iran, 12–14 February 2019; pp. 470–474. [Google Scholar]

- Sun, Z.; Bae, S. Multiple-Input Soft-Switching Step-up/down Converter for Renewable Energy Systems. In Proceedings of the 7th International Conference on Renewable Energy Research and Applications (ICRERA), Paris, France, 14–17 October 2018; pp. 632–636. [Google Scholar]

- Moury, S.; Lam, J. New soft-switched high frequency multi-input step-up/down converters for high voltage DC-distributed hybrid renewable systems. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 5537–5544. [Google Scholar]

- Maroti, P.K.; Esmaeili, S.; Iqbal, A.; Meraj, M. High step-up single switch quadratic modified SEPIC converter for DC microgrid applications. IET Power Electron. 2020, 13, 3717–3726. [Google Scholar] [CrossRef]

- Muranda, C.; Ozsoy, E.; Padmanaban, S.; Bhaskar, M.S.; Fedak, V.; Ramachandaramurthy, V.K. Modified SEPIC DC-to-DC boost converter with high output-gain configuration for renewable applications. In Proceedings of the 2017 IEEE Conference on Energy Conversion (CENCON), Kuala Lumpur, Malaysia, 30–31 October 2017; pp. 317–322. [Google Scholar]

- Baliwant, B.B.; Gothane, A.R.; Waghmare, V.B. Hardware Implementation of DC-DC SEPIC Converter for Applications of Renewable Energy Using PWM Based Charge Controller. In Proceedings of the 3rd International Conference on Electronics, Communication and Aerospace Technology (ICECA), Coimbatore, India, 12–14 June 2019; pp. 562–565. [Google Scholar]

- De Melo, P.F.; Gules, R.; Romaneli, E.F.R.; Annunziato, R.C. A Modified SEPIC Converter for High-Power-Factor Rectifier and Universal Input Voltage Applications. IEEE Trans. Power Electron. 2009, 25, 310–321. [Google Scholar] [CrossRef]

- Mosconi Ewerling, M.V.; Brunelli Lazzarin, T.; Illa Font, C.H. Proposal of an Isolated Two-Switch DC-DC SEPIC Converter. In Proceedings of the 2019 IEEE 15th Brazilian Power Electronics Conference and 5th IEEE Southern Power Electronics Conference (COBEP/SPEC), Santos, Brazil, 1–4 December 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Ranjana, M.S.; SreeramulaReddy, N.; Kumar, R.K. A novel sepic based dual output DC-DC converter for solar applications. In Proceedings of the 2014 Power and Energy Systems: Towards Sustainable Energy, Bangalore, India, 13–15 March 2014; pp. 1–5. [Google Scholar] [CrossRef]

- Ravindran, V.; Ponraj, R.; Syed Zameerbasha, S.; Santhosh Kanna, N.; SamuelRaj, S.; Sabarish, B. Dynamic Performance Enhancement of Modified Sepic Converter. In Proceedings of the 2021 2nd International Conference for Emerging Technology (INCET), Belagavi, India, 21–23 May 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Prajof, P.; Agarwal, V. Novel boost-SEPIC type interleaved dc-dc converter for low-voltage bipolar dc microgrid-tied solar pv applications. In Proceedings of the 2015 IEEE 42nd Photovoltaic Specialist Conference (PVSC), New Orleans, LA, USA, 14–19 June 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Zhou, Z.; Li, L. Isolated Sepic Three-Level DC-DC converter. In Proceedings of the 2011 6th IEEE Conference on Industrial Electronics and Applications, Beijing, China, 21–23 June 2011; pp. 2162–2165. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Soltani, M.; Blaabjerg, F.; Mostaan, A. A novel quasi-SEPIC high-voltage boost DC-DC converter. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 2213–2216. [Google Scholar] [CrossRef]

- Park, K.; Moon, G.; Youn, M. Nonisolated High Step-up Boost Converter Integrated With Sepic Converter. IEEE Trans. Power Electron. 2010, 25, 2266–2275. [Google Scholar] [CrossRef]

- Rashmi Manohar, J.; Rajesh, K.S. A comparative study and performance analysis of synchronous SEPIC Converter and synchronous Zeta Converter by using PV system with MPPT technique. In Proceedings of the 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Delhi, India, 4–6 July 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Suryoatmojo, H.; Dilianto, I.; Suwito; Mardiyanto, R.; Setijadi, E.; Riawan, D.C. Design and analysis of high gain modified SEPIC converter for photovoltaic applications. In Proceedings of the 2018 IEEE International Conference on Innovative Research and Development (ICIRD), Bangkok, Thailand, 11–12 May 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Kaouane, M.; Boukhelifa, A.; Cheriti, A. Design of a synchronous sepic DC-DC converter for a stand-alone photovoltaic system. In Proceedings of the 2015 IEEE 28th Canadian Conference on Electrical and Computer Engineering (CCECE), Halifax, NS, Canada, 3–6 May 2015; pp. 870–874. [Google Scholar] [CrossRef]

- Verma, M.; Kumar, S.S. Hardware Design of SEPIC Converter and its Analysis. In Proceedings of the 2018 International Conference on Current Trends towards Converging Technologies (ICCTCT), Coimbatore, India, 1–3 March 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Maheshwari, M.; Arounassalame, M. Control of Integrated Quadratic Boost Sepic Converter for High Gain Applications. In Proceedings of the 2019 Fifth International Conference on Science Technology Engineering and Mathematics (ICONSTEM), Chennai, India, 14–15 March 2019; pp. 348–353. [Google Scholar] [CrossRef]

- Soedibyo; Amri, B.; Ashari, M. The comparative study of Buck-boost, Cuk, Sepic and Zeta converters for maximum power point tracking photovoltaic using P&O method. In Proceedings of the 2015 2nd International Conference on Information Technology, Computer, and Electrical Engineering (ICITACEE), Semarang, Indonesia, 16–18 October 2015; pp. 327–332. [Google Scholar] [CrossRef]

- Chandran, A.; Reshmi, V.; Mathew, B.K. Comparative Analysis of P&O and FLC based SEPIC Boost Converter for Solar PV Application. In Proceedings of the 2020 Third International Conference on Smart Systems and Inventive Technology (ICSSIT), Tirunelveli, India, 20–22 August 2020; pp. 616–621. [Google Scholar] [CrossRef]

- Massey, R.P.; Snyder, E.C. High voltage single-ended DC-DC converter. In Proceedings of the 1977 IEEE Power Electronics Specialists Conference, Palo Alto, CA, USA, 14–16 June 1977; pp. 156–159. [Google Scholar] [CrossRef]

- Ioinovici, A. Power Electronics and Energy Conversion Systems-Fundamentals and Hard-Switching Converters, 1st ed.; John Wiley & Sons, Ltd.: Hoboken, NJ, USA, 2013. [Google Scholar]

- Pop-Calimanu, I.-M.; Balint, M.; Lascu, D. A New Hybrid Ćuk DC-DC Converter with Coupled Inductors. Electronics 2020, 9, 2188. [Google Scholar] [CrossRef]

- Pop-Calimanu, I.-M.; Lica, S.; Popescu, S.; Lascu, D.; Lie, I.; Mirsu, R. A New Hybrid Inductor-Based Boost DC-DC Converter Suitable for Applications in Photovoltaic Systems. Energies 2019, 12, 252. [Google Scholar] [CrossRef] [Green Version]

- Jude, G.-M.; Pop-Calimanu, I.-M.; Renken, F. A New Step-Up Converter with Coupled Inductor. In Proceedings of the 2020 International Symposium on Electronics and Telecommunications (ISETC), Timisoara, Romania, 5–6 November 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Renken, F.; Schürmann, U.; Chen, Q.; Pop-Calimanu, I.-M. Novel hybrid buck L converter for wide conversion ratios. In Proceedings of the 2016 IEEE International Power Electronics and Motion Control Conference (PEMC), Varna, Bulgaria, 25–28 September 2016; pp. 158–167. [Google Scholar] [CrossRef]

- CASPOC. Online Manuals. Available online: http://www.caspoc.com/support/manuals/ (accessed on 10 May 2021).

- ADuCino 360. Datasheet. Available online: https://kamami.com/analog-devices/208971-aducino-360.html (accessed on 10 May 2021).

- LEM HO-8-NSM/SP33. Datasheet. Available online: https://www.lem.com/sites/default/files/products_datasheets/ho-nsm_sp33-1000_series.pdf (accessed on 10 May 2021).

- Irradiance and Temperature Sensor SI-12TC. Datasheet. Available online: http://www.renewpowers.com/datasheets/METEO%20CONTROL/meteocontrol_Si12TC_DataSheet_en.pdf (accessed on 10 May 2021).

| Parameter | Type of Converter | ||

|---|---|---|---|

| Classical Buck-Boost [13] | Classical Nonisolated SEPIC [13] | Hybrid SEPIC [24] | |

| Switches | 1 | 1 | 1 |

| Diodes | 1 | 1 | 4 |

| No. of cores/windings | 1/1 | 2/2 | 3/3 |

| Total no. of components | 4 | 6 | 10 |

| System order | 2 | 4 | 5 |

| Static conversion ratio-M | |||

| Duty cycle-D | |||

| Switch current stress | |||

| Switch voltage stress | |||

| Maximum diode dc current stress | |||

| Maximum diode voltage stress | |||

| Parameter | Type of Converter | ||

| Proposed Hybrid SEPIC | |||

| Switches | 1 | ||

| Diodes | 3 | ||

| No. of cores/windings | 2/3 | ||

| Total no. of components | 8 | ||

| System order | 4 | ||

| Static conversion ratio-M | |||

| Duty cycle-D | |||

| Switch current stress | |||

| Switch voltage stress | |||

| Maximum diode dc current stress | |||

| Maximum diode voltage stress | |||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pop-Calimanu, I.-M.; Popescu, S.; Lascu, D. A New SEPIC-Based DC-DC Converter with Coupled Inductors Suitable for High Step-Up Applications. Appl. Sci. 2022, 12, 178. https://doi.org/10.3390/app12010178

Pop-Calimanu I-M, Popescu S, Lascu D. A New SEPIC-Based DC-DC Converter with Coupled Inductors Suitable for High Step-Up Applications. Applied Sciences. 2022; 12(1):178. https://doi.org/10.3390/app12010178

Chicago/Turabian StylePop-Calimanu, Ioana-Monica, Sorin Popescu, and Dan Lascu. 2022. "A New SEPIC-Based DC-DC Converter with Coupled Inductors Suitable for High Step-Up Applications" Applied Sciences 12, no. 1: 178. https://doi.org/10.3390/app12010178

APA StylePop-Calimanu, I.-M., Popescu, S., & Lascu, D. (2022). A New SEPIC-Based DC-DC Converter with Coupled Inductors Suitable for High Step-Up Applications. Applied Sciences, 12(1), 178. https://doi.org/10.3390/app12010178