A Survey on Dynamic Corrective Control of Asynchronous Sequential Machines

Abstract

:1. Introduction

- (i)

- Supervisors for DESs receive traces of inputs (or events) so as to generate commands specifying whether the current (controllable) input be enabled or disabled. Hence a supervisor cannot enlarge the controlled behavior of a DES; the supervisor can only curtail it to meet a given specification. On the other hand, since a corrective controller generates its own control input sequences while suppressing the current external input, it can provide the controlled ASM with new stable-state behaviors that otherwise could not be displayed.

- (ii)

- Rather than using the method of formal languages, corrective control theory exploits transition equivalence in evaluating the success of control goals. In the case of model matching, for example, the stable-state behavior of the closed-loop system is deemed to be matched with that of the reference model if, staying at the same state, they move to the same next stable state in response to a common input. In this sense, the control specification of corrective control is stricter than supervisory control.

- (iii)

- Although having a conceptual similarity to corrective control, supervisory control cannot be applied to controlling ASMs since it does not consider intrinsic characteristics of ASMs such as discrimination between stable and transient states and abiding by the principle of fundamental mode operations.

2. Mathematical Formulation of Corrective Control

2.1. Modeling of ASMs

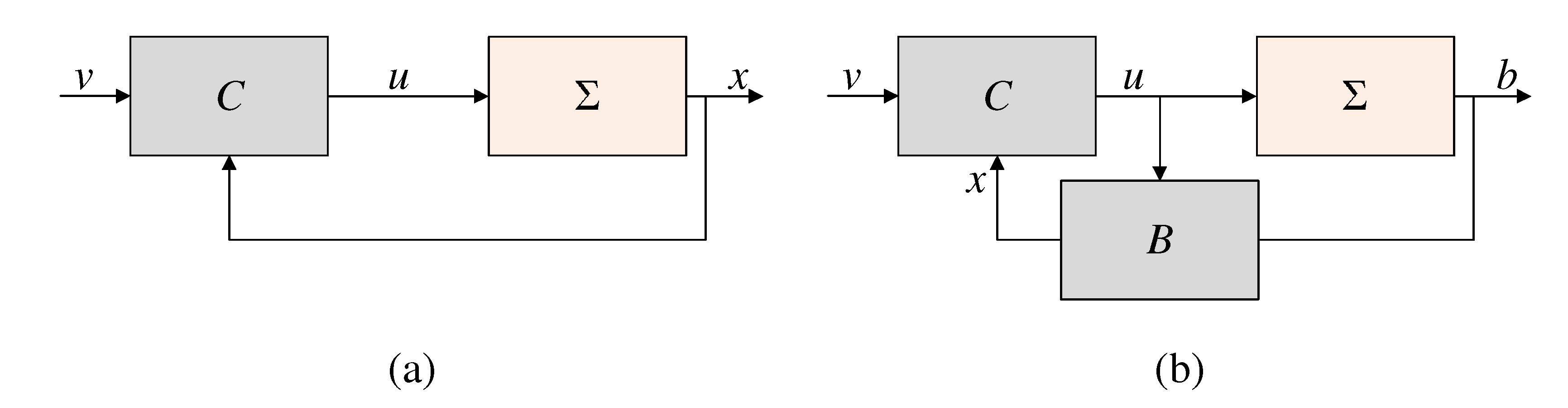

2.2. Closed-Loop System

- (a)

- When one of B, C, and Σ changes its output or undertakes state transitions, the others must maintain their stable states.

- (b)

- The external input v must remain unchanged when either of B, C, or Σ is under transient transitions.

3. Stable Reachability and Detectability

3.1. Stable Reachability of Input/State ASMs

3.2. Detectability and Stable Reachability of Input/Output ASMs

4. Model Matching Control

4.1. Model Matching for Input/State ASMs

4.2. Model Matching for Input/Output ASMs

4.3. Model Matching for Composite ASMs

5. Fault-Tolerant Control

5.1. Transient Faults

5.2. Permanent Faults and Intermittent Faults

5.3. Intelligent and Cyber Attacks

5.4. Applications to Space-Borne Digital Systems

6. Conclusions and Future Studies

- (i)

- It is anticipated that fault-tolerant corrective control schemes can be further developed by presenting dominant cyber attacks, e.g., false data injection attacks [108,109,110] and denial of service (DoS) attacks [111,112,113], to the configuration of the corrective control system in a more practical way. To this end, previous research on network attacks in cyber-physical systems (CPSs) [114,115,116] must be incorporated into corrective control theory.

- (ii)

- Though many convincing experimental evaluations of corrective controllers exist, there is still a lack of application studies which validate that asynchronous digital systems embedded with the corrective controller show fault-hardening ability [117,118,119] against real radiation-related faults. For this purpose, radiation exposure experiments [120] on the implemented corrective control systems must be conducted.

- (iii)

- All previous researches on dynamic corrective control aim at controlling ASMs only. However, synchronous sequential machines comprise the majority of existing digital systems. Hence, it would represent trailblazing work if a novel corrective control methodology is developed that can improve the behavior of synchronous sequential machines, possibly under the globally asynchronous locally synchronous (GALS) architecture [121,122,123].

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Huffman, D.A. The synthesis of sequential switching circuits. J. Frank. Inst. 1954, 257, 161–190. [Google Scholar] [CrossRef] [Green Version]

- Whitaker, S.R.; Maki, G.K. Pass-transistor asynchronous sequential circuits. IEEE J. Solid-State Circuits 1989, 24, 71–78. [Google Scholar] [CrossRef]

- Wu, S.-F.; Fisher, P.D. Automating the design of asynchronous sequential logic circuits. IEEE J. Solid-State Circuits 1991, 26, 364–370. [Google Scholar] [CrossRef]

- Hauck, S. Asynchronous design methodologies: An overview. Proc. IEEE 1995, 83, 69–93. [Google Scholar] [CrossRef] [Green Version]

- Sparsø, J.; Furber, S. Principles of Asynchronous Circuit Design—A Systems Perspective; Kluwer Academic Publishers: Boston, MA, USA, 2002. [Google Scholar]

- Martin, A.J.; Nyström, M. Asynchronous techniques for system-on-chip design. Proc. IEEE 2006, 94, 1089–1120. [Google Scholar] [CrossRef] [Green Version]

- Beerel, P.A.; Ozdag, R.O.; Ferretti, M. A Designer’s Guide to Asynchronous VLSI; Cambridge University Press: Cambridge, UK, 2010. [Google Scholar]

- Fisher, P.D.; Wu, S.-F. Race-free state assignments for synthesizing large-scale asynchronous sequential logic circuits. IEEE Trans. Comput. 1993, 42, 1025–1034. [Google Scholar] [CrossRef]

- Chu, T.A. Synthesis of hazard-free control circuits from asynchronous finite state machines specifications. J. VLSI Signal Process. Syst. Signal Image Video Technol. 1994, 7, 61–84. [Google Scholar] [CrossRef]

- Unger, S.H. Hazards, critical races, and metastability. IEEE Trans. Comput. 1995, 44, 754–768. [Google Scholar] [CrossRef]

- Bychko, V.; Yershov, R.; Gulyi, Y.; Zhydko, M. Automation of anti-race state encoding of asynchronous FSM for robust systems. In Proceedings of the 2020 IEEE International Conference on Problems of Infocommunications, Science and Technology, Kharkiv, Ukraine, 6–9 October 2020; pp. 501–506. [Google Scholar]

- Hammer, J. On the corrective control of sequential machines. Int. J. Control 1996, 65, 249–276. [Google Scholar] [CrossRef]

- Hammer, J. On the control of incompletely described sequential machines. Int. J. Control 1996, 63, 1005–1028. [Google Scholar] [CrossRef]

- Hammer, J. On the control of sequential machines with disturbances. Int. J. Control 1997, 67, 307–331. [Google Scholar] [CrossRef]

- Hammer, J. Controlling sequential machines with disturbances. In Proceedings of the 1997 American Control Conference, Albuquerque, NM, USA, 6 June 1997; pp. 2184–2188. [Google Scholar]

- Murphy, T.E. On the Control of Asynchronous Sequential Machines with Races. Ph.D. Thesis, University of Florida, Gainesville, FL, USA, 1996. [Google Scholar]

- Fujimori, A. Optimization of static output feedback using substitutive LMI formulation. IEEE Trans. Autom. Control 2004, 49, 995–999. [Google Scholar] [CrossRef]

- Bara, G.; Boutayeb, M. Static output feedback stabilization with H∞ performance for linear discrete-time systems. IEEE Trans. Autom. Control 2005, 50, 250–254. [Google Scholar] [CrossRef]

- Li, X.; Gao, H. A heuristic approach to static output-feedback controller synthesis with restricted frequency-domain specifications. IEEE Trans. Autom. Control 2013, 59, 1008–1014. [Google Scholar] [CrossRef]

- Wang, B.; Feng, J.E. A matrix approach for the static correction problem of asynchronous sequential machines. Int. J. Control. Autom. Syst. 2020, 18, 477–485. [Google Scholar] [CrossRef]

- Ramadge, P.J.; Wonham, W.M. The control of discrete event systems. Proc. IEEE 1989, 77, 81–98. [Google Scholar] [CrossRef]

- Shu, S.; Lin, F.; Ying, H. Detectability of discrete event systems. IEEE Trans. Autom. Control 2007, 52, 2356–2359. [Google Scholar] [CrossRef]

- Cassandras, C.G.; Lafortune, S. Introduction to Discrete Event Systems, 2nd ed.; Springer: New York, NY, USA, 2008. [Google Scholar]

- Shu, S.; Lin, F. I-detectability of discrete-event systems. IEEE Trans. Autom. Sci. Eng. 2013, 10, 187–196. [Google Scholar] [CrossRef]

- Zhang, J.; Khalgui, M.; Li, Z.; Frey, G.; Mosbahi, O.; Salah, H.B. Reconfigurable coordination of distributed discrete event control systems. IEEE Trans. Control Syst. Technol. 2015, 23, 323–330. [Google Scholar] [CrossRef]

- Wonham, W.M.; Cai, K. Supervisory Control of Discrete-Event Systems; Springer: Cham, Switzerland, 2019. [Google Scholar]

- Murphy, T.E.; Geng, X.; Hammer, J. Controlling races in asynchronous sequential machines. In Proceedings of the 15th Triennial World Congress, Barcelona, Spain, 21–26 July 2002; pp. 67–72. [Google Scholar]

- Murphy, T.E.; Geng, X.; Hammer, J. On the control of asynchronous machines with races. IEEE Trans. Autom. Control 2003, 48, 1073–1081. [Google Scholar] [CrossRef] [Green Version]

- Geng, X. Model Matching for Asynchronous Sequential Machines. Ph.D. Thesis, University of Florida, Gainesville, FL, USA, 2003. [Google Scholar]

- Geng, X.; Hammer, J. Asynchronous sequential machines: Input/output control. In Proceedings of the 12th Mediterranean Conference on Control and Automation, Kusadasi, Turkey, 6–9 June 2004. [Google Scholar]

- Geng, X.; Hammer, J. Input/output control of asynchronous sequential machines. IEEE Trans. Autom. Control 2005, 50, 1956–1970. [Google Scholar] [CrossRef]

- Eilenberg, S. Automata, Languages, and Machines; Academic Press: New York, NY, USA, 1974. [Google Scholar]

- Kohavi, Z.; Jha, Z. Switching and Finite Automata Theory, 3rd ed.; Cambridge University Press: Cambridge, UK, 2010. [Google Scholar]

- Rey, C.A.; Vaucher, J. Self-synchronized asynchronous sequential machines. IEEE Trans. Comput. 1974, C-23, 1306–1311. [Google Scholar] [CrossRef]

- Renaudin, M. Asynchronous circuits and systems: A promising design alternative. Microelectron. Eng. 2000, 54, 133–149. [Google Scholar] [CrossRef]

- Cheng, D.; Qi, H.; Li, Z. Analysis and Control of Boolean Networks: A Semi-Tensor Product Approach; Springer Science & Business Media: London, UK, 2011. [Google Scholar]

- Cheng, D.; Qi, H.; Li, Z.; Liu, J.B. Stability and stabilization of Boolean networks. Int. J. Robust Nonlinear Control 2011, 21, 134–156. [Google Scholar] [CrossRef] [Green Version]

- Yan, Y.; Chen, Z.; Liu, Z. Semi-tensor product approach to controllability and stabilizability of finite automata. J. Syst. Eng. Electron. 2015, 26, 134–141. [Google Scholar] [CrossRef]

- Lu, J.; Li, H.; Liu, Y.; Li, F. Survey on semi-tensor product method with its applications in logical networks and other finite-valued systems. IET Control Theory Appl. 2017, 11, 2040–2047. [Google Scholar] [CrossRef]

- Li, H.; Zhao, G.; Meng, M.; Feng, J. A survey on applications of semi-tensor product method in engineering. Sci. China Inf. Sci. 2018, 61, 1–17. [Google Scholar] [CrossRef] [Green Version]

- Chen, Z.; Zhou, Y.; Zhang, Z.; Liu, Z. Semi-tensor product of matrices approach to the problem of fault detection for discrete event systems (DESs). IEEE Trans. Circuits Syst. II Exp. Briefs 2020, 67, 3098–3102. [Google Scholar] [CrossRef]

- Zhang, Z.; Xia, C.; Chen, S.; Yang, T.; Chen, Z. Reachability analysis of networked finite state machine with communication losses: A switched perspective. IEEE J. Sel. Areas Commun. 2020, 38, 845–853. [Google Scholar] [CrossRef]

- Xu, X.; Hong, Y. Matrix approach and model matching of asynchronous sequential machines. IEEE Trans. Autom. Control 2013, 58, 2974–2979. [Google Scholar] [CrossRef]

- Wang, J.; Han, X.; Chen, Z.; Zhang, Q. Calculating skeleton matrix of asynchronous sequential machines based on the semi-tensor product of matrices. IET Control Theory Appl. 2017, 11, 2131–2139. [Google Scholar] [CrossRef]

- Wang, J.; Han, X.; Chen, Z.; Zhang, Q. Model matching of input/output asynchronous sequential machines based on the semi-tensor product of matrices. Future Gener. Comput. Syst. 2018, 83, 468–475. [Google Scholar] [CrossRef]

- Di Benedetto, M.D.; Sangiovanni-Vincentelli, A.; Villa, T. Model matching for finite-state machines. IEEE Trans. Autom. Control 2001, 11, 1726–1743. [Google Scholar] [CrossRef]

- Venkatraman, N.; Hammer, J. Stable realizations of asynchronous sequential machines with infinite cycles. In Proceedings of the 2006 Asian Control Conference, Bali, Indonesia, 18–21 July 2006; pp. 45–51. [Google Scholar]

- Venkatraman, N.; Hammer, J. Controllers for asynchronous sequential machines with infinite cycles. In Proceedings of the 17th International Symposium on the Mathematical Theory of Networks and Systems, Kyoto, Japan, 24–28 July 2006; pp. 1002–1007. [Google Scholar]

- Venkatraman, N.; Hammer, J. On the control of asynchronous sequential machines with infinite cycles. Int. J. Control 2006, 79, 764–785. [Google Scholar] [CrossRef]

- Yang, J.-M. State feedback control of asynchronous machines with nondeterministic models. IEEE Trans. Autom. Control 2009, 54, 1072–1076. [Google Scholar] [CrossRef]

- Yang, J.-M. Model matching inclusion for input/state asynchronous sequential machines. Automatica 2011, 47, 597–602. [Google Scholar] [CrossRef]

- Peng, J.; Hammer, J. Generalized realizations and output feedback control of asynchronous sequential machines with races. In Proceedings of the 2009 European Control Conference (ECC), Budapest, Hungary, 23–26 August 2009; pp. 892–897. [Google Scholar]

- Peng, J.; Hammer, J. Input/output control of asynchronous sequential machines with races. Int. J. Control 2010, 83, 125–144. [Google Scholar] [CrossRef]

- Peng, J.; Hammer, J. Output feedback and bursts: Overcoming uncertainty in asynchronous sequential machines. In Proceedings of the 8th IFAC Symposium on Nonlinear Control Systems, Bologna, Italy, 1–3 September 2010; pp. 1152–1157. [Google Scholar]

- Peng, J.; Hammer, J. Bursts and output feedback control of non-deterministic asynchronous sequential machines. Eur. J. Control 2012, 18, 286–300. [Google Scholar] [CrossRef] [Green Version]

- Yang, J.-M. Modeling and control of switched asynchronous sequential machines. IEEE Trans. Autom. Control 2016, 61, 2174–2719. [Google Scholar] [CrossRef]

- Wang, B.; Feng, J.E.; Meng, M. Model matching of switched asynchronous sequential machines via matrix approach. Int. J. Control 2019, 92, 2430–2440. [Google Scholar] [CrossRef]

- Yang, J.-M. Corrective control of composite asynchronous sequential machines under partial observation. IEEE Trans. Autom. Control 2016, 61, 473–478. [Google Scholar] [CrossRef]

- Wang, B.; Feng, J.E.; Meng, M. Matrix approach to model matching of composite asynchronous sequential machines. IET Control Theory Appl. 2017, 11, 2122–2130. [Google Scholar] [CrossRef]

- Kabore, R.; Wang, H. Design of fault diagnosis filters and fault-tolerant control for a class of nonlinear systems. IEEE Trans. Autom. Control 2001, 46, 1805–1810. [Google Scholar] [CrossRef]

- Gao, Z.; Cecati, C.; Ding, S.X. A survey of fault diagnosis and fault-tolerant techniques—Part I: Fault diagnosis with model-based and signal-based approaches. IEEE Trans. Ind. Electron. 2015, 62, 3757–3767. [Google Scholar] [CrossRef] [Green Version]

- Zhou, Z.; Zhong, M.; Wang, Y. Fault diagnosis observer and fault-tolerant control design for unmanned surface vehicles in network environments. IEEE Access 2019, 7, 173694–173702. [Google Scholar] [CrossRef]

- Sosnowski, J. Transient fault tolerance in digital systems. IEEE Micro 1994, 14, 24–35. [Google Scholar] [CrossRef]

- Krishina, C.M.; Shin, K.G. Real-Time Systems; McGraw-Hill: New York, NY, USA, 1997. [Google Scholar]

- Sengupta, A.; Kachave, D. Spatial and temporal redundancy for transient fault-tolerant datapath. IEEE Trans. Aerosp. Electron. Syst. 2018, 54, 1168–1183. [Google Scholar] [CrossRef]

- Maio, F.D.; Secchi, P.; Vantini, S.; Zio, E. Fuzzy c-means clustering of signal functional principal components for post-processing dynamic scenarios of a nuclear power plant digital instrumentation and control system. IEEE Trans. Reliab. 2011, 60, 415–425. [Google Scholar] [CrossRef] [Green Version]

- Rashvand, H.F.; Abedi, A.; Alcaraz-Calero, J.M.; Mitchell, P.D.; Mukhopadhyay, S.C. Wireless sensor systems for space and extreme environments: A review. IEEE Sens. J. 2014, 14, 3955–3970. [Google Scholar] [CrossRef]

- Yang, M.; Hua, G.; Feng, Y.; Gong, J. Fault-Tolerance Techniques for Spacecraft Control Computers; John Wiley & Sons: Singapore, 2017. [Google Scholar]

- Caron, P.; Inguimbert, C.; Artola, L.; Ecoffet, R.; Bezerra, F. Physical mechanisms of proton-induced single-event upset in integrated memory devices. IEEE Trans. Nucl. Sci. 2019, 66, 1404–1409. [Google Scholar] [CrossRef]

- Yang, J.-M.; Hammer, J. State feedback control of asynchronous sequential machines with adversarial inputs. Int. J. Control 2008, 81, 1910–1929. [Google Scholar] [CrossRef]

- Yang, J.-M.; Kwak, S.-W. Output feedback control of asynchronous sequential machines with disturbance inputs. Inf. Sci. 2014, 259, 87–99. [Google Scholar] [CrossRef]

- Feng, C.; Lu, Z.; Jantsch, A.; Zhang, M.; Xing, Z. Addressing transient and permanent faults in NoC with efficient fault-tolerant deflection router. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2013, 21, 1053–1066. [Google Scholar] [CrossRef] [Green Version]

- Mireshghallah, F.; Bakhshalipour, M.; Sadrosadati, M.; Sarbazi-Azad, H. Energy-efficient permanent fault tolerance in hard real-time systems. IEEE Trans. Comput. 2019, 68, 1539–1545. [Google Scholar] [CrossRef]

- Yang, J.-M. Fault tolerance in asynchronous sequential machines using output feedback control. IEEE Trans. Autom. Control 2012, 57, 1604–1609. [Google Scholar] [CrossRef]

- Syed, W.A.; Perinpanayagam, S.; Samie, M.; Jennions, I. A novel intermittent fault detection algorithm and health monitoring for electronic interconnections. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 400–406. [Google Scholar] [CrossRef] [Green Version]

- Cai, B.; Liu, Y.; Xie, M. A dynamic-bayesian-network-based fault diagnosis methodology considering transient and intermittent faults. IEEE Trans. Autom. Sci. Eng. 2017, 14, 276–285. [Google Scholar] [CrossRef]

- Yang, J.-M.; Kwak, S.-W. Fault tolerance in switched ASMs with intermittent faults. IET Control Theory Appl. 2017, 11, 1443–1449. [Google Scholar] [CrossRef]

- Bou-Harb, E.; Lucia, W.; Forti, N.; Weerakkody, S.; Ghani, N.; Sinopoli, B. Cyber meets control: A novel federated approach for resilient CPS leveraging real cyber threat intelligence. IEEE Commun. Mag. 2017, 55, 198–204. [Google Scholar] [CrossRef]

- Kwon, C.; Hwang, I. Reachability analysis for safety assurance of cyber-physical systems against cyber attacks. IEEE Trans. Autom. Control 2018, 63, 2272–2279. [Google Scholar] [CrossRef]

- Farivar, F.; Haghighi, M.S.; Jolfaei, A.; Alazab, M. Artificial intelligence for detection, estimation, and compensation of malicious attacks in nonlinear cyber-physical systems and industrial IoT. IEEE Trans. Ind. Inform. 2020, 16, 2716–2725. [Google Scholar] [CrossRef]

- Hammer, J. Defensive state feedback control of asynchronous sequential machines. In Proceedings of the 23rd Mediterranean Conference on Control and Automation (MED), Torremolinos, Spain, 16–19 June 2015; pp. 495–500. [Google Scholar]

- Hammer, J. Automatic defensive control of asynchronous sequential machines. Int. J. Control 2016, 89, 193–209. [Google Scholar] [CrossRef]

- Yang, J.-M.; Kwak, S.-W. State feedback corrective control with a self-repair scheme against transient faults. J. Frankl. Inst. 2021, 358, 8485–8505. [Google Scholar] [CrossRef]

- Niranjan, S.; Frenzel, J.F. A comparison of fault-tolerant state machine architectures for space-borne electronics. IEEE Trans. Reliab. 1996, 45, 109–113. [Google Scholar] [CrossRef]

- Campbell, A.; McDonald, P.; Ray, K. Single event upset rates in space. IEEE Trans. Nucl. Sci. 1992, 39, 1828–1835. [Google Scholar] [CrossRef]

- Karp, S.; Gilbert, B.K. Digital system design in the presence of single event upsets. IEEE Trans. Aerosp. Electron. Syst. 1993, 29, 310–316. [Google Scholar] [CrossRef]

- Dodd, P.E.; Massengill, L.W. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Cardarilli, G.C.; Ottavi, M.; Pontarelli, S.; Re, M.; Salsano, A. Fault tolerant solid state mass memory for space applications. IEEE Trans. Aerosp. Electron. Syst. 2005, 41, 1353–1372. [Google Scholar] [CrossRef]

- Gao, Z.; Zhu, J.; Han, R.; Xu, Z.; Ullah, A.; Reviriego, P. Design and implementation of configuration memory SEU-tolerant viterbi decoders in SRAM-based FPGAs. IEEE Trans. Nanotechnol. 2019, 18, 691–699. [Google Scholar] [CrossRef]

- Sterpone, L.; Violante, M. Analysis of the robustness of the TMR architecture in SRAM-based FPGAs. IEEE Trans. Nucl. Sci. 2005, 52, 1545–1549. [Google Scholar] [CrossRef]

- Legat, U.; Biasizzo, A.; Novak, F. SEU recovery mechanism for SRAM-based FPGAs. IEEE Trans. Nucl. Sci. 2012, 59, 2562–2571. [Google Scholar] [CrossRef]

- Gil-Tomás, D.; Gracia-Morán, J.; Baraza-Calvo, J.C.; Saiz-Adalid, L.J.; Gil-Vicente, P.J. Studying the effects of intermittent faults on a microcontroller. Microelectron. Reliab. 2012, 52, 2837–2846. [Google Scholar] [CrossRef] [Green Version]

- Singh, U.; Green, M. New structures for very high-frequency CMOS clock dividers. In Proceedings of the 2001 IEEE International Symposium on Circuits and Systems, Sydney, Australia, 6–9 May 2001; pp. 622–625. [Google Scholar]

- Lin, H.Y.; Hsu, S.S.H.; Chan, C.Y.; Jin, J.D.; Lin, Y.S. A wide locking-range frequency divider for LMDS applications. IEEE Trans. Circuits Syst. II Exp. Briefs 2007, 54, 750–754. [Google Scholar] [CrossRef] [Green Version]

- Bentoutou, Y. A real time EDAC system for applications onboard earth observation small satellites. IEEE Trans. Aerosp. Electron. Syst. 2012, 48, 648–657. [Google Scholar] [CrossRef]

- Gu, B.; Kim, S.; Lee, J.; Oh, S.; Chae, J. Development of flight model NEXTSat-1 on board computer (in Korean). In Proceedings of the 2016 Korean Society for Aeronautical and Space Sciences (KSAS) Fall Conference, Jeju, Korea, 16–18 November 2016; pp. 1074–1075. [Google Scholar]

- Burek, R.K. The near solid-state data recorders. Johns Hopkins APL Tech. Dig. 1998, 19, 235–240. [Google Scholar]

- Burlyaev, D.; Leuken, R. System fault-tolerance analysis of COTS-based satellite on-board computers. Microelectron. J. 2014, 45, 1335–1341. [Google Scholar] [CrossRef]

- He, G.; Zheng, S.; Jing, N. A hierarchical scrubbing technique for SEU mitigation on SRAM-based FPGAs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 2134–2145. [Google Scholar] [CrossRef]

- Sterpone, L.; Porrmann, M.; Hagemeyer, J. A novel fault tolerant and runtime reconfigurable platform for satellite payload processing. IEEE Trans. Comput. 2013, 62, 1508–1525. [Google Scholar] [CrossRef]

- Gu, B.; Kim, S.; Lee, J.; Oh, S. Design of mass memory unit in the NEXTSat-2 (in Korean). In Proceedings of the 2018 Korean Society for Aeronautical and Space Sciences (KSAS) Fall Conference, Jeju, Korea, 28 November–1 December 2018; pp. 1079–1980. [Google Scholar]

- Elias, M. Development of a low cost, fault tolerant, and highly reliable command and data handling computer (PulseTM). In Proceedings of the 19th Digital Avionics Systems Conference, Philadelphia, PA, USA, 7–13 October 2000; pp. 8B4/1–8B4/8. [Google Scholar]

- Carmichael, C.; Tseng, C.W. Correcting Single-Event Upsets in Virtex-4 FPGA Configuration Memory. Xilinx Application Notes XAPP1088 (vl.0). 2009. Available online: http://application-notes.digchip.com/077/77-43209.pdf (accessed on 5 January 2022).

- Herrera-Alzu, I.; Lopez-Vallejo, M. Design techniques for Xilinx virtex FPGA configuration memory scrubbers. IEEE Trans. Nucl. Sci. 2013, 60, 376–385. [Google Scholar] [CrossRef] [Green Version]

- Stoddard, A.; Gruwell, A.; Zabriskie, P.; Wirthlin, M.J. A hybrid approach to FPGA configuration scrubbing. IEEE Trans. Nucl. Sci. 2017, 64, 497–503. [Google Scholar] [CrossRef]

- Sterpone, L.; Violante, M.; Rezgui, S. An analysis based on fault injection of hardening techniques for SRAM-based FPGAs. IEEE Trans. Nucl. Sci. 2006, 53, 2054–2059. [Google Scholar] [CrossRef]

- Yang, J.-M.; Kwak, S.-W. Realizing fault-tolerant asynchronous sequential machines using corrective control. IEEE Trans. Control Syst. Technol. 2010, 18, 1457–1463. [Google Scholar] [CrossRef]

- Hu, L.; Wang, Z.; Han, Q.-L.; Liu, X. State estimation under false data injection attacks: Security analysis and system protection. Automatica 2018, 87, 176–183. [Google Scholar] [CrossRef] [Green Version]

- Guan, Y.; Ge, X. Distributed attack detection and secure estimation of networked cyber-physical systems against false data injection attacks and jamming attacks. IEEE Trans. Signal Inf. Process. Netw. 2018, 4, 48–59. [Google Scholar] [CrossRef] [Green Version]

- Musleh, A.S.; Chen, G.; Dong, Z.Y. A survey on the detection algorithms for false data injection attacks in smart grids. IEEE Trans. Smart Grid 2020, 11, 2218–2234. [Google Scholar] [CrossRef]

- Long, M.; Wu, C.-H.; Hung, J.Y. Denial of service attacks on network-based control systems: Impact and mitigation. IEEE Trans. Ind. Inform. 2005, 1, 85–96. [Google Scholar] [CrossRef]

- Aad, I.; Hubaux, J.; Knightly, E.W. Impact of denial of service attacks on Ad Hoc networks. IEEE/ACM Trans. Netw. 2008, 16, 791–802. [Google Scholar] [CrossRef] [Green Version]

- Zhang, X.-M.; Han, Q.-L.; Ge, X.; Ding, L. Resilient control design based on a sampled-data model for a class of networked control systems under denial-of-service attacks. IEEE Trans. Cybern. 2020, 50, 3616–3626. [Google Scholar] [CrossRef]

- Pasqualetti, F.; Dörfler, F.; Bullo, F. Attack detection and identification in cyber-physical systems. IEEE Trans. Autom. Control 2013, 58, 2715–2729. [Google Scholar] [CrossRef] [Green Version]

- Liu, Y.; Peng, Y.; Wang, B.; Yao, S.; Liu, Z. Review on cyber-physical systems. IEEE/CAA J. Autom. Sin. 2017, 4, 27–40. [Google Scholar] [CrossRef]

- Cao, L.; Jiang, X.; Zhao, Y.; Wang, S.; You, D.; Xu, X. A survey of network attacks on cyber-physical systems. IEEE Access 2020, 8, 44219–44227. [Google Scholar] [CrossRef]

- Lin, S.; Kim, Y.-B.; Lombardi, F. Design and performance evaluation of radiation hardened latches for nanoscale CMOS. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2011, 19, 1315–1319. [Google Scholar] [CrossRef]

- De Oliveira, D.A.G.G.; Pilla, L.L.; Santini, T.; Rech, P. Evaluation and mitigation of radiation-induced soft errors in graphics processing units. IEEE Trans. Comput. 2016, 65, 791–804. [Google Scholar] [CrossRef]

- Pagliarini, S.; Benites, L.; Martins, M.; Rech, P.; Kastensmidt, F. Evaluating architectural, redundancy, and implementation strategies for radiation hardening of FinFET integrated circuits. IEEE Trans. Nucl. Sci. 2021, 68, 1045–1053. [Google Scholar] [CrossRef]

- Kim, H.; Noh, S.J.; Kim, H.; Jeong, D.H.; Yang, K.; Kim, G.; Kang, Y.R. Photon activation analysis of NIST SRM sediment sample using the electron linear accelerator at Pohang Accelerator Laboratory. J. Radioanal. Nucl. Chem. 2018, 316, 1139–1144. [Google Scholar] [CrossRef]

- Krstic, M.; Grass, E.; Gürkaynak, F.K.; Vivet, P. Globally asynchronous, locally synchronous circuits: Overview and outlook. IEEE Des. Test. 2007, 24, 430–441. [Google Scholar] [CrossRef]

- Horak, M.N.; Nowick, S.M.; Carlberg, M.; Vishkin, U. A low-overhead asynchronous interconnection network for GALS chip multiprocessors. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2011, 30, 494–507. [Google Scholar] [CrossRef]

- Yoong, L.H.; Shaw, G.D.; Roop, P.S.; Salcic, Z. Synthesizing globally asynchronous locally synchronous systems with IEC 61499. IEEE Trans. Syst. Man Cybern. Part C Appl. Rev. 2012, 42, 1465–1477. [Google Scholar] [CrossRef]

| System | ASM Type | Fault Type | Result |

|---|---|---|---|

| Error counter [93,94,95,96] | Input/output | Transient fault | [71] |

| Input/state | Input constraint | ||

| Scrubbing scheduler | Input/output | Permanent fault | [83] |

| for memory [97,98,99] | Input/state | Attack to controller | |

| ROM controller [102] | Switched | Intermittent fault | [77] |

| Transient fault | |||

| TMR memory [90,106] | Input/state | Transient fault | [107] |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, J.-M.; Kwak, S.-W. A Survey on Dynamic Corrective Control of Asynchronous Sequential Machines. Appl. Sci. 2022, 12, 2562. https://doi.org/10.3390/app12052562

Yang J-M, Kwak S-W. A Survey on Dynamic Corrective Control of Asynchronous Sequential Machines. Applied Sciences. 2022; 12(5):2562. https://doi.org/10.3390/app12052562

Chicago/Turabian StyleYang, Jung-Min, and Seong-Woo Kwak. 2022. "A Survey on Dynamic Corrective Control of Asynchronous Sequential Machines" Applied Sciences 12, no. 5: 2562. https://doi.org/10.3390/app12052562