Current Context and Research Trends in Linear DC–DC Converters

Abstract

:1. Introduction

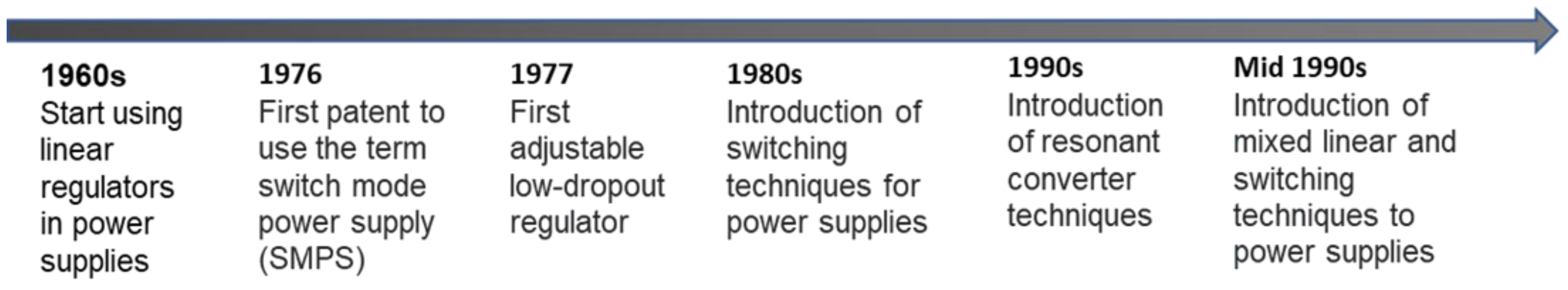

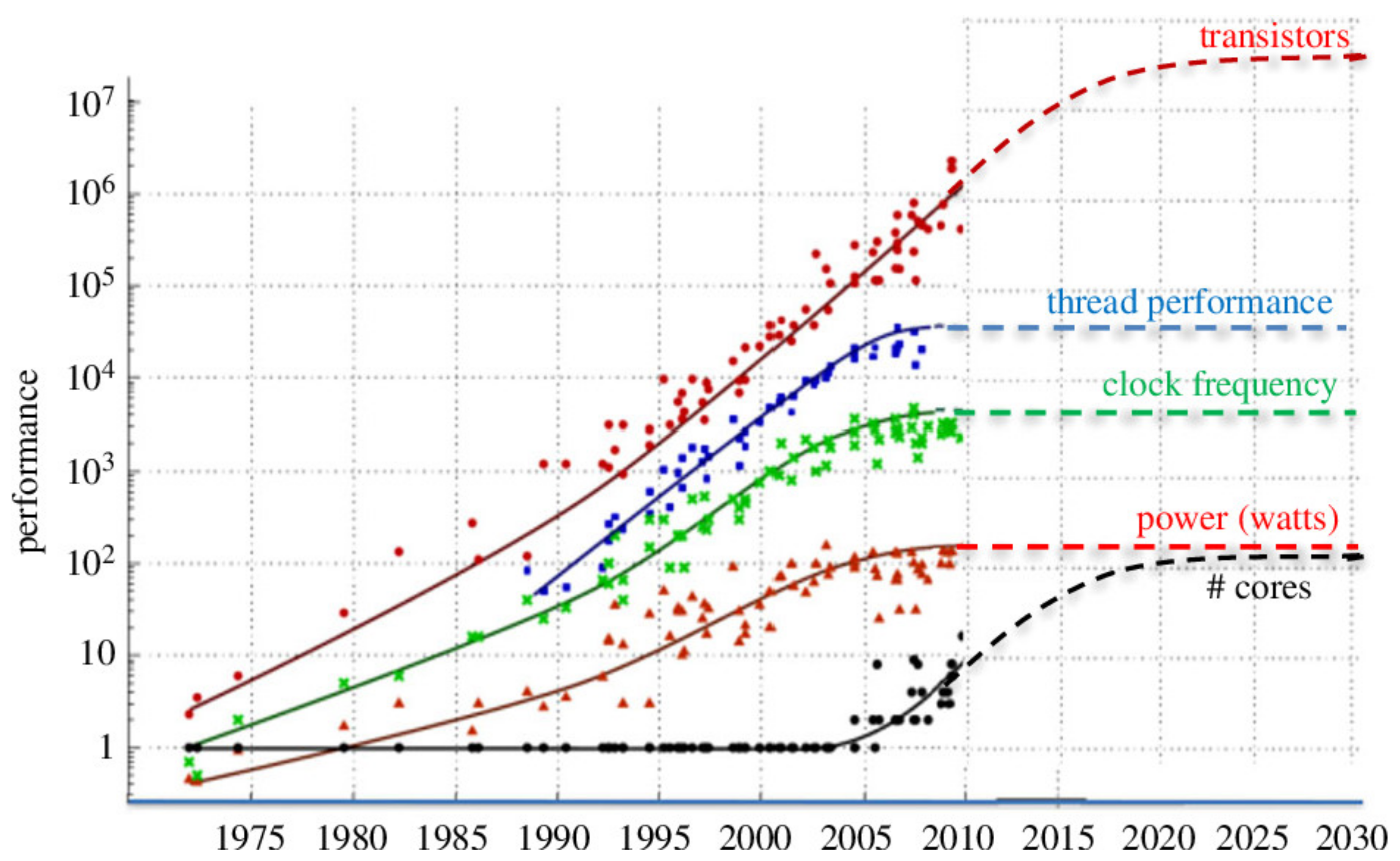

Evolution of Power Supply Design Technology

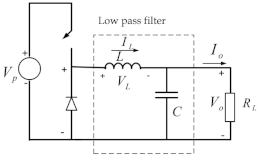

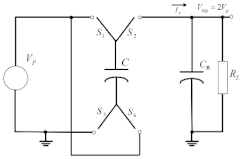

2. Switch Mode Power Supplies (SMPS)

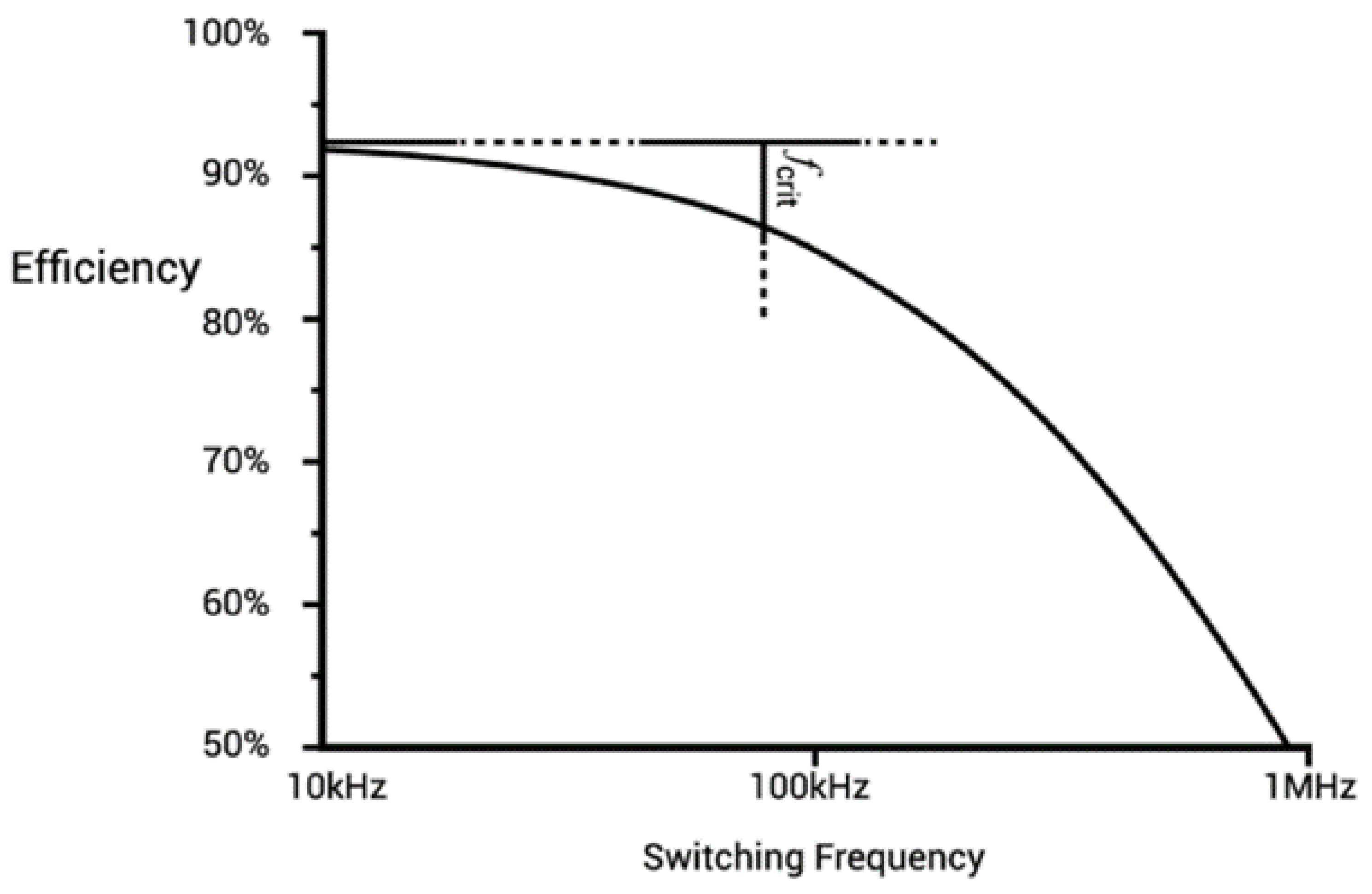

2.1. Issues with SMPS

2.1.1. Inductors and Transformers

2.1.2. Capacitors

2.1.3. Switch Elements

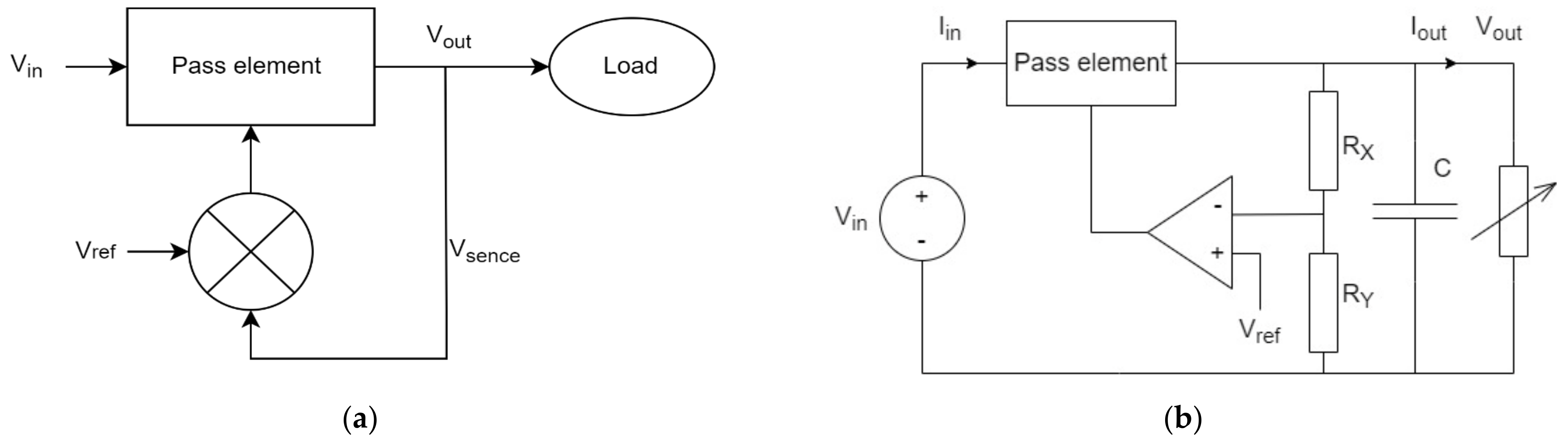

3. Linear/Low-Dropout Regulators Operating Principle

4. Dominant Characteristics of LDOs

4.1. Higher Efficiency

4.2. Low Noise

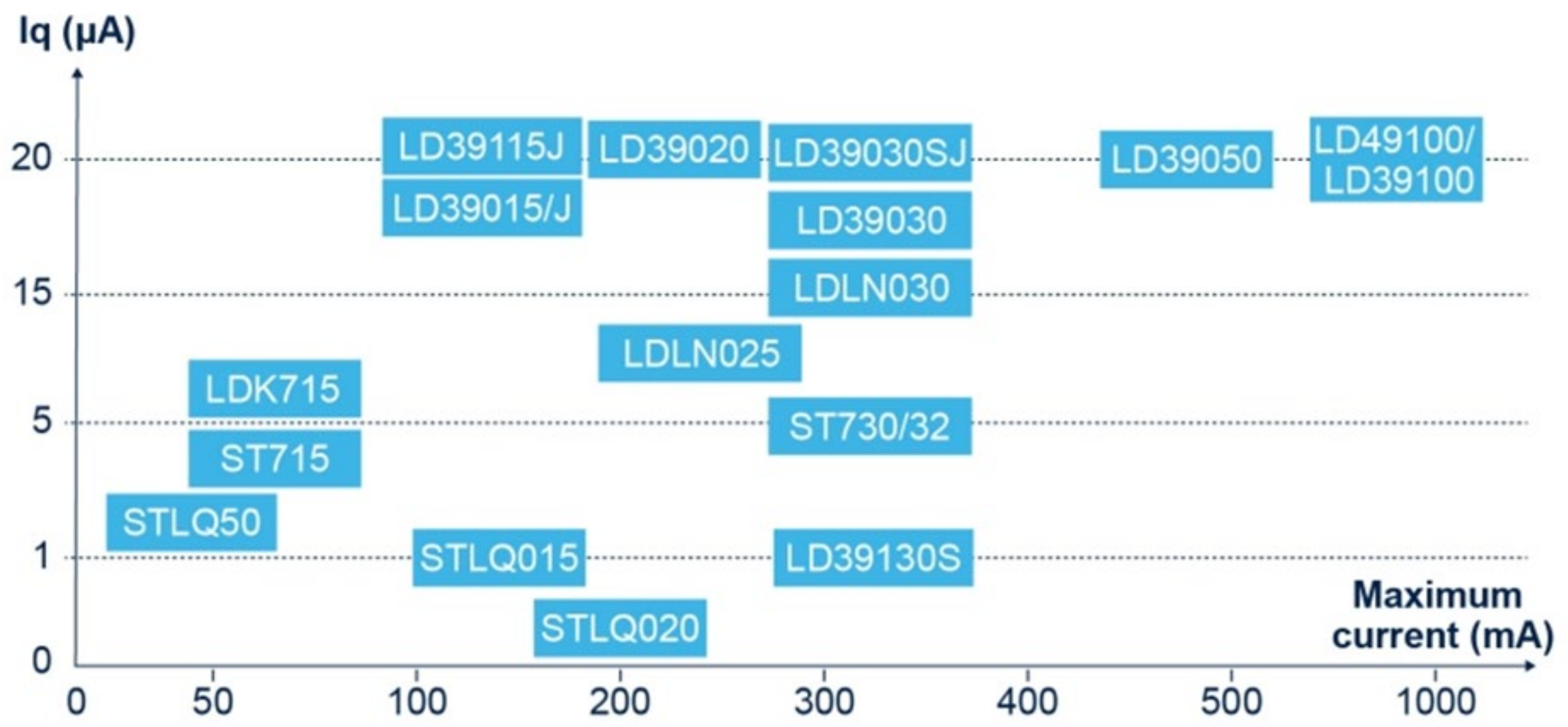

4.3. Low Quiescent Current

4.4. Better Transient Performances

4.5. Small Package Size

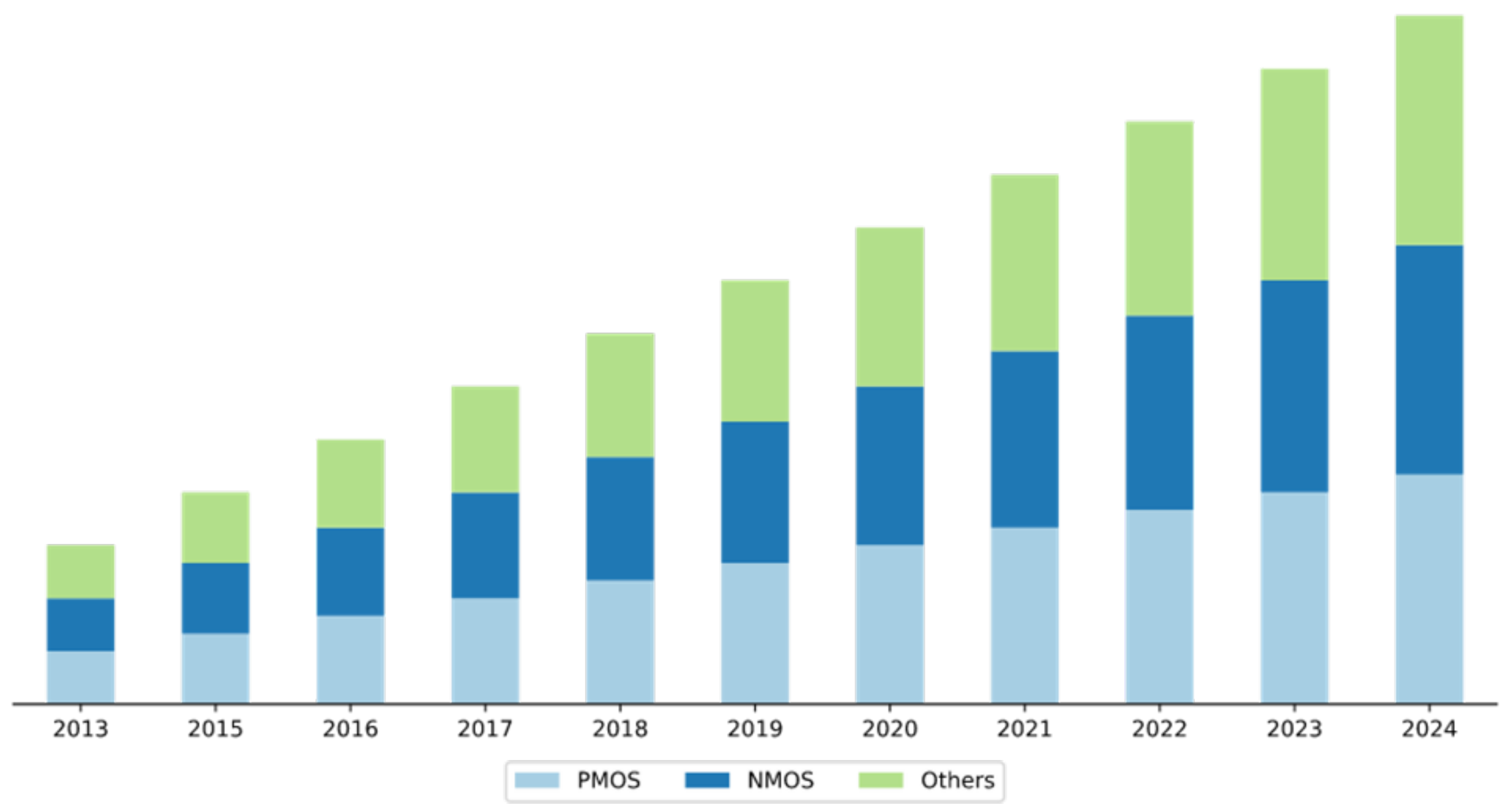

5. Current LDO Application Trends and Their Market Share

6. LDO’s Recent Research Trends

6.1. Improving the Compactness

6.2. Reducing Noise Levels Further

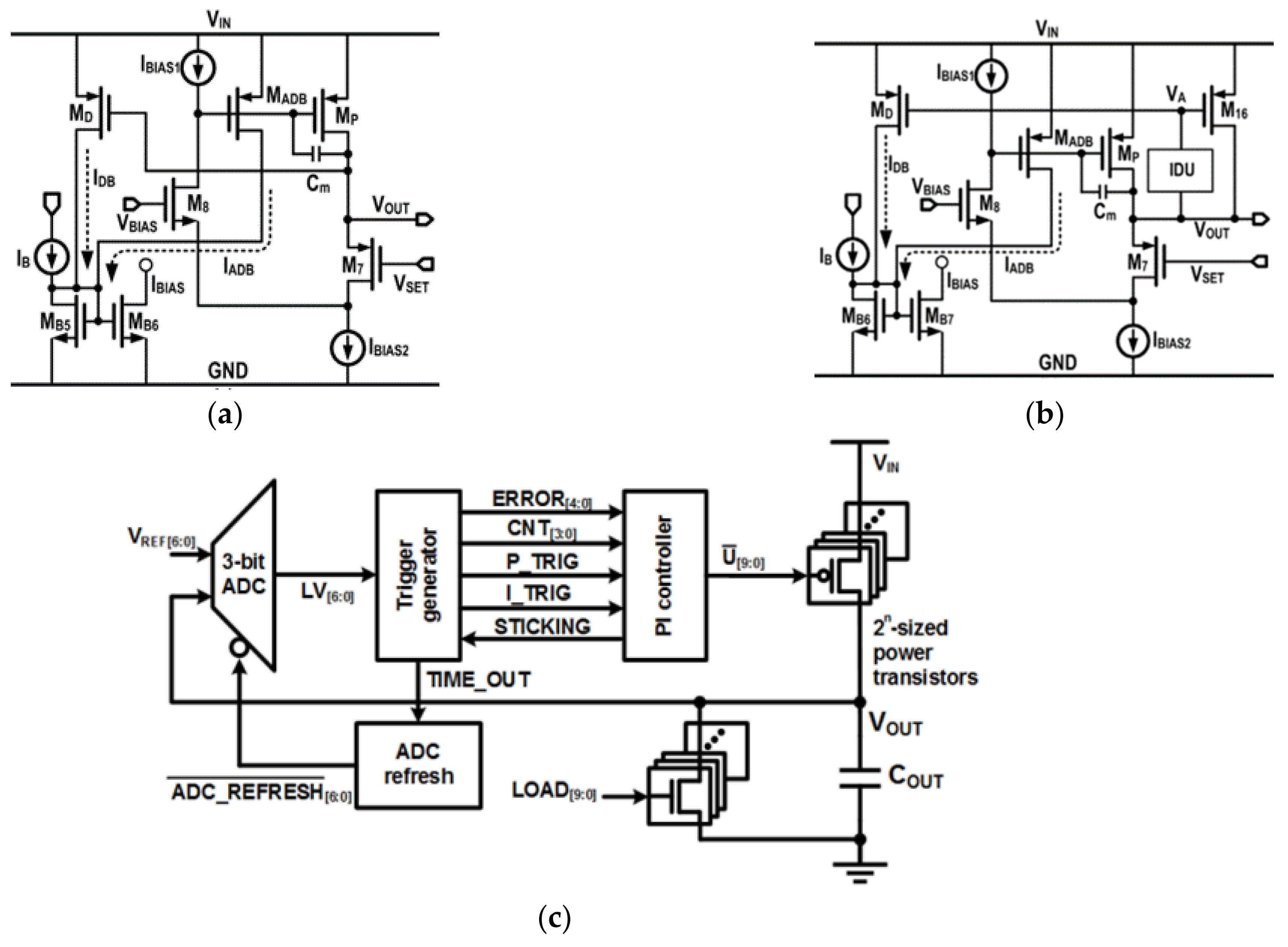

6.3. Improving the Transient Performance

6.4. Improving the Efficiency

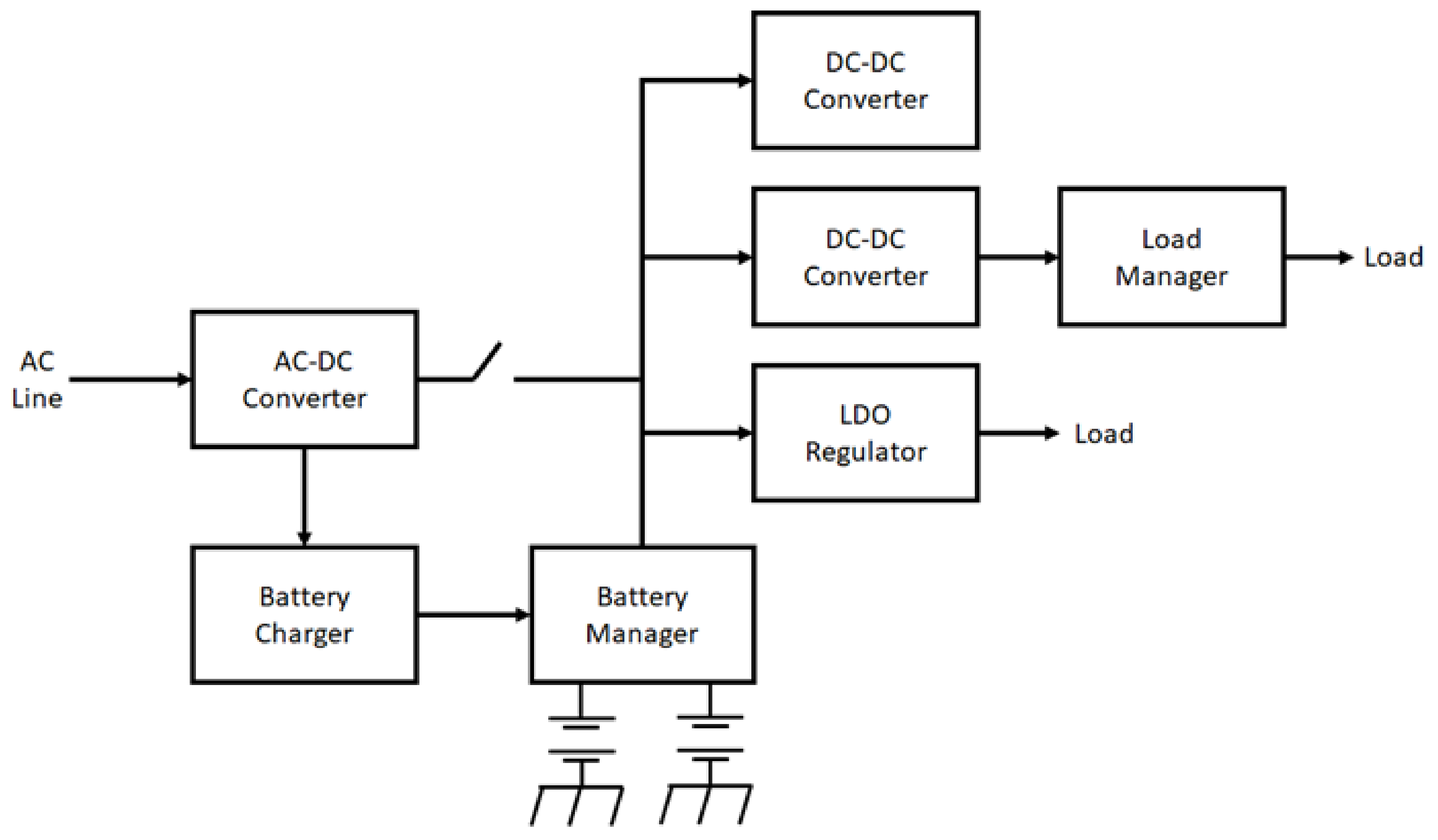

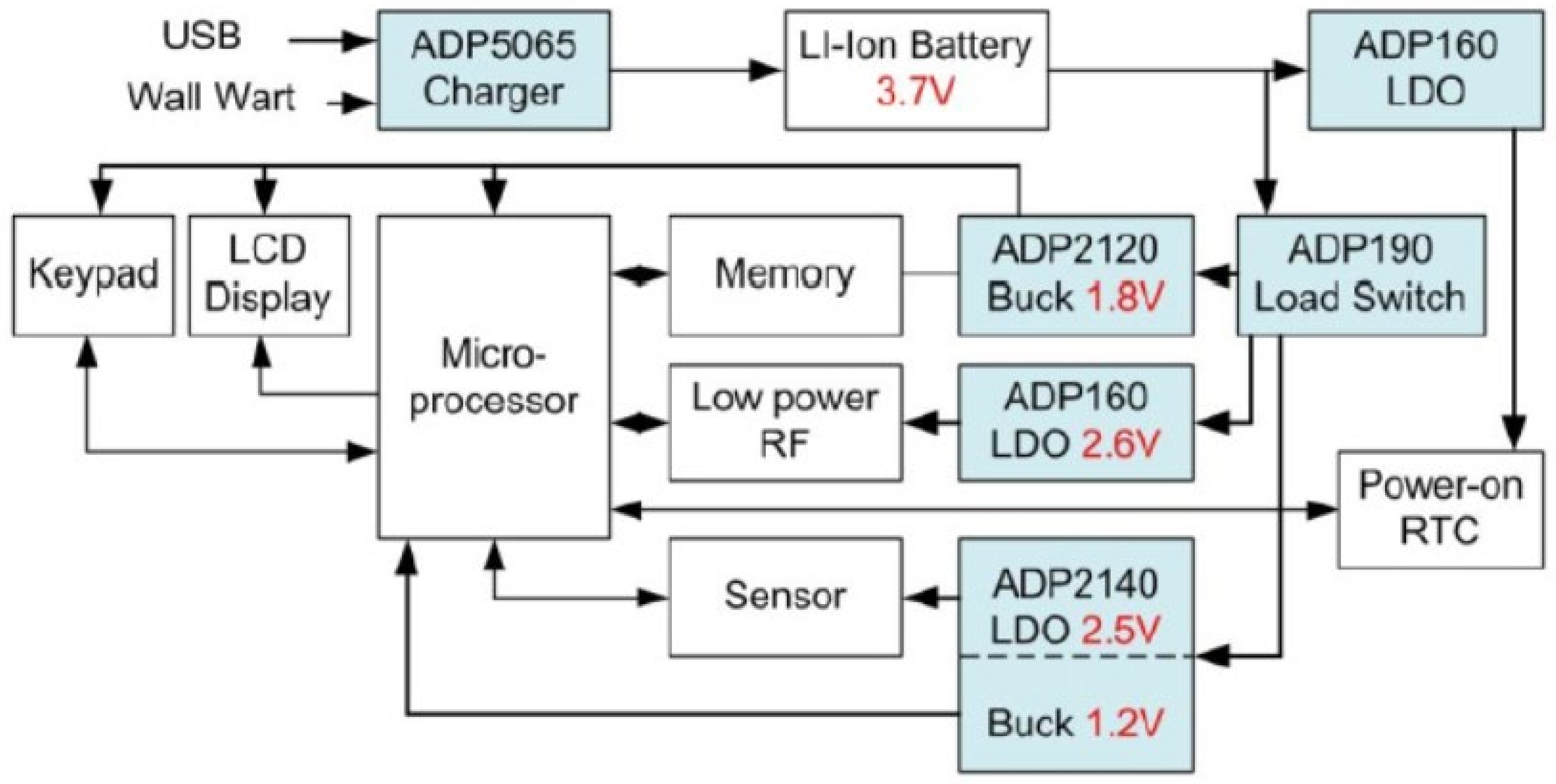

7. Current Context of Portable Power Supply Designs

- Variation of the current consumed by the subsystem.

- Fluctuation of the battery voltage in the portable device.

- Variations due to operating conditions of the device, such as temperature.

- Output rail voltage.

- Maximum load current.

- Output impedance of the power supply.

- Noise and ripple allowed.

- Input voltage range.

- Efficiency.

- Weight/volume of the power supply.

- Transient response capability and transient response.

- Radio frequency interference/electromagnetic interference (RFI/EMI).

- Reliability and the age of the power supply.

8. Future Prospects for LDO Regulators in Power Supplies

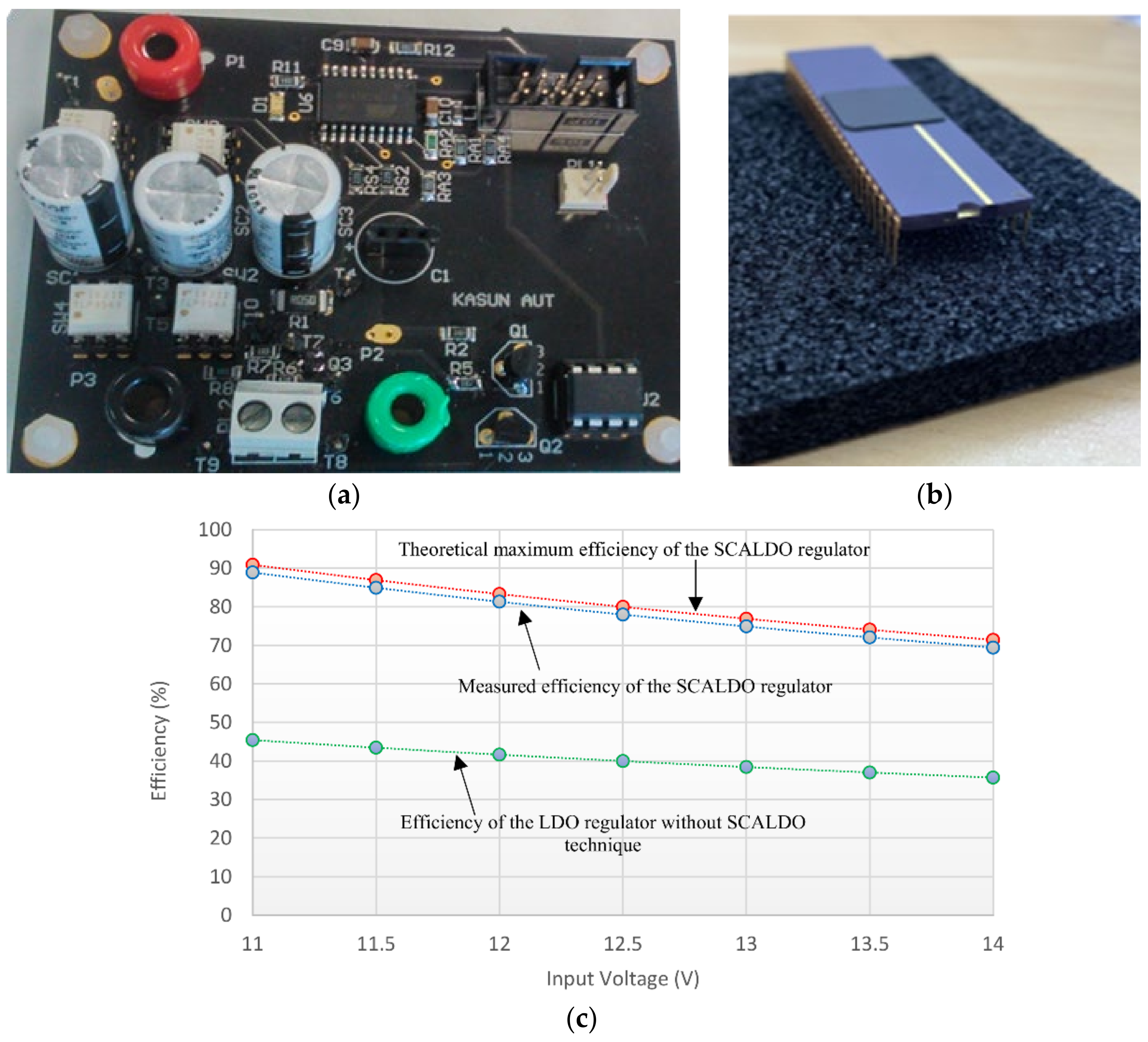

9. Supercapacitor-Assisted Low-Dropout Regulators (SCALDO) as a Solution to the Linear Regulator Efficiency Problem

9.1. Supercapacitors as Lossless Voltage Droppers

9.2. Concept of SCALDO

9.3. Advantages of Using SCALDO in Portable Devices

9.4. Limitations of SCALDO Technology

10. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Nomenclature

| SMPS | Switch-mode power supplies |

| SCC | Switched capacitor converters |

| PMS | Power management system |

| ESR | Equivalent series resistance |

| LDO | Low-dropout regulator |

| ETEE | End-to-end efficiency |

| POL | Point of load |

| SCALDO | Supercapacitor-assisted LDO |

| EMI | Electromagnetic interference |

| PSRR | Power supply rejection ratio |

| SC | Supercapacitor |

| Vref | Desired voltage in volts |

| Vout | Output voltage in volts |

| Iq | Current used by the control circuit in amps |

| Vin | Input voltage in volts |

| Vd | Dropout voltage in V |

| PD | Power consumption across LDO in watt |

| C | Capacitance in farads |

| dv | Voltage change |

| i(t) | Instantaneous current through the capacitor in amps |

| tcharging | Charging time in seconds |

| tdischarging | Discharging time in seconds |

| IAVG | Average current drawn from the unregulated power supply in amps |

References

- Darwish, M. Role of Semiconductor Devices in Portable Electronics Power Management. In IEE Colloquium on Recent Advances in Power Devices (Ref. No. 1999/104); IET: London, UK, 1999; pp. 1–4. [Google Scholar]

- Fernando, J. 5—Electrical Double-Layer Capacitors: Fundamentals, Characteristics, and Equivalent Circuits. In Energy Storage Devices for Electronic Systems; Kularatna, N., Ed.; Academic Press: Boston, MA, USA, 2015; pp. 149–186. ISBN 978-0-12-407947-2. [Google Scholar]

- Kularatna, N. DC Power Supplies: Power Management and Surge Protection for Power Electronic Systems; CRC Press: Boca Raton, FL, USA, 2018; ISBN 978-0-415-80248-2. [Google Scholar]

- Tuite, D. Inventor Updates a Classic 30 Years Later. 2007. Available online: https://www.electronicdesign.com/technologies/boards/article/21777220/inventor-updates-a-classic-30-years-later (accessed on 10 February 2022).

- Subasinghage, K.; Gunawardane, K.; Kularatna, N. Comparison of step-down charge pump converters and supercapacitor-assisted low- dropout (scaldo) regulators. In Proceedings of the TENCON 2021—2021 IEEE Region 10 Conference (TENCON), Auckland, New Zealand, 7–10 December 2021; pp. 299–304. [Google Scholar]

- Subasinghage, K.; Gunawardane, K.; Kularatna, N. Circuit Protection Techniques for Supercapacitor-Assisted Low-Dropout (SCALDO) Regulator. In Proceedings of the TENCON 2021—2021 IEEE Region 10 Conference (TENCON), Auckland, New Zealand, 7–10 December 2021; pp. 851–856. [Google Scholar]

- Xin, P.; Xue, J.; Mi, H. Research on Switch Power Supply Device. In Proceedings of the 2017 7th International Conference on Education, Management, Computer and Society (EMCS 2017), Shenyang, China, 17–19 March 2017. [Google Scholar]

- Mohan, N.; Undeland, T.M.; Robbins, W.P. Power Electronics: Converters, Applications, and Design; Wiley: Hoboken, NJ, USA, 1995; ISBN 978-0-471-58408-7. [Google Scholar]

- Femia, N.; Vitelli, M. Resistive losses of conductors carrying SMPS current waveforms. In Proceedings of the 2002 IEEE International Symposium on Industrial Electronics, L’Ayuila, Italy, 8–11 July 2002; Volume 9, pp. V-852–V-855. [Google Scholar]

- Rincon-Mora, G. Analog IC Design with Low-Dropout Regulators (LDOs), 1st ed.; McGraw-Hill, Inc.: New York, NY, USA, 2009; ISBN 978-0-07-160893-0. [Google Scholar]

- Zhang, H. Basic Concepts of Linear Regulator and Switching Mode Power Supplies 2013; Analog Devices: Norwood, MA, USA, 2013. [Google Scholar]

- Gunawardane, K. 6—Supercapacitor as a Lossless Dropper in DC-DC Converters. In Energy Storage Devices for Electronic Systems; Kularatna, N., Ed.; Academic Press: Boston, MA, USA, 2015; pp. 187–225. ISBN 978-0-12-407947-2. [Google Scholar]

- STMicroelectronics International N.V. 200 MA Very Low Quiescent Current Linear Regulator IC in (0.47 × 0.47) mm2 STSTAMPTM Package 2021; STMicroelectronics International N.V.: Geneva, Sitzerland, 2021. [Google Scholar]

- Texas Instruments. 1.5 A Low-Dropout Linear Regulator with Programmable Soft-Start 2020; Texas Instruments: Dallas, TX, USA, 2017. [Google Scholar]

- STMicroelectronics International N.V. 150 MA Low Quiescent Current and Low Noise Voltage Regulator, LD39015 2015; STMicroelectronics International N.V.: Geneva, Switzerland, 2015. [Google Scholar]

- Texas Instruments. TPS7A54 4-A, High-Accuracy (0.5%), Low-Noise (4.4 ΜVRMS), LDO Voltage Regulator 2020; Texas Instruments: Dallas, TX, USA, 2020. [Google Scholar]

- Texas Instruments. TLV752 Dual, 1-A, High-Accuracy, Adjustable-LDO in a Small-Size Package 2020; Texas Instruments: Dallas, TX, USA, 2020. [Google Scholar]

- Texas Instruments. TPS7A8101 Low-Noise, Wide-Bandwidth, High PSRR, Low-Dropout 1-A Linear Regulator 2015; Texas Instruments: Dallas, TX, USA, 2015. [Google Scholar]

- Texas Instruments. TPS74401 3.0-A, Ultra-LDO with Programmable Soft-Start 2017; Texas Instruments: Dallas, TX, USA, 2017. [Google Scholar]

- Nogawa, M. LDO Noise Examined in Detail 2012; Texas Instruments: Dallas, TX, USA, 2012. [Google Scholar]

- Low Quiescent Current (IQ) LDO Regulators—STMicroelectronics. Available online: https://www.st.com/en/power-management/low-iq-ldo-regulators.html (accessed on 6 February 2022).

- Texas Instruments. TPS57140-Q1 1.5-A 42-V Step-Down DC-DC Converter with Eco-ModeTM Control 2016; Texas Instruments: Dallas, TX, USA, 2016. [Google Scholar]

- Texas Instruments. Low-Noise, High-Bandwidth PSRR, Low-Dropout, 150-MA Linear Regulator 2006; Texas Instruments: Dallas, TX, USA, 2016. [Google Scholar]

- Texas Instruments. TPS720 350 MA, Ultra-Low VIN, RF Low-Dropout Linear Regulator With Bias Pin 2015; Texas Instruments: Dallas, TX, USA, 2015. [Google Scholar]

- Texas Instruments. TLV733P Capacitor-Free, 300-MA, Low-Dropout Regulator in 1-mm × 1-mm X2SON Package 2019; Texas Instruments: Dallas, TX, USA, 2019. [Google Scholar]

- Analog Devices. Ultralow Quiescent Current, 150 MA, CMOS Linear Regulators Data Sheet ADP160/ADP161/ADP162/ADP163 2013; Analog Devices: Norwood, MA, USA, 2013. [Google Scholar]

- Analog Devices. Ultralow Noise, 200 MA Linear Regulator Data Sheet ADM7160 2014; Analog Devices: Norwood, MA, USA, 2014. [Google Scholar]

- Texas Instruments. TPS7A19 40-V, 450-MA, Wide VIN, Low IQ, Low- Dropout Voltage Regulator with Power Good 2016; Texas Instruments: Dallas, TX, USA, 2016. [Google Scholar]

- Texas Instruments. TPS7B69xx-Q1 High-Voltage Ultra-Low IQ Low-Dropout Regulator 2015; Texas Instruments: Dallas, TX, USA, 2015. [Google Scholar]

- Analog Devices. 3µA IQ, 20mA Low Dropout Linear Regulators, LT3009 Series 2007; Analog Devices: Norwood, MA, USA, 2007. [Google Scholar]

- STLQ50—50 mA, 3 µA Supply Current Low Drop Linear Regulator—STMicroelectronics. Available online: https://www.st.com/en/power-management/stlq50.html (accessed on 7 February 2022).

- LDK715—High Input Voltage 85 MA LDO Linear Regulator—STMicroelectronics. Available online: https://www.st.com/en/power-management/ldk715.html (accessed on 7 February 2022).

- Gonzalez, J. Linear Power for Automated Industrial Systems; Texas Instruments: Dallas, TX, USA, 2017; p. 6. [Google Scholar]

- Zhang, Y.; Rasmussen, K. Detection of electromagnetic interference attacks on sensor systems. In Proceedings of the 2020 IEEE Symposium on Security and Privacy (SP), San Francisco, CA, USA, 18–21 May 2020; pp. 203–216. [Google Scholar]

- Holt, W. 1.1 Moore’s law: A path going forward. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016. [Google Scholar] [CrossRef]

- Shalf, J. The Future of Computing beyond Moore’s Law. Philos. Trans. R. Soc. A Math. Phys. Eng. Sci. 2020, 378, 20190061. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Low Dropout (LDO) Linear Regulators Market Research: Global Status & Forecast by Geography, Type & Application (2015–2025). Available online: https://marketintellica.com (accessed on 7 February 2022).

- Texas Instruments. TPS7A02 Nanopower IQ, 25-NA, 200-MA, Low-Dropout Voltage Regulator With Fast Transient Response 2020; Texas Instruments: Dallas, TX, USA, 2020. [Google Scholar]

- Nogawa, M. A Topical Index of TI LDO Application Notes 2019; Texas Instruments: Dallas, TX, USA, 2019. [Google Scholar]

- Man, T.Y.; Leung, K.N.; Leung, C.Y.; Mok, P.K.T.; Chan, M. Development of Single-Transistor-Control LDO Based on Flipped Voltage Follower for SoC. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 1392–1401. [Google Scholar] [CrossRef] [Green Version]

- Ho, M.; Guo, J.; Mak, K.H.; Goh, W.L.; Bu, S.; Zheng, Y.; Tang, X.; Leung, K.N. A CMOS Low-Dropout Regulator With Dominant-Pole Substitution. IEEE Trans. Power Electron. 2016, 31, 6362–6371. [Google Scholar] [CrossRef]

- Ahmed, F.U.; Sandhie, Z.T.; Chowdhury, M.H. An implementation of external capacitor-less low-dropout voltage regulator in 45 nm technology with output voltage ranging from 0.4 V–1.2 V. In Proceedings of the 2020 IEEE 38th International Conference on Computer Design (ICCD), Hartford, CT, USA, 18–21 October 2020; pp. 453–456. [Google Scholar]

- Liu, X.; Zhan, C.; Qiao, H. Chip-area-efficient capacitor-less LDO regulator with fast-transient response. In Proceedings of the 2019 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Chengdu, China, 13–15 November 2019; pp. 27–28. [Google Scholar]

- Li, Q.; Wang, K.; Zhao, J. A Capacitor-less LDO with fast transient response using push-pull buffer. In Proceedings of the 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi’an, China, 12–14 June 2019; pp. 1–3. [Google Scholar]

- Ho, M.; Leung, K.N.; Or, P.Y.; Guo, J. Analysis of CMOS low-dropout regulator—Power-supply rejection ratio. In Proceedings of the 2014 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Ishigaki, Japan, 17–20 November 2014; pp. 109–112. [Google Scholar]

- Park, J.-E.; Hwang, J.; Oh, J.; Jeong, D.-K. 32.4 A 0.4-to-1.2 V 0.0057 mm2 55 fs-transient-FoM ring-amplifier-based low-dropout regulator with replica-based PSR enhancement. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 492–494. [Google Scholar]

- Akram, M.A.; Hwang, I.-C.; Ha, S. Architectural Advancement of Digital Low-Dropout Regulators. IEEE Access 2020, 8, 137838–137855. [Google Scholar] [CrossRef]

- Ooishi, T.; Komiya, Y.; Hamade, K.; Asakura, M.; Yasuda, K.; Furutani, K.; Kato, T.; Hidaka, H.; Ozaki, H. A Mixed-Mode Voltage down Converter with Impedance Adjustment Circuitry for Low-Voltage High-Frequency Memories. IEEE J. Solid-State Circuits 1996, 31, 575–585. [Google Scholar] [CrossRef]

- Hazucha, P.; Moon, S.T.; Schrom, G.; Paillet, F.; Gardner, D.; Rajapandian, S.; Karnik, T. High Voltage Tolerant Linear Regulator With Fast Digital Control for Biasing of Integrated DC-DC Converters. IEEE J. Solid-State Circuits 2007, 42, 66–73. [Google Scholar] [CrossRef]

- Okuma, Y.; Ishida, K.; Ryu, Y.; Zhang, X.; Chen, P.-H.; Watanabe, K.; Takamiya, M.; Sakurai, T. 0.5-V input digital LDO with 98.7% current efficiency and 2.7-ΜA quiescent current in 65 nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference 2010, San Jose, CA, USA, 19–22 September 2010; pp. 1–4. [Google Scholar]

- Huang, M.; Lu, Y.; Martins, R.P. Review of Analog-Assisted-Digital and Digital-Assisted-Analog Low Dropout Regulators. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 24–29. [Google Scholar] [CrossRef]

- Yoon, K.-S.; Kim, H.-S.; Qu, W.; Yuk, Y.-S.; Cho, G.-H. Fully Integrated Digitally Assisted Low-Dropout Regulator for a NAND Flash Memory System. IEEE Trans. Power Electron. 2018, 33, 388–406. [Google Scholar] [CrossRef]

- Huang, Y.; Lu, Y.; Maloberti, F.; Martins, R.P. Nano-Ampere Low-Dropout Regulator Designs for IoT Devices. IEEE Trans. Circuits Syst. I: Regul. Pap. 2018, 65, 4017–4026. [Google Scholar] [CrossRef]

- Kim, D.; Seok, M. A Fully Integrated Digital Low-Dropout Regulator Based on Event-Driven Explicit Time-Coding Architecture. IEEE J. Solid-State Circuits 2017, 52, 3071–3080. [Google Scholar] [CrossRef]

- Cericola, D.; Novák, P.; Wokaun, A.; Kötz, R. Hybridization of Electrochemical Capacitors and Rechargeable Batteries: An Experimental Analysis of the Different Possible Approaches Utilizing Activated Carbon, Li4Ti5O12 and LiMn2O4. J. Power Sources 2011, 196, 10305–10313. [Google Scholar] [CrossRef]

- Israelsohn, J. Battery Management Included. EDN. 2001. Available online: https://www.edn.com/battery-management-included/ (accessed on 12 February 2022).

- Juzkow, M.W.; St. Louis, C. Designing Lithium-Ion Batteries into Today’s Portable Products. In Proceedings of the Portable by Design Conference, Santa Clara, CA, USA, 25–28 February 1996; pp. 13–22. [Google Scholar]

- Lopez, J.; Gonzalez, M.; Viera, J.C.; Blanco, C. Fast-charge in lithium-ion batteries for portable applications. In Proceedings of the INTELEC 2004 26th Annual International Telecommunications Energy Conference, Chicago, IL, USA, 19–23 September 2004; pp. 19–24. [Google Scholar]

- Dileepan, V.M.; Jayakumar, J. Performance analysis of lithium batteries. In Proceedings of the 2017 International Conference on Innovations in Electrical, Electronics, Instrumentation and Media Technology (ICEEIMT), Coimbatore, India, 3–4 February 2017; pp. 330–333. [Google Scholar]

- Dostal, F. Power Management for Healthcare Applications|Analog Devices. Available online: https://www.analog.com/ru/technical-articles/power-management-for-health-care-applications.html (accessed on 6 February 2022).

- Saggini, S. Power management in battery powered handheld portable applications. In Proceedings of the 2015 Mobile Systems Technologies Workshop (MST), Milan, Italy, 22 May 2015; pp. 12–14. [Google Scholar]

- Manninger, M. Power management for portable devices. In Proceedings of the ESSCIRC 2007—33rd European Solid-State Circuits Conference, Munich, Germany, 11–13 September 2007; pp. 167–173. [Google Scholar]

- Kankanamge, K.; Kularatna, N.; Steyn-Ross, A. Laplace transform-based theoretical foundations and experimental validation—low frequency supercapacitor circulation technique for efficiency improvements in linear regulators. In Proceedings of the IECON 2011—37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, VC, Australia, 7–10 November 2011; pp. 4113–4118. [Google Scholar]

- Kankanamge, K.; Kularatna, N. Improving the end-to-end efficiency of DC–DC converters based on a supercapacitor-assisted low-dropout regulator technique. IEEE Trans. Ind. Electron. 2014, 61, 223–230. [Google Scholar] [CrossRef]

- Shen, Z.-H.; Min, H. Combination Method of DC-DC Converter and LDO to Improve Efficiency and Load Regulation. Electron. Lett. 2011, 47, 615–617. [Google Scholar] [CrossRef]

- Day, M. Integration Saves Time and Board Space Converter. Available online: https://www.electronicdesign.com/content/article/21186830/integration-saves-time-and-board-space (accessed on 8 February 2022).

- Analog Devices. LTM8001: 36 VIN, 5 A ΜModule Regulator with 5-Output Configurable LDO Array 2013; Analog Devices: Norwood, MA, USA, 2013. [Google Scholar]

- Andy, R. µModule Regulator Combines a Switcher with Five 1.1 A LDOs: Use Them for Multiple Low Noise Rails, or Parallel Them to Spread Heat and Share Current to 5 A; Analog Devices: Norwood, MA, USA, 2014. [Google Scholar]

- Samwha Capacitor Co., Ltd. ESD-SCAP; Samwha Capacitor Co., Ltd.: Gangnam, Korea, 2018. [Google Scholar]

- Kularatna, N.; Jayananda, D. Supercapacitor-Based Long Time-Constant Circuits: A Unique Design Opportunity for New Power Electronic Circuit Topologies. IEEE Ind. Electron. Mag. 2020, 14, 40–56. [Google Scholar] [CrossRef]

- Şahin, M.E.; Blaabjerg, F.; Sangwongwanich, A. A Comprehensive Review on Supercapacitor Applications and Developments. Energies 2022, 15, 674. [Google Scholar] [CrossRef]

- Gunawardane, K. Analysis on Supercapacitor Assisted Low Dropout Regulators. Ph.D. Thesis, University of Waikato, Hamilton, New Zealand, 2014. [Google Scholar]

- Kularatna, N.; Subasinghage, K.; Gunawardane, K.; Jayananda, D.; Ariyarathna, T. Supercapacitor-Assisted Techniques and Supercapacitor-Assisted Loss Management Concept: New Design Approaches to Change the Roadmap of Power Conversion Systems. Electronics 2021, 10, 1697. [Google Scholar] [CrossRef]

- Gunawardane, K.; Kularatna, N. Supercapacitor assisted ldo (scaldo) techniquean extra low frequency design approach to high efficiency DC-DC converters and how it compares with the classical switched capacitor converters. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; p. 1984, ISBN 978-1-4673-4354-1. [Google Scholar]

- Wickramasinghe, T. Supercapacitor-Based Linear Converter for Voltage Regulator Modules. Ph.D. Thesis, University of Waikato, Hamilton, New Zealand, 2016. [Google Scholar]

- Subasinghage, K.; Gunawardane, K.; Lie, T.T.; Kularatna, N. Single-input, dual polarity, dual output DC-DC converter implementation based on the SCALDO technique. In Proceedings of the 2017 IEEE International Conference on Industrial Technology (ICIT), Toronto, ON, Canada, 22–25 March 2017; pp. 207–212. [Google Scholar]

- Gunawardane, K.; Kularatna, N. Supercapacitor-assisted low dropout regulator technique: A new design approach to achieve high-efficiency linear DC–DC converters. IET Power Electron. 2018, 11, 229–238. [Google Scholar] [CrossRef]

| Parameter | Linear Regulators and LDOs | SMPS | Charge Pumps |

|---|---|---|---|

| Design flexibility | Step down | Step up/Step down/Inversion | Step up/Step down/Inversion |

| Circuit Diagram |  LDO |  Buck Converter |  Switch capacitor voltage doubler |

| Efficiency (typical) | Linear regulators: 50–60% LDOs up to 98% | Higher than 95% | 70–80% |

| Complexity | Low | High | Low |

| Size | small | Smaller than LDO | Smallest |

| Total Cost | Low | High | Low |

| Electromagnetic interference (EMI) | Low | High | Medium |

| Noise | Low | High | Medium |

| Input voltage range | Narrow | Wide | Narrow |

| Thermal management | Moderate (mainly the series pass device) | Complex (multiple devices to deal with where the heat is dissipated) | Moderate (switches) |

| Output current capability | Medium | High | Low |

| Dropout Voltage (mV) | Input Voltage Range (V) | Output Voltage Range (V) | Current Rating (mA) | Maximum Efficiency (%) | Commercially Available LDOs |

|---|---|---|---|---|---|

| 200 | 1.5–5.5 | −0.3 ± 0.3 | 200 | 96.36 | LDBL20 [13] |

| 65–125 | 0.8–5.5 | 0.8–3.6 | 1500 | 97.72 | LD59150 [14] |

| 80 | 1.5–5.5 | 0.8–3.3 | 100 | 98.55 | LD39015 [15] |

| 175 | 1.1–6.5 | 0.8–5.15 | 4000 | 97.31 | TPS7A54 [16] |

| 225 | 1.5–6 | 0.55–5.5 | 1000 | 96.25 | TLV752 [17] |

| LDO Specific Property | Industrial Application | Commercially Available LDOs |

|---|---|---|

| Reduce noise and PSRR levels | High-speed communications applications, video processing applications, and high-accuracy measurement applications. | TPS717xx family [23] |

| Compactness | Compact portable devices | TPS720 [24], TLV733P [25], ADP160 [26], ADP166 [26], ADM7160 [27] |

| Lower quiescent current | Battery-powered applications | TPS7A19 [28], TPS7B69 [29], LT3009 [30], STLQ50 [31], LDK715 [32] |

| Item | Loss | Reason | Remarks |

|---|---|---|---|

| 1 | Static losses of the switches such as transistors and diodes |

| These show up a cumulative content known as “static losses” which increases with output voltage and the load current. |

| 2 | Dynamic losses in transistors and diodes increase with the switching frequency |

| The higher switching frequency of switch-mode power supplies increases the dynamic losses linearly with the frequency in general. |

| 3 | Secondary losses in inductors |

| Except for ohmic losses, others are frequency-dependent and have a nonlinear behaviour with frequency. |

| 4 | Secondary losses in capacitors |

| Smaller capacitors have high ESR and large capacitors have relatively lower ESR. |

| 5 | Power consumed by the controller circuit associated with the power stage |

| These losses depend on the control circuit section of the switch-mode power supply. |

| 6 | PCB track losses/interconnection losses in an IC version |

| The larger the current the higher these are. |

| Parameter | Unit | Range |

|---|---|---|

| Rated voltage | V | 1.2–3.8 |

| Capacitance | F | 1–3000 |

| Specific energy density | Wh/kg. | 1–10 |

| Specific power density | W/kg | <10,000 |

| Cycle life | Cycle number | >50,000 |

| Charge and discharge efficiency | % | 85–98 |

| Fast charge duration | Seconds | 0.3–30 |

| Fast discharge duration | Seconds | 0.3–30 |

| Shelf life | Years | 20 |

| Operating temperature | °C | −40 to 75 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gunawardane, K.; Padmawansa, N.; Kularatna, N.; Subasinghage, K.; Lie, T.T. Current Context and Research Trends in Linear DC–DC Converters. Appl. Sci. 2022, 12, 4594. https://doi.org/10.3390/app12094594

Gunawardane K, Padmawansa N, Kularatna N, Subasinghage K, Lie TT. Current Context and Research Trends in Linear DC–DC Converters. Applied Sciences. 2022; 12(9):4594. https://doi.org/10.3390/app12094594

Chicago/Turabian StyleGunawardane, Kosala, Nisitha Padmawansa, Nihal Kularatna, Kasun Subasinghage, and Tek Tjing Lie. 2022. "Current Context and Research Trends in Linear DC–DC Converters" Applied Sciences 12, no. 9: 4594. https://doi.org/10.3390/app12094594

APA StyleGunawardane, K., Padmawansa, N., Kularatna, N., Subasinghage, K., & Lie, T. T. (2022). Current Context and Research Trends in Linear DC–DC Converters. Applied Sciences, 12(9), 4594. https://doi.org/10.3390/app12094594