Virtual Admittance Feedforward Compensation and Phase Correction for Average-Current-Mode-Controlled Totem-Pole PFC Converters

Abstract

:Featured Application

Abstract

1. Introduction

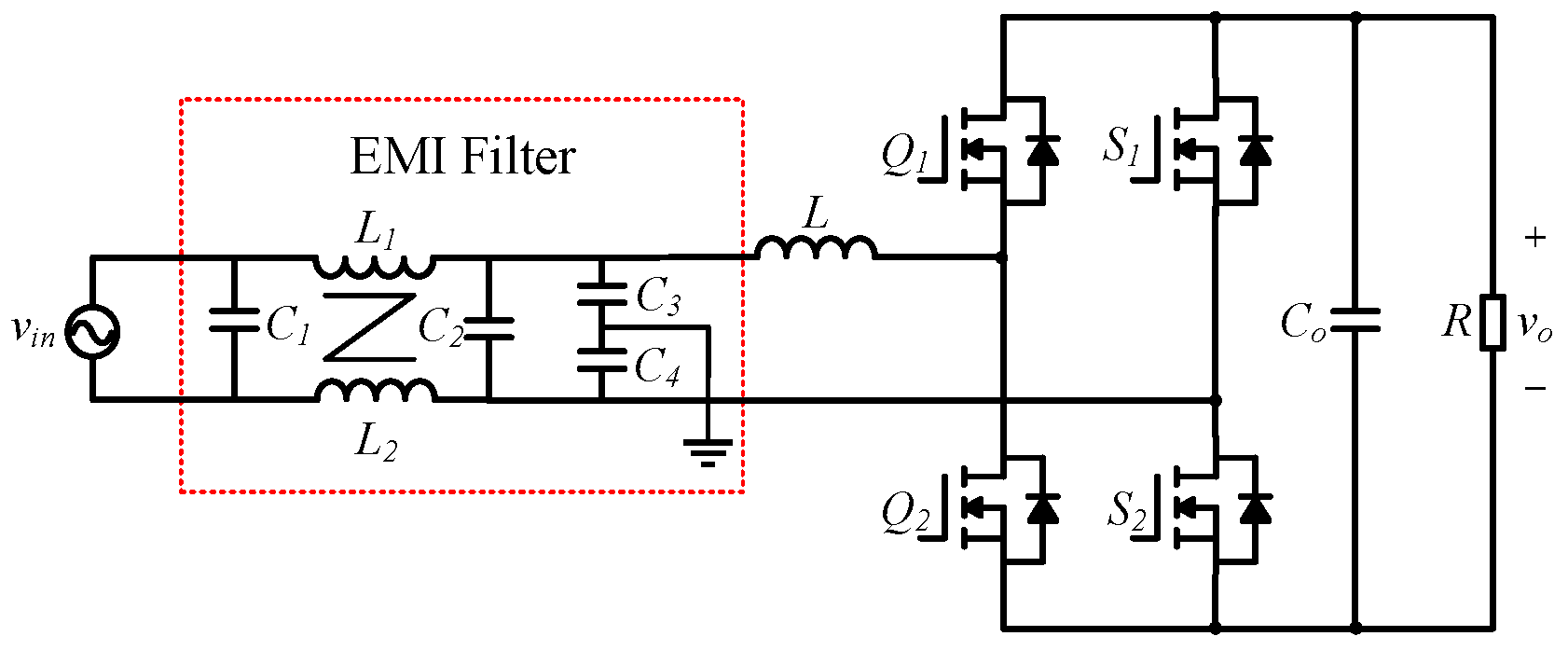

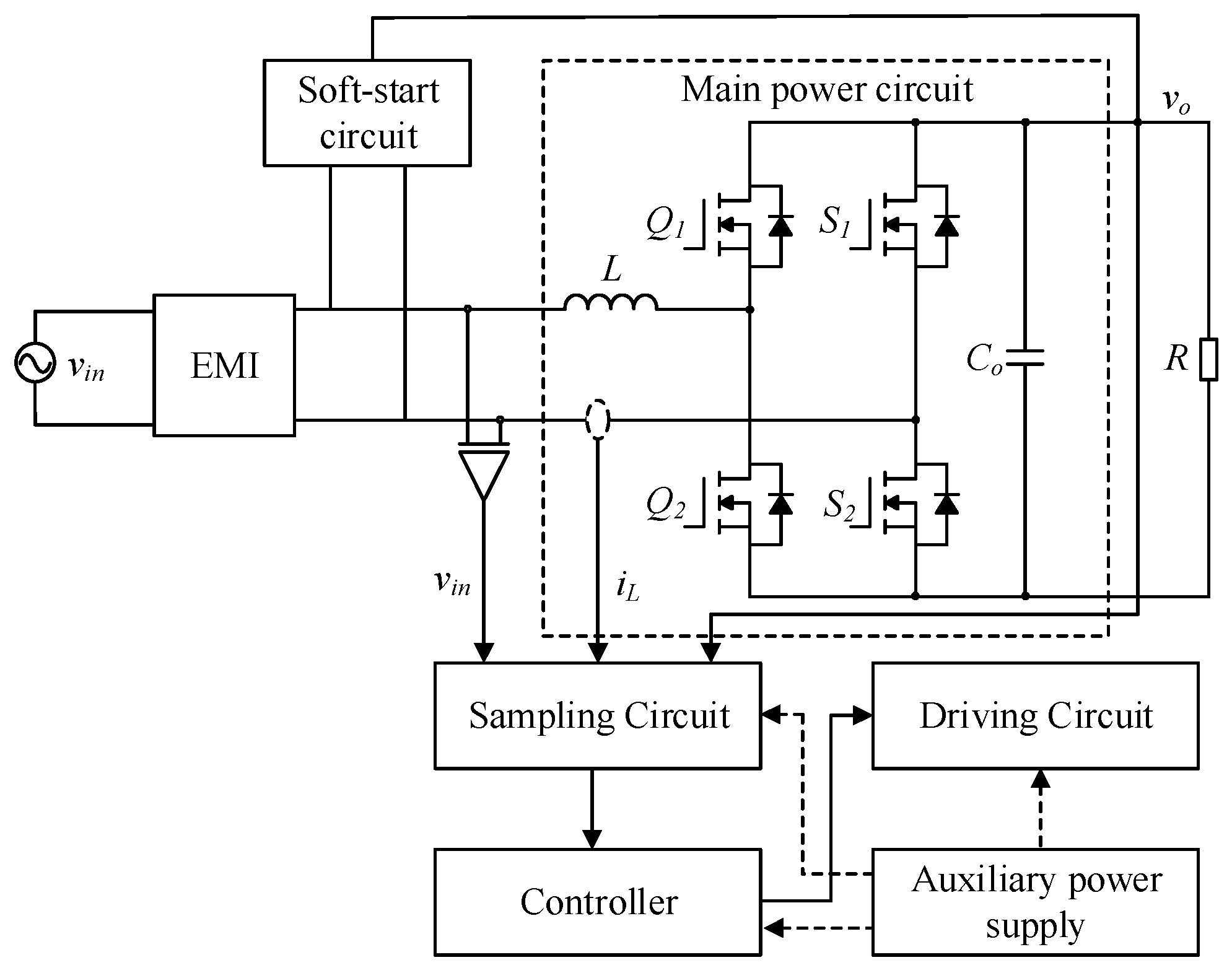

2. Current-Distortion Problem in Totem-Pole Bridgeless PFC Converter

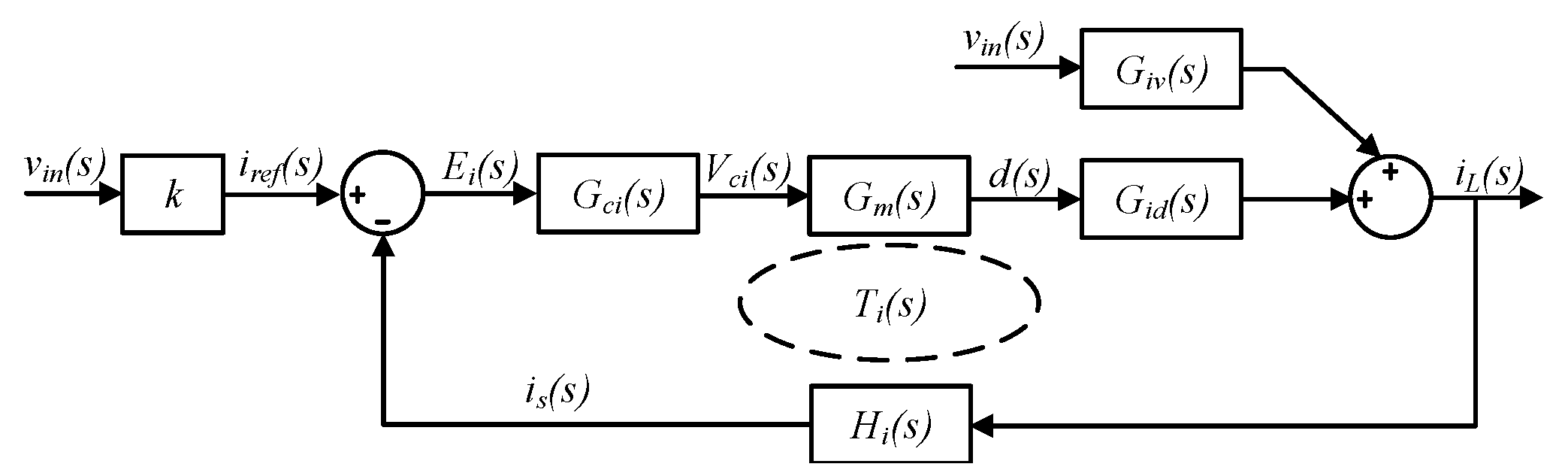

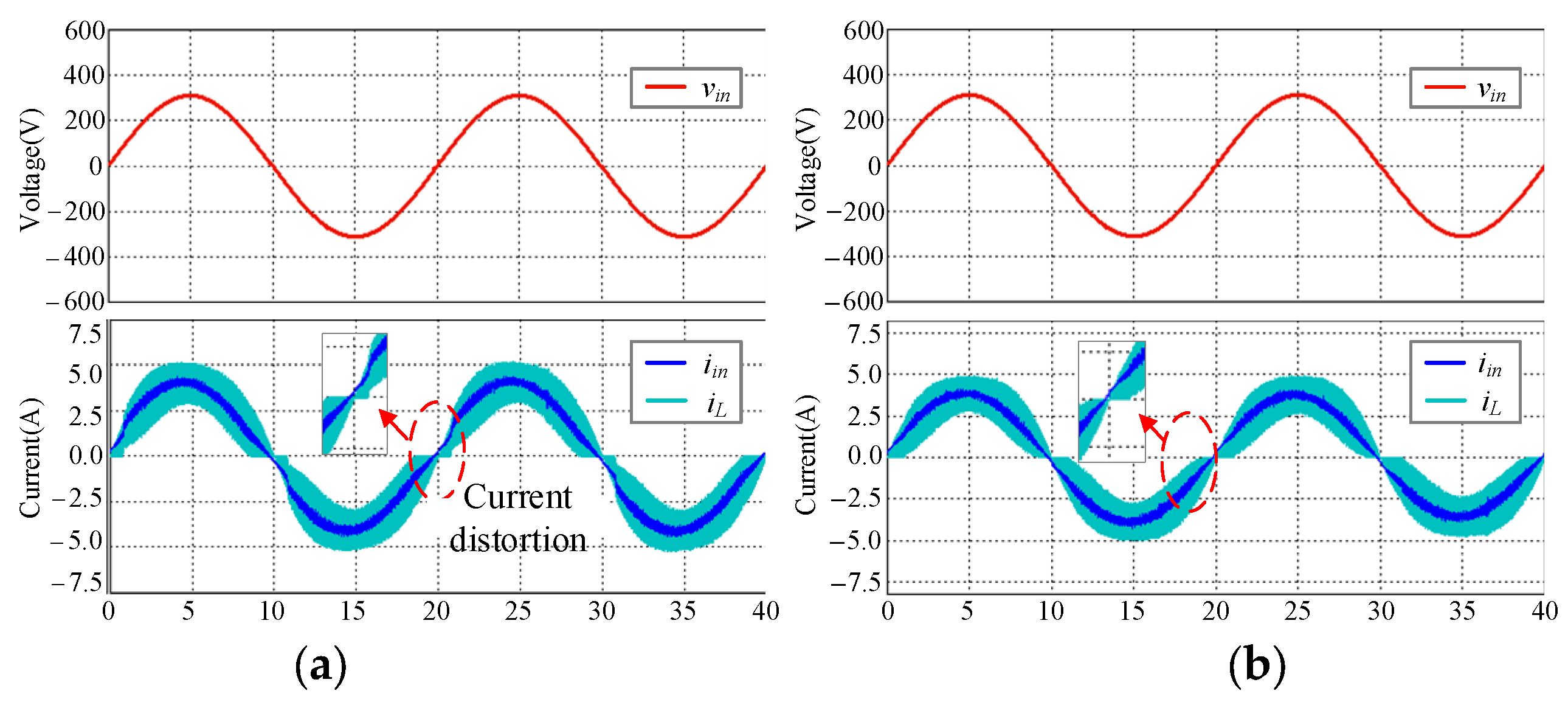

2.1. Current Distortion Caused by Limited Current Loop Bandwidth

2.2. Current Distortion Caused by Input Capacitor

3. Virtual Admittance Feedforward Compensation and Phase Correction to Reduce Current Distortion

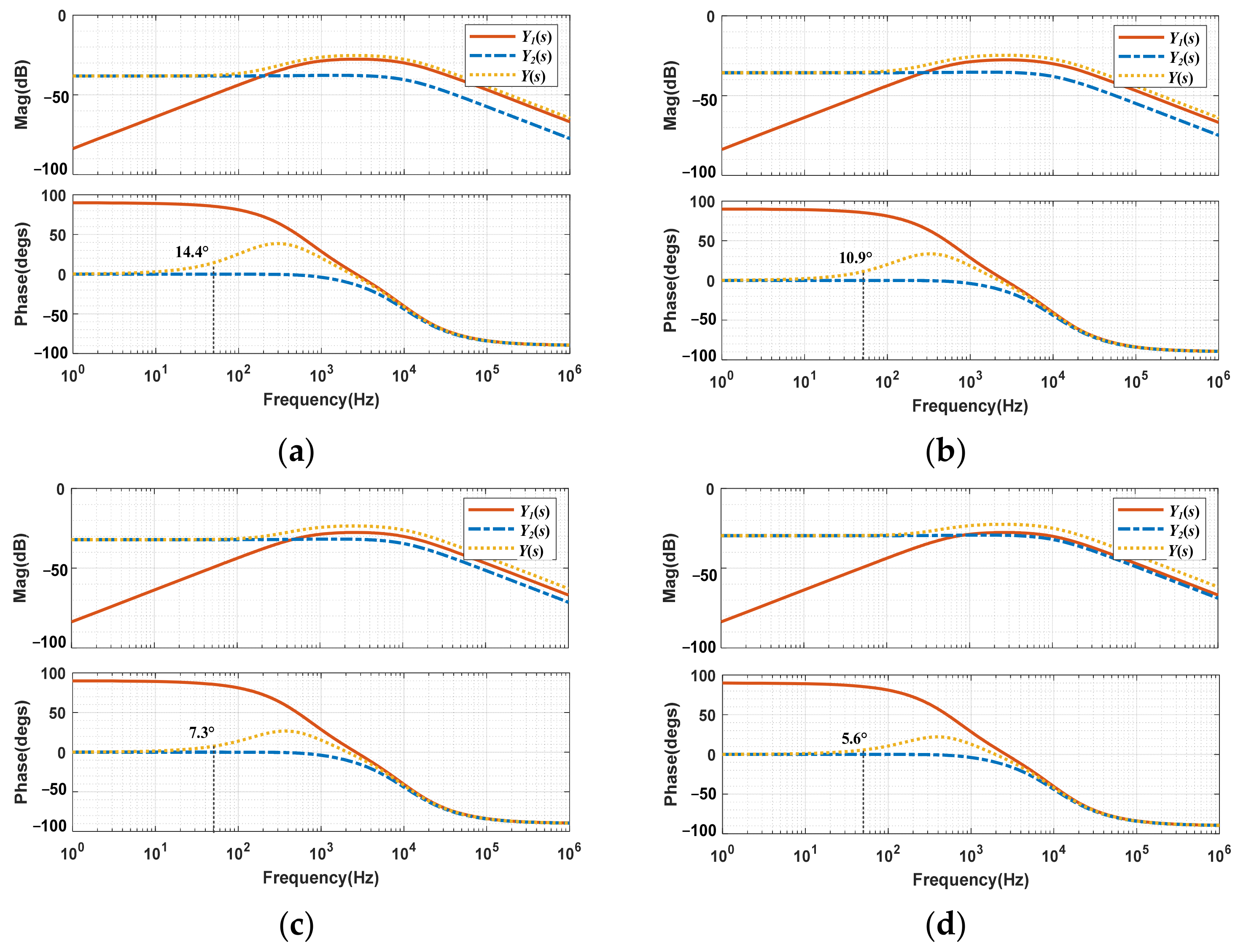

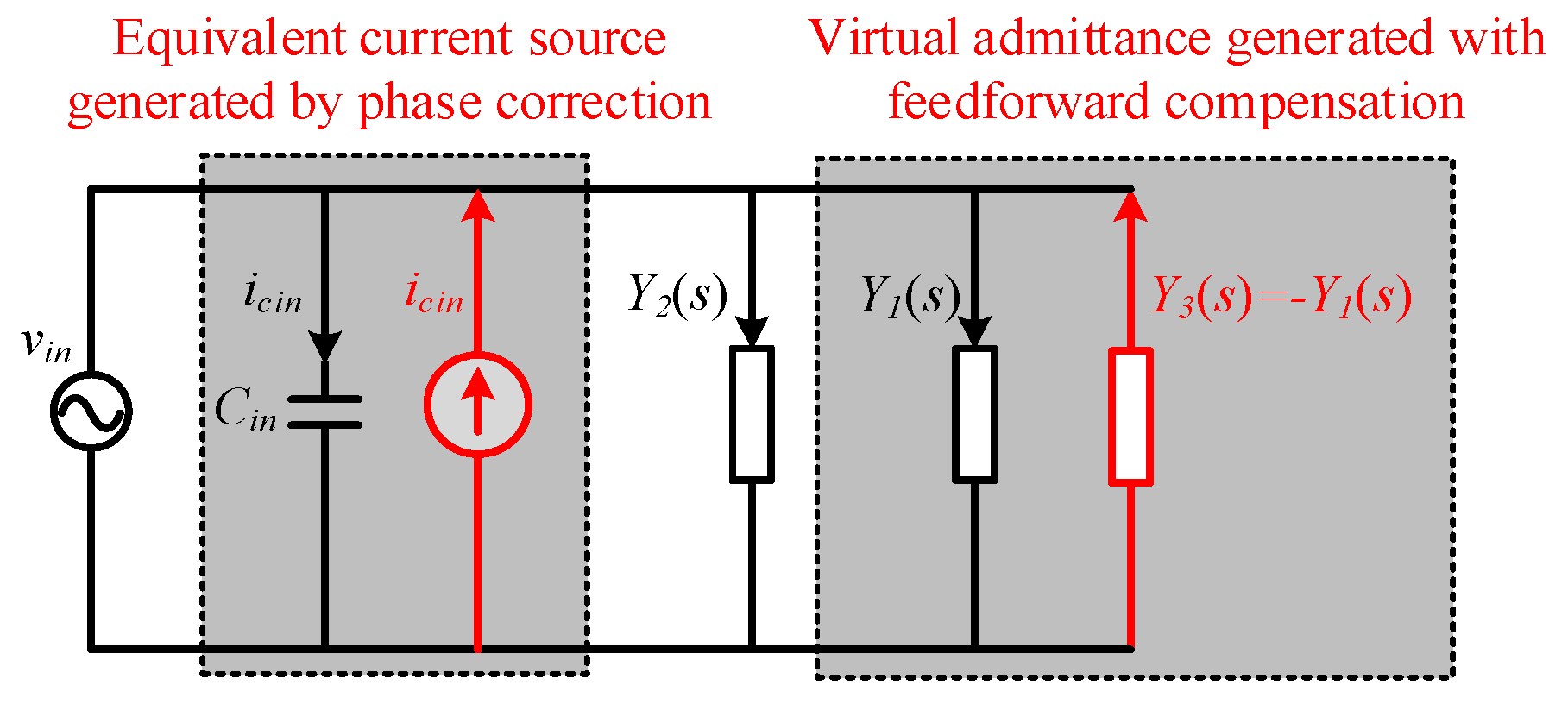

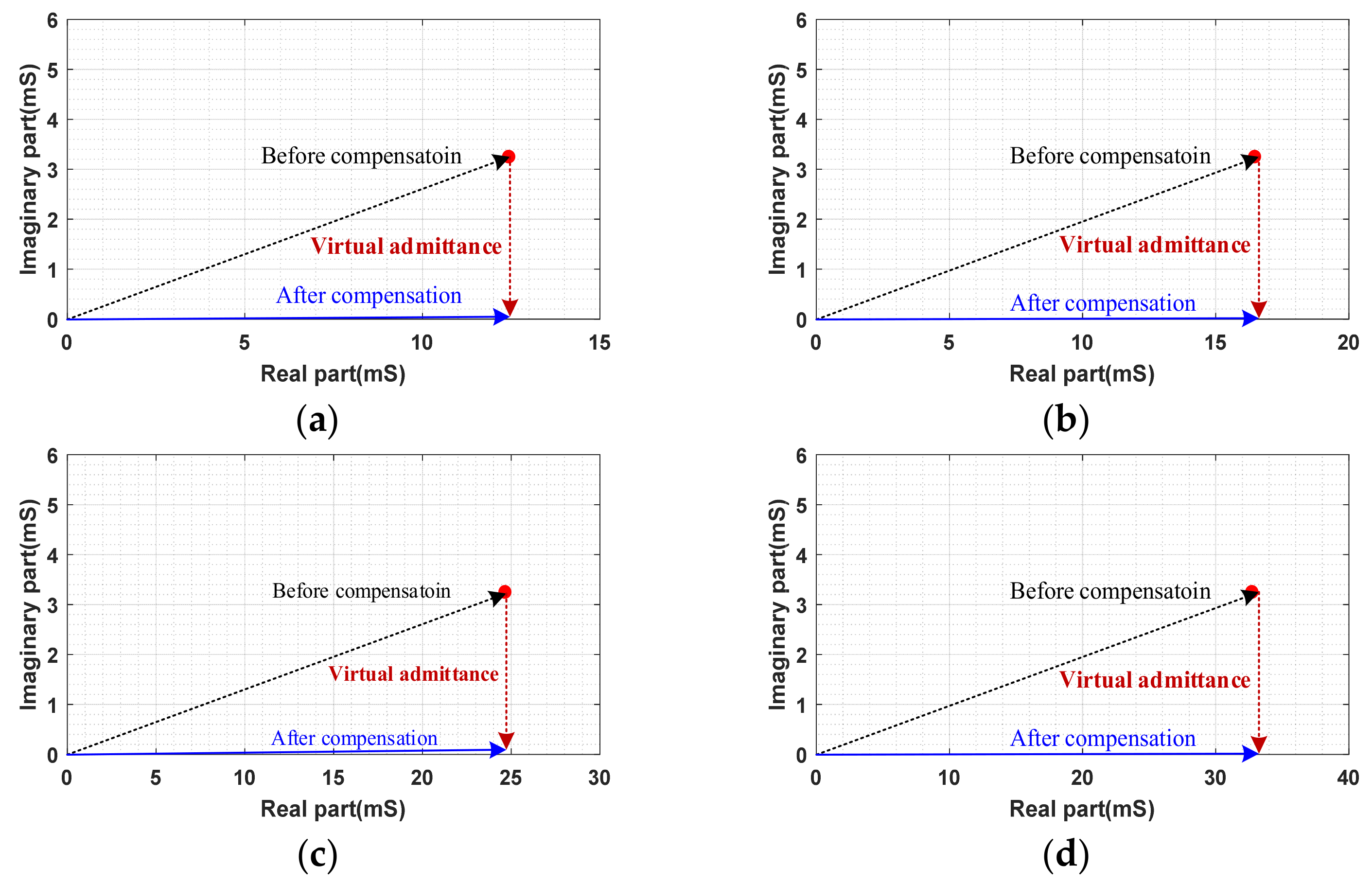

3.1. Virtual Admittance Feedforward Compensation

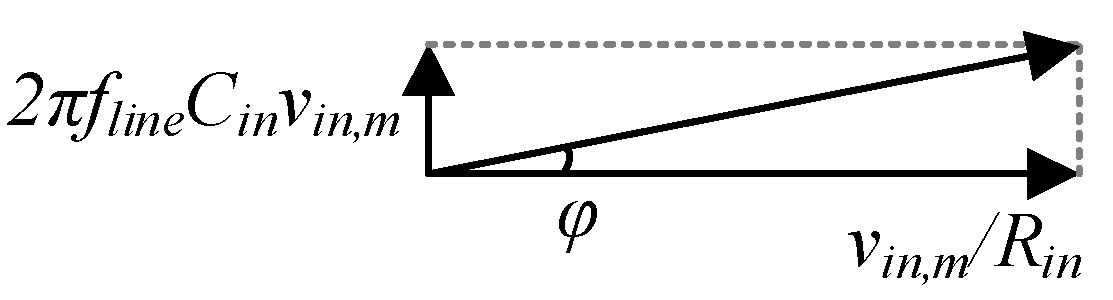

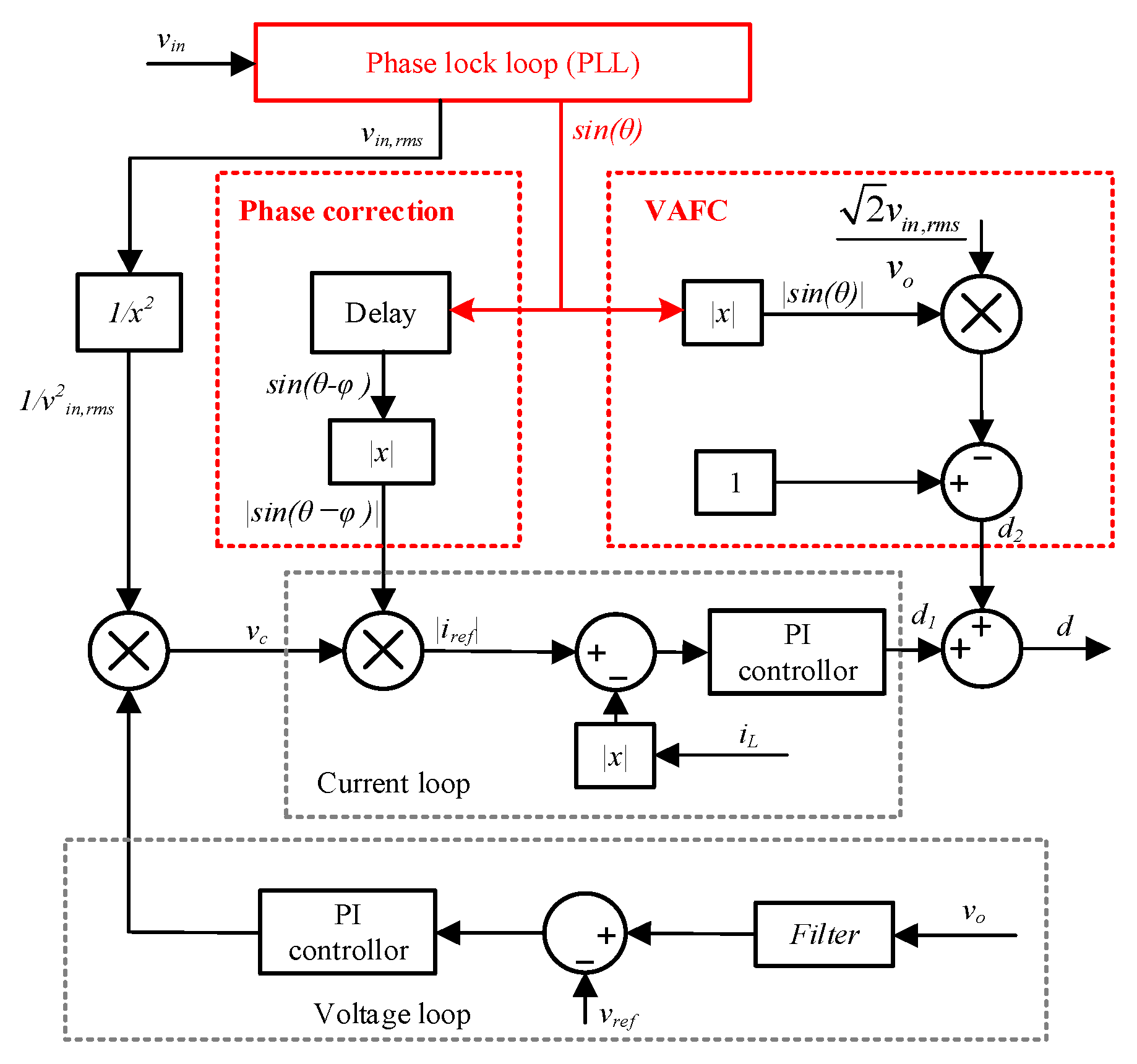

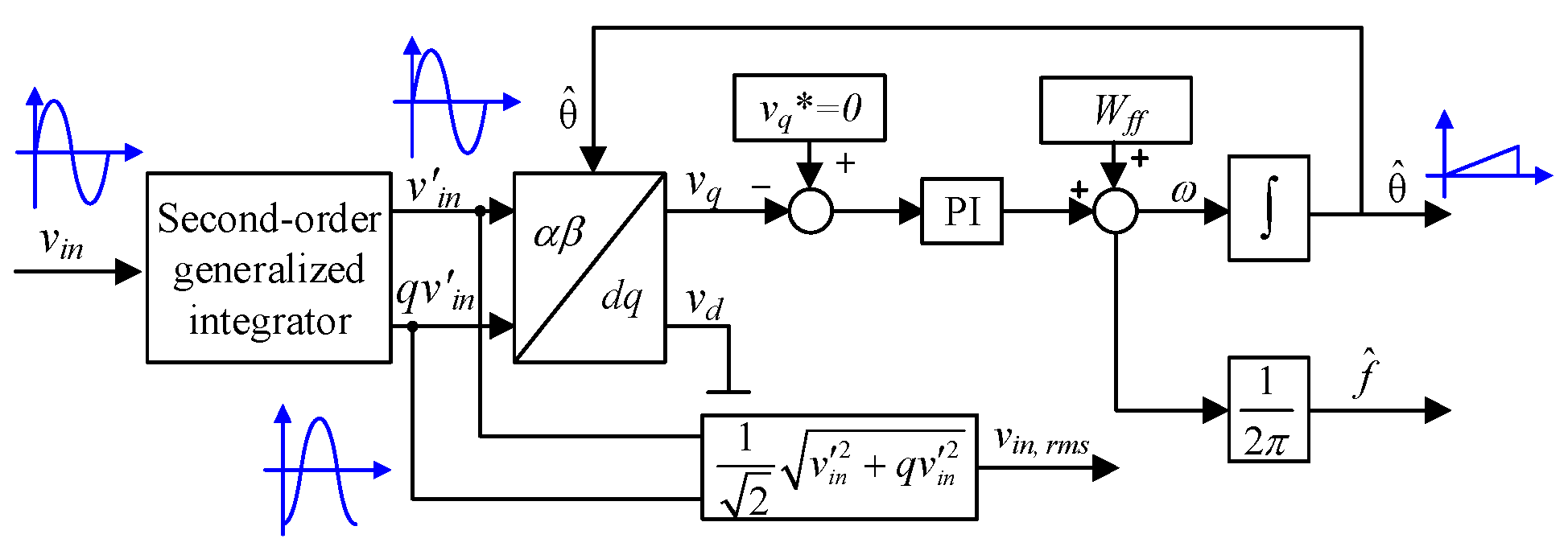

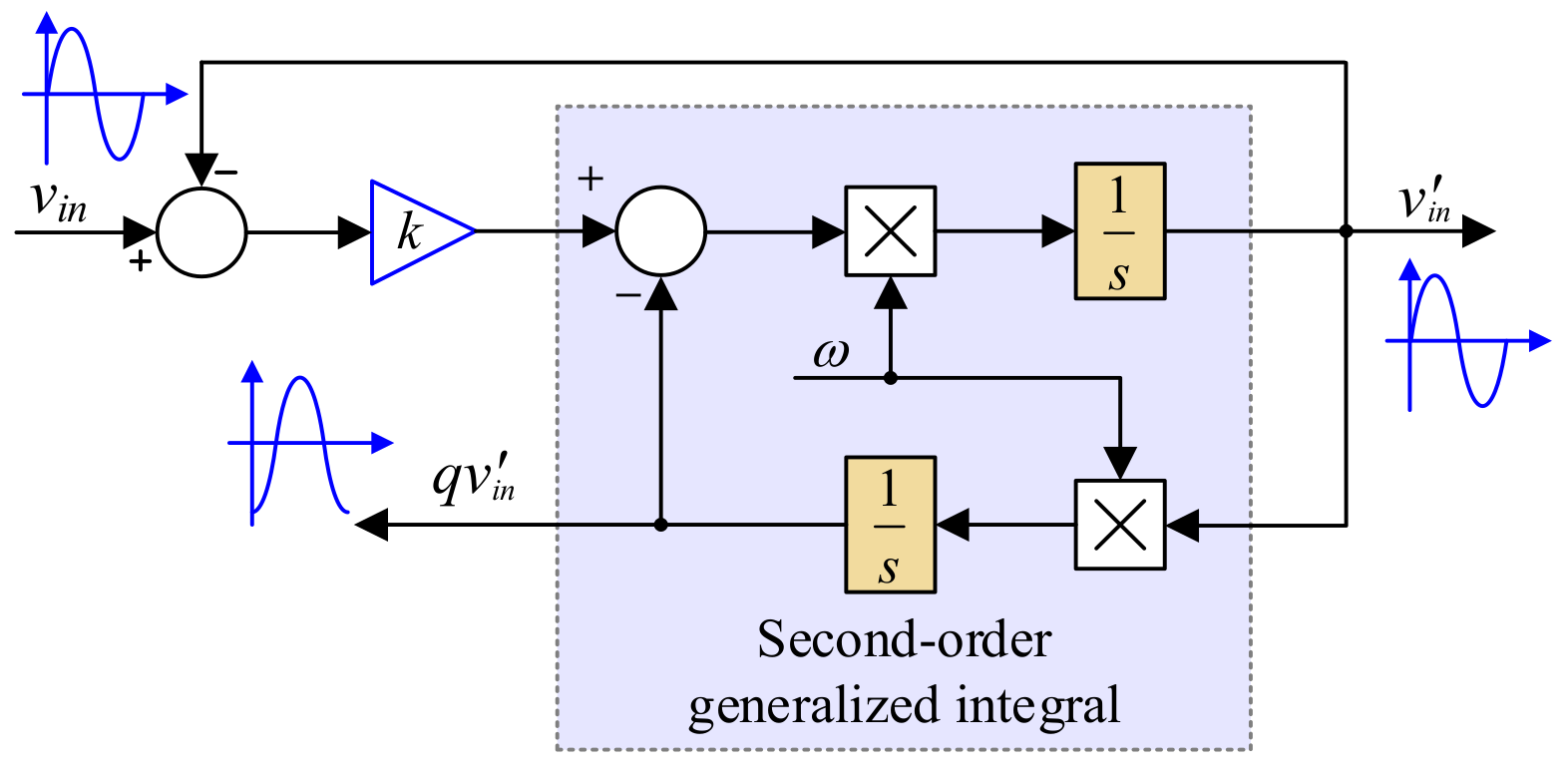

3.2. Reference Current Phase Correction

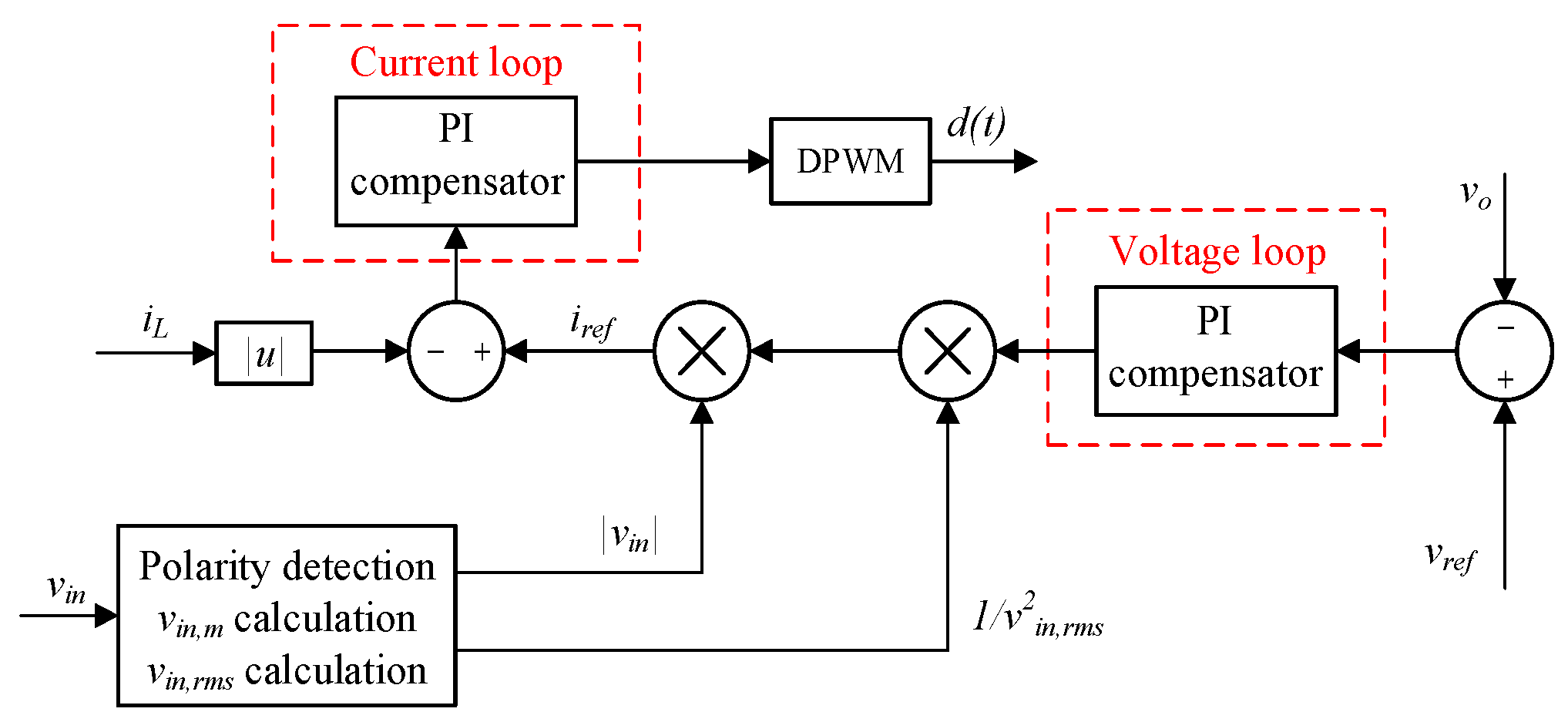

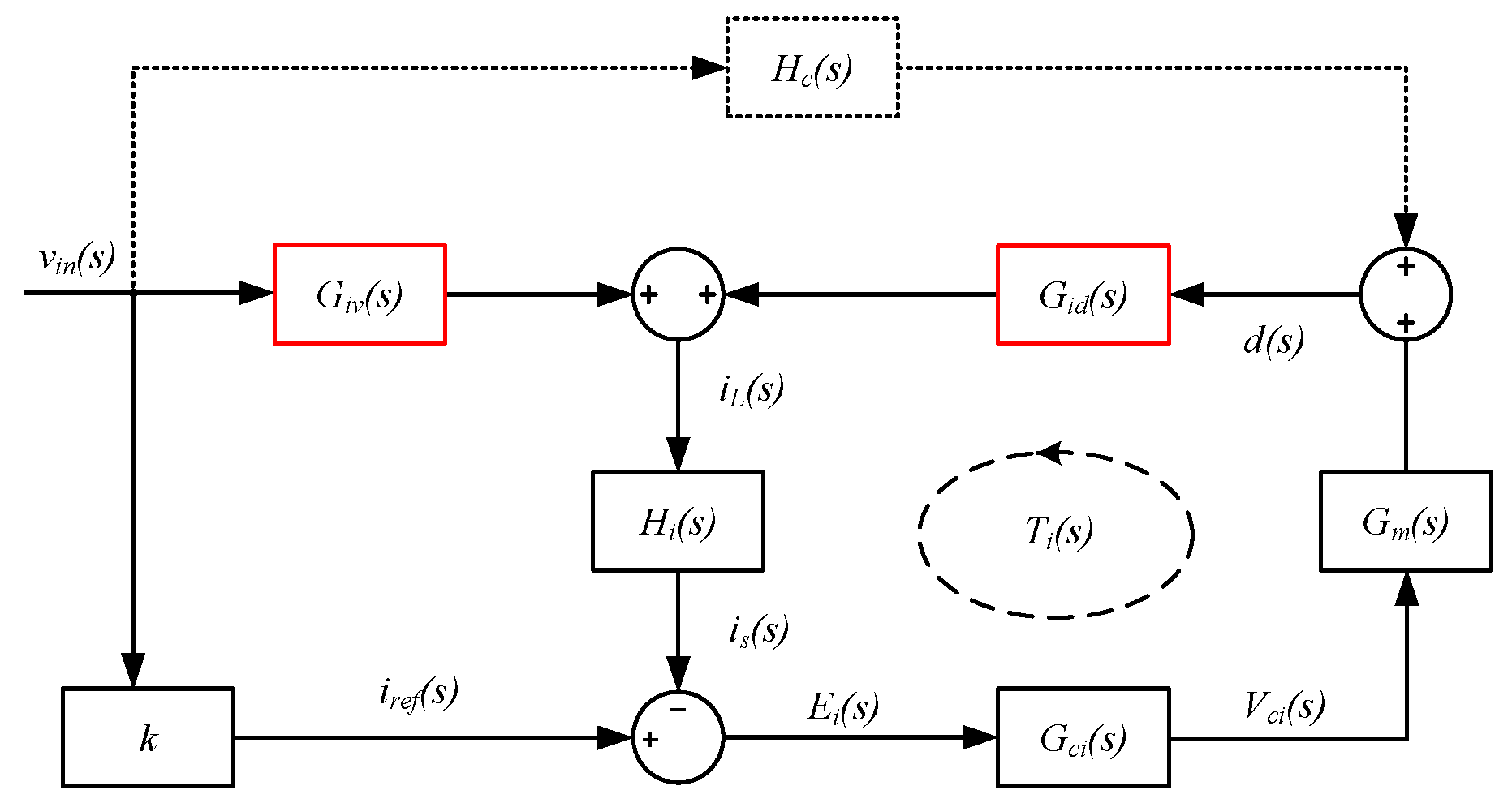

3.3. Overall Control Diagram

4. Experimental Results

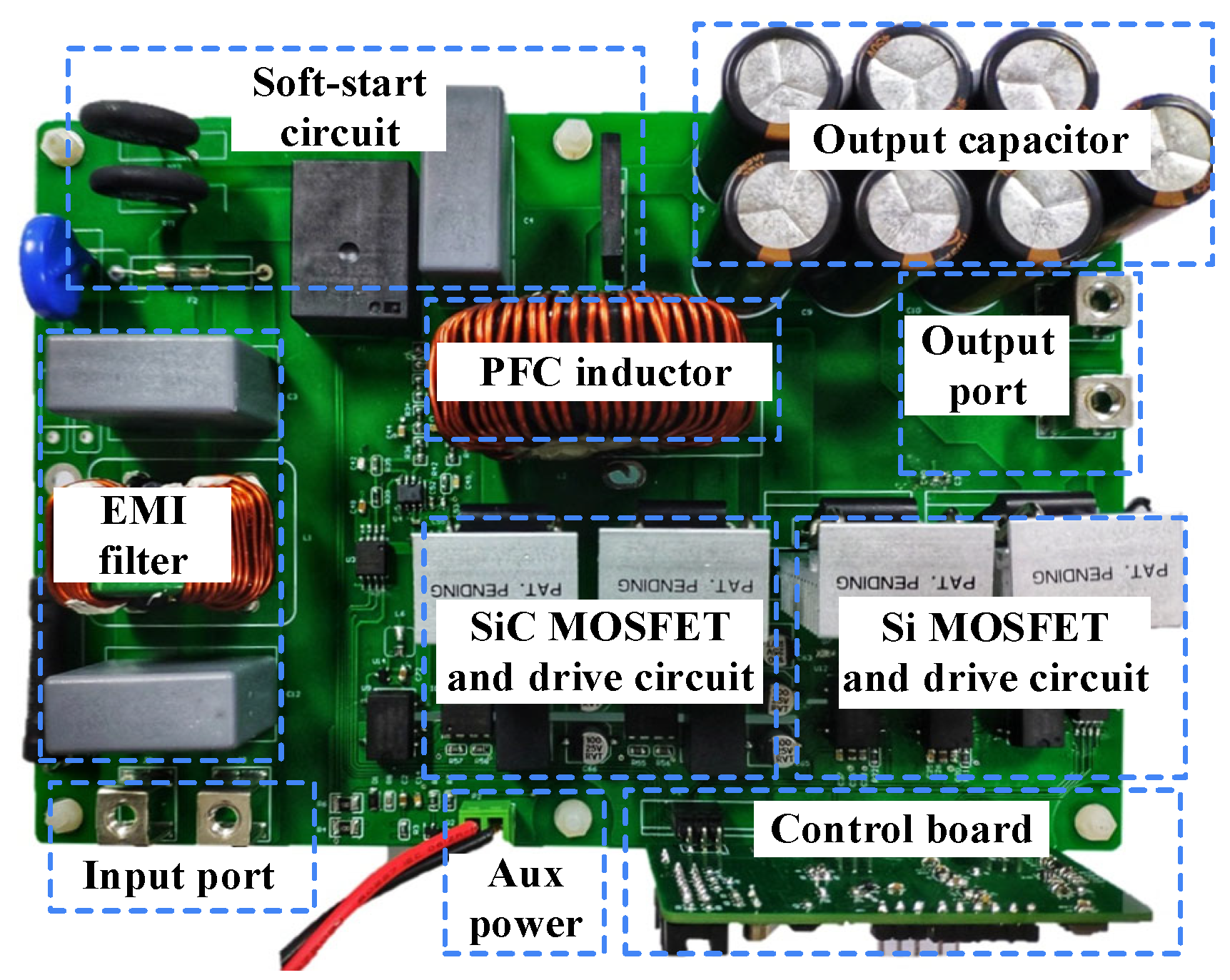

4.1. Hardware Design of the Totem-Pole Bridgeless PFC Converter

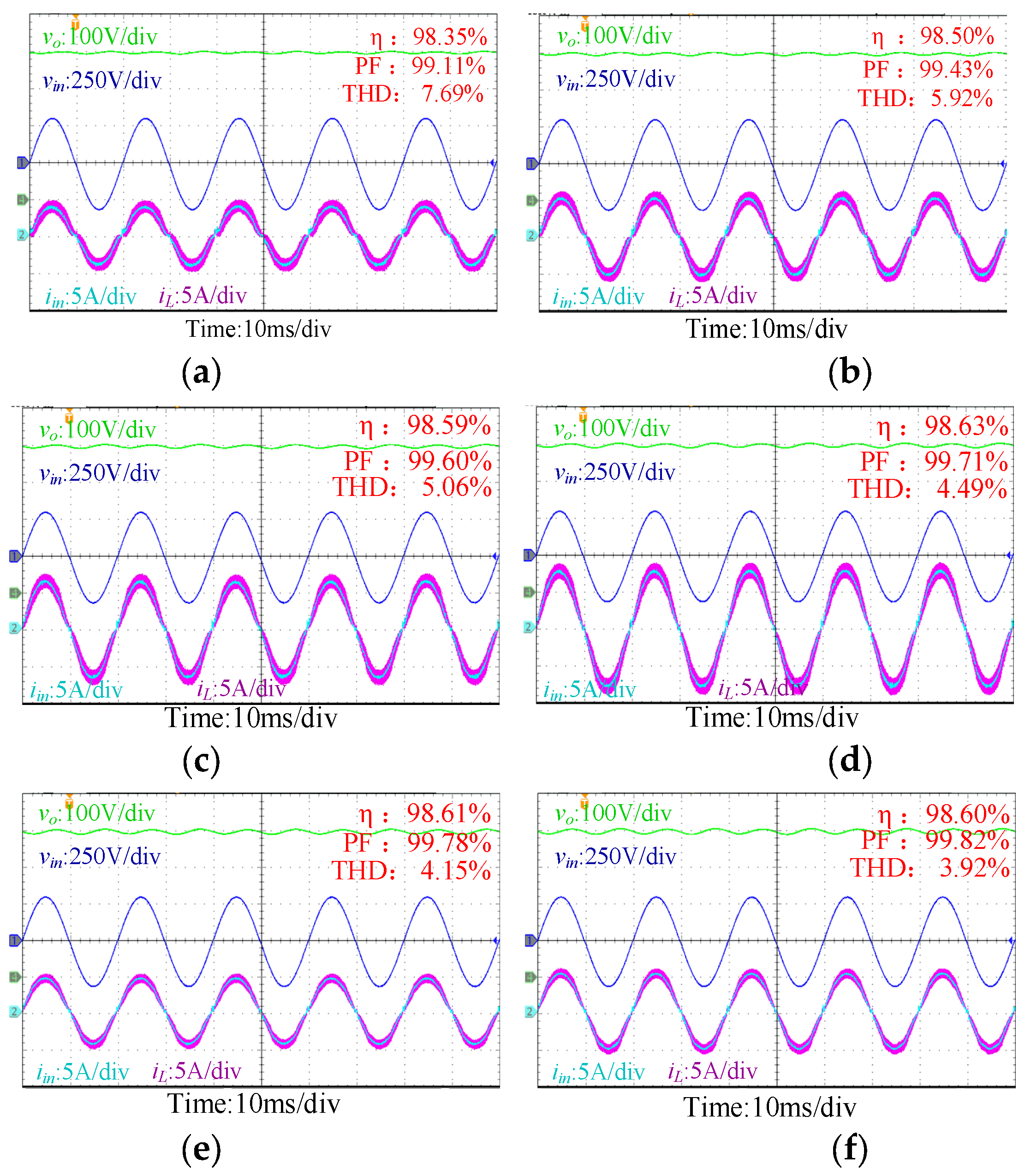

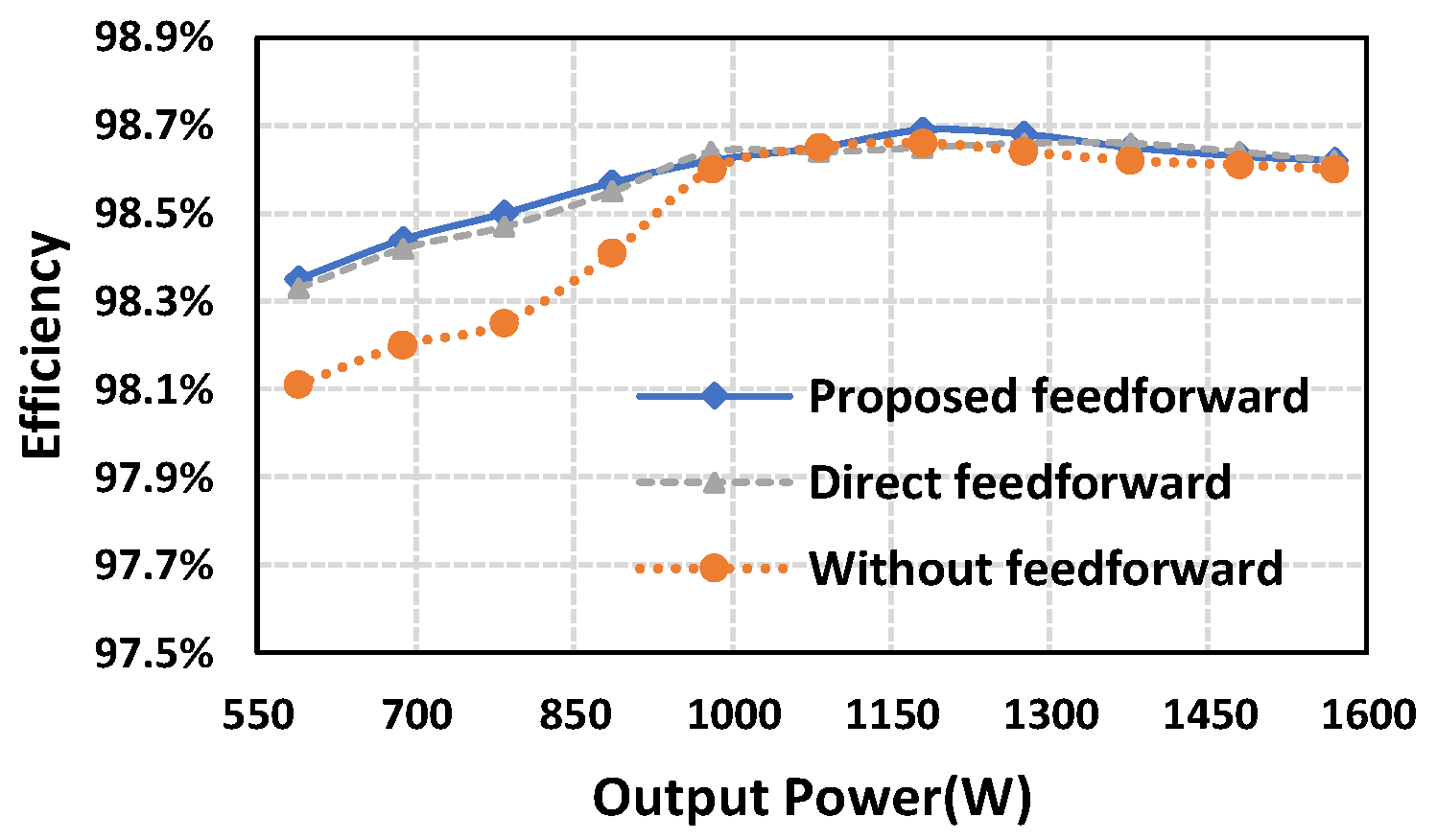

4.2. Performance Test under Different Power Rates

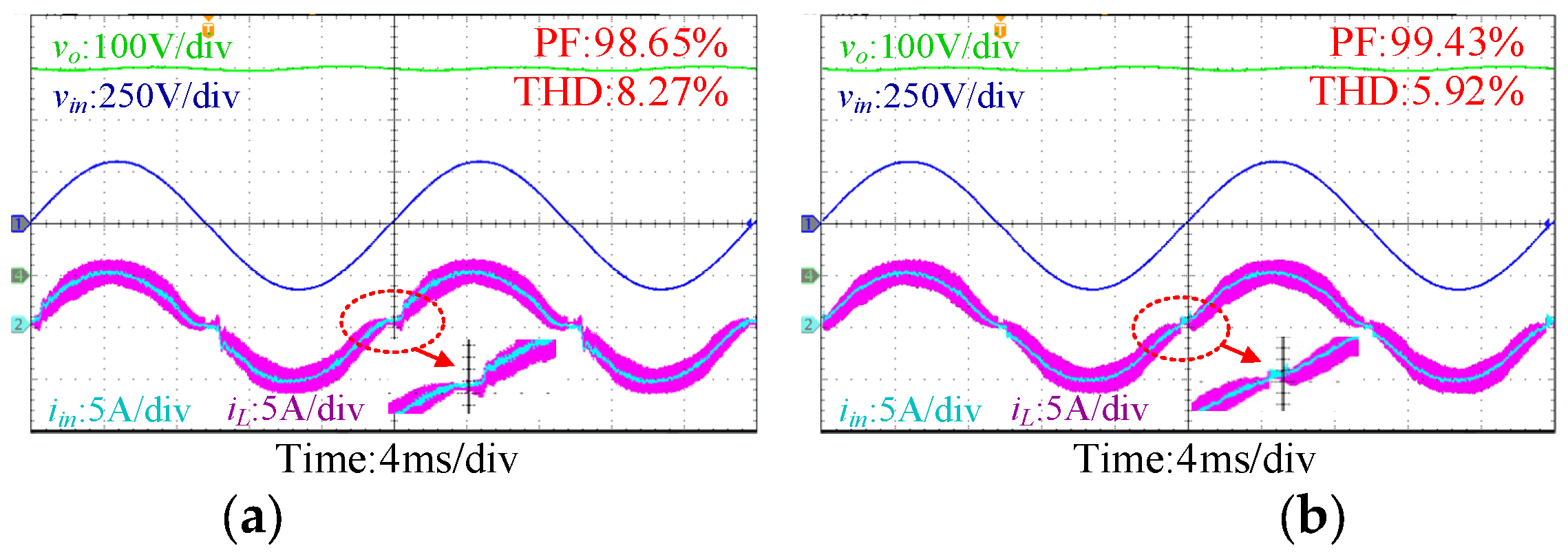

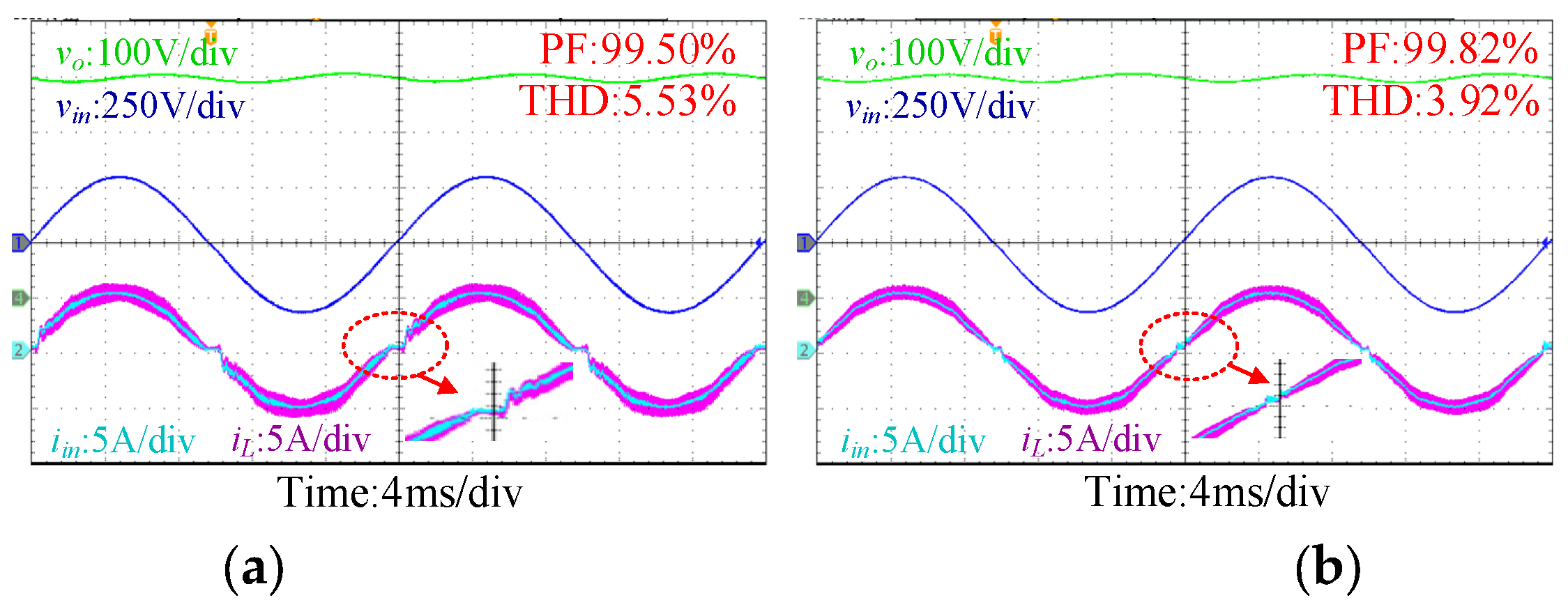

4.3. Waveform Comparisons with and without Feedforward Compensation

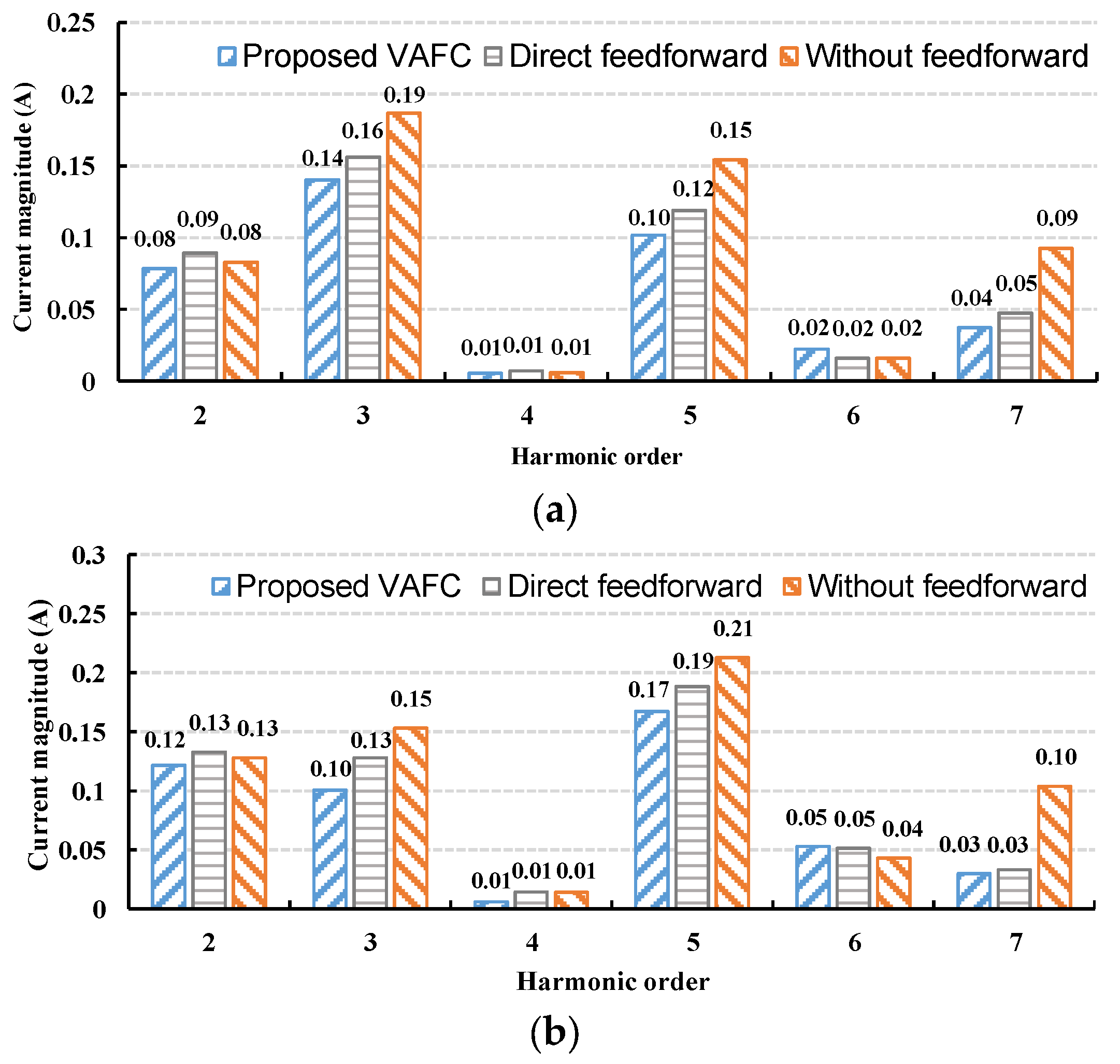

4.4. PF and THD Comparisons with and without Feedforward Compensation

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Acknowledgments

Conflicts of Interest

References

- Collin, A.J.; Drapela, J.; Langella, R.; Testa, A. Emission assessment of single-phase switch-mode PFC loads up to 150 kHz: Experimental analysis and modelling. Electr. Power Syst. Res. 2023, 220, 109236. [Google Scholar] [CrossRef]

- Lopez, V.M.; Azcondo, F.J.; de Castro, A.; Zane, R. Universal Digital Controller for Boost CCM Power Factor Correction Stages Based on Current Rebuilding Concept. IEEE Trans. Power Electron. 2014, 29, 3818–3829. [Google Scholar] [CrossRef]

- Rosa, A.H.R.; Morais, L.M.F.; Fortes, G.O.; Seleme Júnior, S.I. Practical considerations of nonlinear control techniques applied to static power converters: A survey and comparative study. Int. J. Electr. Power Energy Syst. 2021, 127, 106545. [Google Scholar] [CrossRef]

- Szekely, N.C.; Salcu, S.I.; Suciu, V.M.; Pintilie, L.N.; Fasola, G.I.; Teodosescu, P.D. Power Factor Correction Application Based on Independent Double-Boost Interleaved Converter (IDBIC). Appl. Sci. 2022, 12, 7209. [Google Scholar] [CrossRef]

- Tiwari, S.; Basu, S.; Undeland, T.M.; Midtgård, O.M. Efficiency and Conducted EMI Evaluation of a Single-Phase Power Factor Correction Boost Converter Using State-of-the-Art SiC Mosfet and SiC Diode. IEEE Trans. Ind. Appl. 2019, 55, 7745–7756. [Google Scholar] [CrossRef]

- Singh, A.; Mallik, A.; Khaligh, A. A Comprehensive Design and Optimization of the DM EMI Filter in a Boost PFC Converter. IEEE Trans. Ind. Appl. 2018, 54, 2023–2031. [Google Scholar] [CrossRef]

- Benyamina, A.; Moulahoum, S.; Colak, I.; Bayindir, R. Design and real time implementation of adaptive neural-fuzzy inference system controller based unity single phase power factor converter. Electr. Power Syst. Res. 2017, 152, 357–366. [Google Scholar] [CrossRef]

- Chen, Z.; Liu, B.; Yang, Y.; Davari, P.; Wang, H. Bridgeless PFC Topology Simplification and Design for Performance Benchmarking. IEEE Trans. Power Electron. 2021, 36, 5398–5414. [Google Scholar] [CrossRef]

- Chen, Z.; Davari, P.; Wang, H. Single-Phase Bridgeless PFC Topology Derivation and Performance Benchmarking. IEEE Trans. Power Electron. 2020, 35, 9238–9250. [Google Scholar] [CrossRef]

- Ortiz-Castrillón, J.R.; Mejía-Ruíz, G.E.; Muñoz-Galeano, N.; López-Lezama, J.M.; Saldarriaga-Zuluaga, S.D. PFC Single-Phase AC/DC Boost Converters: Bridge, Semi-Bridgeless, and Bridgeless Topologies. Appl. Sci. 2021, 11, 7651. [Google Scholar] [CrossRef]

- Huang, Q.; Ma, Q.; Yu, R.; Chen, T.; Huang, A.Q.; Liu, Z. Improved analysis, design and control for interleaved dual-phase ZVS GaN-based totem-pole PFC rectifier with coupled inductor. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 2077–2083. [Google Scholar]

- Amiri, P.; Eberle, W.; Gautam, D.; Botting, C. An Adaptive Method for DC Current Reduction in Totem Pole Power Factor Correction Converters. IEEE Trans. Power Electron. 2021, 36, 11900–11909. [Google Scholar] [CrossRef]

- Kumar, V.; Yi, K. Single-Phase, Bidirectional, 7.7 kW Totem Pole On-Board Charging/Discharging Infrastructure. Appl. Sci. 2022, 12, 2236. [Google Scholar] [CrossRef]

- Zhang, C.; Qu, K.; Hu, B.; Wang, J.; Yin, X.; Shen, Z.J. A High-Frequency Dynamically Coordinated Hybrid Si/SiC Interleaved CCM Totem-Pole Bridgeless PFC Converter. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 2088–2100. [Google Scholar] [CrossRef]

- Ali, A.I.M.; Takeshita, T.; Sayed, M.A. In depth mathematical-analysis and experimentation of high-power SiC-FET based single-stage three-phase differential-based flyback inverter with practical design issues for grid-tied applications. Int. J. Electr. Power Energy Syst. 2022, 140, 108041. [Google Scholar] [CrossRef]

- Piriienko, S.; Röser, T.; Neuburger, M.; Balakhontsev, A. Current source gate drivers for 3-phase VSI operated in small-scale wind turbine systems. Int. J. Electr. Power Energy Syst. 2022, 141, 108160. [Google Scholar] [CrossRef]

- Zhang, R.; Liu, S.; Li, B.; Zhao, N.; Wang, G.; Xu, D. Totem-Pole Bridgeless Boost PFC Converter Based on GaN HEMT for Air Conditioning Applications. In Proceedings of the 2018 2nd IEEE Conference on Energy Internet and Energy System Integration (EI2), Beijing, China, 20–22 October 2018; pp. 1–9. [Google Scholar]

- Karaarslan, A.; Iskender, I. Analysis and comparison of current control methods on bridgeless converter to improve power quality. Int. J. Electr. Power Energy Syst. 2013, 51, 1–13. [Google Scholar] [CrossRef]

- Wang, L.; Wu, Q.H.; Tang, W.H.; Yu, Z.Y.; Ma, W. CCM-DCM average current control for both continuous and discontinuous conduction modes boost PFC converters. In Proceedings of the 2017 IEEE Electrical Power and Energy Conference (EPEC), Saskatoon, SK, Canada, 22–25 October 2017; pp. 1–6. [Google Scholar]

- Kim, J.W.; Moon, G.W. Minimizing Effect of Input Filter Capacitor in a Digital Boundary Conduction Mode Power Factor Corrector Based on Time-Domain Analysis. IEEE Trans. Power Electron. 2016, 31, 3827–3836. [Google Scholar] [CrossRef]

- Memon, A.H.; Baloach, M.H.; Sahito, A.A.; Soomro, A.M.; Memon, Z.A. Achieving High Input PF for CRM Buck-Buck/Boost PFC Converter. IEEE Access 2018, 6, 79082–79093. [Google Scholar] [CrossRef]

- Chrin, P.; Bunlaksananusorn, C. Novel Current Feedforward Average Current Mode Control Technique to Improve Output Dynamic Performance of DC-DC Converters. In Proceedings of the 2007 7th International Conference on Power Electronics and Drive Systems, Bangkok, Thailand, 27–30 November 2007; pp. 1416–1421. [Google Scholar]

- Youn, H.S.; Lee, J.B.; Baek, J.I.; Moon, G.W. A Digital Phase Leading Filter Current Compensation (PLFCC) Technique for CCM Boost PFC Converter to Improve PF in High Line Voltage and Light Load Conditions. IEEE Trans. Power Electron. 2016, 31, 6596–6606. [Google Scholar] [CrossRef]

- Sype, D.M.V.d.; Koen De, G.; Bossche, A.P.M.V.d.; Melkebeek, J.A. Duty-ratio feedforward for digitally controlled boost PFC converters. IEEE Trans. Ind. Electron. 2005, 52, 108–115. [Google Scholar] [CrossRef]

- Zhao, W.; Liu, B.; Duan, S.; Sheng, W.; Wu, M.; Song, Z. A Digital Control Method with Feedforward Reconstruction for Improved Sampling Interference Suppression in GaN HEMTs based Totem-pole PFC Converters. In Proceedings of the 2018 1st Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Xi’an, China, 16–18 May 2018; pp. 1–6. [Google Scholar]

- Park, S.M.; Lee, Y.D.; Park, S.Y. Voltage sensorless feedforward control of a dual boost PFC converter for battery charger applications. In Proceedings of the 2011 IEEE Energy Conversion Congress and Exposition, Phoenix, AZ, USA, 17–22 September 2011; pp. 1376–1380. [Google Scholar]

| Input voltage | 220 VAC |

| Output voltage | 400 VDC |

| Rated output power | 1600 W |

| Switching frequency | 100 kHz |

| Inductor | 350 μH |

| Magnetic core | NPS184060 |

| Number of windings turns | 50 |

| Enameled wire diameter | 1.63 mm |

| Output electrolytic capacitor | 7 × 150 μF/450 V |

| SiC MOSFET | C3M0030090K |

| Si MOSFET | Cool MOS IPW65R045C7 |

| Driver chip | IXDN609SIA |

| Isolator | ACPL-4800-300E |

| Controller | TMS320F280049 |

| Input Signal Frequency | Current Error | Voltage Error | Power Error |

|---|---|---|---|

| DC | 0.05% | 0.05% | 0.05% |

| 0.1–30 Hz | 0.03% | 0.05% | 0.08% |

| 30–45 Hz | 0.03% | 0.05% | 0.08% |

| 45–66 Hz | 0.03% | 0.05% | 0.05% |

| 66 Hz–1 kHz | 0.1% | 0.1% | 0.2% |

| 1–10 kHz | 0.15% | 0.1% | 0.3% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

He, H.; Zhang, D.; Zhou, A.; Zhang, F.; Zou, X.; Yuan, J.; Wei, M. Virtual Admittance Feedforward Compensation and Phase Correction for Average-Current-Mode-Controlled Totem-Pole PFC Converters. Appl. Sci. 2023, 13, 9498. https://doi.org/10.3390/app13179498

He H, Zhang D, Zhou A, Zhang F, Zou X, Yuan J, Wei M. Virtual Admittance Feedforward Compensation and Phase Correction for Average-Current-Mode-Controlled Totem-Pole PFC Converters. Applied Sciences. 2023; 13(17):9498. https://doi.org/10.3390/app13179498

Chicago/Turabian StyleHe, Hongkai, Desheng Zhang, Aosong Zhou, Fanwu Zhang, Xuecheng Zou, Jun Yuan, and Meng Wei. 2023. "Virtual Admittance Feedforward Compensation and Phase Correction for Average-Current-Mode-Controlled Totem-Pole PFC Converters" Applied Sciences 13, no. 17: 9498. https://doi.org/10.3390/app13179498