Design of Dual-Notch-Filter-Based Controllers for Enhancing the Dynamic Response of Universal Single-Phase Grid-Connected Power Converters

Abstract

:1. Introduction

- 1.

- It is suggested to combine a PI term with two notch filters, tuned to 50 Hz and 60 Hz, respectively, in order to support universal grid interfacing without the need for controller redesign.

- 2.

- The minimum allowed phase margin is used as the second performance merit (along with the maximum tolerable grid-side current THD) rather than the maximum tolerable transient DC link voltage deviation. Such an approach allows the optimization of the latter rather than setting a desired value a priori (which may lead to a non-existing solution, requiring further iterations).

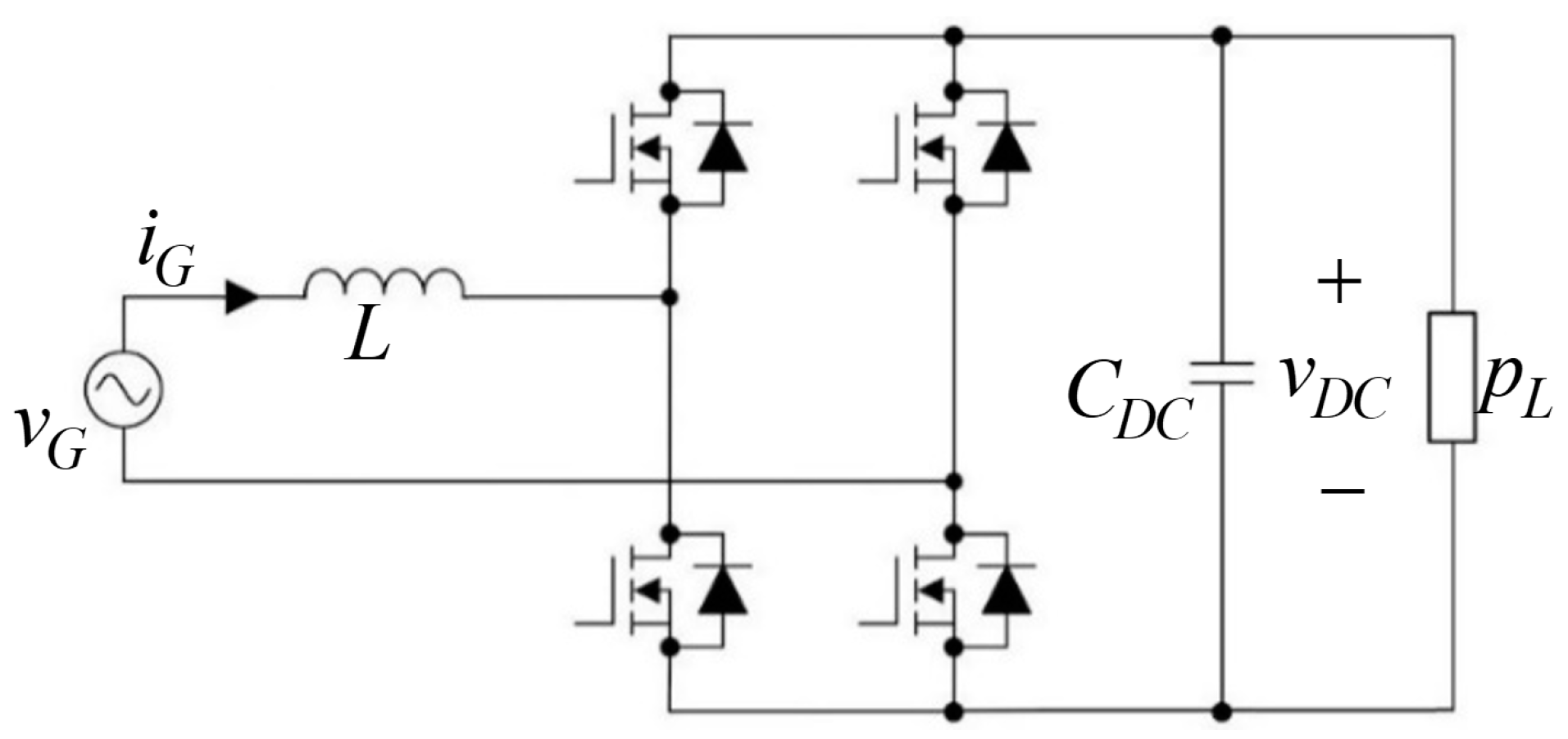

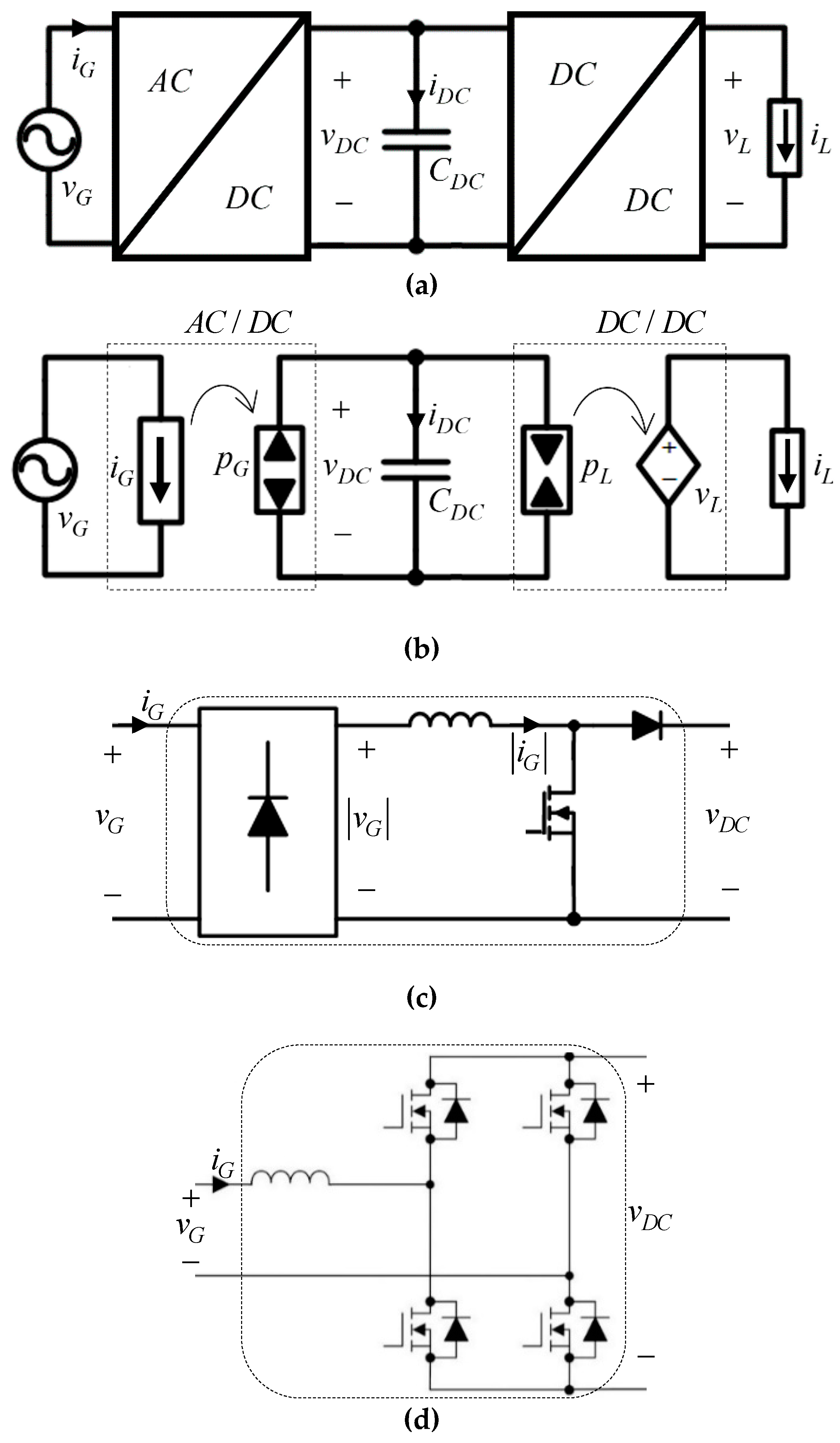

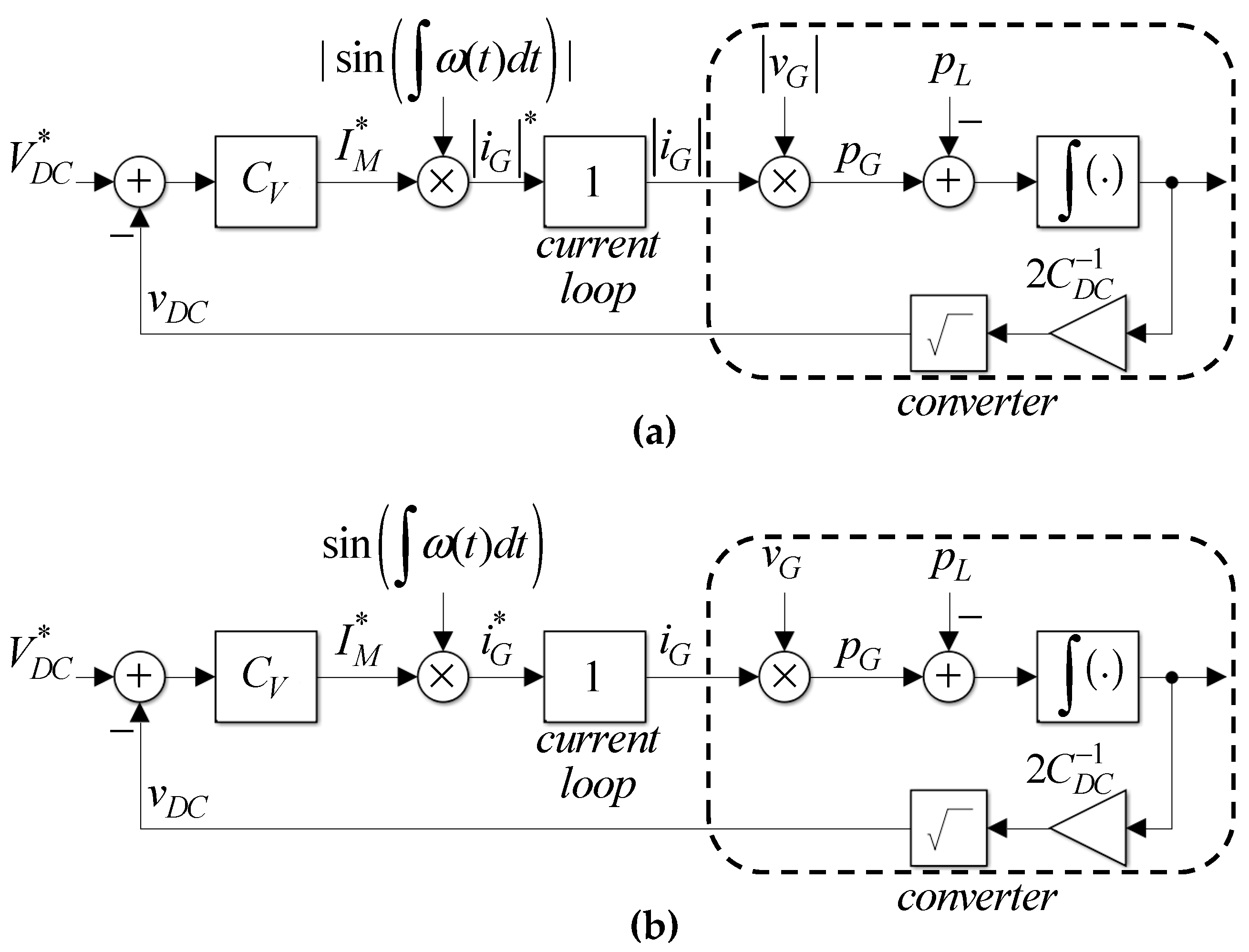

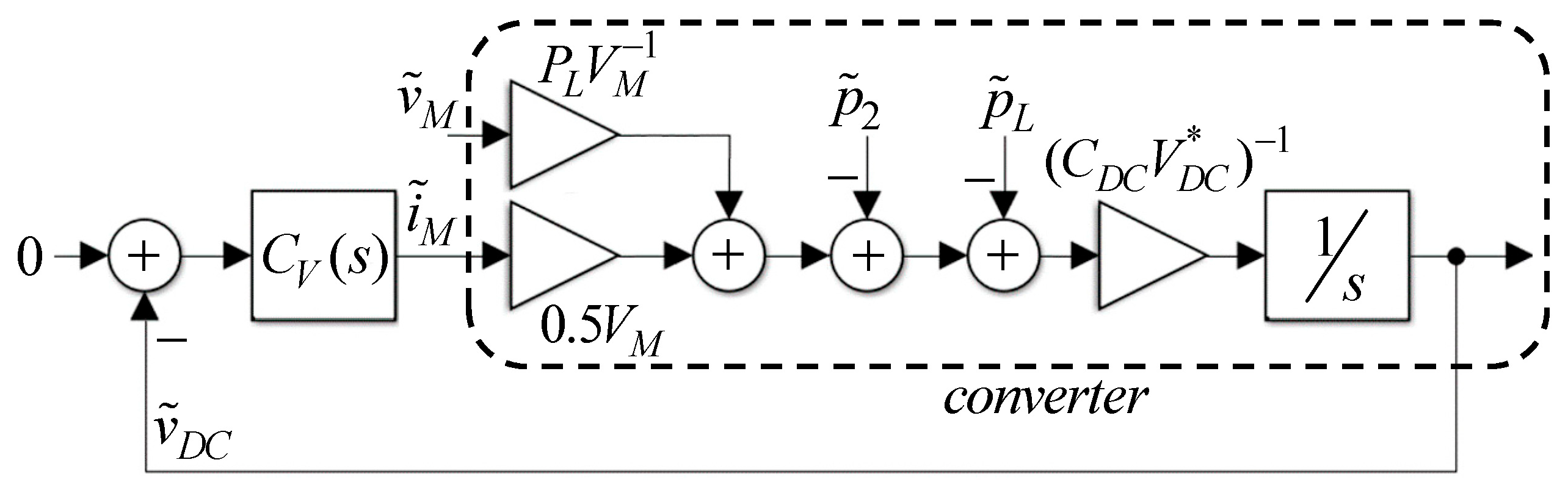

2. Single-Phase Grid-Connected Power Conversion System

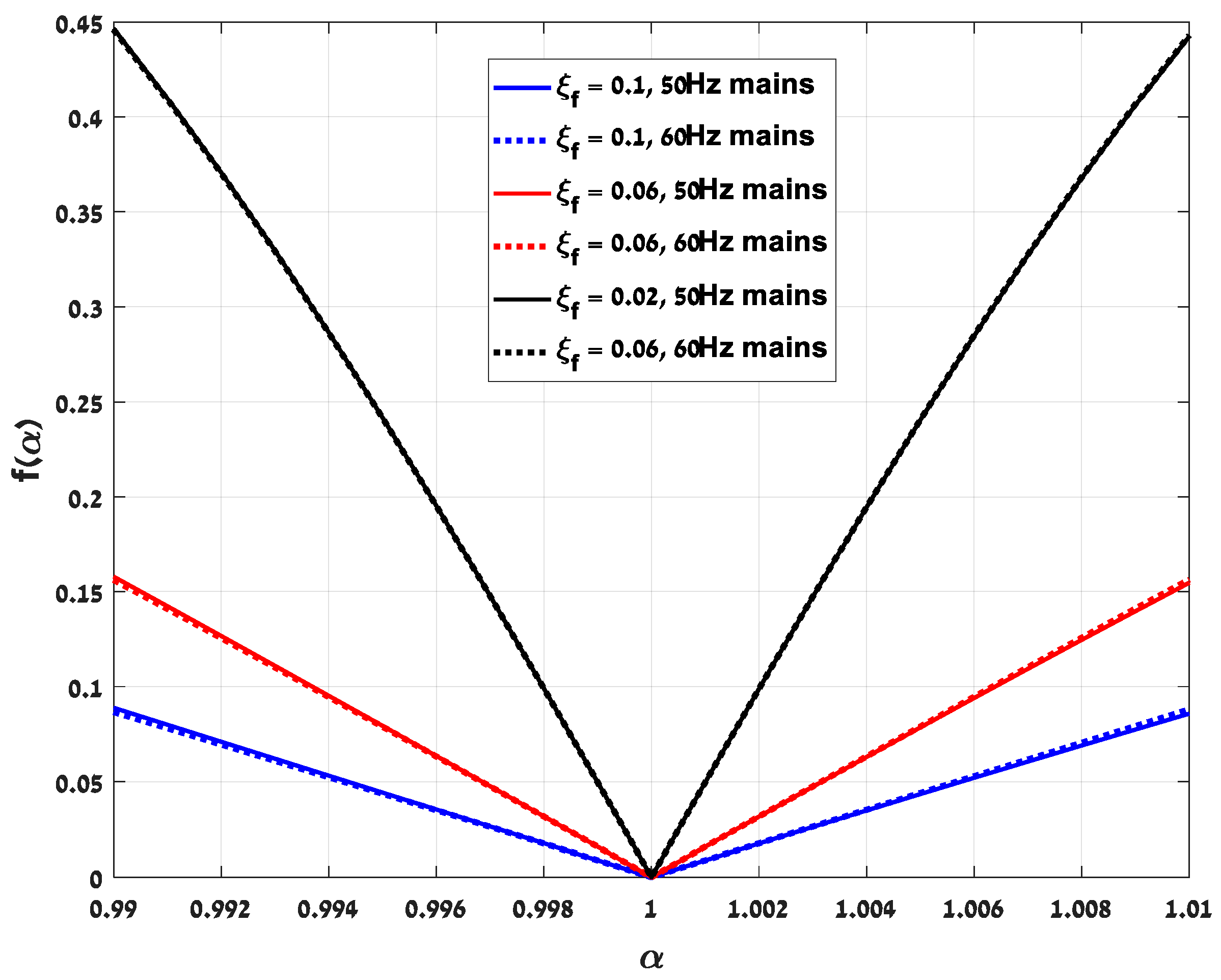

3. Total Harmonic Distortion

4. Dynamic Response

5. Controller Parameters Selection

- 1.

- Initialize βmax and.

- 2.

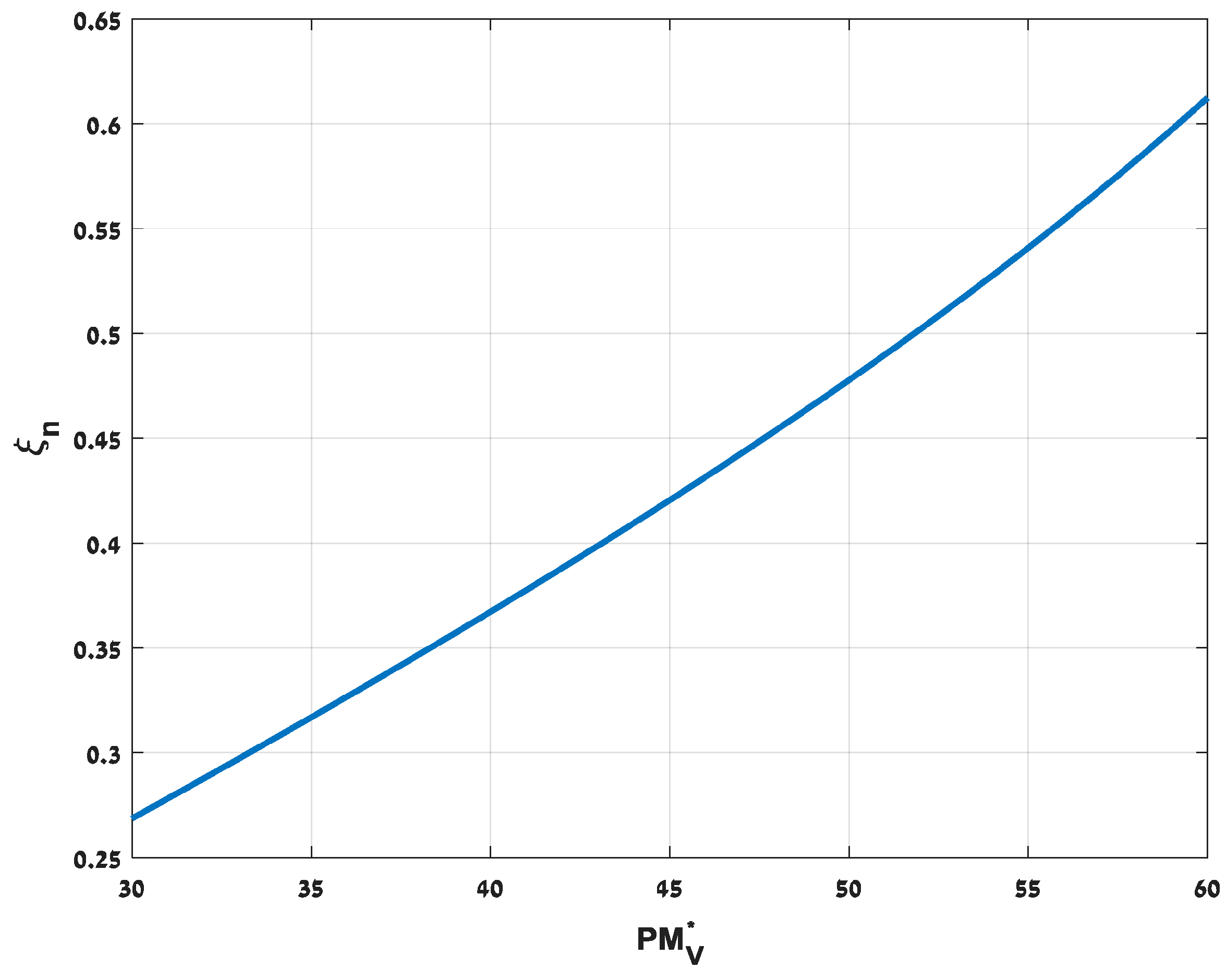

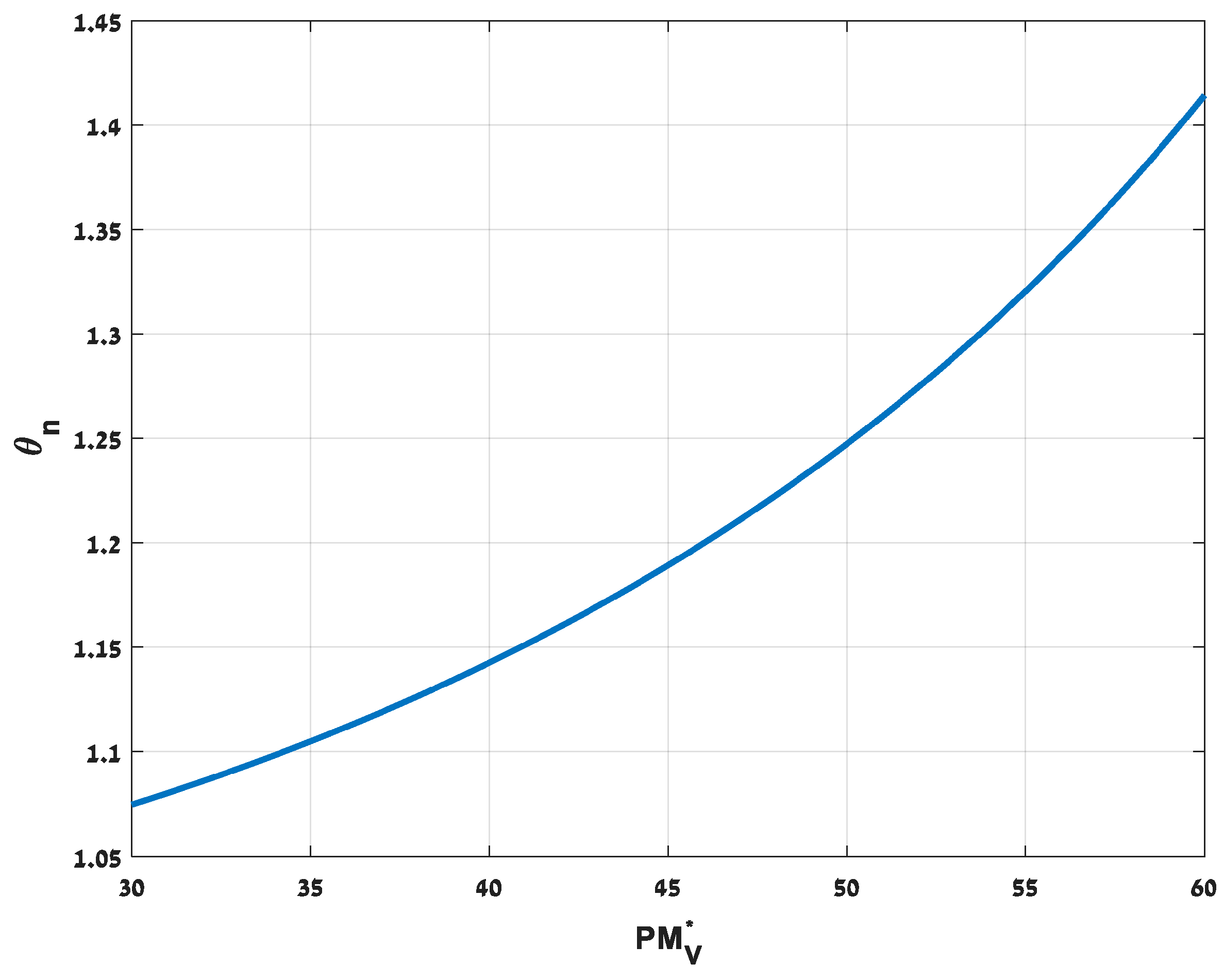

- Obtain using (36), ξn using (38) and λ using (43).

- 3.

- Initialize THD* and αmin.

- 4.

- Obtain ξf using (51) and ωn using (48).

- 5.

- Initialize VM, CDC and .

- 6.

- Determine K and τ using (52).

- 7.

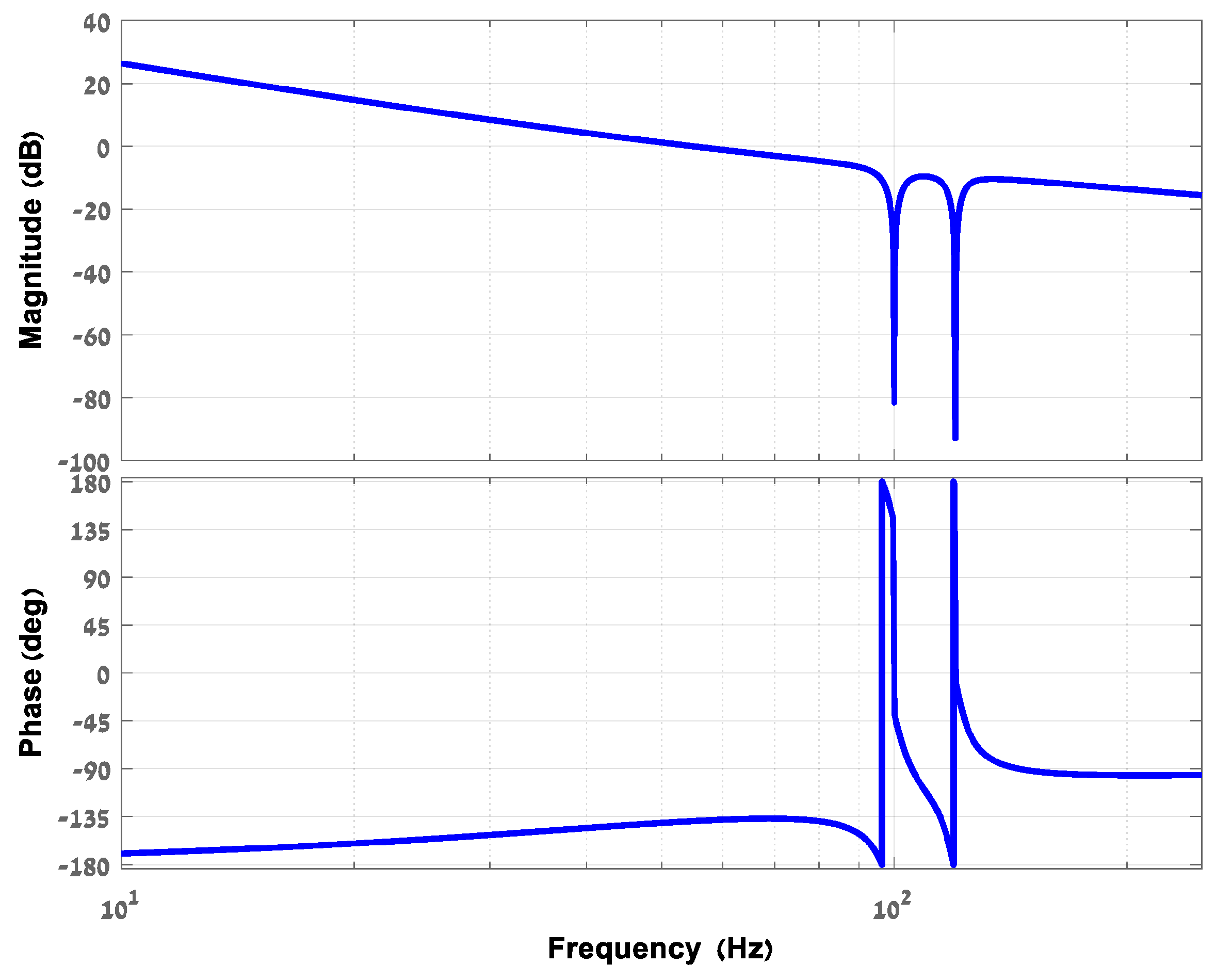

- Verify the design by Bode diagram.

- 8.

- Release requirement/s and iterate if necessary.

6. Example and Validation

- 1.

- β = 7.5° and = 40° + 7.5°.

- 2.

- = 1.2, ξn = 0.45 and λ = 0.066.

- 3.

- THD* = 0.05 and αmin = 0.99.

- 4.

- ξf = 0.047 and ωn = 2π∙45 rad/s.

- 5.

- VM = 325 V, CDC = and = 400 V.

- 6.

- K = 76 and τ = 0.0032.

6.1. Simulations

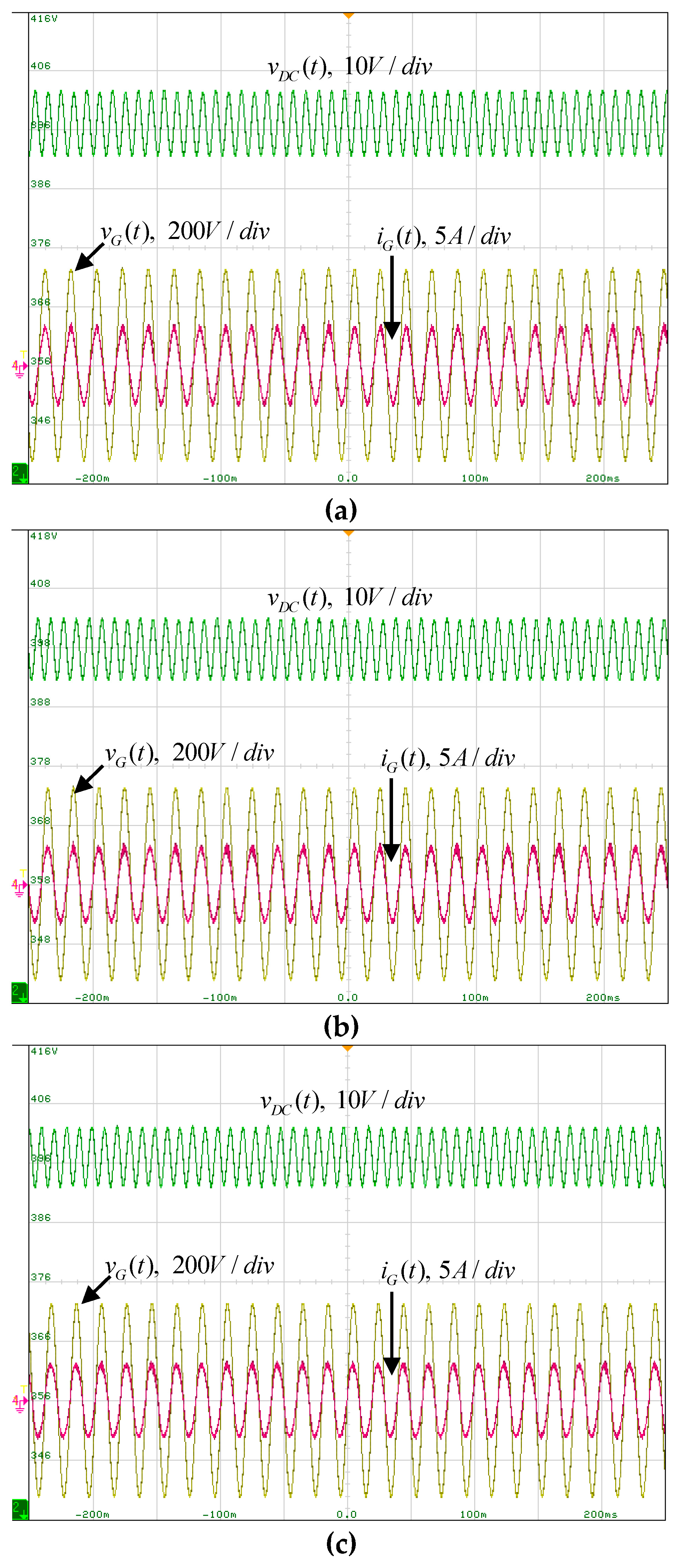

6.2. Experiments

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Zha, X.; Huang, M.; Liu, Y.; Tian, Z. An overview on safe operation of grid-connected converters from resilience perspective: Analysis and design. Int. J. Electr. Power Energy Syst. 2022, 143, 108511. [Google Scholar] [CrossRef]

- Taul, M.G.; Wang, X.; Davari, P.; Blaabjerg, F. Current reference generation based on next-generation grid code requirements of grid-tied converters during asymmetrical faults. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 3784–3797. [Google Scholar] [CrossRef]

- Liu, Y.; Li, L.; Shan, P.; Yu, H.; Zhang, S.; Huang, M.; Liu, W.; You, X.; Zhang, P.; Sun, Y.; et al. Coordinated mitigation control for wideband harmonic of the photovoltaic grid-connected inverter. Appl. Sci. 2023, 13, 7441. [Google Scholar] [CrossRef]

- Castellan, S.; Buja, G.; Menis, R. Single-phase power line conditioning with unity power factor under distorted utility voltage. Int. J. Electr. Power Energy Syst. 2020, 121, 106057. [Google Scholar] [CrossRef]

- Gazafrudi, S.M.M.; Langerudy, A.T.; Fuchs, E.F.; Al-Haddad, K. Power quality issues in railway electrification: A comprehensive perspective. IEEE Trans. Ind. Electron. 2015, 62, 3081–3090. [Google Scholar] [CrossRef]

- Awad, H.; Ibrahim, A.M.; De Santis, M.; Bayoumi, E.H.E. Unity power factor operation in microgrid applications using fuzzy type 2 nested controllers. Appl. Sci. 2023, 13, 5537. [Google Scholar] [CrossRef]

- Li, X.; Zhang, W.; Li, H.; Xie, R.; Chen, M.; Shen, G.; Xu, D. Power management unit with its control for a three-phase fuel cell power system without large electrolytic ca-pacitors. IEEE Trans. Power Electron. 2011, 26, 3766–3777. [Google Scholar] [CrossRef]

- Baek, J.-B.; Choi, W.-I.; Cho, B.-H. Digital adaptive frequency modulation for bidirectional DC–DC converter. IEEE Trans. Ind. Electron. 2013, 60, 5167–5176. [Google Scholar] [CrossRef]

- Wen, H.; Xiao, W.; Wen, X.; Armstrong, P. Analysis and evaluation of DC-Link capacitors for high-power-density electric vehicle drive systems. IEEE Trans. Veh. Technol. 2012, 61, 2950–2964. [Google Scholar] [CrossRef]

- Mellincovsky, M.; Yuhimenko, V.; Peretz, M.M.; Kuperman, A. Low-frequency DC-link ripple elimination in power converters with reduced capacitance by multi-resonant direct voltage regulation. IEEE Trans. Ind. Electron. 2017, 64, 2015–2023. [Google Scholar] [CrossRef]

- Strajnikov, P.; Peretz, M.M.; Kuperman, A. Reduced-rating-electronic-capacitor-based DC links for power electronics sup-ported distributed energy resources. IEEE Trans. Smart Grid 2022, 13, 3943–3953. [Google Scholar] [CrossRef]

- Wang, H.; Wang, H.; Zhu, G.; Blaabjerg, F. An overview of capacitive DC links topology derivation and scalability analysis. IEEE Trans. Power Electron. 2020, 35, 1805–1829. [Google Scholar] [CrossRef]

- Cheikh-Mohamad, S.; Celik, B.; Sechilariu, M.; Locment, F. PV-Powered Charging Station with Energy Cost Optimization via V2G Services. Appl. Sci. 2023, 13, 5627. [Google Scholar] [CrossRef]

- Khajehoddin, S.A.; Karimi-Ghartemani, M.; Jain, P.K.; Bakhshai, A. DC-Bus Design and control for a single-phase grid-connected renewable converter with a small energy storage component. IEEE Trans. Power Electron. 2013, 28, 3245–3254. [Google Scholar] [CrossRef]

- Mallik, A.; Lu, J.; Khaligh, A. Notice of Removal: A Comparative study between PI and Type-II compensators for H-bridge PFC converter. IEEE Trans. Ind. Appl. 2018, 54, 1128–1135. [Google Scholar] [CrossRef]

- Nabatirad, M.; Razzaghi, R.; Bahrani, B. Autonomous power balance in hybrid AC/DC microgrids. Int. J. Electr. Power Energy Syst. 2023, 146, 108752. [Google Scholar] [CrossRef]

- Mellincovsky, M.; Yuhimenko, V.; Peretz, M.M.; Kuperman, A. Analysis and control of direct voltage regulated active DC-link capacitance reduction circuit. IEEE Trans. Power Electron. 2018, 33, 6318–6332. [Google Scholar] [CrossRef]

- Mellincovsky, M.; Yuhimenko, V.; Zhong, Q.-C.; Peretz, M.M.; Kuperman, A. Active DC link capacitance reduction in grid-connected power conversion systems by direct voltage regulation. IEEE Access 2018, 6, 18163–18173. [Google Scholar] [CrossRef]

- Liu, B.; Song, D.; He, D.; Song, S.; Yang, J.; Su, M.; Lu, Y.; Chen, Y.; Liu, H. A modified modulation for single-phase photovoltaic/battery inverter to improve AC power quality with low DC-link capacitance. Int. J. Electr. Power Energy Syst. 2019, 110, 705–712. [Google Scholar] [CrossRef]

- Mutovkin, A.; Yuhimenko, V.; Mellincovsky, M.; Schacham, S.; Kuperman, A. Control of direct voltage regulated active DC-link capacitance reduction circuits to allow plug-and-play operation. IEEE Trans. Ind. Electron. 2019, 66, 6527–6537. [Google Scholar] [CrossRef]

- Merai, M.; Naouar, M.; Slama-Belkhodja, I.; Monmasson, E. A systematic design methodology for DC-link voltage control of single phase grid-tied PV systems. Math. Comput. Simul. 2021, 183, 158–170. [Google Scholar] [CrossRef]

- Strajnikov, P.; Kuperman, A. Guidelines for voltage controller coefficients design to attain prescribed grid current THD and DC-link voltage undershoot values in power factor correction front ends. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 6523–6533. [Google Scholar] [CrossRef]

- Kuperman, A. On the explicit relation between mains-side current THD and DC link voltage controller gain in grid-connected converters. In Proceedings of the 2022 IEEE 26th International Conference on Intelligent Engineering Systems (INES), Georgioupolis Chania, Greece, 12–15 August 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 000069–000072. [Google Scholar] [CrossRef]

- Sebastián, J.; Lamar, D.G.; Rodríguez-Alonso, A.; de Azpeitia, M.A.P.; Gonzalez, A.F. On the maximum bandwidth attainable by power factor correctors with a standard compensator. IEEE Trans. Ind. Appl. 2010, 46, 1485–1497. [Google Scholar] [CrossRef]

- Mutovkin, A.; Mellincovsky, M.; Yuhimenko, V.; Schacham, S.; Kuperman, A. Conditions for direct applicability of electronic capacitors to dual-stage grid-connected power conversion systems. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1805–1814. [Google Scholar] [CrossRef]

- Zarei, S.F.; Mokhtari, H.; Ghasemi, M.A.; Peyghami, S.; Davari, P.; Blaabjerg, F. DC-link loop bandwidth selection strategy for grid-connected inverters considering power quality requirements. Int. J. Electr. Power Energy Syst. 2020, 119, 105879. [Google Scholar] [CrossRef]

- Ghosh, R.; Narayanan, G. Generalized feed-forward control of single phase PWM rectifiers using disturbance observes. IEEE Trans. Ind. Electron. 2007, 54, 984–993. [Google Scholar] [CrossRef]

- Figures, E.; Benavent, J.M.; Garcera, G.; Pascual, M. A control circuit with load-current injection for single-phase pow-er-factor-correction rectifiers. IEEE Trans. Ind. Electron. 2007, 54, 1272–1282. [Google Scholar] [CrossRef]

- Yao, K.; Wu, C.; Chen, J.; Yang, J.; Li, J.; Jin, Z.; Wang, S.; Yang, R.; Liu, L.; Gao, Y.; et al. A Scheme to improve power factor and dynamic response performance for CRM/DCM Buck–Buck/Boost PFC converter. IEEE Trans. Power Electron. 2021, 36, 1828–1843. [Google Scholar] [CrossRef]

- Chiang, H.C.; Lin, F.J.; Chang, J.K.; Chen, K.F.; Chen, Y.L.; Liu, K.C. Control method for improving the response of single-phase continuous conduction mode boost power factor correction rectifier. IET Power Electron. 2016, 9, 1792–1800. [Google Scholar] [CrossRef]

- Pena-Alzola, R.; Bianchi, M.A.; Ordonez, M. Control Design of a PFC with Harmonic mitigation function for small hybrid AC/DC buildings. IEEE Trans. Power Electron. 2016, 31, 6607–6620. [Google Scholar] [CrossRef]

- Leung, K.H.; Loo, K.H.; Lai, Y.M. Unity-power-factor control based on precise ripple cancellation for fast-response PFC preregulator. IEEE Trans. Power Electron. 2016, 31, 3324–3337. [Google Scholar] [CrossRef]

- Leung, K.H.; Loo, K.H.; Lai, Y.M. A Family of ripple estimation–Cancellation methods based on switched-resistor circuits and their application in fast-response PFC preregulator. IEEE Trans. Power Electron. 2017, 32, 2608–2621. [Google Scholar] [CrossRef]

- Li, S.; Lu, W.; Yan, S.; Zhao, Z. Improving dynamic performance of boost pfc converter using current-harmonic feedforward compensation in synchronous reference frame. IEEE Trans. Ind. Electron. 2020, 67, 4857–4866. [Google Scholar] [CrossRef]

- Lu, W.; Han, J.; Li, S.; Iu, H.H.-C. Mitigating line frequency instability of boost pfc converter under proportional outer-voltage loop with additional third current-harmonic feedforward compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 4528–4541. [Google Scholar] [CrossRef]

- Luo, H.; Xu, J.; He, D.; Sha, J. Pulse train control strategy for CCM boost PFC converter with improved dynamic response and unity power factor. IEEE Trans. Ind. Electron. 2020, 67, 10377–10387. [Google Scholar] [CrossRef]

- Kessal, A.; Rahmani, L. Analysis and design of sliding mode controller gains for boost power factor corrector. ISA Trans. 2013, 52, 638–643. [Google Scholar] [CrossRef]

- Mohanty, P.R.; Panda, A.K. Fixed-frequency sliding-mode control scheme based on current control manifold for improved dynamic performance of boost PFC converter. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 576–586. [Google Scholar] [CrossRef]

- Bouafassa, A.; Rahmani, L.; Kessal, A.; Babes, B. Unity power factor Converter based on a Fuzzy controller and Predictive Input Current. ISA Trans. 2014, 53, 1817–1821. [Google Scholar] [CrossRef]

- Merai, M.; Naouar, M.W.; Slama-Belkhodja, I.; Monmasson, E. An adaptive pi controller design for dc-link voltage control of single-phase grid-connected converters. IEEE Trans. Ind. Electron. 2019, 66, 6241–6249. [Google Scholar] [CrossRef]

- Ma, W.; Wang, M.; Liu, S.; Li, S.; Yu, P. Stabilizing the average-current-mode-controlled boost PFC converter via washout-filter-aided method. IEEE Trans. Circuits Syst. II Express Briefs 2011, 58, 595–599. [Google Scholar] [CrossRef]

- Nair, H.S.; Narasamma, L. Simple digital algorithm for improved performance in a boost PFC converter operating in CCM. IET Power Electron. 2019, 12, 1102–1113. [Google Scholar] [CrossRef]

- Buso, S.; Mattavelli, P.; Rossetto, L.; Spiazzi, G. Simple digital control improving dynamic performance of power factor preregulators. IEEE Trans. Power Electron. 1998, 13, 814–823. [Google Scholar] [CrossRef]

- El Aroudi, A.; Haroun, R.; Cid-Pastor, A.; Martinez-Salamero, L. Suppression of line frequency instabilities in PFC AC-DC power supplies by feedback notch filtering the pre-regulator output voltage. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 796–809. [Google Scholar] [CrossRef]

- Karimi-Ghartemani, M.; Khajehoddin, S.A.; Jain, P.K.; Bakhshai, A. A systematic approach to DC-bus control design in single-phase grid-connected renewable converters. IEEE Trans. Power Electron. 2013, 28, 3158–3166. [Google Scholar] [CrossRef]

- Cheung, M.K.H.; Chow, M.H.L.; Tse, C.K. An analog implementation to improve load transient response of PFC pre-regulators. In Proceedings of the INTELEC 07-29th International Telecommunications Energy Conference, Rome, Italy, 30 September–4 October 2007; pp. 848–855. [Google Scholar]

- Levron, Y.; Canaday, S.; Erickson, R.W. Bus voltage control with zero distortion and high bandwidth for single-phase solar inverters. IEEE Trans. Power Electron. 2016, 31, 258–269. [Google Scholar] [CrossRef]

- Taghizadeh, S.; Hossain, M.J.; Lu, J.; Karimi-Ghartemani, M. An Enhanced DC-bus voltage-control loop for single-phase grid-connected DC/AC converters. IEEE Trans. Power Electron. 2019, 34, 5819–5829. [Google Scholar] [CrossRef]

- Cho, Y.; Lai, J.-S. Digital plug-in repetitive controller for single-phase bridgeless PFC converters. IEEE Trans. Power Electron. 2013, 28, 165–175. [Google Scholar] [CrossRef]

- Vule, Y.; Kuperman, A. Plug-in disturbance observer assisted DC link voltage control of grid-connected converters to improve transient performance without deteriorating grid current quality. Int. J. Electr. Power Energy Syst. 2022, 143, 108439. [Google Scholar] [CrossRef]

- Strajnikov, P.; Kuperman, A. Selection of PI+Notch voltage controller coefficients to attain desired steady-state and transient performance in PFC rectifiers. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 6534–6544. [Google Scholar] [CrossRef]

- Vule, Y.; Kuperman, A. Fast and robust DC link voltage control of single-phase grid-connected converters supporting 50 Hz and 60 Hz mains with universal magnitudes range. Int. J. Electr. Power Energy Syst. 2023, 154, 109430. [Google Scholar] [CrossRef]

- Holmes, D.G.; Lipo, T.A.; McGrath, B.P.; Kong, W.Y. Optimized design of stationary frame three phase AC current regulators. IEEE Trans. Power Electron. 2009, 24, 2417–2426. [Google Scholar] [CrossRef]

- Borafker, S.; Kuperman, A. Dual-notch-filter equipped DC link voltage controller for single-phase grid-connected converters. In Proceedings of the of the 15th International Conference on Electronics and Communication Systems, Ierapetra, Greece, 25–27 August 2023. [Google Scholar]

- Singer, S.; Erickson, R. Power-source element and its properties. IEE Proc. Circuits Devices Syst. 1994, 141, 220–226. [Google Scholar] [CrossRef]

- Elkayam, M.; Kolesnik, S.; Basha, Y.; Kuperman, A. Loop shaping by single-resonant controllers for prescribed tracking of sinusoidal references. IEEE Trans. Power Electron. 2019, 34, 11352–11360. [Google Scholar] [CrossRef]

- Yepes, A.G.; Freijedo, F.D.; Doval-Gandoy, J.; López, Ó.; Malvar, J.; Fernandez-Comesaña, P. Effects of discretization methods on the performance of resonant controllers. IEEE Trans. Power Electron. 2010, 25, 1692–1712. [Google Scholar] [CrossRef]

| ωG/2π | 49.5 Hz | 50 Hz | 50.5 Hz | 59.4 Hz | 60 Hz | 60.6 Hz |

|---|---|---|---|---|---|---|

| THD% | 5 | 0.1 | 4.52 | 3.98 | 0.067 | 3.68 |

| ωG/2π | 49.5 Hz | 50 Hz | 50.5 Hz | 59.4 Hz | 60 Hz | 60.6 Hz |

|---|---|---|---|---|---|---|

| THD | 0.0535 | 0.0261 | 0.053 | 0.0528 | 0.0212 | 0.046 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Borafker, S.; Strajnikov, P.; Kuperman, A. Design of Dual-Notch-Filter-Based Controllers for Enhancing the Dynamic Response of Universal Single-Phase Grid-Connected Power Converters. Appl. Sci. 2023, 13, 10144. https://doi.org/10.3390/app131810144

Borafker S, Strajnikov P, Kuperman A. Design of Dual-Notch-Filter-Based Controllers for Enhancing the Dynamic Response of Universal Single-Phase Grid-Connected Power Converters. Applied Sciences. 2023; 13(18):10144. https://doi.org/10.3390/app131810144

Chicago/Turabian StyleBorafker, Sahar, Pavel Strajnikov, and Alon Kuperman. 2023. "Design of Dual-Notch-Filter-Based Controllers for Enhancing the Dynamic Response of Universal Single-Phase Grid-Connected Power Converters" Applied Sciences 13, no. 18: 10144. https://doi.org/10.3390/app131810144

APA StyleBorafker, S., Strajnikov, P., & Kuperman, A. (2023). Design of Dual-Notch-Filter-Based Controllers for Enhancing the Dynamic Response of Universal Single-Phase Grid-Connected Power Converters. Applied Sciences, 13(18), 10144. https://doi.org/10.3390/app131810144