A Low-Power ECG Processor ASIC Based on an Artificial Neural Network for Arrhythmia Detection

Abstract

:1. Introduction

2. Overall Architecture

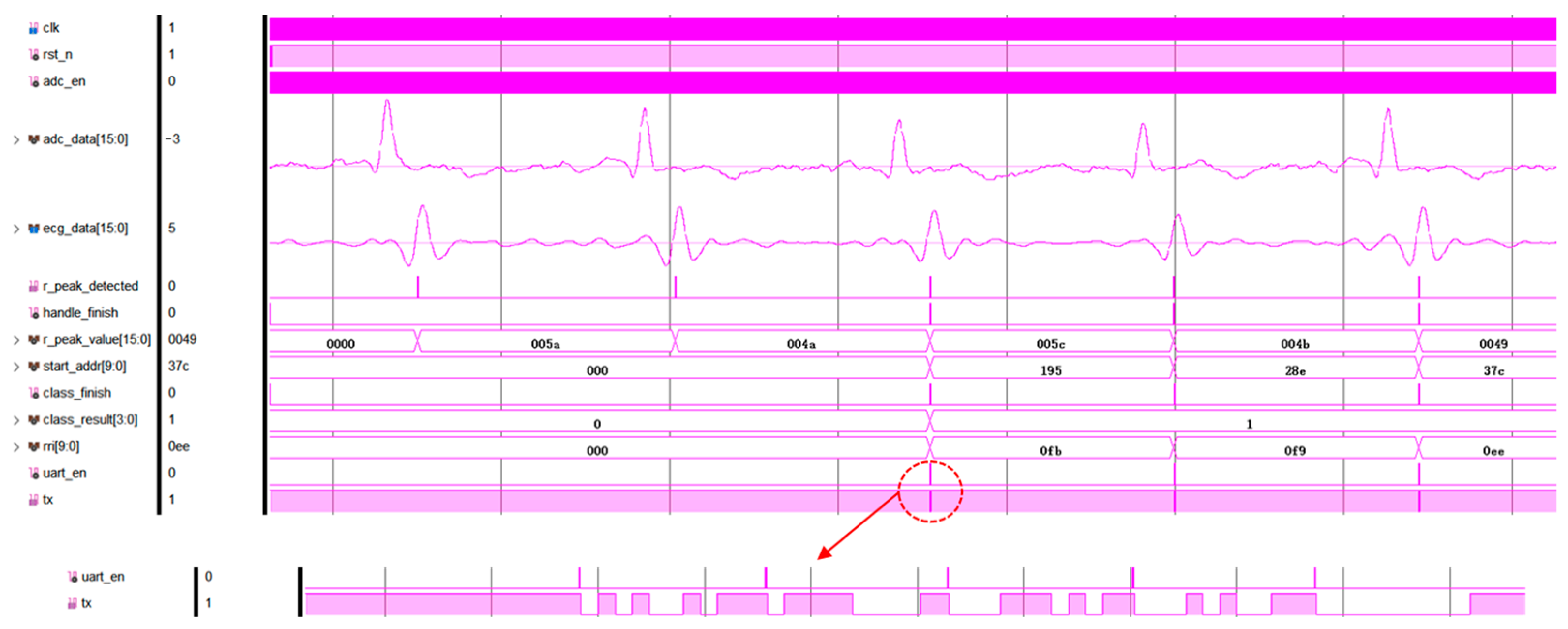

3. System Modules

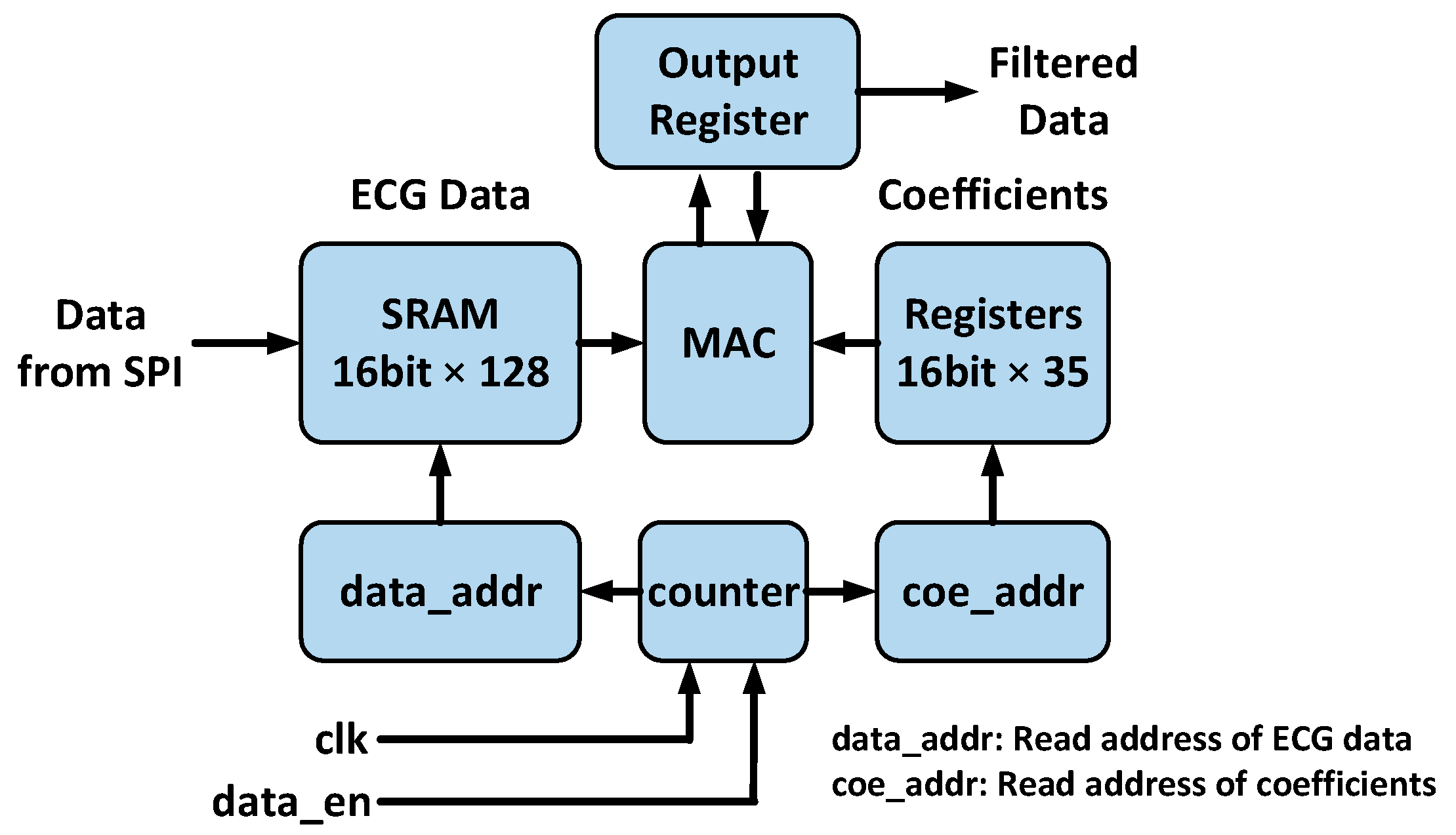

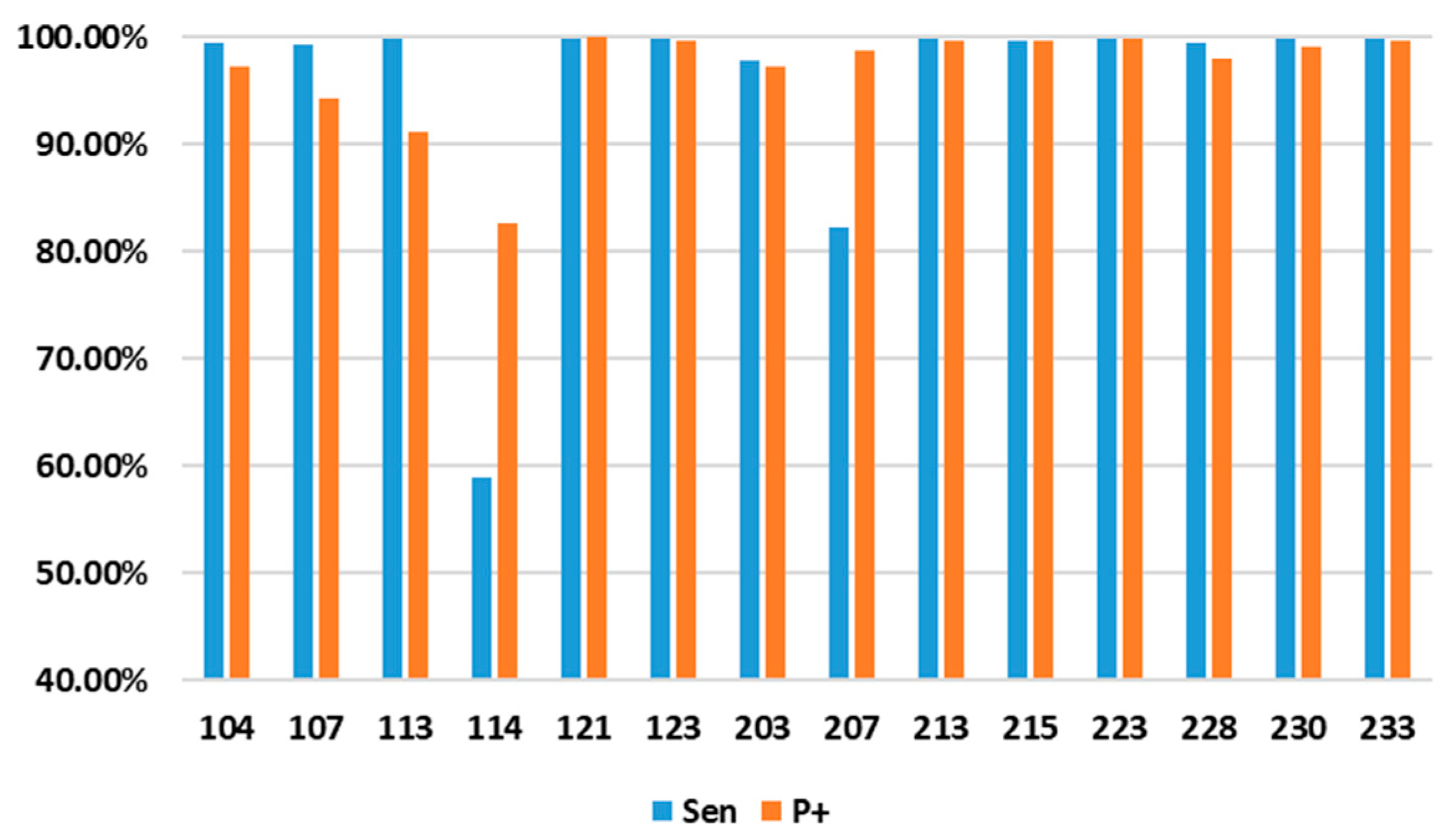

3.1. Pre-Processing Engine

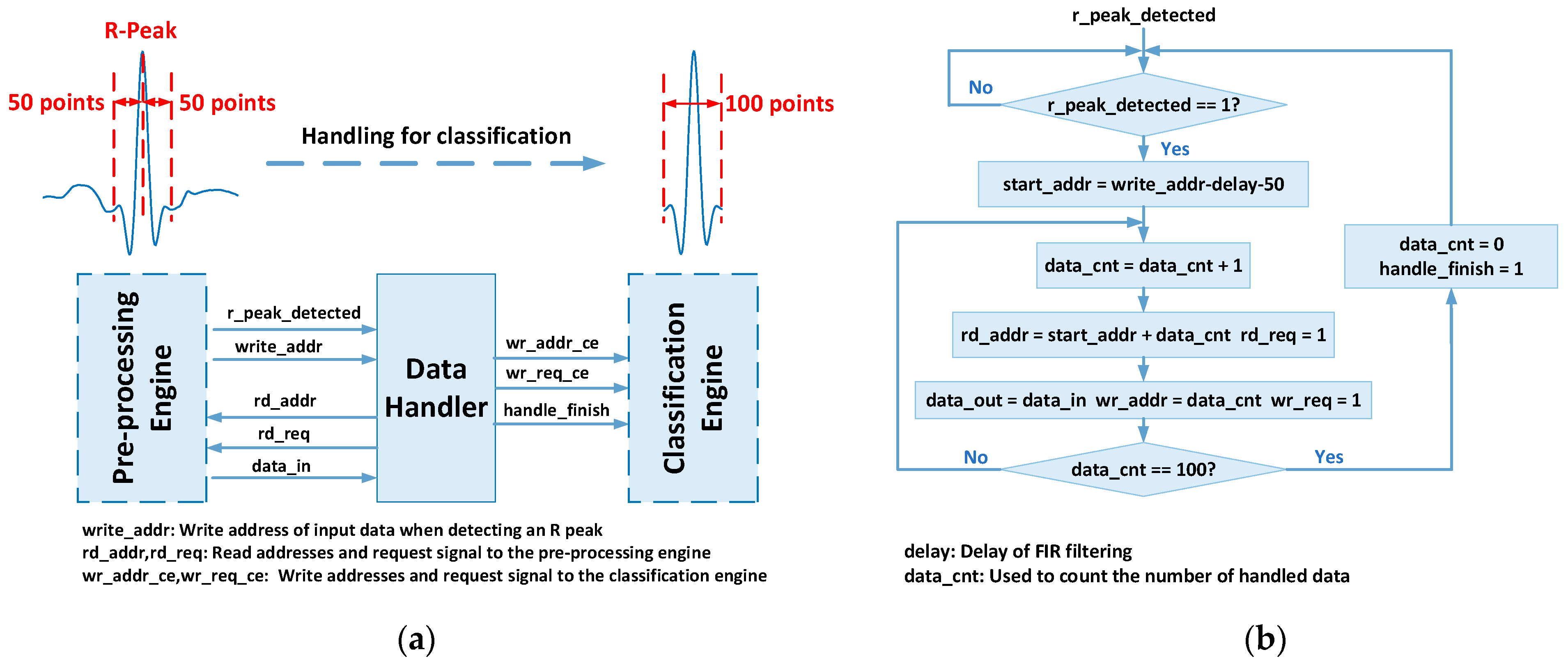

3.2. Data Handler

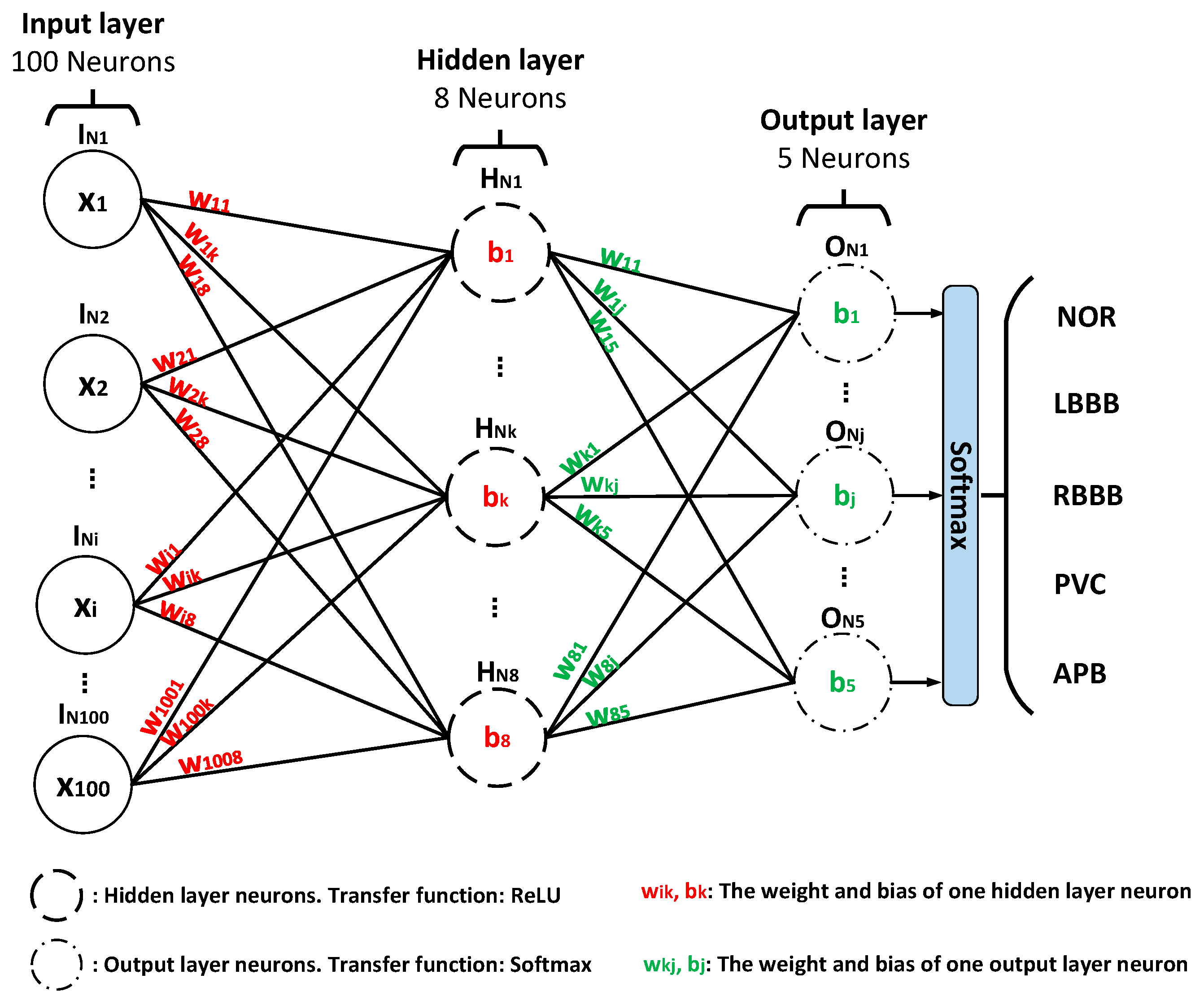

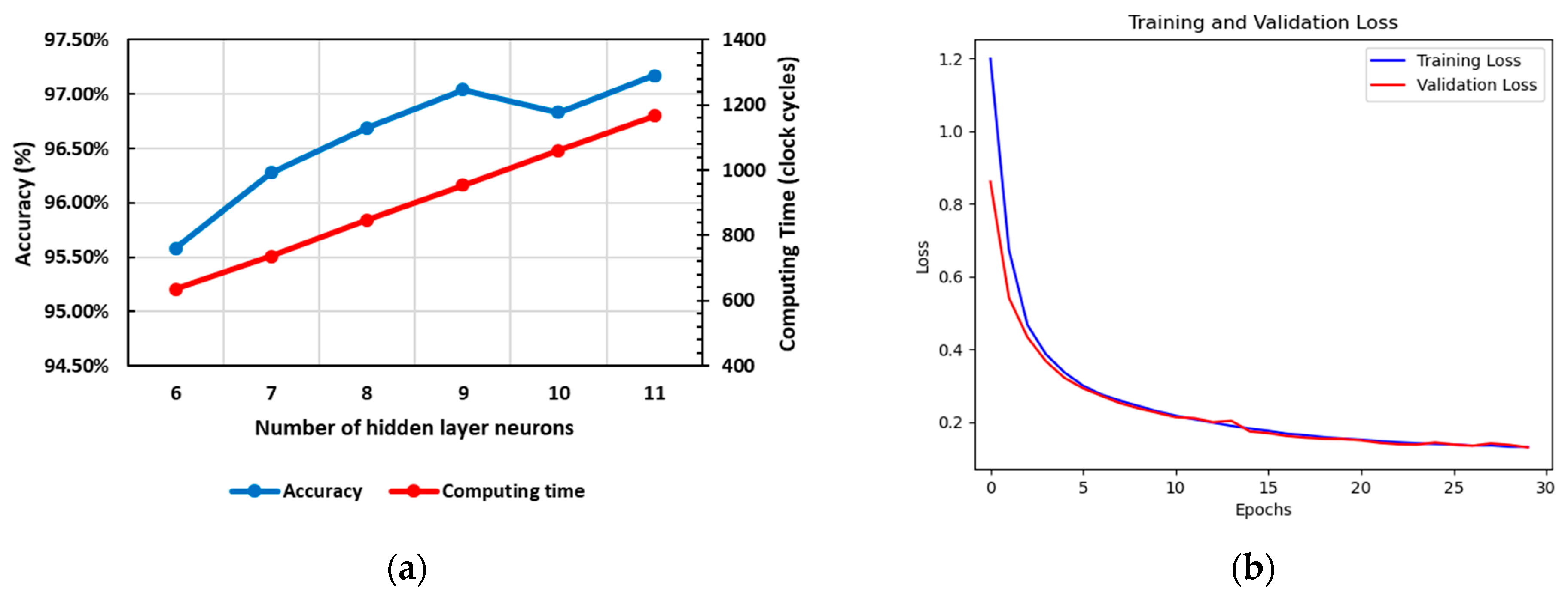

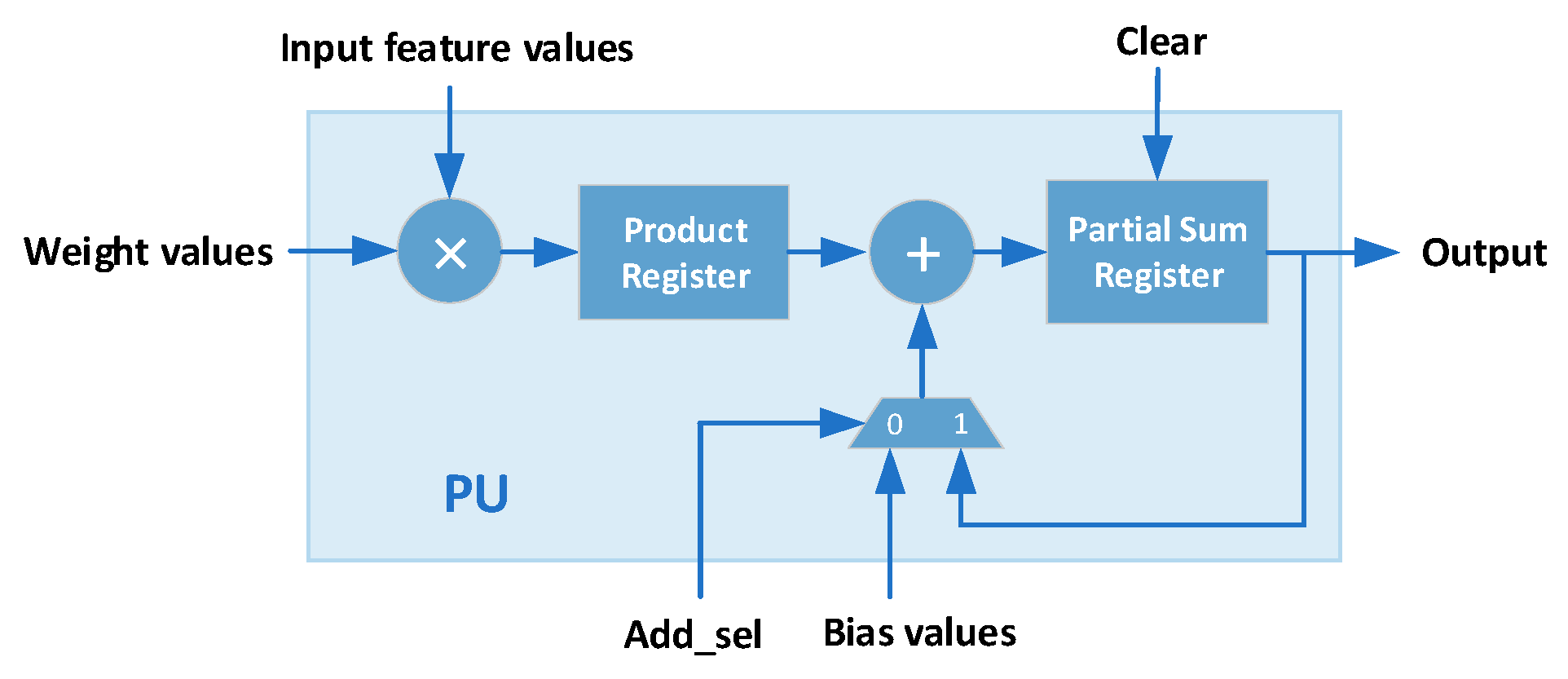

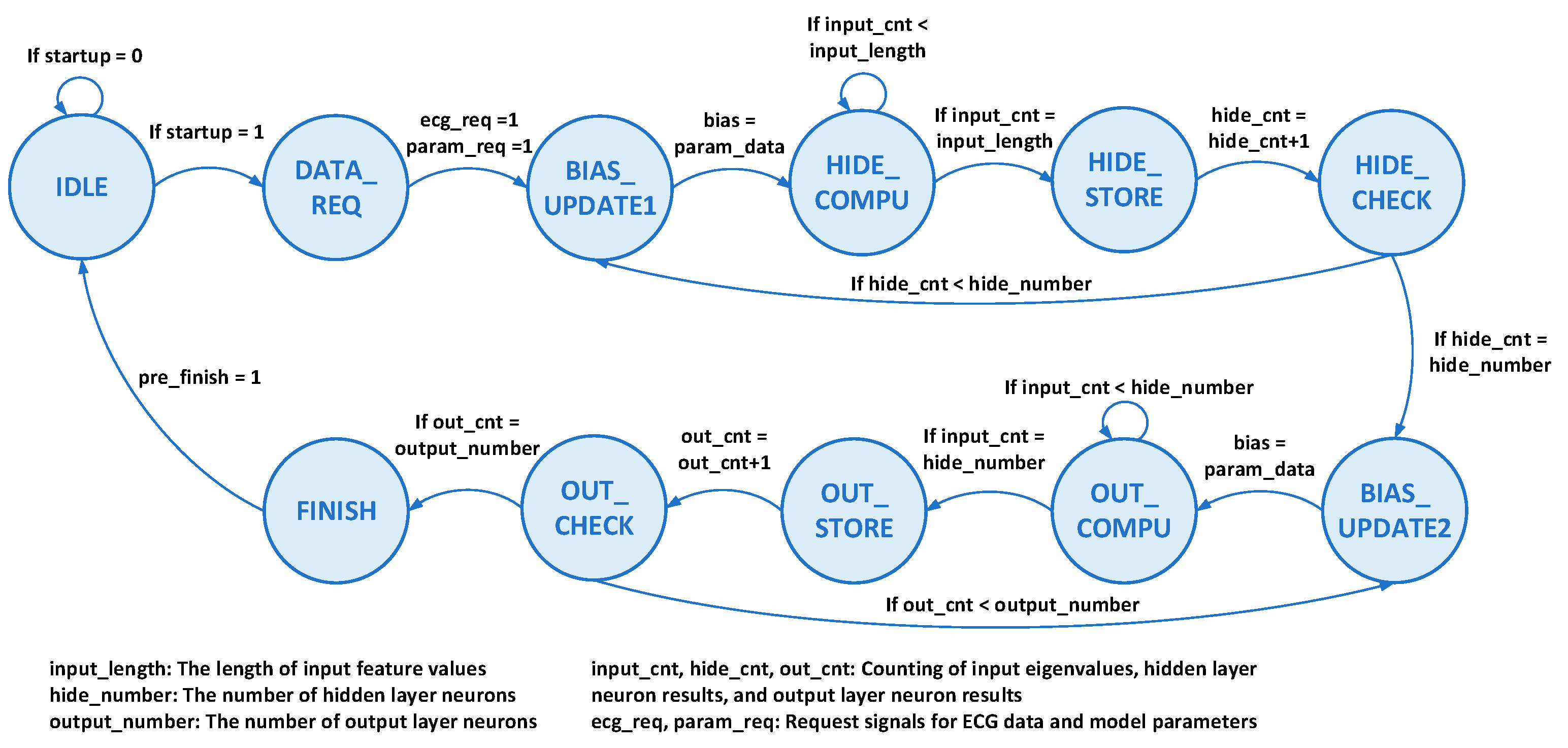

3.3. Classification Engine

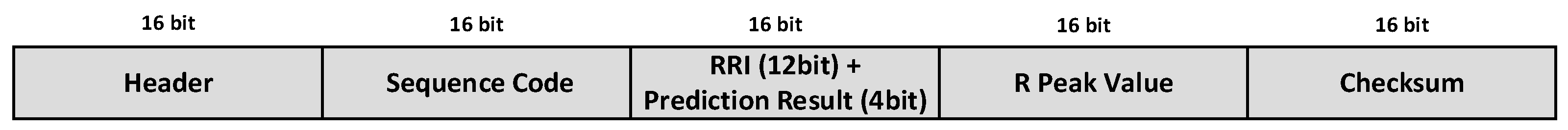

3.4. Data Transmitter

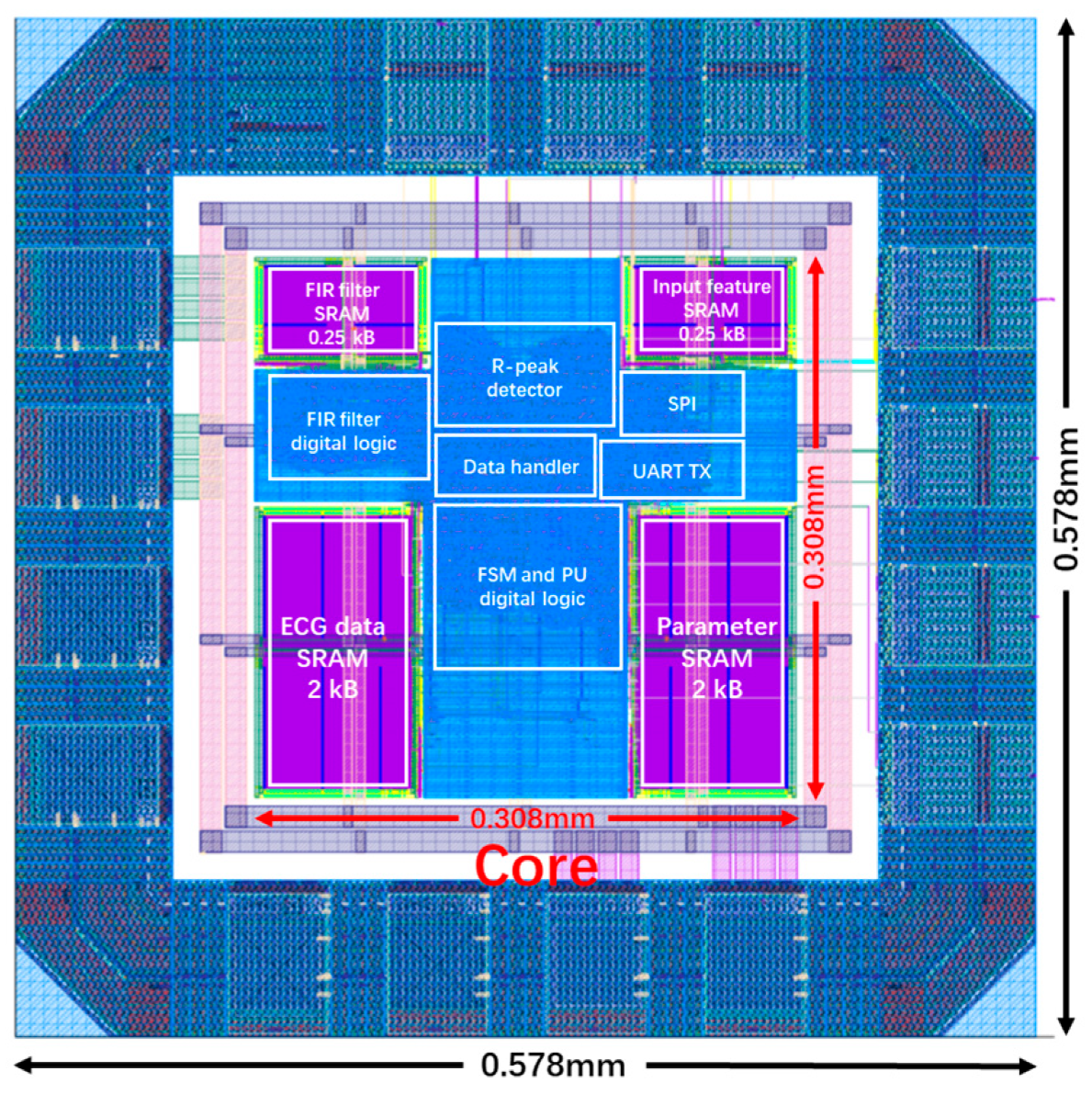

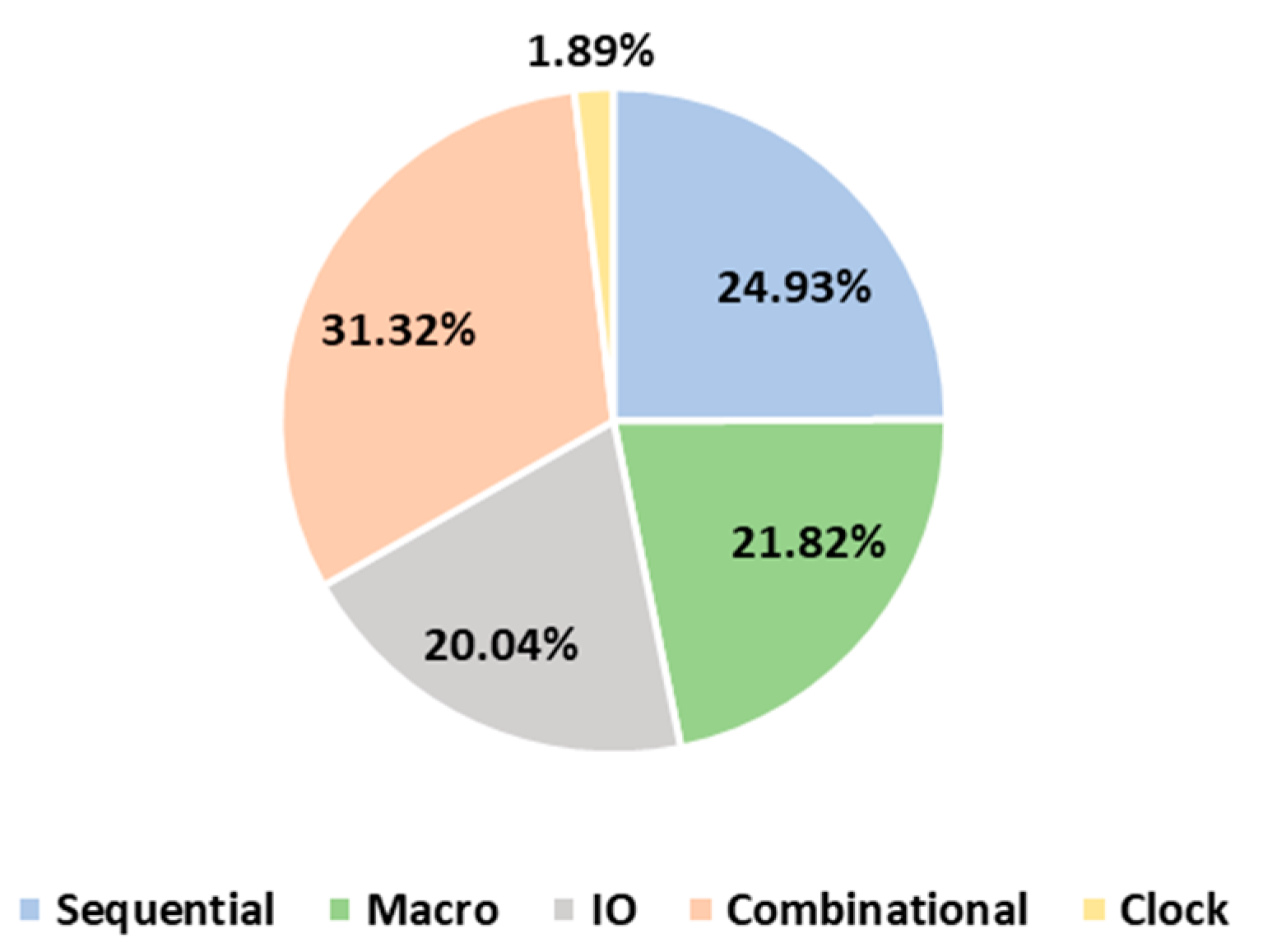

4. Hardware Implementation

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Luna, A.; Coumel, P.; Leclercq, J. Ambulatory sudden cardiac death: Mechanisms of production of fatal arrhythmia on the basis of data from 157 cases. Am. Heart J. 1989, 117, 151–159. [Google Scholar] [CrossRef] [PubMed]

- Verma, N.; Shoeb, A.; Bohorquez, J.; Dawson, J.; Guttag, J.; Chandrakasan, A.P. A Micro-Power EEG Acquisition SoC with Integrated Feature Extraction Processor for a Chronic Seizure Detection System. IEEE J. Solid State Circuits 2010, 45, 804–816. [Google Scholar] [CrossRef]

- Kwong, J.; Chandrakasan, A.P. An Energy-Efficient Biomedical Signal Processing Platform. IEEE J. Solid State Circuits 2011, 46, 1742–1753. [Google Scholar] [CrossRef]

- Hsu, S.-Y.; Ho, Y.; Chang, P.-Y.; Su, C.; Lee, C.-Y. A 48.6-to-105.2 µW Machine Learning Assisted Cardiac Sensor SoC for Mobile Healthcare Applications. IEEE J. Solid State Circuits 2014, 49, 801–811. [Google Scholar] [CrossRef]

- Chen, Z.; Luo, J.; Lin, K.; Wu, J.; Zhu, T.; Xiang, X.; Meng, J. An Energy-Efficient ECG Processor with Weak-Strong Hybrid Classifier for Arrhythmia Detection. IEEE Trans. Circuits Syst. II Exp. Briefs 2018, 65, 948–952. [Google Scholar] [CrossRef]

- Yin, Y.; Abubakar, S.M.; Tan, S.; Shi, J.; Yang, P.; Yang, W.; Jiang, H.; Wang, Z.; Jia, W.; Seng-Pan, U. A 2.63 μW ECG Processor With Adaptive Arrhythmia Detection and Data Compression for Implantable Cardiac Monitoring Device. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 777–790. [Google Scholar] [CrossRef] [PubMed]

- Zhao, Y.; Shang, Z.; Lian, Y. A 13.34 μW Event-Driven Patient-Specific ANN Cardiac Arrhythmia Classifier for Wearable ECG Sensors. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 186–197. [Google Scholar] [CrossRef] [PubMed]

- Janveja, M.; Parmar, R.; Tantuway, M.; Trivedi, G. A DNN-Based Low Power ECG Co-Processor Architecture to Classify Cardiac Arrhythmia for Wearable Devices. IEEE Trans. Circuits Syst. II Exp. Briefs 2022, 69, 2281–2285. [Google Scholar] [CrossRef]

- Liu, J.; Xiao, J.; Fan, J.; Liu, Q.; Zhu, Z.; Li, S.; Zhang, Z.; Yang, S.; Shan, W.; Lin, S.; et al. An Energy-Efficient Cardiac Arrhythmia Classification Processor using Heartbeat Difference based Classification and Event-Driven Neural Network Computation with Adaptive Wake-Up. In Proceedings of the 2022 IEEE Custom Integrated Circuits Conference (CICC), Newport Beach, CA, USA, 24–27 April 2022; pp. 1–2. [Google Scholar]

- Chuang, Y.-C.; Chen, Y.-T.; Li, H.-T.; Wu, A.-Y.A. An Arbitrarily Reconfigurable Extreme Learning Machine Inference Engine for Robust ECG Anomaly Detection. IEEE Open J. Circuits Syst. 2021, 2, 196–209. [Google Scholar] [CrossRef]

- Liu, J.; Zhu, Z.; Zhou, Y.; Wang, N.; Dai, G.; Liu, Q.; Xiao, J.; Xie, Y.; Zhong, Z.; Liu, H.; et al. BioAIP: A Reconfigurable Biomedical AI Processor with Adaptive Learning for Versatile Intelligent Health Monitoring. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 62–64. [Google Scholar]

- Lu, J.; Liu, D.; Liu, Z.; Cheng, X.; Wei, L.; Zhang, C.; Zou, X.; Liu, B. Efficient Hardware Architecture of Convolutional Neural Network for ECG Classification in Wearable Healthcare Device. IEEE Trans. Circuits Syst. I Reg. Pap. 2021, 68, 2976–2985. [Google Scholar] [CrossRef]

- Rijn, A.C.M.V.; Peper, A.; Grimbergen, C.A. High-quality recording of bioelectric events. Part 1. Interference reduction, theory and practice. Med. Biol. Eng. Comput. 1990, 28, 389–397. [Google Scholar] [CrossRef] [PubMed]

- Goldberger, A. PhysioBank, PhysioToolkit, and PhysioNet: Components of a new research resource for complex physiologic signals. Circulation 2000, 101, e215–e220. [Google Scholar] [CrossRef] [PubMed]

- Wang, H.-M.; Lai, Y.-L.; Hou, M.C.; Lin, S.-H.; Yen, B.S.; Huang, Y.-C.; Chou, L.-C.; Hsu, S.-Y.; Huang, S.-C.; Jan, M.-Y. A ±6 ms-accuracy, 0.68 mm2 and 2.21 μW QRS detection ASIC. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems (ISCAS), Paris, France, 30 May–2 June 2010; pp. 1372–1375. [Google Scholar]

- Deepu, C.J.; Xu, X.Y.; Wong, D.L.T.; Heng, C.H.; Lian, Y. A 2.3 μW ECG-On-Chip for Wireless Wearable Sensors. IEEE Trans. Circuits Syst. II Exp. Briefs 2018, 65, 1385–1389. [Google Scholar]

- Zou, Y.; Han, J.; Xuan, S.; Huang, S.; Weng, X.; Fang, D.; Zeng, X. An Energy-Efficient Design for ECG Recording and R-Peak Detection Based on Wavelet Transform. IEEE Trans. Circuits Syst. II Exp. Briefs 2015, 62, 119–123. [Google Scholar] [CrossRef]

- Yin, Y.; Abubakar, S.M.; Tan, S.; Jiang, H.; Wang, Z.; Seng-Pan, U.; Jia, W. A 17.7-pJ/Cycle ECG Processor for Arrhythmia Detection with High Immunity to Power Line Interference and Baseline Drift. In Proceedings of the 2020 IEEE Asian Solid-State Circuits Conference (A-SSCC), Hiroshima, Japan, 9–11 November 2020; pp. 1–4. [Google Scholar]

- Shen, T.W.; Tompkins, W.J.; Hu, Y.H. Implementation of a one-lead ECG human identification system on a normal population. J. Eng. Comput. Innov. 2011, 2, 12–21. [Google Scholar]

- Analog Devices: MAX30003. Available online: https://www.analog.com/cn/products/MAX30003.html#product-overview (accessed on 12 August 2023).

| Reference | [15] | [16] | [17] | [18] | This Design |

|---|---|---|---|---|---|

| Method | derivative and squaring | morpho- logical filter | wavelet transform | slope comparison | derivative and MA 2 comparison |

| Sen (%) | 95.65 | 99.82 | 99.72 | 96.9 | 98.62 |

| P+ (%) | 99.36 | 99.71 | 99.49 | 99.1 | 98.74 |

| Memory Used (kB 1) | N.A. 3 | 1 | 1 | N.A. | 0.25 |

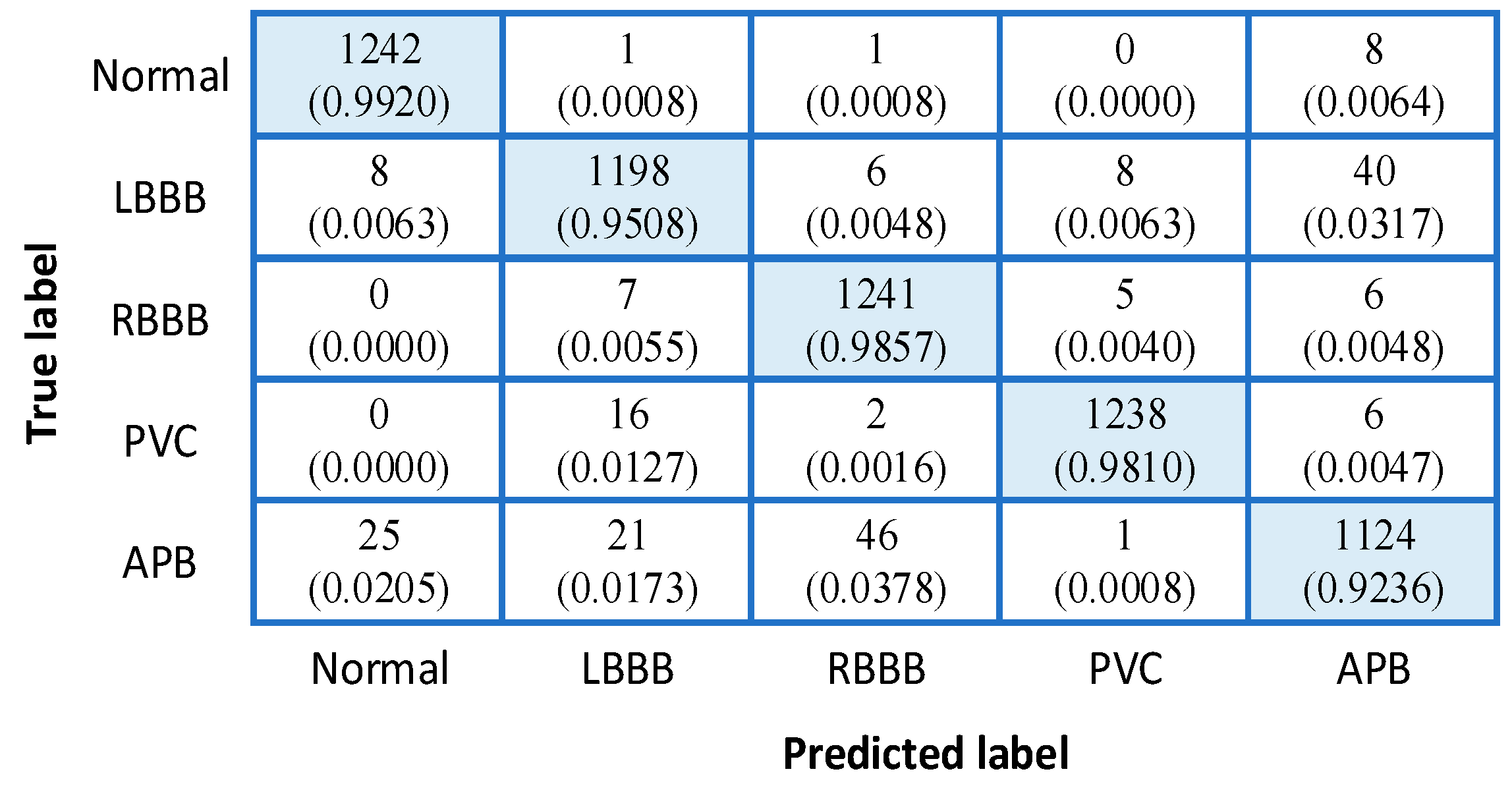

| Reference | NOR | LBBB | RBBB | PVC | APB | Overall |

|---|---|---|---|---|---|---|

| Sensitivity (%) | 99.20 | 95.08 | 98.57 | 98.10 | 92.36 | 96.66 |

| PPV (%) | 97.41 | 96.38 | 95.76 | 98.88 | 94.93 | 96.67 |

| Reference | [4] | [7] | [8] | [10] | [11] | This Work |

|---|---|---|---|---|---|---|

| Process (nm) | 90 | 180 | 180 | 40 | 65 | 55 |

| Frequency (Hz) | 40 M | 10 k–25 M | 12 k | 70 M | 5 M | 100 k |

| VDD (V) | 0.5–1.0 | 1.8 | 1.98 | 0.6 | 1 | 1.2 |

| Power (μW) | 20.1 | 13.34 | 8.75 | 2940 | 46.8 | 12.88 |

| Area (mm2) | 4.99 | 0.925 | 1.32 | 0.2123 | 1.74 | 0.33 |

| Algorithm Model | SVM | ANN | DNN | ELM | ANN | ANN |

| Energy Eff. (nJ/Classifi.) | N.A. | 3210 | 2080 | 212 | 2250 | 234.4 |

| Memory (kB) | 20 | 64 | N.A. | 52 | 73 | 4.5 |

| Accuracy (%) | 95.8 | 99.32 | 91.6 | 92 | 99.3 | 96.69 |

| Number of classes | 2 | 5 | 5 | 2 | 2 | 5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, C.; Chang, J.; Guan, Y.; Li, Q.; Wang, X.; Zhang, X. A Low-Power ECG Processor ASIC Based on an Artificial Neural Network for Arrhythmia Detection. Appl. Sci. 2023, 13, 9591. https://doi.org/10.3390/app13179591

Zhang C, Chang J, Guan Y, Li Q, Wang X, Zhang X. A Low-Power ECG Processor ASIC Based on an Artificial Neural Network for Arrhythmia Detection. Applied Sciences. 2023; 13(17):9591. https://doi.org/10.3390/app13179591

Chicago/Turabian StyleZhang, Chen, Junfeng Chang, Yujiang Guan, Qiuping Li, Xin’an Wang, and Xing Zhang. 2023. "A Low-Power ECG Processor ASIC Based on an Artificial Neural Network for Arrhythmia Detection" Applied Sciences 13, no. 17: 9591. https://doi.org/10.3390/app13179591

APA StyleZhang, C., Chang, J., Guan, Y., Li, Q., Wang, X., & Zhang, X. (2023). A Low-Power ECG Processor ASIC Based on an Artificial Neural Network for Arrhythmia Detection. Applied Sciences, 13(17), 9591. https://doi.org/10.3390/app13179591