A High Performance 0.3 V Standard-Cell-Based OTA Suitable for Automatic Layout Flow

Abstract

:1. Introduction

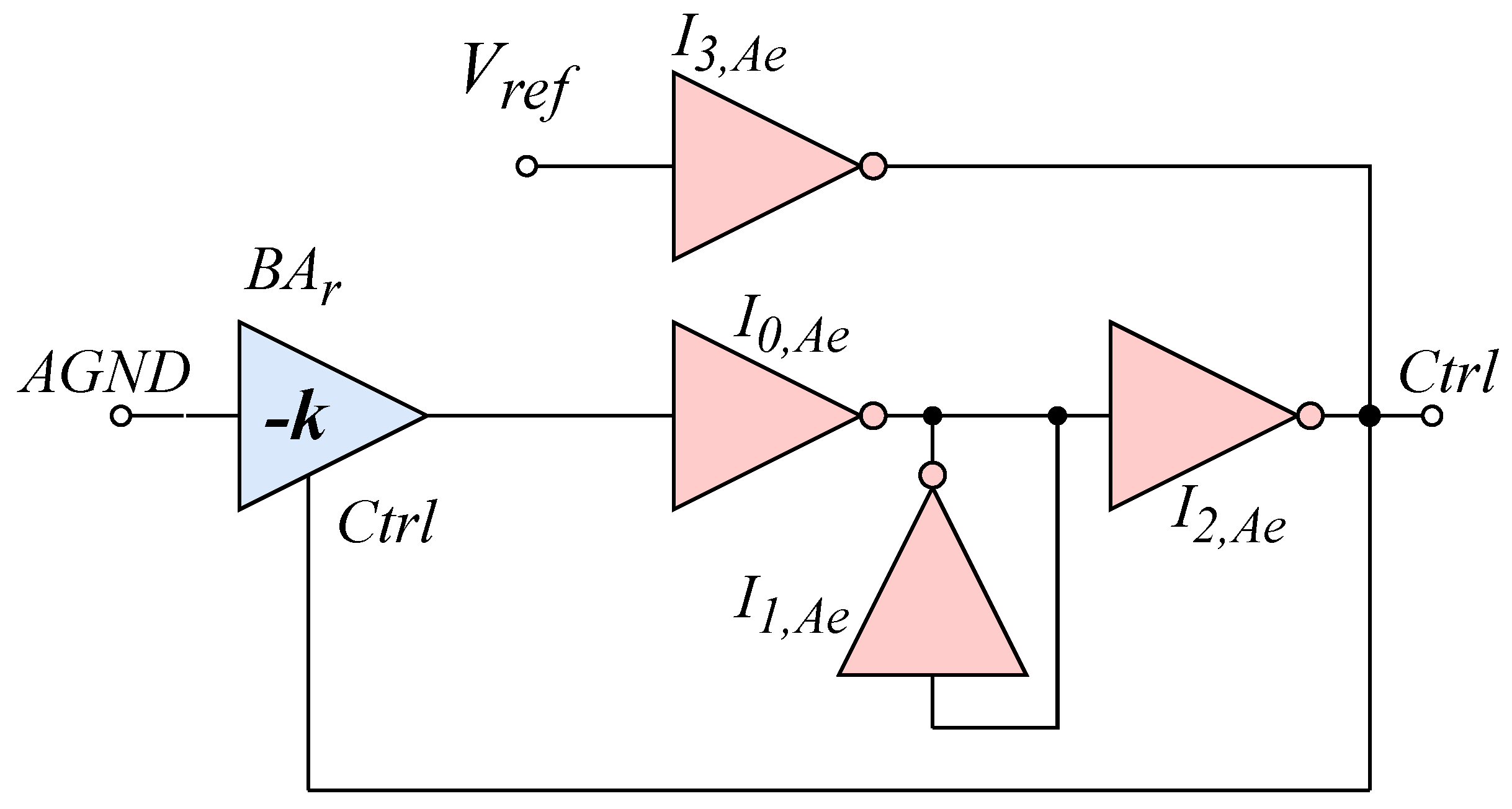

2. Replica Bias Approach to Control the Static Output Voltage of Inverters

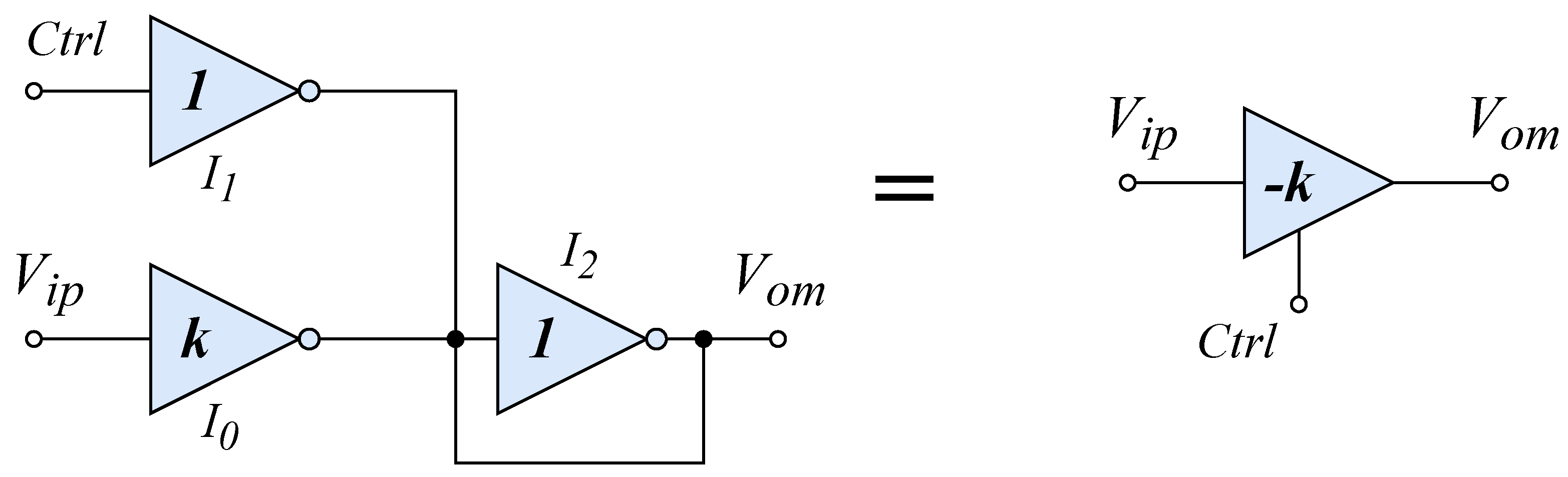

3. A Standard-Cell-Based Amplifier Cell with Stable Voltage Gain and Well-Defined DC Output Voltage

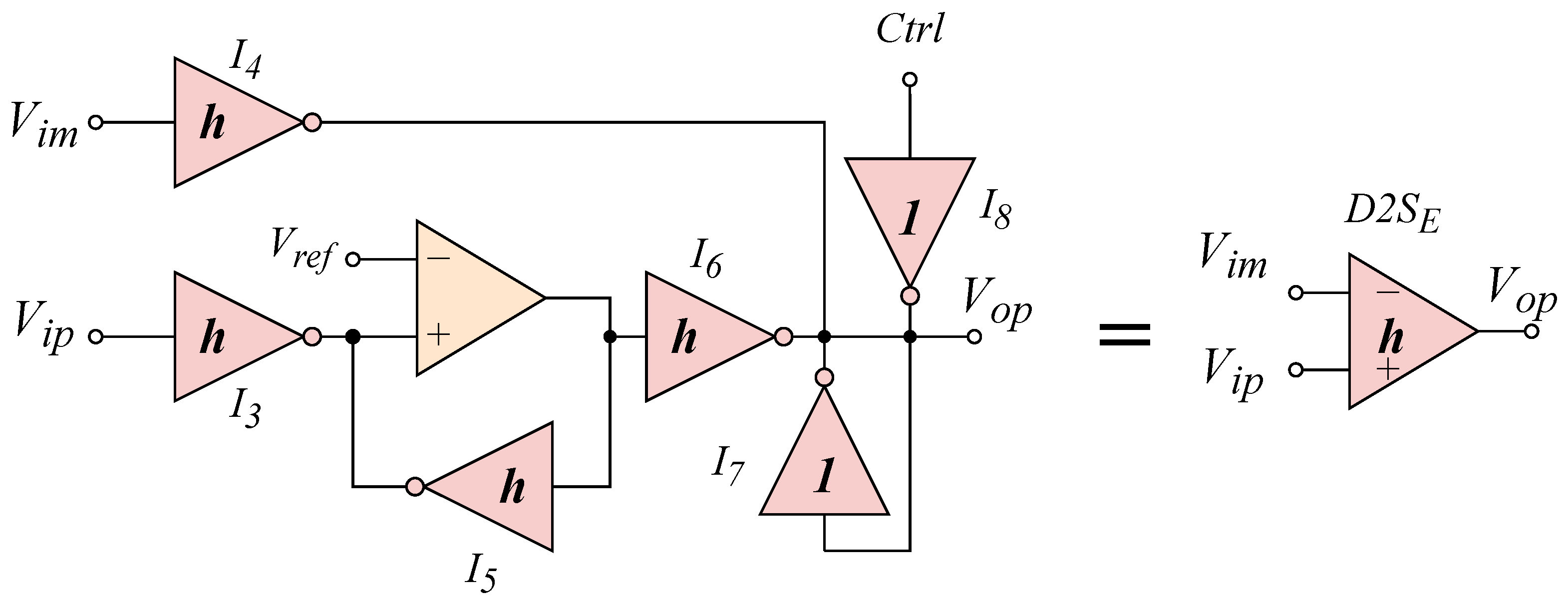

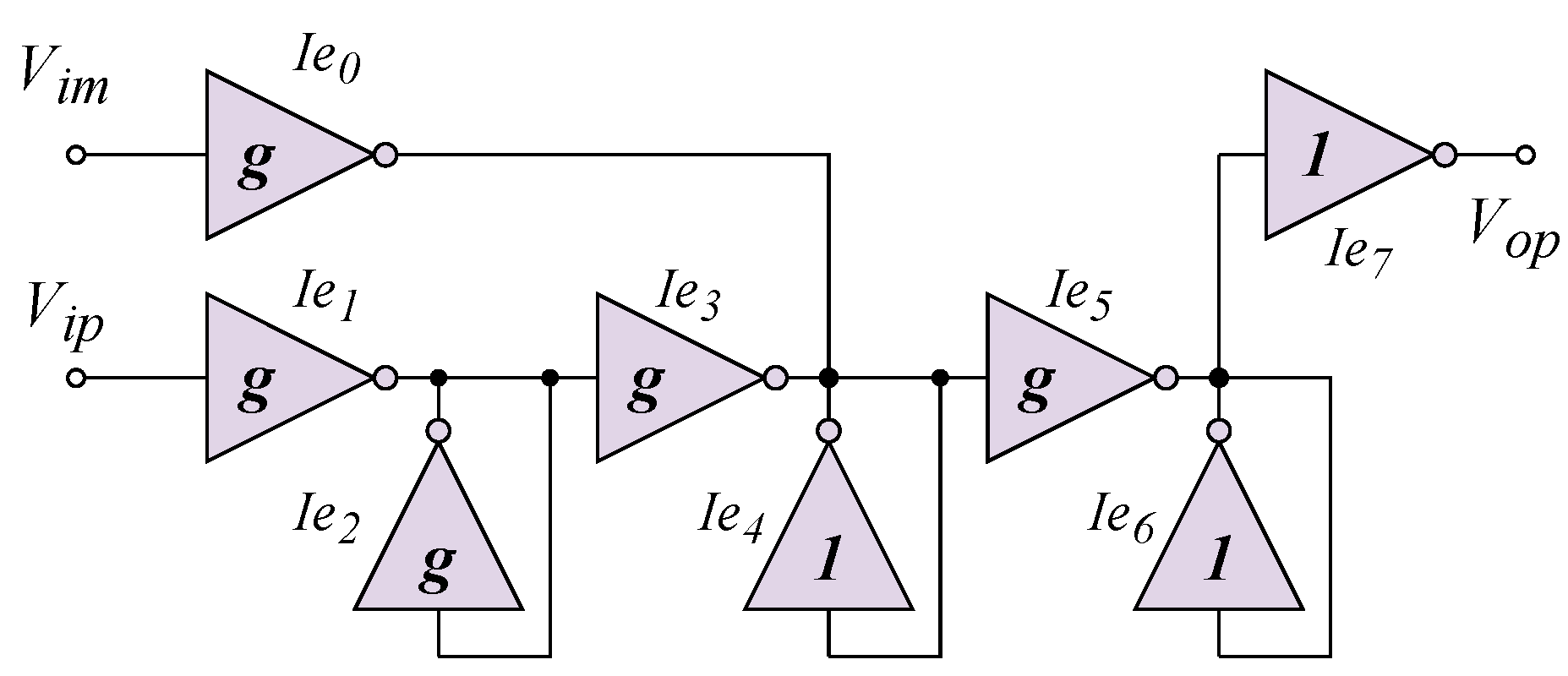

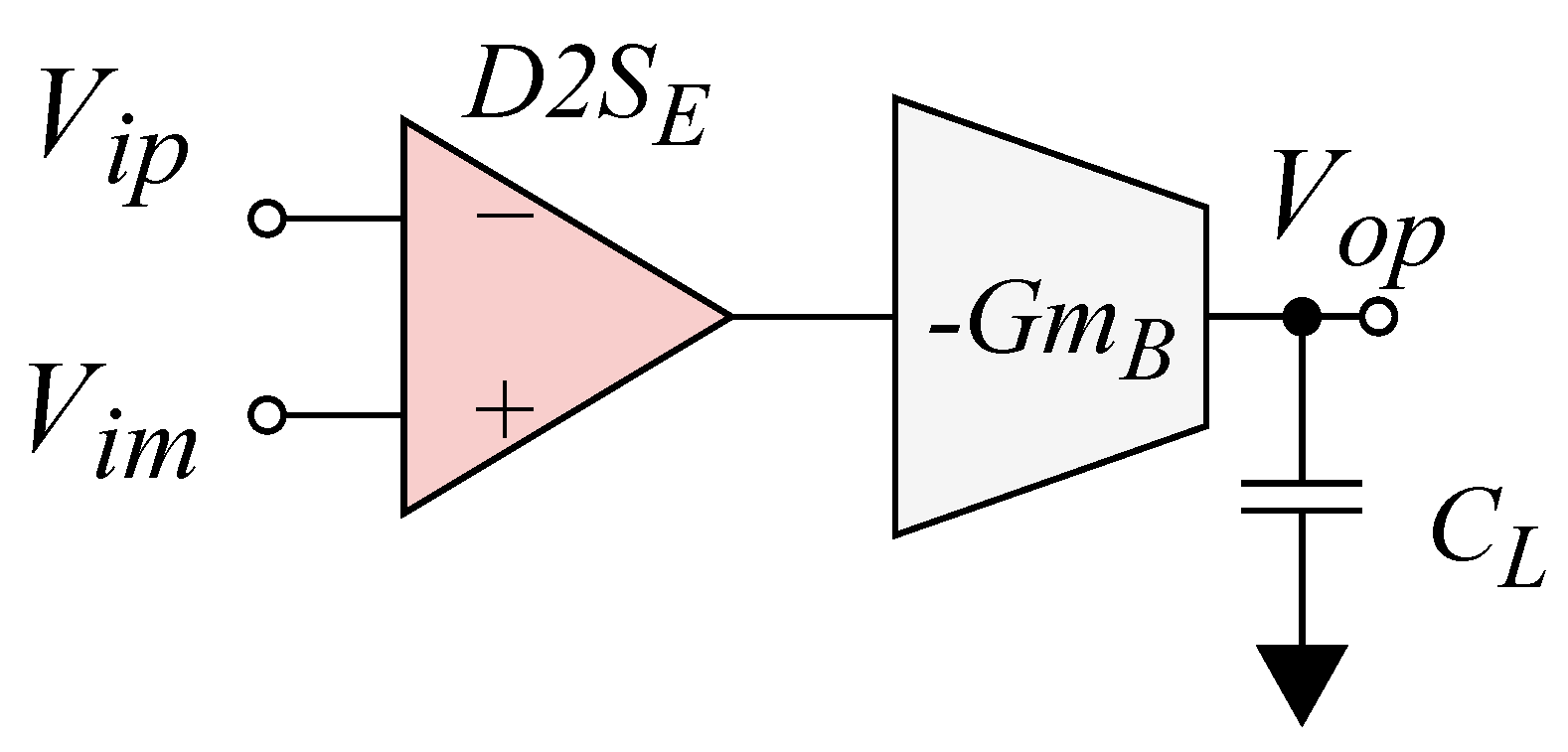

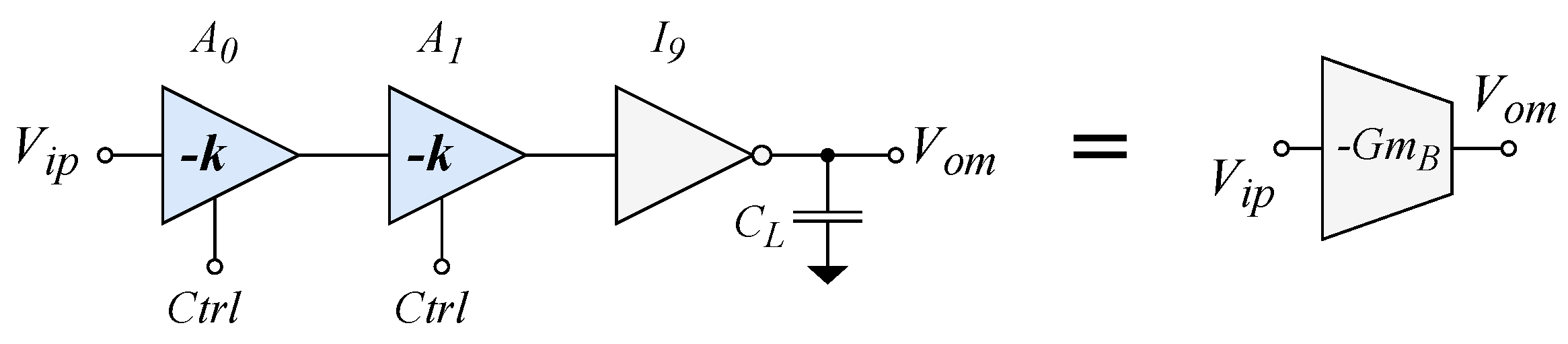

4. The Proposed Inverter-Based D2S Converter with Enhanced Common Mode Rejection

5. Proposed Standard-Cell-Based ULV OTA Architecture

5.1. Analytical Model and Design Guidelines

6. Design of the Standard-Cell-Based ULV OTA

6.1. Simulation of the Standard-Cell-Based Basic Voltage Amplifier in ULV Conditions

6.2. Design Flow

6.3. Automatic Layout Flow within the Cadence Innovus Tool

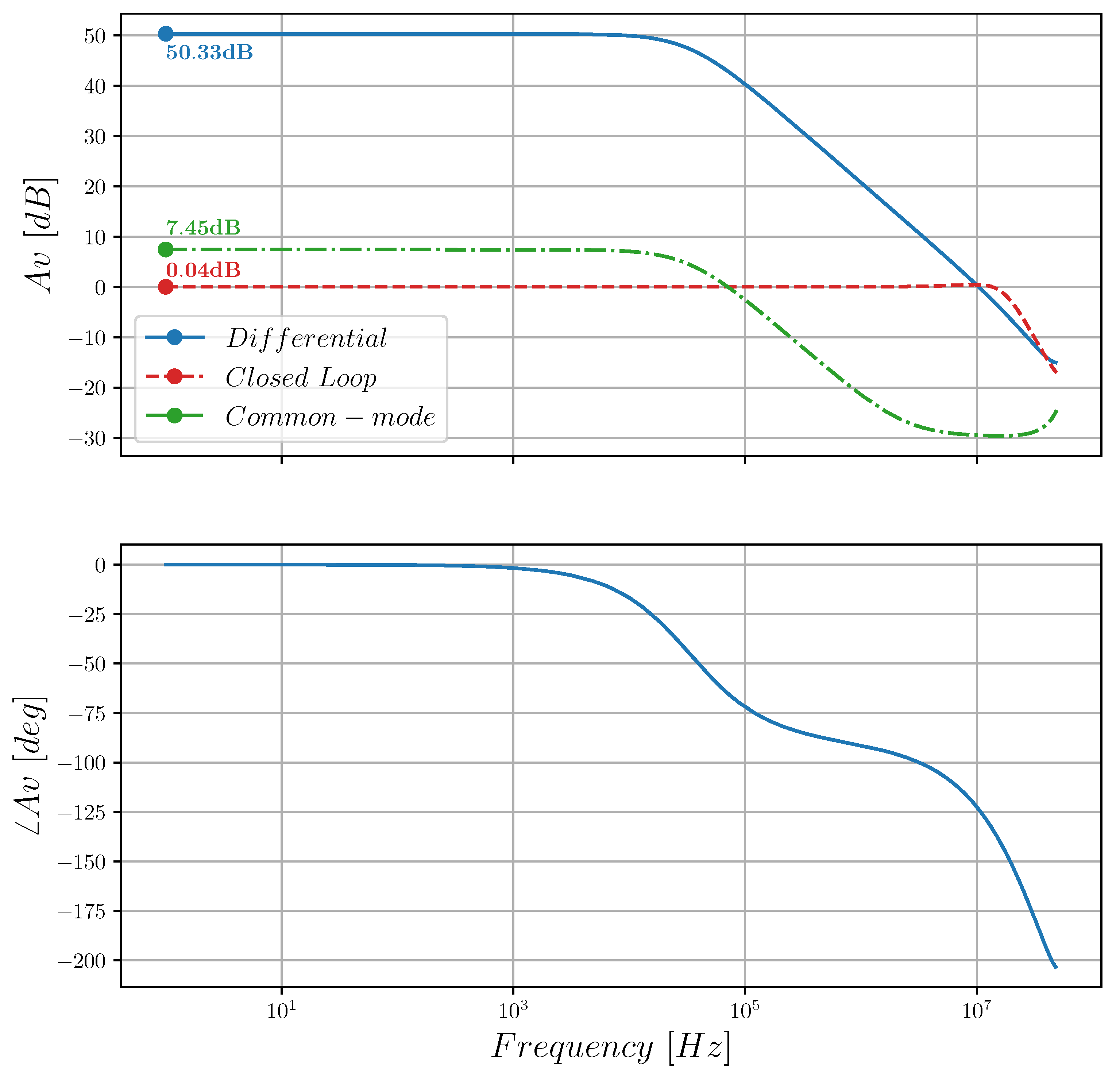

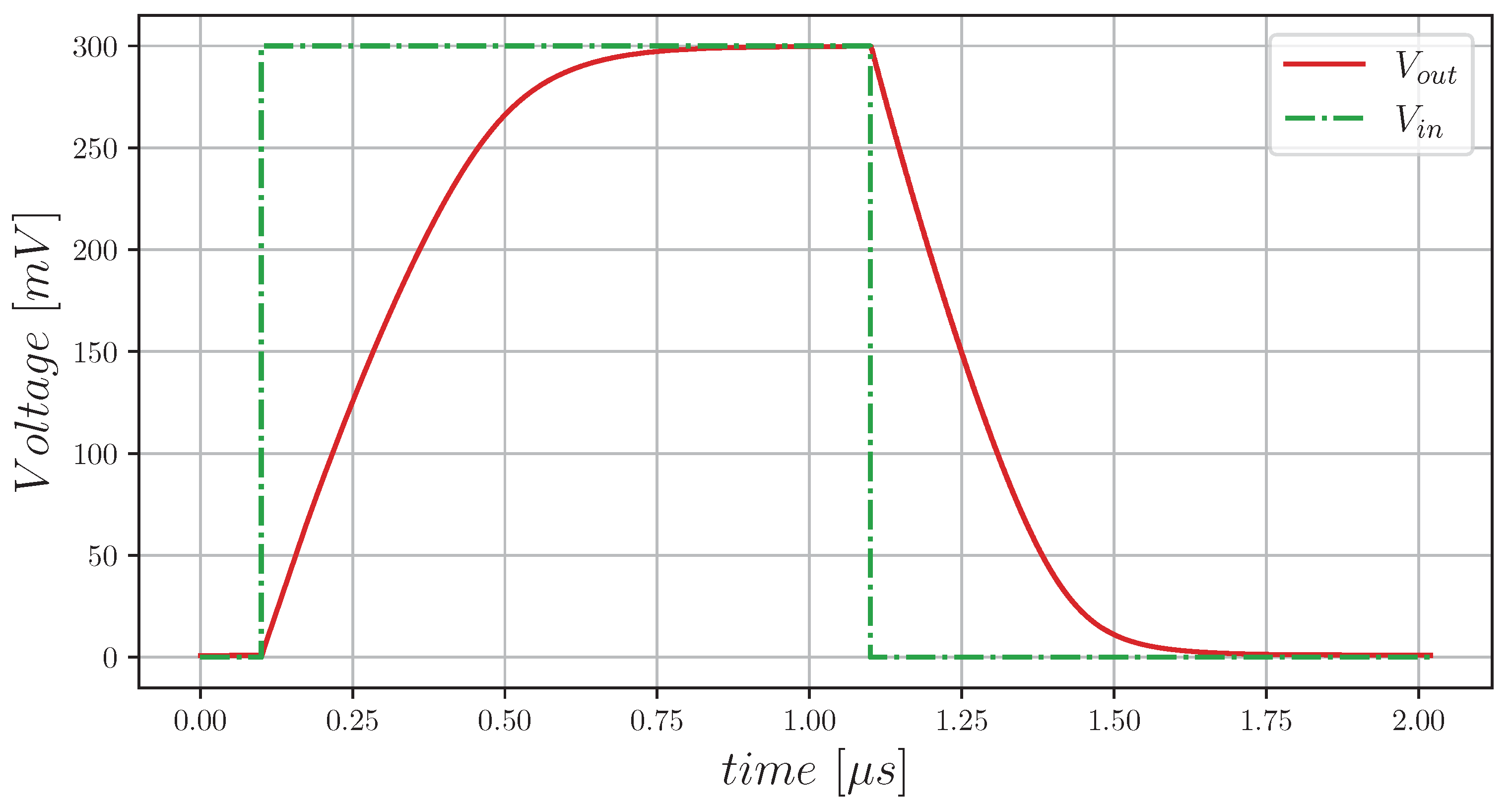

7. Simulations of the Proposed Standard-Cell-Based ULV OTA

Simulations in the Different PVT Conditions

8. Comparison

9. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| ADC | Analog-to-Digital Converter |

| BA | Basic Amplifier |

| BD | Body-Driven |

| D2S | Differential-to-Single-Ended |

| DIGOTA | Fully-Digital Operational Transconductance Amplifier |

| CMRR | Common Mode Rejection Ratio |

| EDA | Electronic Design Automation |

| FOM | Figure Of Merit |

| GBW | Gain-Bandwidth Product |

| IC | Integrated Circuit |

| ICMR | Input Common Mode Range |

| IoT | Internet-of-Things |

| OTA | Operational Transconductance Amplifier |

| PVT | Process, Supply Voltage and Temperature |

| THD | Total Harmonic Distortion |

| SR | Slew Rate |

| ULV | Ultra-Low Voltage |

References

- Alioto, M.; Shahghasemi, M. The Internet of Things on its edge: Trends toward its tipping point. IEEE Consum. Electron. Mag. 2018, 7, 77–87. [Google Scholar] [CrossRef]

- Sobin, C.C. A survey on architecture, protocols and challenges in IoT. Wirel. Pers. Commun. 2020, 112, 1383–1429. [Google Scholar] [CrossRef]

- Chi, Q.; Yan, H.; Zhang, C.; Pang, Z.; Xu, L.D. A reconfigurable smart sensor interface for industrial WSN in IoT environment. IEEE Trans. Ind. Inf. 2014, 10, 1417–1425. [Google Scholar] [CrossRef]

- Abella, C.S.; Bonina, S.; Cucuccio, A.; D’Angelo, S.; Giustolisi, G.; Grasso, A.D.; Imbruglia, A.; Mauro, G.S.; Nastasi, G.A.M.; Palumbo, G.; et al. Autonomous energy-efficient wireless sensor network platform for home/office automation. IEEE Sens. J. 2019, 19, 3501–3512. [Google Scholar] [CrossRef]

- Alioto, M. From less batteries to battery-less alert systems with wide power adaptation down to nWs—Toward a smarter, greener world. IEEE Des. Test 2021, 38, 90–133. [Google Scholar] [CrossRef]

- Carrara, S. Body dust: Well beyond wearable and implantable sensors. IEEE Sens. J. 2021, 21, 12398–12406. [Google Scholar] [CrossRef]

- Grossi, M. Energy harvesting strategies for wireless sensor networks and mobile devices: A review. Electronics 2021, 10, 661. [Google Scholar] [CrossRef]

- Ballo, A.; Grasso, A.D.; Palumbo, G. A Review of Charge Pump Topologies for the Power Management of IoT Nodes. Electronics 2019, 8, 480. [Google Scholar] [CrossRef]

- Ballo, A.; Bottaro, M.; Grasso, A.D. A Review of Power Management Integrated Circuits for Ultrasound-Based Energy Harvesting in Implantable Medical Devices. Appl. Sci. 2021, 11, 2487. [Google Scholar] [CrossRef]

- Centurelli, F.; Della Sala, R.; Monsurró, P.; Tommasino, P.; Trifiletti, A. An ultra-low-voltage class-AB OTA exploiting local CMFB and body-to-gate interface. AEU Int. J. Electron. Commun. 2022, 145, 154081. [Google Scholar] [CrossRef]

- Centurelli, F.; Della Sala, R.; Monsurró, P.; Scotti, G.; Trifiletti, A. A tree-based architecture for high-performance ultra-low-voltage amplifiers. J. Low Power Electron. Appl. 2022, 12, 12. [Google Scholar] [CrossRef]

- Kulej, T.; Khateb, F. A compact 0.3-V class AB bulk-driven OTA. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2020, 28, 224–232. [Google Scholar] [CrossRef]

- Kulej, T.; Khateb, F. A 0.3-V 98-dB rail-to-rail OTA in 0.18 μm CMOS. IEEE Access 2020, 8, 27459–27467. [Google Scholar] [CrossRef]

- Kulej, T.; Khateb, F.; Arbet, D.; Stopjakova, V. A 0.3-V high linear rail-to-rail bulk-driven OTA in 0.13 μm CMOS. IEEE Trans. Circuits Syst. II 2022, 69, 2046–2050. [Google Scholar] [CrossRef]

- Rodovalho, L.H.; Aiello, O.; Rodrigues, C.R. Ultra-low-voltage inverter-based operational transconductance amplifiers with voltage gain enhancement by improved composite transistors. Electronics 2020, 9, 1410. [Google Scholar] [CrossRef]

- Lv, L.; Zhou, X.; Qiao, Z.; Li, Q. Inverter-based subthreshold amplifier techniques and their application in 0.3-V ΔΣ-modulators. IEEE J. Solid-State Circuits 2019, 54, 1436–1445. [Google Scholar] [CrossRef]

- Rodovalho, L.H.; Ramos Rodrigues, C.; Aiello, O. Self-biased and supply-voltage scalable inverter-based operational transconductance amplifier with improved composite transistors. Electronics 2021, 10, 935. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Monsurrò, P.; Scotti, G.; Trifiletti, A. A body-driven rail-to-rail 0.3 V operational transconductance amplifier exploiting current gain stages. Int. J. Circuit Theory Appl. 2022. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Scotti, G.; Tommasino, P.; Trifiletti, A. A Differential-to-Single-Ended Converter Based on Enhanced Body-Driven Current Mirrors Targeting Ultra-Low-Voltage OTAs. Electronics 2022, 11, 3838. [Google Scholar] [CrossRef]

- Deng, W.; Yang, D.; Ueno, T.; Siriburanon, T.; Kondo, S.; Okada, K.; Matsuzawa, A. A fully synthesizable all-digital PLL with interpolative phase coupled oscillator, current-output DAC, and fine-resolution digital varactor using gated edge injection technique. IEEE J. Solid-State Circuits 2015, 50, 68–80. [Google Scholar] [CrossRef]

- Liu, J.; Maghari, N. A fully-synthesizable 0.6V digital LDO with dual-loop control using digital standard cells. In Proceedings of the 2016 14th IEEE International New Circuits and Systems Conference (NEWCAS), Vancouver, BC, Canada, 26–29 June 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Liu, J.; Park, B.; Guzman, M.; Fahmy, A.; Kim, T.; Maghari, N. A fully synthesized 77-dB SFDR reprogrammable SRMC filter using digital standard cells. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2018, 26, 1126–1138. [Google Scholar] [CrossRef]

- Seo, M.J.; Roh, Y.J.; Chang, D.J.; Kim, W.; Kim, Y.D.; Ryu, S.T. A Reusable Code-Based SAR ADC Design With CDAC Compiler and Synthesizable Analog Building Blocks. IEEE Trans. Circuits Syst. Express Briefs 2018, 65, 1904–1908. [Google Scholar] [CrossRef]

- Liu, B.; Zhang, Y.; Qiu, J.; Deng, W.; Xu, Z.; Zhang, H.; Pang, J.; Wang, Y.; Wu, R.; Someya, T.; et al. An HDL-described Fully-synthesizable Sub-GHz IoT Transceiver with Ring Oscillator based Frequency Synthesizer and Digital Background EVM Calibration. In Proceedings of the 2019 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Park, J.E.; Hwang, Y.H.; Jeong, D.K. A 0.5-V fully synthesizable SAR ADC for on-chip distributed waveform monitors. IEEE Access 2019, 7, 63686–63697. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Sharma, A.; Alioto, M. Fully-Synthesizable Current-Input ADCs for Ultra-Low Area and Minimal Design Effort. In Proceedings of the 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Genoa, Italy, 27–29 November 2019; pp. 27–29. [Google Scholar]

- Ojima, N.; Xu, Z.; Iizuka, T. A 0.0053-mm2 6-bit fully-standard-cell-based synthesizable SAR ADC in 65 nm CMOS. In Proceedings of the 2019 17th IEEE International New Circuits and Systems Conference (NEWCAS), Munich, Germany, 23–26 June 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Alioto, M. Fully synthesizable low-area analogue-to-digital converters with minimal design effort based on the dyadic digital pulse modulation. IEEE Access 2020, 8, 70890–70899. [Google Scholar] [CrossRef]

- Liu, Y.; Zhang, B.; Cheng, X.; Han, J.; Zeng, X. A 0.9V all digital synthesizable OPAMP with boosted gain and widened common mode input range. In Proceedings of the 2020 IEEE 15th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Kunming, China, 3–6 November 2020; pp. 1–3. [Google Scholar] [CrossRef]

- Liu, C.; Zhao, C.; Shi, C.J.R. A Fully-Synthesizable Fast-Response Digital LDO Using Automatic Offset Control and Reuse. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021; pp. 1–5. [Google Scholar]

- Park, J.; Kim, J.; Kim, K.; Yang, J.H.; Choi, M.; Shin, J. A 0.65V 1316μm2 Fully Synthesizable Digital Temperature Sensor Using Wire Metal Achieving O.16nJ.%2-Accuracy FoM in 5nm FinFET CMOS. In Proceedings of the 2022 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; Volume 65, pp. 220–222. [Google Scholar]

- Correia, A.; Tavares, V.G.; Barquinha, P.; Goes, J. All-Standard-Cell-Based Analog-to-Digital Architectures Well-Suited for Internet of Things Applications. J. Low Power Electron. Appl. 2022, 12, 64. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Scotti, G. A novel differential to single-ended converter for ultra-low-voltage inverter-based OTAs. IEEE Access 2022, 10, 98179–98190. [Google Scholar] [CrossRef]

- Toledo, P.; Rubino, R.; Musolino, F.; Crovetti, P. Re-thinking analog integrated circuits in digital terms: A new design concept for the IoT era. IEEE Trans. Circuits Syst. II 2021, 68, 816–822. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.S.; Alioto, M. Fully synthesizable low-area digital-to-analog converter with graceful degradation and dynamic power-resolution scaling. IEEE Trans. Circ. Syst. I 2019, 66, 2865–2875. [Google Scholar] [CrossRef]

- Sood, L.; Agarwal, A. A CMOS standard-cell based fully-synthesizable low-dropout regulator for ultra-low power applications. AEU Int. J. Electron. Commun. 2021, 141, 153958. [Google Scholar] [CrossRef]

- Drost, B.; Talegaonkar, M.; Hanumolu, P.K. Analog filter design using ring oscillator integrators. IEEE J. Solid-State Circuits 2012, 47, 3120–3129. [Google Scholar] [CrossRef]

- Kalani, S.; Haque, T.; Gupta, R.; Kinget, P.R. Benefits of using VCO-OTAs to construct TIAs in wideband current-mode receivers over inverter-based OTAs. IEEE Trans. Circ. Syst. I 2019, 66, 1681–1691. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.; Aiello, O.; Alioto, M. Design of digital OTAs with operation down to 0.3 V and nW power for direct harvesting. IEEE Trans. Circ. Syst. I 2021, 68, 3693–3706. [Google Scholar] [CrossRef]

- Palumbo, G.; Scotti, G. A novel standard-cell-based implementation of the digital OTA suitable for automatic place and route. J. Low Power Electron. Appl. 2021, 11, 42. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.S.; Klimach, H.D.; Musolino, F.; Bampi, S. Low-voltage, low-area, nW-power CMOS digital-based biosignal amplifier. IEEE Access 2022, 10, 44106–44115. [Google Scholar] [CrossRef]

- Nauta, B. A CMOS transconductance-C filter technique for very high frequencies. IEEE J. Solid-State Circuits 1992, 27, 142–153. [Google Scholar] [CrossRef]

- Barthélemy, H.; Meillère, S.; Gaubert, J.; Dehaese, N.; Bourdel, S. OTA based on CMOS inverters and application in the design of tunable bandpass filter. Analog Integr. Circ. Sig. Process. 2008, 57, 169–178. [Google Scholar] [CrossRef]

- Bae, W. CMOS inverter as analog circuit: An overview. J. Low Power Electron. Appl. 2019, 9, 26. [Google Scholar] [CrossRef]

- Vlassis, S. 0.5 V CMOS inverter-based tunable transconductor. Analog. Integr. Circuits Signal Process. 2012, 72, 289–292. [Google Scholar] [CrossRef]

- Braga, R.A.S.; Ferreira, L.H.C.; Coletta, G.D.; Dutra, O.O. A 0.25-V calibration-less inverter-based OTA for low-frequency Gm-C applications. Microelectron. J. 2019, 83, 62–72. [Google Scholar] [CrossRef]

- Manfredini, G.; Catania, A.; Benvenuti, L.; Cicalini, M.; Piotto, M.; Bruschi, P. Ultra-low-voltage inverter-based amplifier with novel common-mode stabilization loop. Electronics 2020, 9, 1019. [Google Scholar] [CrossRef]

- Póvoa, R.; Canelas, A.; Martins, R.; Horta, N.; Lourenço, N.; Goes, J. A new family of CMOS inverter-based OTAs for biomedical and healthcare applications. Integration 2020, 71, 38–48. [Google Scholar] [CrossRef]

- Rodovalho, L.H. Push–pull based operational transconductor amplifier topologies for ultra low voltage supplies. Analog Integr. Circ. Sig. Process. 2021, 106, 111–124. [Google Scholar] [CrossRef]

- Lee, S.; Park, S.; Kim, Y.; Kim, Y.; Lee, J.; Lee, J.; Chae, Y. A 0.6-V 86.5-dB DR 40-kHz BW inverter-based continuous-time delta–sigma modulator with PVT-robust body-biasing. IEEE Solid-State Circuits Lett. 2021, 4, 178–181. [Google Scholar] [CrossRef]

- Centurelli, F.; Della Sala, R.; Scotti, G. A standard-cell-based CMFB for fully synthesizable OTAs. J. Low Power Electron. Appl. 2022, 12, 27. [Google Scholar] [CrossRef]

- Della Sala, R.; Centurelli, F.; Scotti, G. Enabling ULV fully synthesizable analog circuits: The BA cell, a standard-cell-based building block for analog design. IEEE Trans. Circuits Syst. II 2022, 69, 4689–4693. [Google Scholar] [CrossRef]

- Nicholson, A.P.; Iberzanov, A.; Jenkins, J.; Hamilton, T.J.; Lehmann, T. A statistical design approach for a digitally programmable mismatch-tolerant high-speed Nauta structure differential OTA in 65-nm CMOS. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2016, 24, 2899–2910. [Google Scholar] [CrossRef]

- Ismail, A.; Mostafa, I. A process-tolerant, low-voltage, inverter-based OTA for continuous-time Σ–Δ ADC. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2016, 24, 2911–2917. [Google Scholar] [CrossRef]

- De Aguirre, P.C.C.; Susin, A.A. PVT compensated inverter-based OTA for low-voltage CT sigma-delta modulators. Electron. Lett. 2018, 54, 1264–1266. [Google Scholar] [CrossRef]

- Baltolu, A.; Albinet, X.; Chalet, F.; Dallet, D.; Begueret, J.B. A robust inverter-based amplifier versus PVT for discrete-time integrators. Int. J. Circuit Theory Appl. 2018, 46, 2160–2169. [Google Scholar] [CrossRef]

- Pradeep, R.; Siddharth, R.K.; Nithin Kumar, Y.B.; Vasantha, M.H. Process corner calibration for standard cell based flash ADC. In Proceedings of the 2019 IEEE International Symposium on Smart Electronic Systems (iSES) (Formerly iNiS), Rourkela, India, 16–18 December 2019; pp. 195–200. [Google Scholar] [CrossRef]

- Faraji Baghtash, H. Bias-stabilized inverter-amplifier: An inspiring solution for low-voltage and low-power applications. Analog Integr. Circ. Sig. Process. 2020, 105, 243–248. [Google Scholar] [CrossRef]

- Centurelli, F.; Giustolisi, G.; Pennisi, S.; Scotti, G. A biasing approach to design ultra-low-power standard-cell-based analog building blocks for nanometer SoCs. IEEE Access 2022, 10, 25892–25900. [Google Scholar] [CrossRef]

- Siddiqi, A.; Jain, N.; Rashed, M. Back-bias generator for post-fabrication threshold voltage tuning applications in 22nm FD-SOI process. In Proceedings of the 2018 19th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 13–14 March 2018; pp. 268–273. [Google Scholar] [CrossRef]

- Höppner, S.; Eisenreich, H.; Walter, D.; Scharfe, A.; Oefelein, A.; Schraut, F.; Schreiter, J.; Riedel, T.; Bauer, H.; Niebsch, R.; et al. Adaptive body bias aware implementation for ultra-low-voltage designs in 22FDX technology. IEEE Trans. Circuits Syst. II 2020, 67, 2159–2163. [Google Scholar] [CrossRef]

- Centurelli, F.; Della Sala, R.; Monsurró, P.; Scotti, G.; Trifiletti, A. A novel OTA architecture exploiting current gain stages to boost bandwidth and slew-rate. Electronics 2021, 10, 1638. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Toledo, P.; Alioto, M. Rail-to-rail dynamic voltage comparator scalable down to pW-range power and 0.15-V supply. IEEE Trans. Circuits Syst. II 2021, 68, 2675–2679. [Google Scholar] [CrossRef]

- Toledo, P.; Aiello, O.; Crovetti, P.S. A 300mV-supply standard-cell-based OTA with digital PWM offset calibration. In Proceedings of the 2019 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC), Helsinki, Finland, 29–30 October 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.; Klimach, H.; Bampi, S.; Aiello, O.; Alioto, M. A 300mV-supply, sub-nW-power digital-based operational transconductance amplifier. IEEE Trans. Circuits Syst. II 2021, 68, 3073–3077. [Google Scholar] [CrossRef]

- Kulej, T.; Khateb, F. Design and implementation of sub 0.5-V OTAs in 0.18-μm CMOS. Int. J. Circuit Theory Appl. 2018, 46, 1129–1143. [Google Scholar] [CrossRef]

| g | h | k | M | |

|---|---|---|---|---|

| Reference inverter | ×2 | ×20 | ×20 | ×20 |

| Value | 6 | 6 | 6 | 11 |

| Parameter | TT | FF | SS | FS | SF |

|---|---|---|---|---|---|

| [dB] | 50.33 | 46.38 | 53.72 | 50.58 | 49.4 |

| [dB] | 7.45 | 8.27 | 8.36 | 25.51 | 13.11 |

| [MHz] | 10.4 | 16.45 | 6.84 | 10.65 | 9.73 |

| [deg] | 56.33 | 63.6 | 49.46 | 56.38 | 59.39 |

| [W] | 12.09 | 26.21 | 6.23 | 13.44 | 12.41 |

| [mV] | −2.2 | −3.7 | −1.93 | −10.72 | 6.32 |

| [V/ms] | 631.4 | 1.044 k | 396.5 | 425.6 | 863.7 |

| [V/ms] | 811.3 | 1.407 k | 504.2 | 1.008 k | 569.6 |

| [%] | 0.24 | 0.28 | 0.26 | 0.99 | 0.95 |

| Parameter | Voltage Variations | Temperature Variations | ||

|---|---|---|---|---|

| T [C] | 27 | 27 | 0 | 80 |

| [mV] | 270 | 330 | 300 | 300 |

| [dB] | 49.2 | 51.19 | 51.38 | 48.14 |

| [dB] | 6.32 | 8.32 | 11.69 | 1.061 |

| [MHz] | 6.73 | 15.57 | 6.59 | 19.68 |

| [deg] | 54.13 | 54.13 | 54.31 | 60.32 |

| [W] | 19.6 | 19.6 | 6.59 | 30.45 |

| [mV] | −2.3 | −2.32 | −2.54 | −1.65 |

| [V/ms] | 367.2 | 1.04 k | 488.8 | 1.006 k |

| [V/ms] | 464.5 | 1.33 k | 614 | 1.178 k |

| [%] | 0.27 | 0.20 | 0.33 | 0.07 |

| Parameter | Typical | Mean | Std |

|---|---|---|---|

| [dB] | 50.33 | 50.24 | 1.12 |

| [dB] | 7.45 | 16 | 9.12 |

| [MHz] | 10.4 | 10.56 | 1.23 |

| [deg] | 56.33 | 55.92 | 3.54 |

| [W] | 12.09 | 12.47 | 0.2 |

| [mV] | −2.2 | −2.12 | 3.94 |

| [V/s] | 631.4 | 634 | 21.97 |

| [V/s] | 811.3 | 824.4 | 42.91 |

| [%] | 0.24 | 0.27 | 0.05 |

| Automatic Layout Flow Available | Automatic Layout Flow Not Available | ||||||

|---|---|---|---|---|---|---|---|

| This Work | [33] | [51] | [39] | [11] | [12] | [66] | |

| Year | 2023 | 2022 | 2022 | 2021 | 2022 | 2020 | 2018 |

| Technology [m] | 0.13 | 0.13 | 0.13 | 0.18 | 0.13 | 0.18 | 0.18 |

| [V] | 0.3 | 0.3 | 0.3 | 0.3 | 0.3 | 0.3 | 0.3 |

| [dB] | 50.33 | 34.97 | 28.3 | 30 | 52.92 | 64.7 | 65.8 |

| [pF] | 150 | 2 | 1.5 | 150 | 50 | 30 | 20 |

| [kHz] | 10.40 k | 12.69 k | 15.42 k | 0.25 | 35.16 | 2.96 | 2.96 |

| [deg] | 56.33 | 62.56 | 54 | 90 | 52.40 | 52 | 61 |

| [V/ms] | 631.4 | 4.54 k | 9.08 k | - | 18.61 | 1.9 | 6.44 |

| [V/ms] | 811.3 | 6.82 k | 9.08 k | - | 11.51 | 6.4 | 7.8 |

| [V/ms] | 721.35 | 5.68 k | 9.08 k | 0.085 | 15.06 | 4.15 | 7.12 |

| [%] | 0.24 | 3.38 | 3 | 2 | 0.67 | 1 | 1 |

| % of input swing | 80 | 90 | 80 | 90 | 90 | 85 | 93.33 |

| [dB] | 42.88 | 27.08 | 41.07 | 41 | 42.11 | 110 | 72 |

| [nW] | 12.09 k | 6.10 k | 4.41 k | 2.4 | 21.89 | 12.6 | 15.4 |

| STD-CELL | STD-CELL | STD-CELL | DIGITAL | BD | BD | BD | |

| 128.2 k | 4.16 k | 5.25 k | 15.89 k | 80.29 k | 7.05 k | 3.61 k | |

| 8.949 k | 1.86 k | 3.09 k | 5.40 k | 34.40 k | 9.88 k | 9.25 k | |

| 7.833 k | 1.49 k | 3.09 k | - | 26.30 k | 4.52 k | 8.36 k | |

| 598 | 217.85 | 164 | 982 | 5200 | 8500 | 8200 | |

| 214.38 | 19.10 | 32.01 | 16.18 | 15.44 | 0.83 | 0.4 | |

| 14.96 | 8.54 | 18.84 | 5.50 | 6.62 | 1.16 | 1.13 | |

| 13.10 | 6.84 | 18.84 | - | 5.06 | 0.53 | 1.02 | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Della Sala, R.; Centurelli, F.; Scotti, G. A High Performance 0.3 V Standard-Cell-Based OTA Suitable for Automatic Layout Flow. Appl. Sci. 2023, 13, 5517. https://doi.org/10.3390/app13095517

Della Sala R, Centurelli F, Scotti G. A High Performance 0.3 V Standard-Cell-Based OTA Suitable for Automatic Layout Flow. Applied Sciences. 2023; 13(9):5517. https://doi.org/10.3390/app13095517

Chicago/Turabian StyleDella Sala, Riccardo, Francesco Centurelli, and Giuseppe Scotti. 2023. "A High Performance 0.3 V Standard-Cell-Based OTA Suitable for Automatic Layout Flow" Applied Sciences 13, no. 9: 5517. https://doi.org/10.3390/app13095517

APA StyleDella Sala, R., Centurelli, F., & Scotti, G. (2023). A High Performance 0.3 V Standard-Cell-Based OTA Suitable for Automatic Layout Flow. Applied Sciences, 13(9), 5517. https://doi.org/10.3390/app13095517