A Novel Battery-Supplied AFE EEG Circuit Capable of Muscle Movement Artifact Suppression

Abstract

:1. Introduction

1.1. Medical Significance of EEG Signal Acquisition

1.2. EEG Signals into Frequency Sub-Bands: Comprehensive Categorization

1.3. Noise Interference in EEG Signal Acquisition

1.4. Design Specifications in Medical-Grade and Research-Grade EEG Generic Circuit Design

1.5. Problem Statement and Structure of the Present Study

- Section 1 (Introduction) highlights the medical importance of acquiring an EEG signal and its role in patient monitoring. It also discusses the sub-bands of frequencies into which the EEG signal is classified and introduces the challenges that noise brings to an acquired EEG signal.

- Section 2 (Related Works in EEG Circuit Design Analog Front-End Architectures) discusses design specifications for medical- and research-grade EEG circuits. The selected case studies are elaborated with respect to the comparative analysis of various architectures of EEG AFE.

- Section 3 (Materials and Methods: Novel Proposed EEG Analog Front-End Circuit System) puts forth a novel methodology for simulating and evaluating the novel EEG AFE circuitry design against practical cases using MATLAB R2023a.

- Section 4 (Simulation and Results: Comprehensive Analysis) is presented with the objective of comparing the theoretical values with the simulated values in a real-world scenario for the given circuit design, EEG-B3V3S7C1. The circuit’s performance is simulated in two of the commonest EEG measurement scenarios: the 50 Hz and 60 Hz power grid environments that exist outside the shielded lab conditions.

- Section 5 (Discussion) discusses the practical implications, potential limitations, and future perspectives of the proposed EEG circuit design.

- Section 6 (Conclusions) summarizes the entire article.

- for each wave and its implications at Table SA1.

- for each noise source and their corresponding frequency ranges at Table SA2.

- of the various components involved in EEG circuits, along with their respective functions at Table SA3.

- of the various technical distinctions in design specifications between medical-grade and research-grade EEG circuits at Table SA4.

2. Related Works: EEG Circuit Design Analog Front-End Architectures

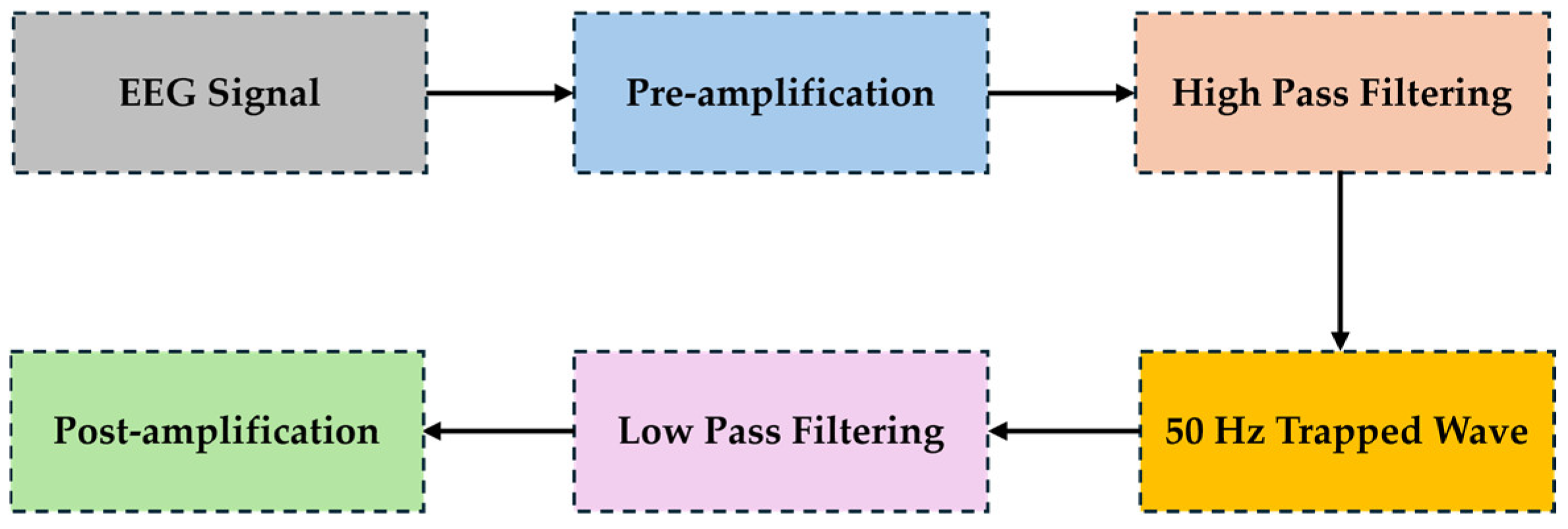

2.1. Low-Cost Circuit Design of EEG Analog Front-Ends: Case “1”

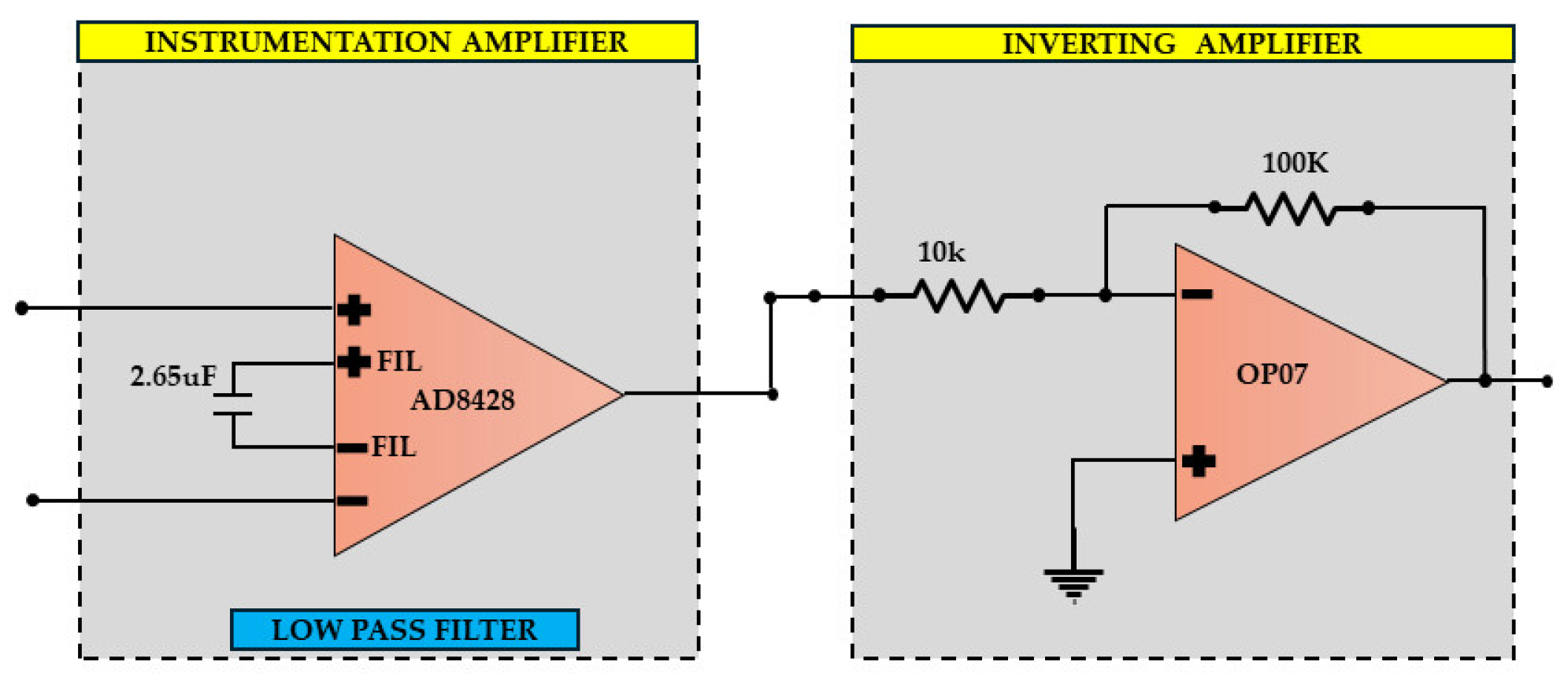

2.2. Battery-Powered, Low-Noise Amplifier Circuit Design of EEG Analog Front-Ends: Case “2”

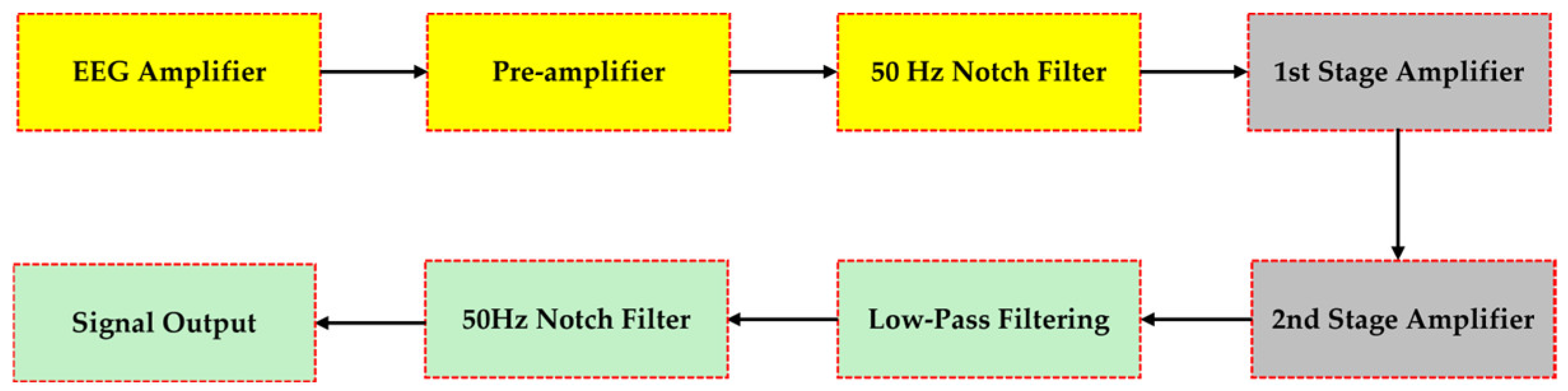

2.3. Double Notch Filter Circuit Design of EEG Analog Front-Ends: Case “3”

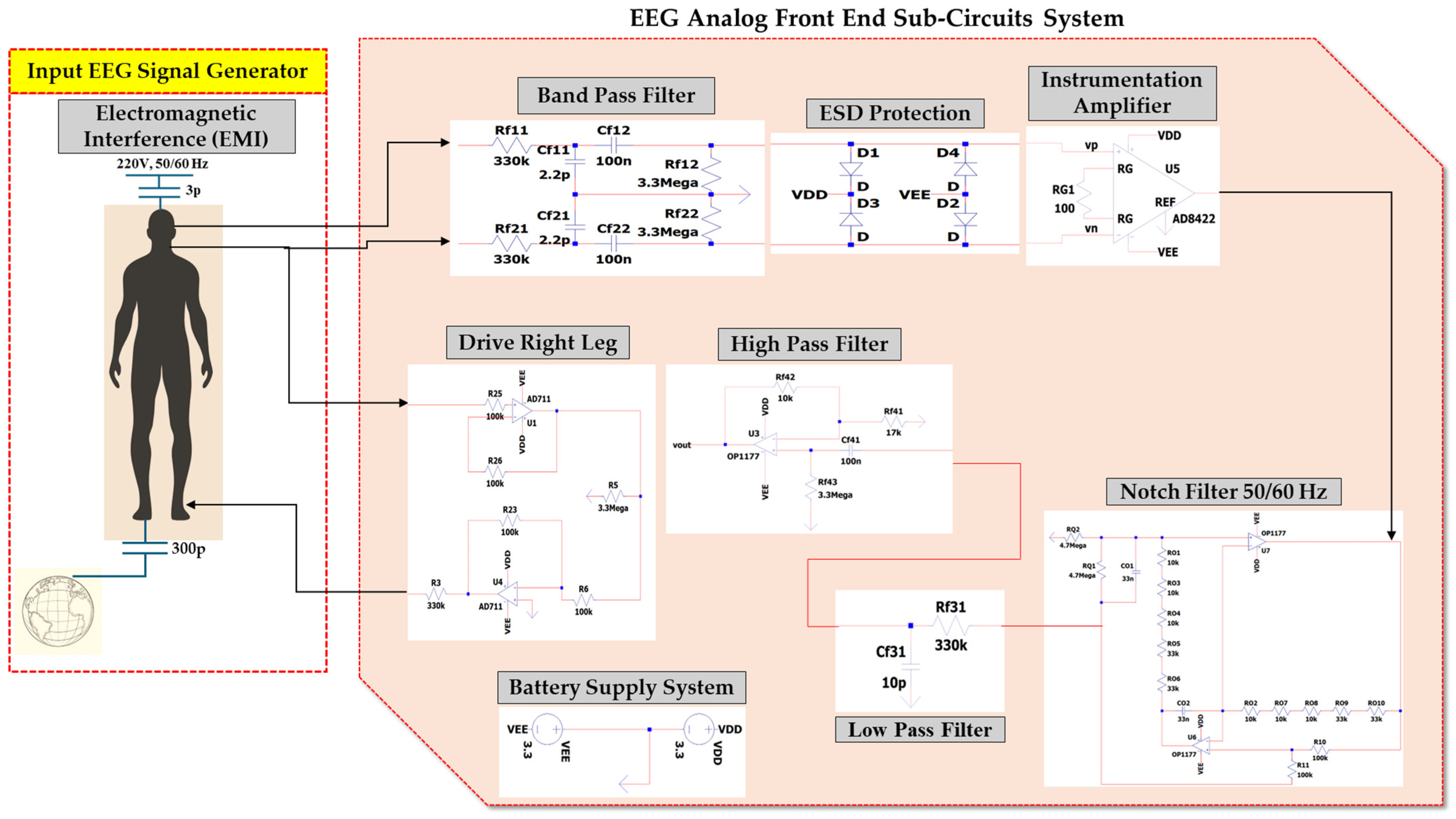

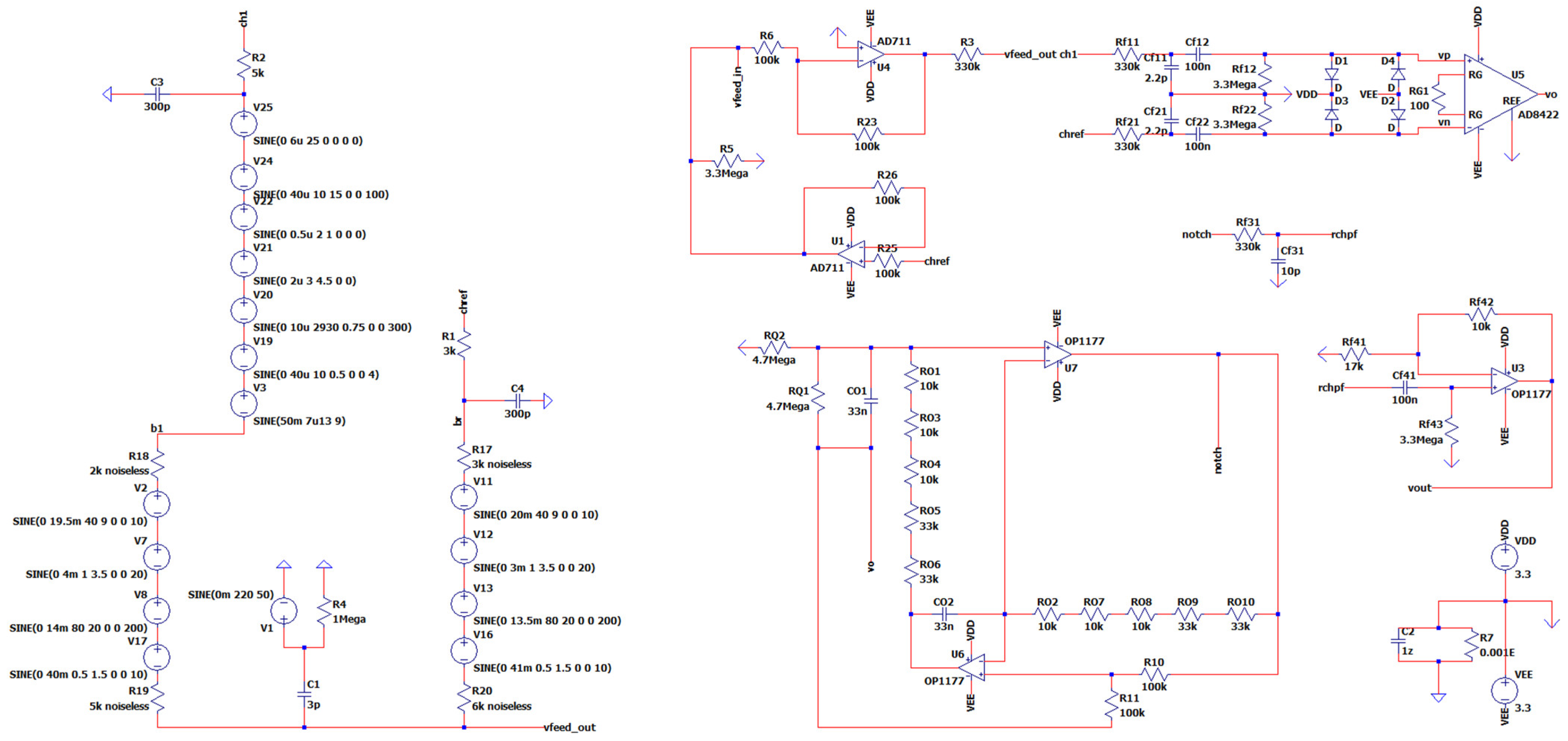

3. Materials and Methods: A Novel Proposed EEG Analog Front-End Circuit System

- 3.1: Simulates the EMI noise,

- 3.2: Simulates all types of muscle artifacts (noise stemming from either EMG, EOG, or ECG types of signals),

- 3.5: Provides a feedback loop between the circuit and the body that leads to a reduction in the overall noise and the possible sharp changes that may occur in the noise sources.,

- 3.6: Achieves an initial reduction in dc-offset and low-frequency and high-frequency noises,

- 3.7: Significantly reduces both EMI and artifacts that are contained in the common mode part of the input signal,

- 3.8: Eliminates the remaining EMI noise from the main either at 50 Hz or 60 Hz depending on the region-specific configuration of the circuit that is being used,

- 3.9: Eliminates the remaining high-frequency noises,

- 3.10: Eliminates the remaining dc-offset and the low-frequency noises.

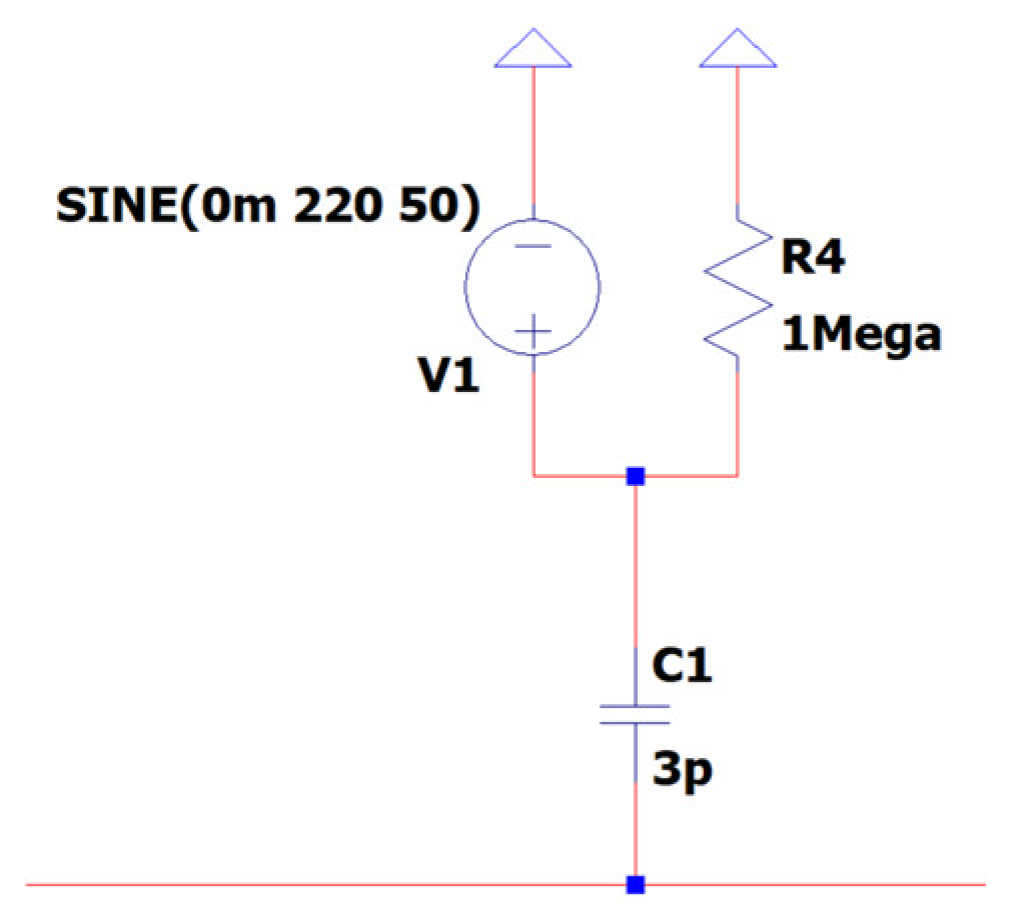

3.1. EEG Sub-Circuit Modeling the Electromagnetic Interference of Electric Grid with the Human Body

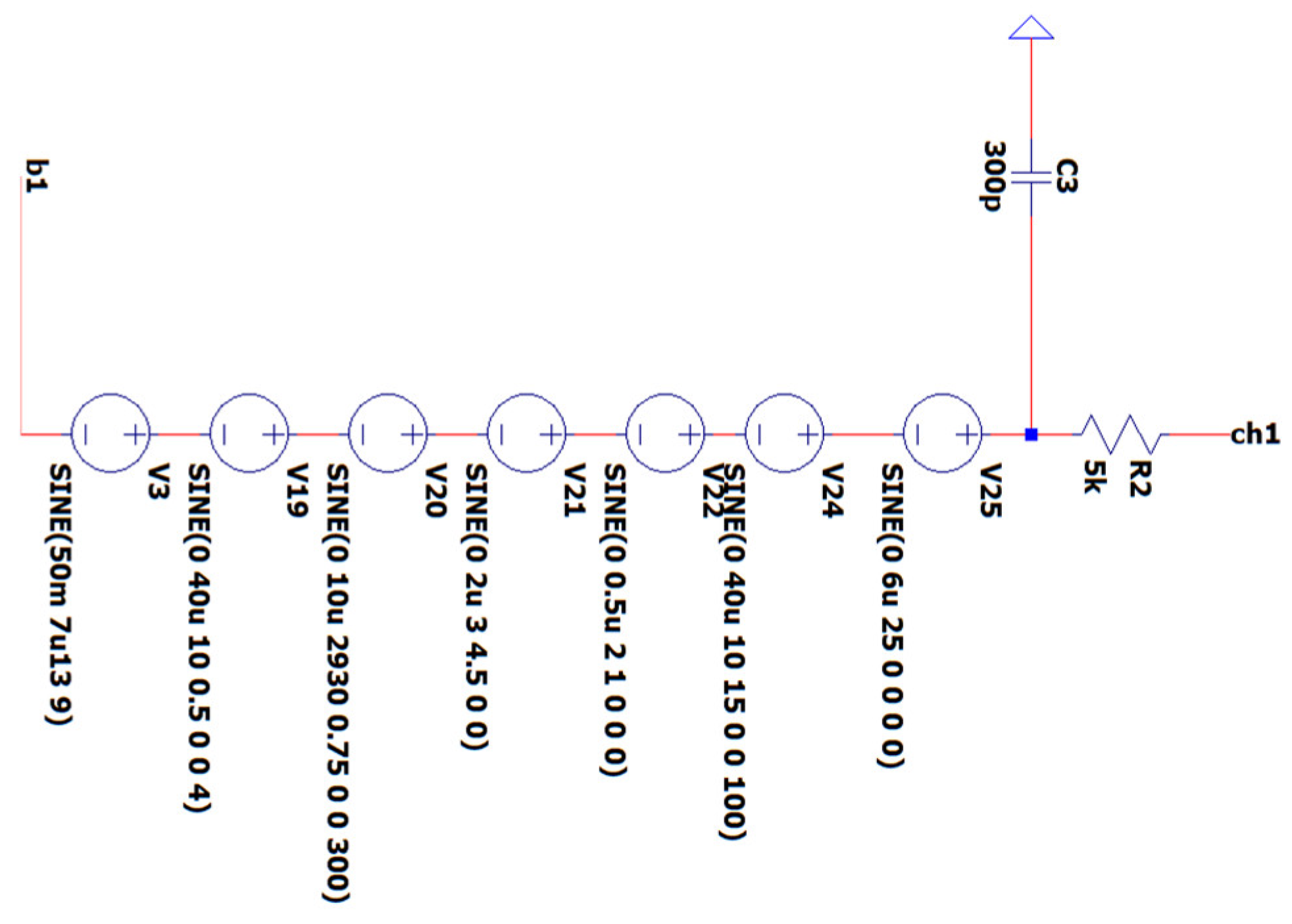

3.2. EEG Sub-Circuit Modeling the Human Body Apart from the Brain and Earth

3.3. EEG Sub-Circuit Modeling the Brain and the Electrode

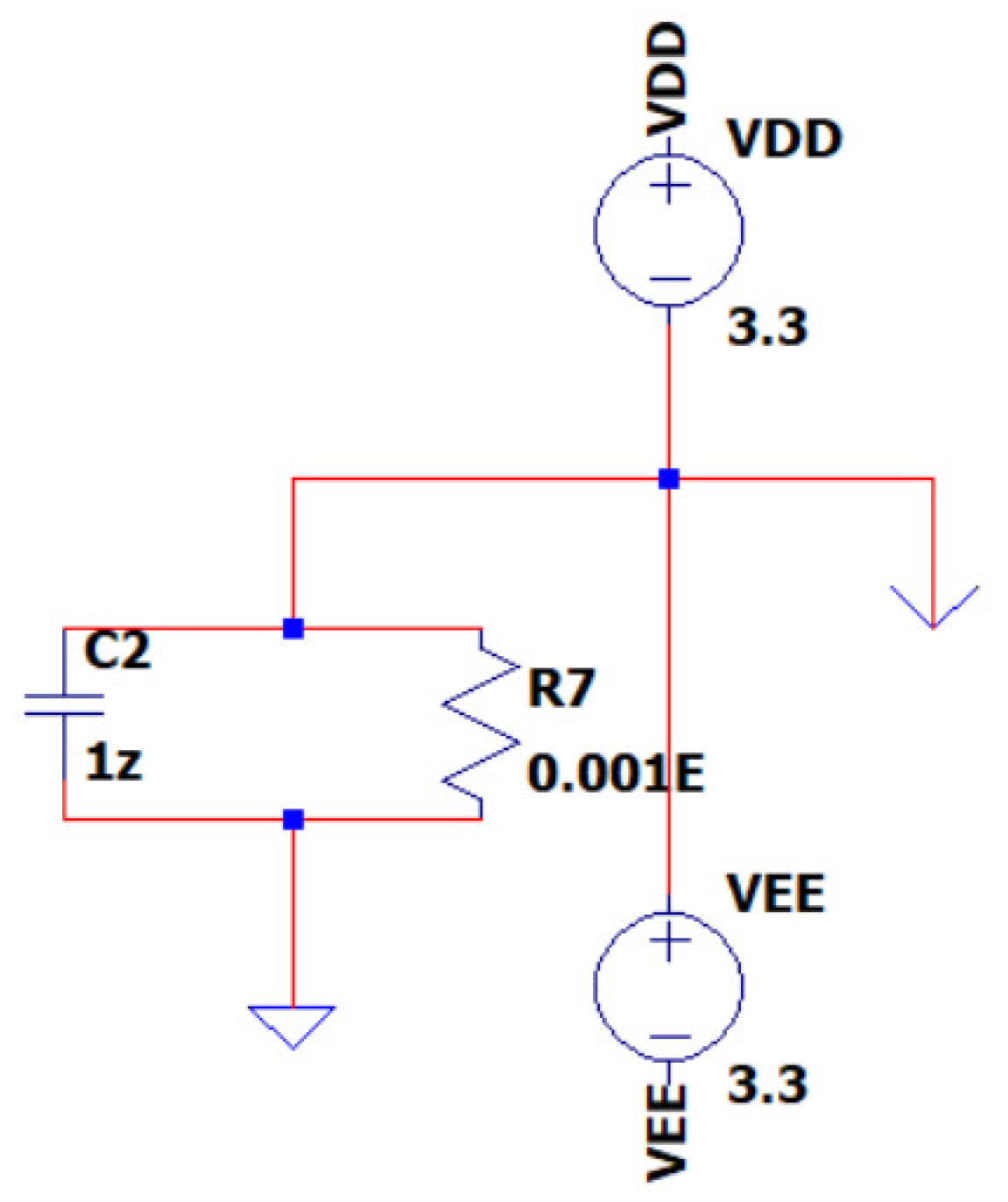

3.4. EEG Sub-Circuit Modeling the Battery Supply of the System

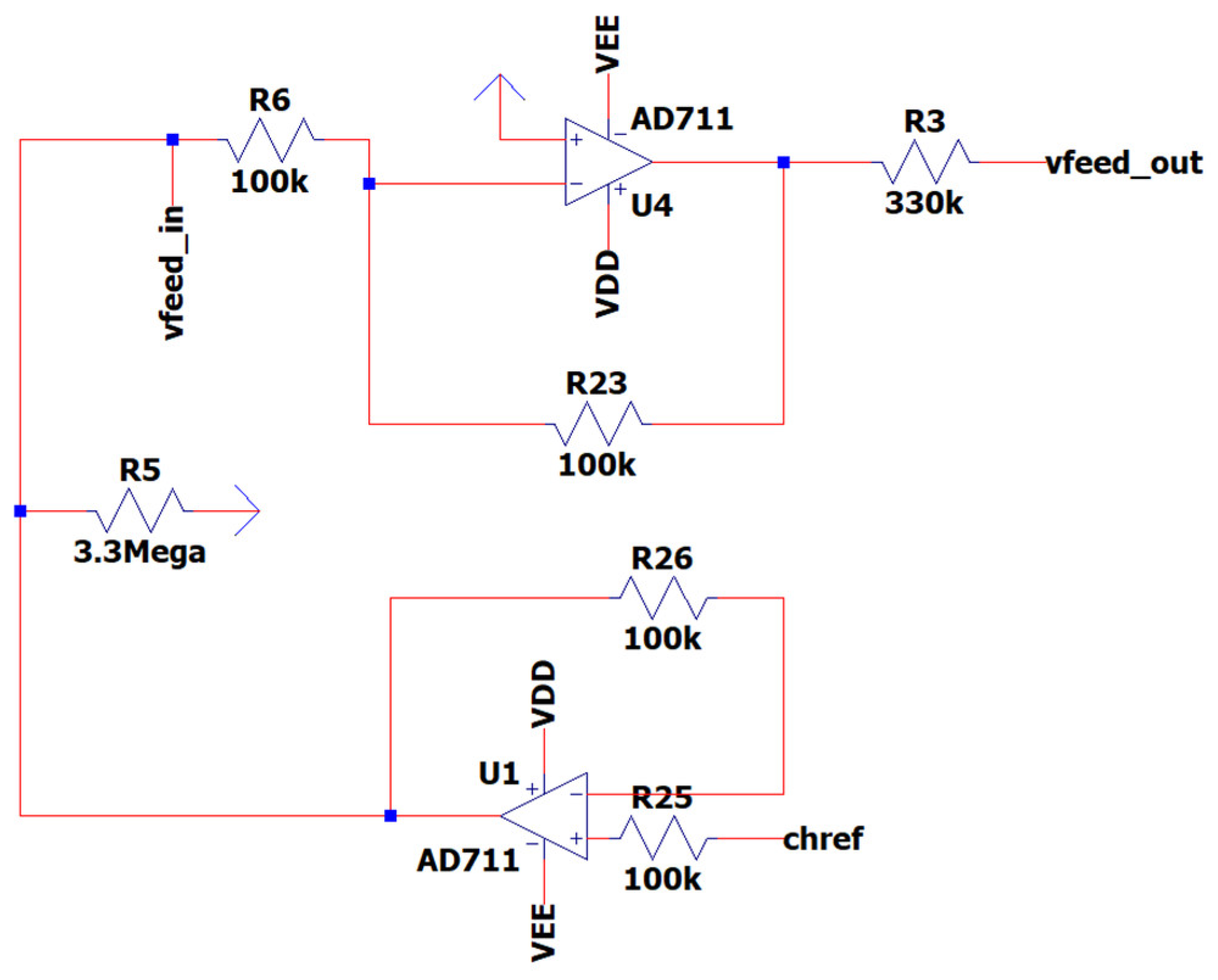

3.5. EEG Sub-Circuit Modeling the Driven Right Leg (DRL) Circuit

3.6. EEG Sub-Circuit Modeling the First Band-Pass Filter

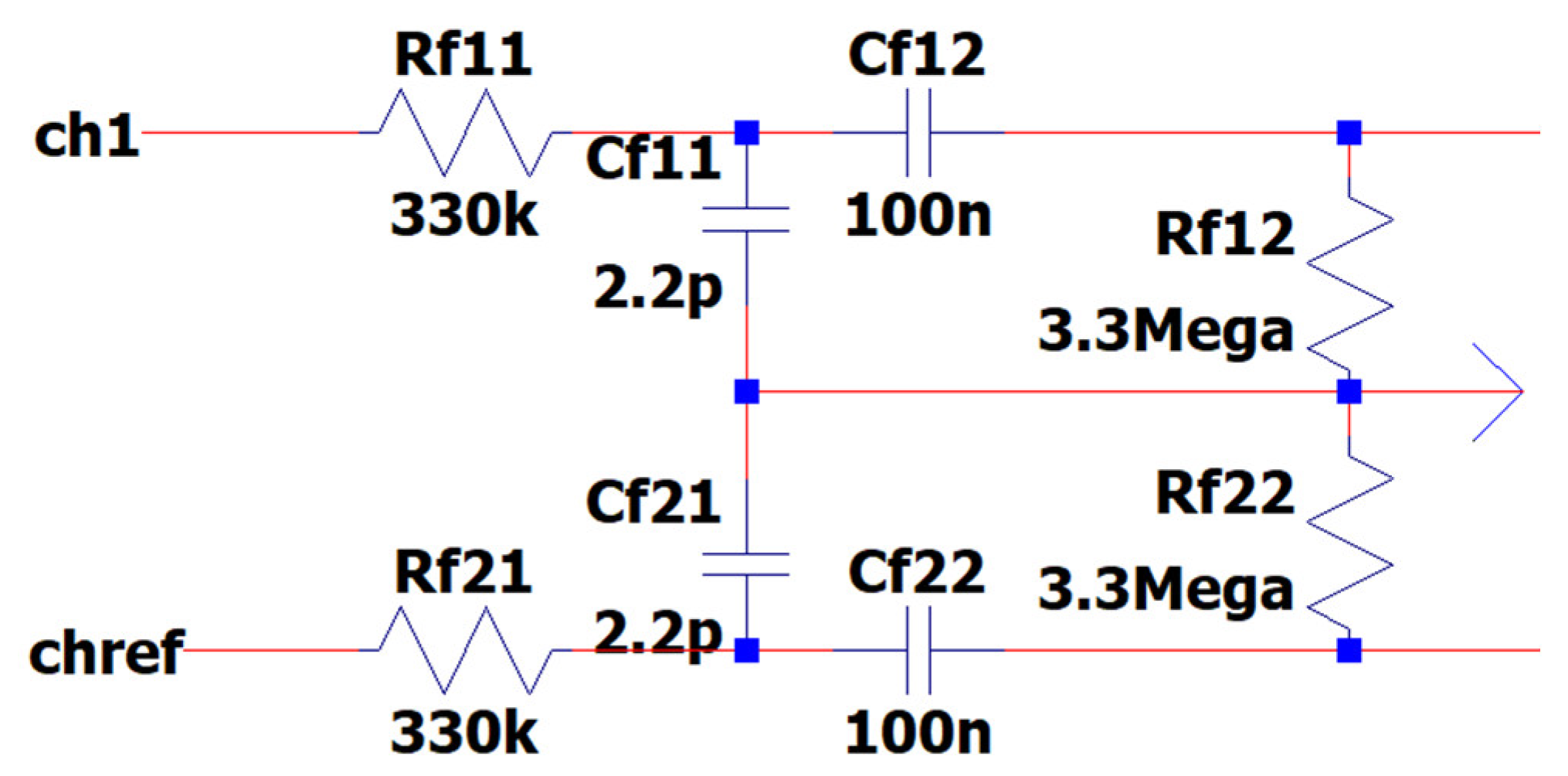

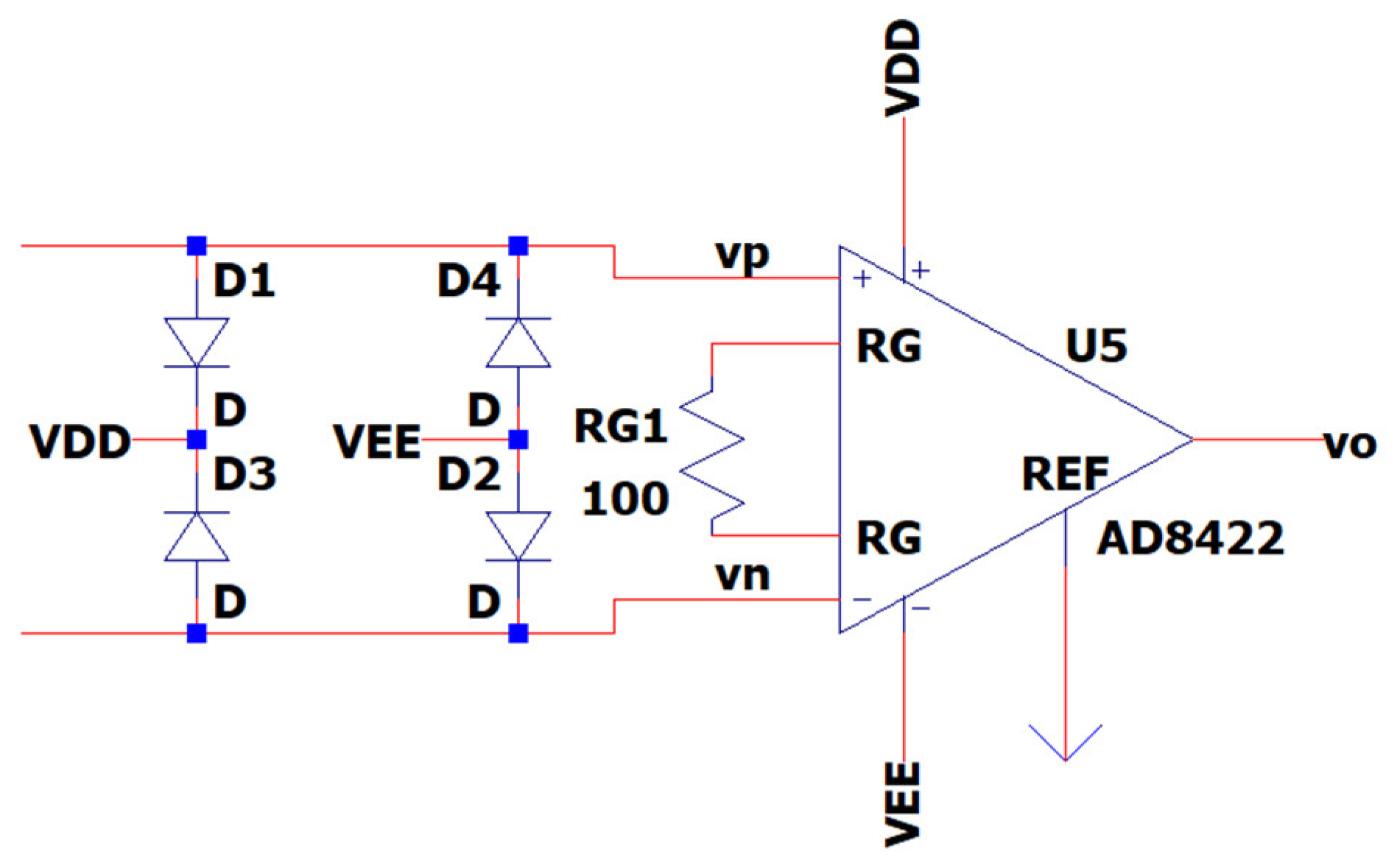

3.7. EEG Sub-Circuit Modeling the ESD Protection and the Instrumentation Amplifier

3.8. EEG Sub-Circuit Modeling the Fliedge Notch Filter 50 Hz or 60 Hz

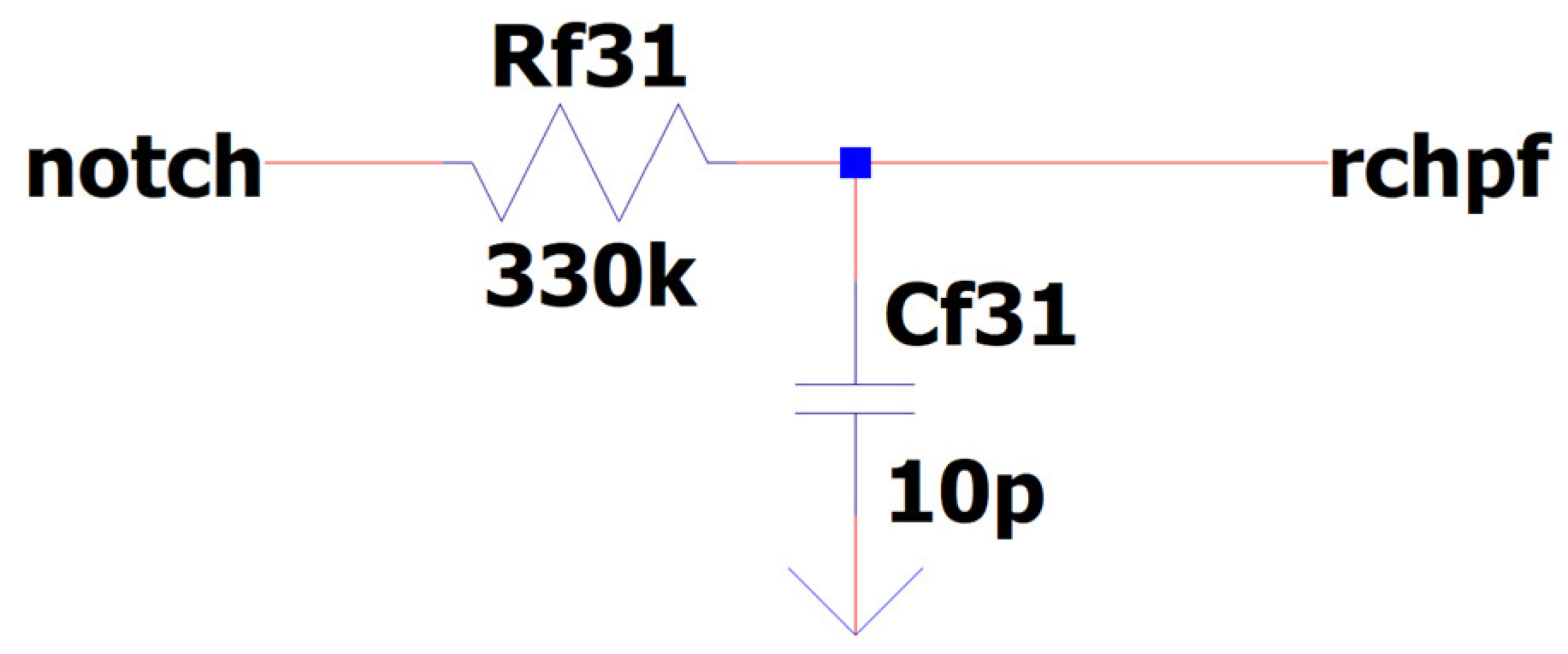

3.9. EEG Sub-Circuit Modeling the Second Low-Pass Filter

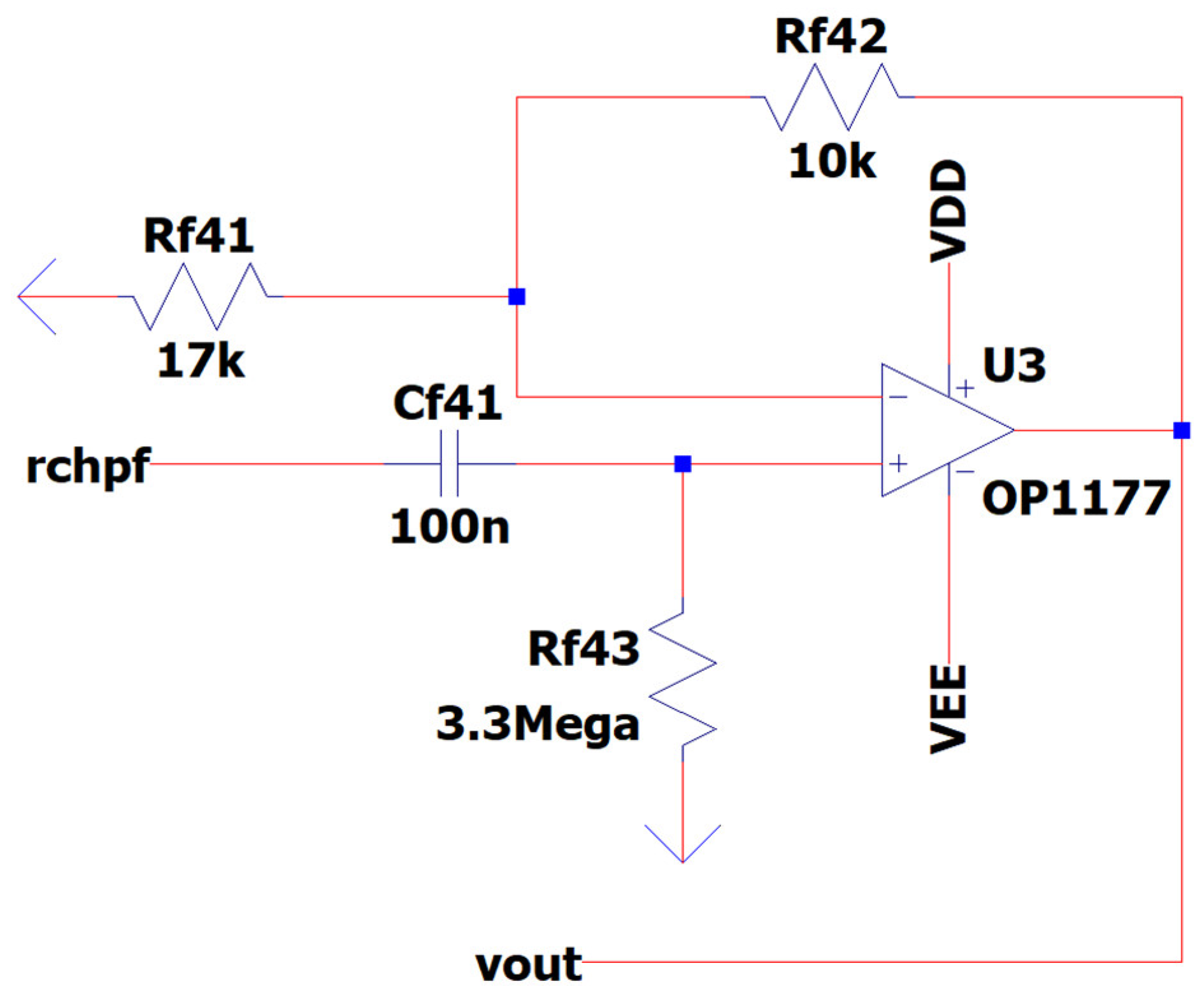

3.10. EEG Sub-Circuit Modeling the Second High-Pass Filter before the Analog to Digital Conversion

3.11. The Overall Novel EEG-B3V3S7C1 Circuit Design

- kB is the Boltzmann’s constant,

- T is absolute temperature in Kelvin in our case at room temperature (usually 25 °C), and

- R is the real part of the band-pass filter’s impedance.

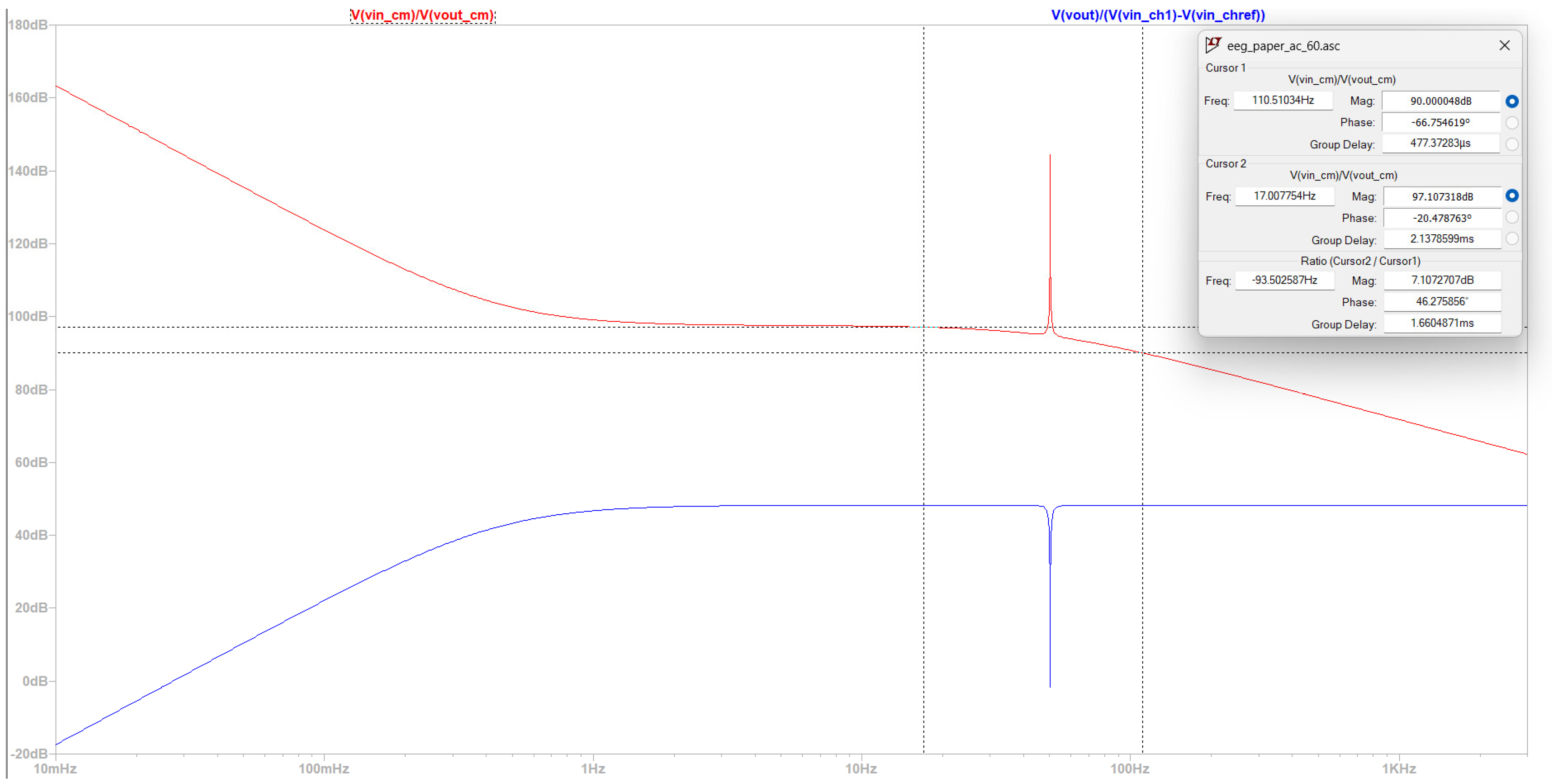

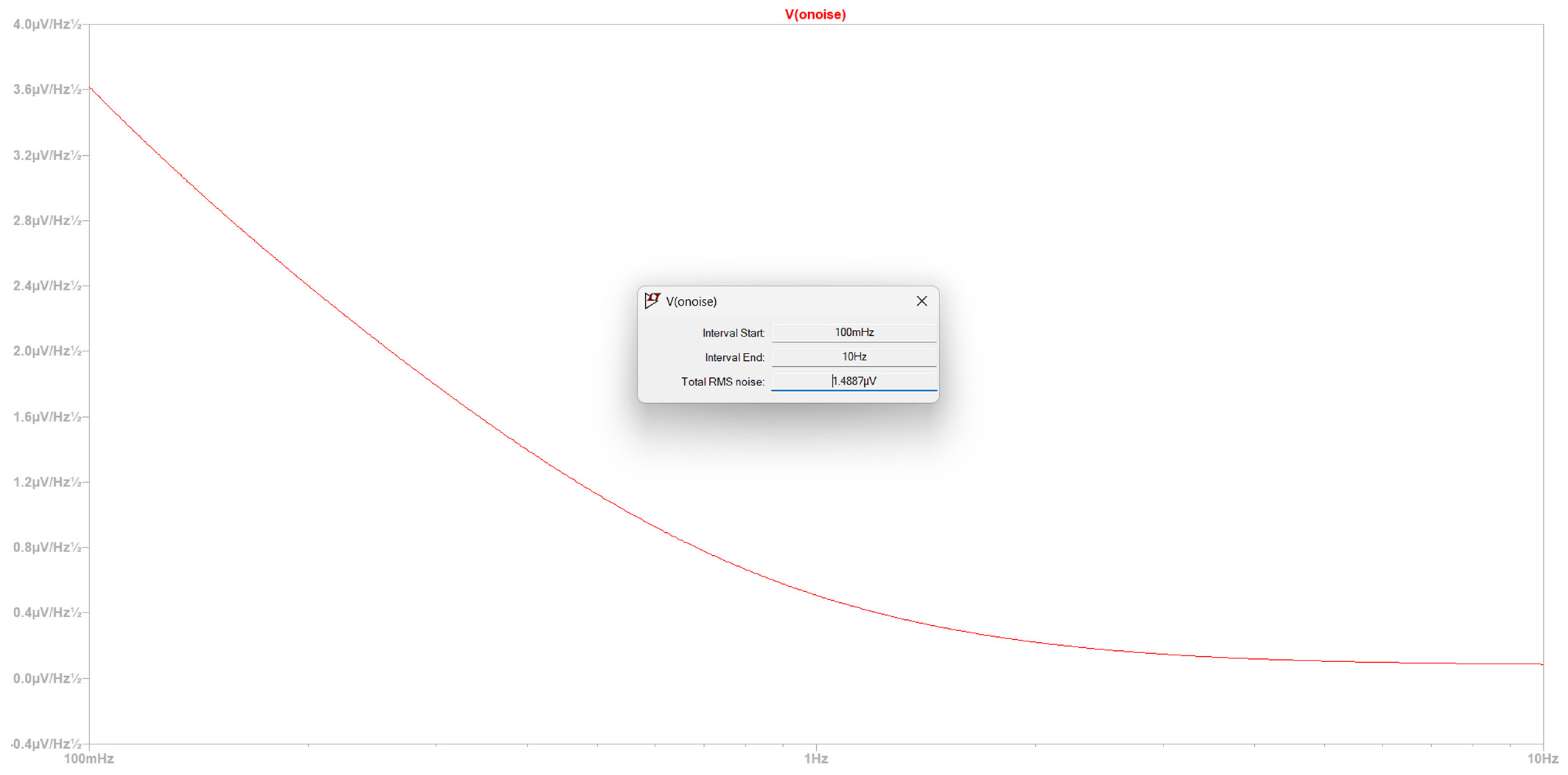

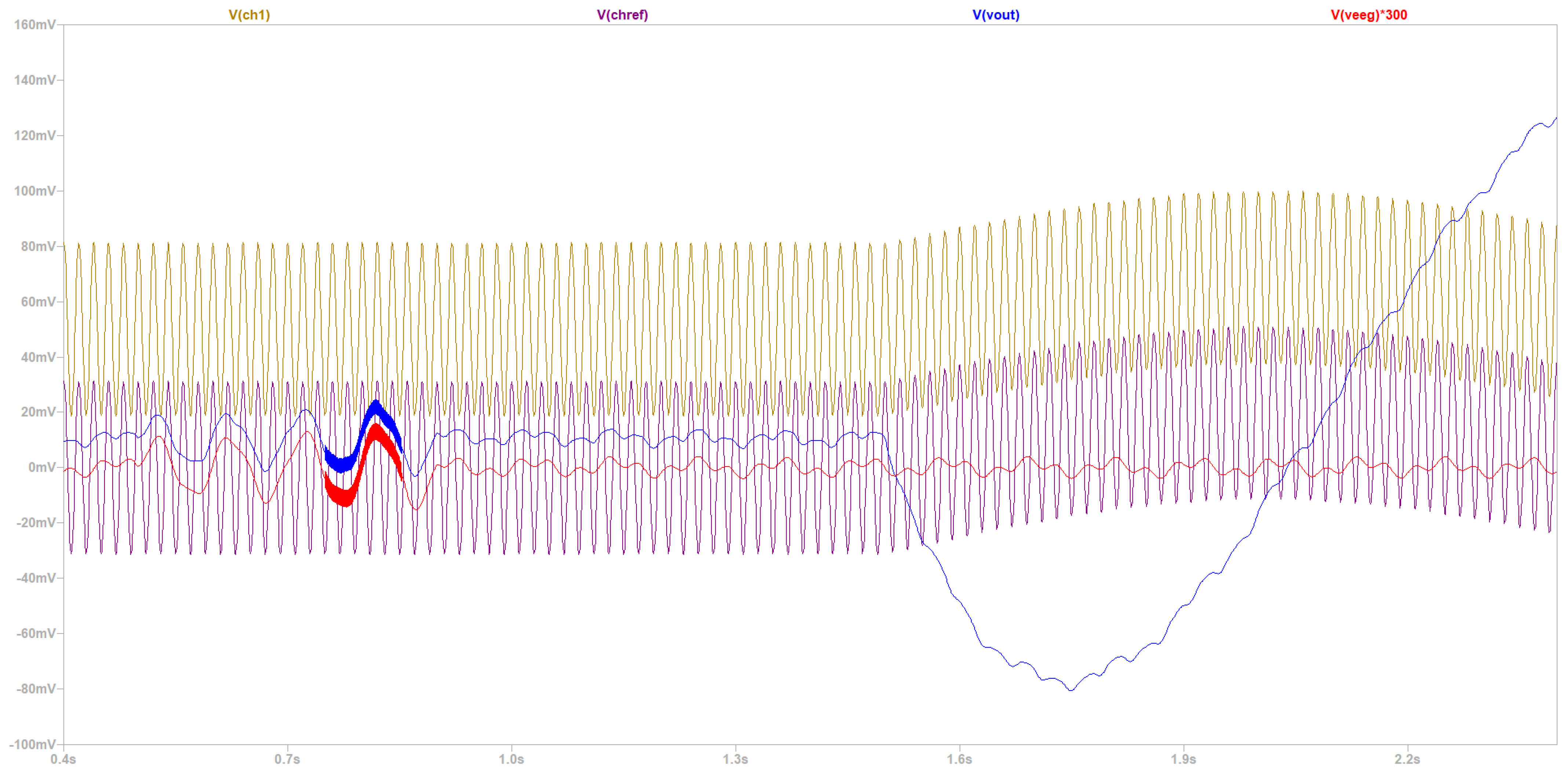

4. Simulation and Results: Comprehensive Analysis

- Time domain to make a qualitative comment with regard to CMRR, power consumption, gain, and noise level before the first amplification.

- Fourier frequency spectrum to validate if the information in the alpha, beta and theta wave bands is preserved.

- Fourier frequency spectrum and time domain to validate that the compound muscle movement artifacts are sufficiently suppressed.

4.1. Simulation of Novel EEG-B3V3S7C1 Circuit Design

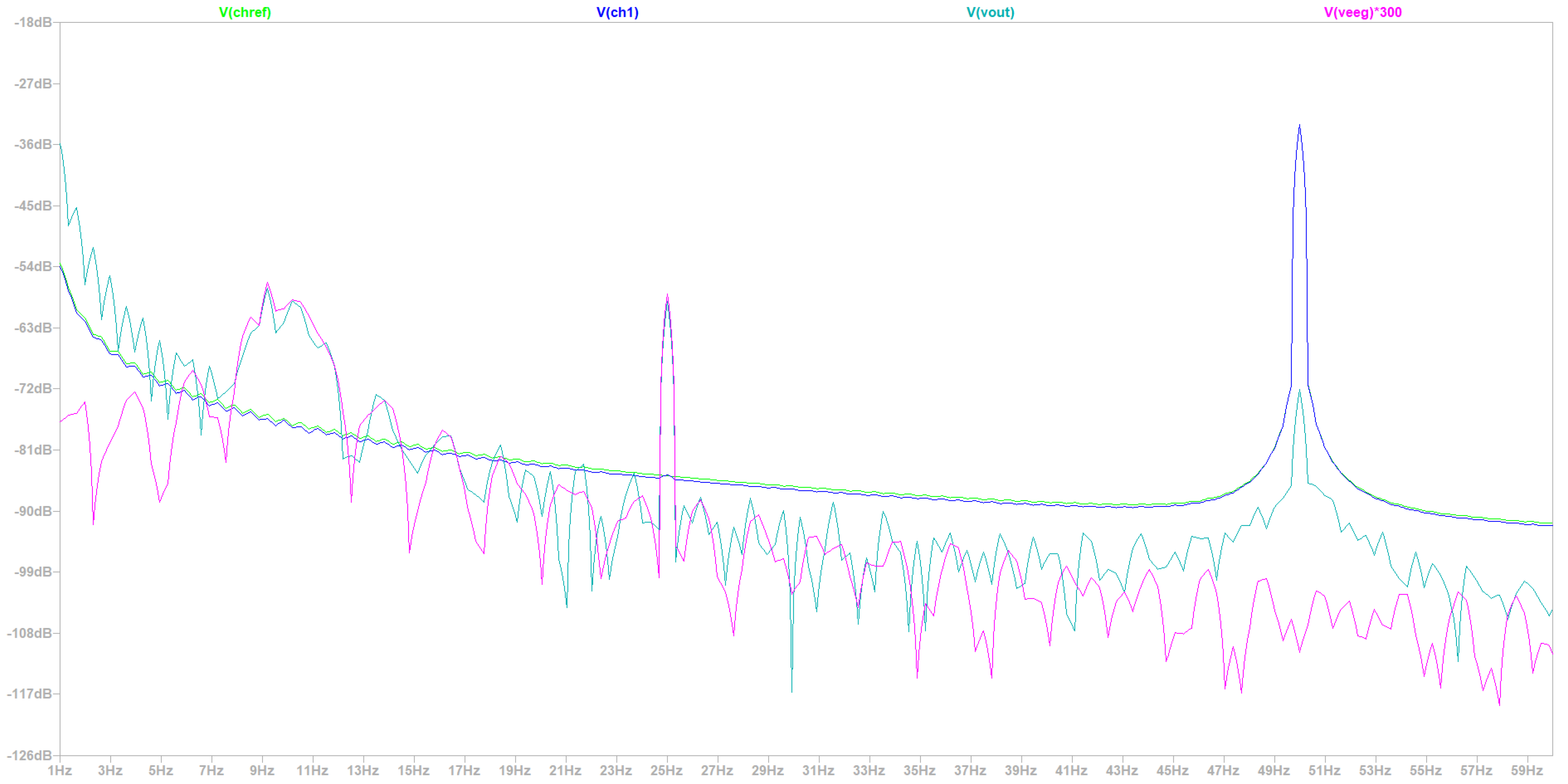

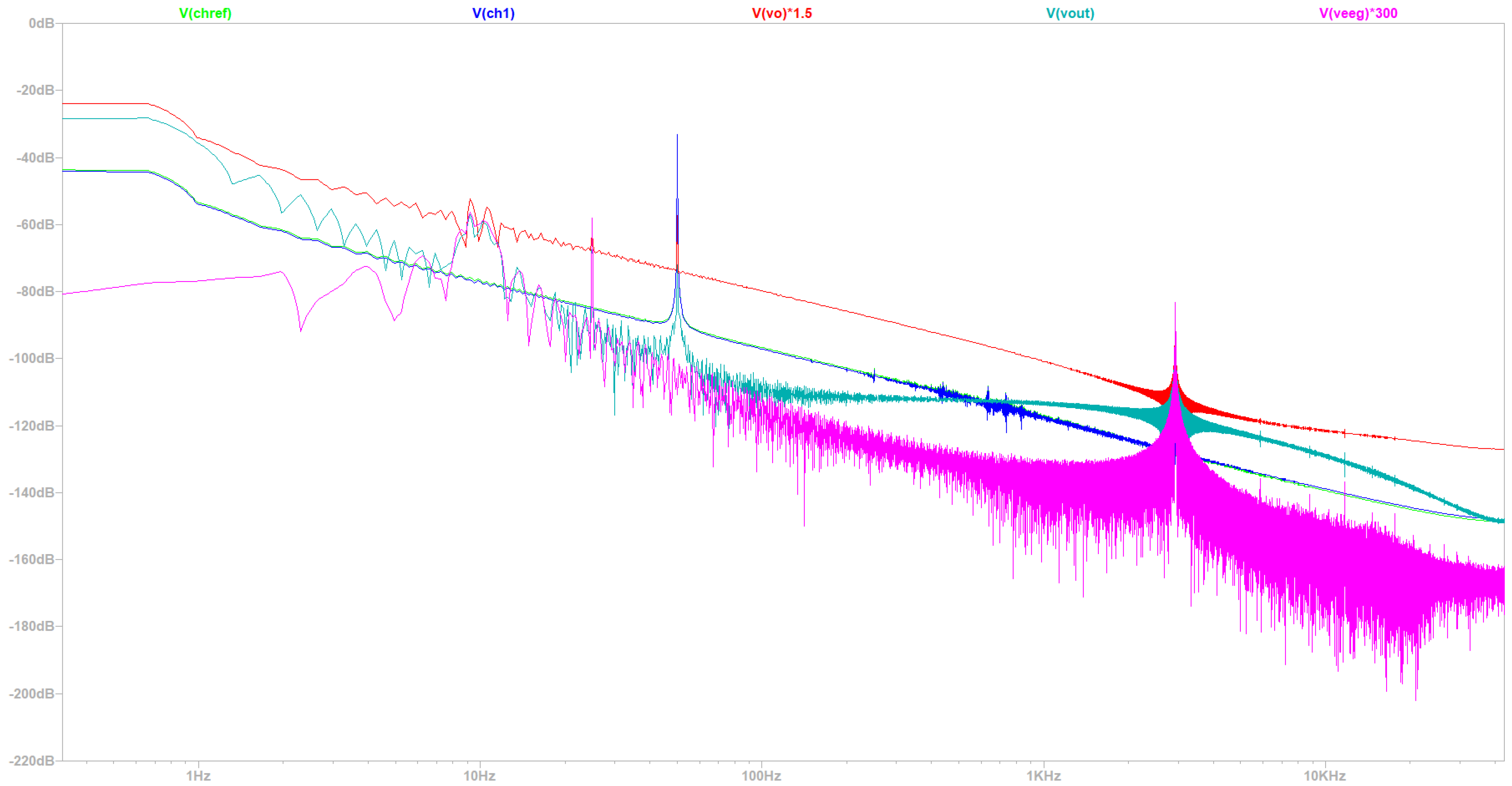

4.1.1. Simulation in a 50 Hz Electrical Grid Environment

- Simulation in a 50 Hz Electrical Grid Environment in the Time Domain

- Simulation at 50 Hz Electrical Grid Environment at the Fourier’s Spectrum

4.1.2. Simulation in an Environment with an Electrical Grid with Frequency 60 Hz

4.2. Comparative Analysis of the Simulated EEG-B3VS7C2 with the Cases 1, 2, 3

5. Discussion

5.1. Observed Limitations of the Proposed EEG Circuit Design

5.2. Future Perspectives: Possible Updates and Real-World Applications of the Proposed EEG Circuit Design

6. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Biasiucci, A.; Franceschiello, B.; Murray, M.M. Electroencephalography. Curr. Biol. 2019, 29, R80–R85. [Google Scholar] [CrossRef] [PubMed]

- Chaudhary, U.; Birbaumer, N.; Ramos-Murguialday, A. Brain–computer interfaces for communication and rehabilitation. Nat. Rev. Neurol. 2016, 12, 513–525. [Google Scholar] [CrossRef] [PubMed]

- Sanei, S.; Chambers, J.A. Fundamentals of EEG Signal Processing. In EEG Signal Processing; John Wiley & Sons Ltd.: Hoboken, NJ, USA, 2007; pp. 35–125. [Google Scholar] [CrossRef]

- Tatum, W.O. Ambulatory EEG. In Handbook of EEG Interpretation; Springer Publishing Company: Danvers, MA, USA, 2021. [Google Scholar] [CrossRef]

- Benbadis, S.R.; Beniczky, S.; Bertram, E.; MacIver, S.; Moshé, S.L. The role of EEG in patients with suspected epilepsy. Epileptic Disord. 2020, 22, 143–155. [Google Scholar] [CrossRef] [PubMed]

- Rubiños, C.; Godoy, D.A. Electroencephalographic monitoring in the critically ill patient: What useful information can it contribute? Med. Intensiv. (Engl. Ed.) 2020, 44, 301–309. [Google Scholar] [CrossRef] [PubMed]

- Michel, C.M.; Murray, M.M. Towards the utilization of EEG as a brain imaging tool. NeuroImage 2012, 61, 371–385. [Google Scholar] [CrossRef] [PubMed]

- Aboalayon, K.; Faezipour, M.; Almuhammadi, W.; Moslehpour, S. Sleep Stage Classification Using EEG Signal Analysis: A Comprehensive Survey and New Investigation. Entropy 2016, 18, 272. [Google Scholar] [CrossRef]

- Diykh, M.; Li, Y.; Wen, P. EEG Sleep Stages Classification Based on Time Domain Features and Structural Graph Similarity. IEEE Trans. Neural Syst. Rehabil. Eng. 2016, 24, 1159–1168. [Google Scholar] [CrossRef] [PubMed]

- Asadzadeh, S.; Yousefi Rezaii, T.; Beheshti, S.; Delpak, A.; Meshgini, S. A systematic review of EEG source localization techniques and their applications on diagnosis of brain abnormalities. J. Neurosci. Methods 2020, 339, 108740. [Google Scholar] [CrossRef] [PubMed]

- Dhar, P.; Garg, V.K. Brain-Related Diseases and Role of Electroencephalography (EEG) in Diagnosing Brain Disorders. In Lecture Notes in Networks and Systems; Springer: Singapore, 2020; pp. 317–326. [Google Scholar] [CrossRef]

- Ullah, H.; Mahmud, S.; Chowdhury, R.H. Identification of Brain disorders by Sub-band Decomposition of EEG signals and Measurement of Signal to Noise Ratio. Indones. J. Electr. Eng. Comput. Sci. 2016, 4, 568. [Google Scholar] [CrossRef]

- Iscan, Z.; Dokur, Z.; Demiralp, T. Classification of electroencephalogram signals with combined time and frequency features. Expert Syst. Appl. 2011, 38, 10499–10505. [Google Scholar] [CrossRef]

- Siuly, S.; Li, Y.; Zhang, Y. Electroencephalogram (EEG) and Its Background. In EEG Signal Analysis and Classification; Springer: Cham, Switzerland, 2016; pp. 3–21. [Google Scholar] [CrossRef]

- Puce, A.; Hämäläinen, M. A Review of Issues Related to Data Acquisition and Analysis in EEG/MEG Studies. Brain Sci. 2017, 7, 58. [Google Scholar] [CrossRef] [PubMed]

- Mumtaz, W.; Rasheed, S.; Irfan, A. Review of challenges associated with the EEG artifact removal methods. Biomed. Signal Process. Control 2021, 68, 102741. [Google Scholar] [CrossRef]

- Botti Benevides, A.; Silva da Paz Floriano, A.; Sarcinelli-Filho, M.; Freire Bastos-Filho, T. Introduction to Non-Invasive EEG-Based Brain–Computer Interfaces for Assistive Technologies, 1st ed.; Review of the Human Brain and EEG Signals; CRC Press: Boca Raton, FL, USA, 2020; pp. 1–49. [Google Scholar] [CrossRef]

- Chen, X.; Xu, X.; Liu, A.; Lee, S.; Chen, X.; Zhang, X.; McKeown, M.J.; Wang, Z.J. Removal of Muscle Artifacts From the EEG: A Review and Recommendations. IEEE Sens. J. 2019, 19, 5353–5368. [Google Scholar] [CrossRef]

- Sanei, S. Adaptive Processing of Brain Signals; Wiley: Hoboken, NJ, USA, 2013; ISBN 9781118622162. [Google Scholar] [CrossRef]

- Lebedev, M.A.; Nicolelis, M.A.L. Brain-Machine Interfaces: From Basic Science to Neuroprostheses and Neurorehabilitation. Physiol. Rev. 2017, 97, 767–837. [Google Scholar] [CrossRef] [PubMed]

- Elsayed, N.; Saad, Z.; Bayoumi, M. Brain Computer Interface: EEG Signal Preprocessing Issues and Solutions. Int. J. Comput. Appl. 2017, 169, 12–16. [Google Scholar] [CrossRef]

- Alkhorshid, D.R.; Molaeezadeh, S.F.; Alkhorshid, M.R. Analysis: Electroencephalography Acquisition System: Analog Design. Biomed. Instrum. Technol. 2020, 54, 346–351. [Google Scholar] [CrossRef] [PubMed]

- Cohen, M.X. Where Does EEG Come from and What Does It Mean? Trends Neurosci. 2017, 40, 208–218. [Google Scholar] [CrossRef] [PubMed]

- Tankisi, H.; Burke, D.; Cui, L.; de Carvalho, M.; Kuwabara, S.; Nandedkar, S.D.; Rutkove, S.; Stålberg, E.; van Putten, M.J.A.M.; Fuglsang-Frederiksen, A. Standards of instrumentation of EMG. Clin. Neurophysiol. 2020, 131, 243–258. [Google Scholar] [CrossRef] [PubMed]

- Vanhatalo, S.; Voipio, J.; Kaila, K. Full-band EEG (FbEEG): An emerging standard in electroencephalography. Clin. Neurophysiol. 2005, 116, 1–8. [Google Scholar] [CrossRef] [PubMed]

- Hari, R.; Parkkonen, L.; Nangini, C. The brain in time: Insights from neuromagnetic recordings. Ann. N. Y. Acad. Sci. 2010, 1191, 89–109. [Google Scholar] [CrossRef] [PubMed]

- Sullivan, T.J.; Deiss, S.R.; Cauwenberghs, G. A Low-Noise, Non-Contact EEG/ECG Sensor. In Proceedings of the IEEE Biomedical Circuits and Systems Conference, Montreal, QC, Canada, 27–30 November 2007. [Google Scholar] [CrossRef]

- Scheer, H.J.; Sander, T.; Trahms, L. The influence of amplifier, interface and biological noise on signal quality in high-resolution EEG recordings. Physiol. Meas. 2005, 27, 109–117. [Google Scholar] [CrossRef] [PubMed]

- Nagulapalli, R. Low Power and High Signal to Noise Ratio Bio-Medical AFE Design Techniques. Ph.D. Thesis, Faculty of Technology, Design & Environment Department of Mechanical Engineering & Mathematical Sciences, Oxford Brookes University, Oxford, UK, January 2023. Available online: https://radar.brookes.ac.uk/radar/file/74e88470-f109-4f23-a355-db01028f36a1/1/Nagulapalli2023AFEdesign.pdf (accessed on 30 July 2024).

- Wasade, V.S.; Spanaki, M.V. Understanding Epilepsy; Cambridge University Press: Cambridge, UK, 2019. [Google Scholar] [CrossRef]

- Usakli, A.B. Improvement of EEG Signal Acquisition: An Electrical Aspect for State of the Art of Front End. In Computational Intelligence and Neuroscience; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2010; Volume 630649, pp. 1–7. [Google Scholar] [CrossRef]

- Gardella, P.J.; Baez, E.; Cesaretti, J.M. Design of ESD protections for ECG applications. In Proceedings of the Conference on Electronics (CAE), Buenos Aires, Argentina, 27–28 February 2020. [Google Scholar] [CrossRef]

- Kuo, K.-C.; Chen, C.-T.; Liao, H.-Y. An Area Efficient Analog Front-End for Sensing EEG Signals with MOS Capacitors in 90 nm Process. In Proceedings of the International Conference on Consumer Electronics—Taiwan (ICCE-Taiwan), PingTung, China, 17–19 July 2023. [Google Scholar] [CrossRef]

- Cornelio, Z.U.; Resurreccion, P.; de Leon, M.T.; Rosales, M.; Hizon, J.R. An EEG Analog Front-End Unit for Wearable Applications Implemented in 28nm FD-SOI. In Proceeding of 20th International SoC Design Conference (ISOCC) 2023, Jeju, Republic of Korea, 25–28 October 2023. [Google Scholar] [CrossRef]

- Le, D.H.; Pham, T.-H.; Pham, C.-K. Design of a Configurable 4-Channel Analog Front-End for EEG Signal Acquisition on 180nm CMOS Process. REV J. Electron. Commun. 2023, 14, 10–19. [Google Scholar] [CrossRef]

- Pham, T.-H.; Huynh, H.-A.; Pham, C.-K.; Le, D.-H. Design of a Configurable Low-Noise 1-Channel Analog Front-End for EEG Signal Recording on 180 nm CMOS Process. In Proceedings of the International Conference on Advanced Technologies for Communications (ATC) 2023, Da Nang, Vietnam, 19–21 October 2023. [Google Scholar] [CrossRef]

- Li, X.; Ren, S.; Li, X.; Zhao, T.; Deng, X.; Zheng, W. An LFP/AP Mode Reconfigurable Analog Front-End Combining an Electrical EEEG-iEEG Model for the Closed-Loop VNS. IEEE Trans. Biomed. Circuits Syst. 2024, 18, 408–422. [Google Scholar] [CrossRef] [PubMed]

- Hu, H.-Y.; Wang, L.-H.; Kuo, I.-C.; Wang, M.-H.; Wang, S.-F.; Huang, P.-C. A Multi-Channel EEG Acquisition Device Based on BT Microcontroller. In Proceedings of the International Conference on Consumer Electronics—Taiwan (ICCE-Taiwan) 2023, PingTung, China, 17–19 July 2023. [Google Scholar] [CrossRef]

- Han, Y.; Zhao, L.; Stephany, R.G.; Hsieh, J.-C.; Wang, H.; Jia, Y. A Scattered Wireless EEG Recording System. In Proceedings of the IEEE Biomedical Circuits and Systems Conference (BioCAS) 2023, Toronto, ON, Canada, 19–21 October 2023. [Google Scholar] [CrossRef]

- Chen, W. Multi-channel EEG signal acquisition system based on nRF52832. In Proceedings of the 5th International Conference on Communications, Information System and Computer Engineering (CISCE) 2023, Guangzhou, China, 14–16 April 2023. [Google Scholar] [CrossRef]

- Liu, L.; Xu, J.; Yin, J.; Liao, X.; Tian, Y. A Low-Power and Constant-Bandwidth Analog Front End Based on Current-Reused DDA for Multibiosignal Acquisition. IEEE Sens. J. 2023, 23, 24711–24720. [Google Scholar] [CrossRef]

- Ge, T.; Li, P.; Duan, Q.; Yu, G. A low-noise, high-precision chopper instrument amplifier for EEG signal amplification. In Proceedings of the 5th International Conference on Circuits and Systems (ICCS) 2023, Huzhou, China, 27–30 October 2023. [Google Scholar] [CrossRef]

- Kumar, S.C.P.; Chandrasekar, A.; Nagaraj, A.; Gupta, P.; Sekhar, S. Design of an ElectroEncephaloGram (EEG) amplification circuit for neonates. In Proceedings of the International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, India, 6–8 April 2016. [Google Scholar] [CrossRef]

- Whitchurch, A.K.; Abraham, J.K.; Lonkar, M.A.; Varadan, V.K. Design of a Compact Amplifier and Signal Conditioning Module for Wireless EEG Monitoring. In Proceedings of the IEEE Region 5 Technical Conference, Fayetteville, AR, USA, 20–22 April 2007. [Google Scholar] [CrossRef]

- Zhang, X.; Zhang, Z. Design on Sampling Circuit of EEG Signal Based on AT89C2051 Single-Chip. In Proceedings of the Fourth International Conference on Innovative Computing, Information and Control (ICICIC), Kaohsiung, China, 7–9 December 2009. [Google Scholar] [CrossRef]

- Salahuddin Morsalin, S.M.; Lai, S.-C. Front-end circuit design for electroencephalography (EEG) signal. In Proceedings of the 2nd International Conference on Computing, Analytics and Networks (ICAN), Indo—Taiwan, Rajpura, India, 7–15 February 2020. [Google Scholar] [CrossRef]

- Xu, X.; Wang, P. Low-Cost Circuit Design for EEG Signal Amplification and Extraction. In Proceedings of the IEEE Asia-Pacific Conference on Image Processing, Electronics and Computers (IPEC), Dalian, China, 14–16 April 2021. [Google Scholar] [CrossRef]

- Choudhary, S.K.; Bera, T.K. Designing of Battery-Based Low Noise Electroencephalography (EEG) Amplifier for Brain Signal Monitoring: A Simulation Study. In Proceedings of the IEEE 6th International Conference on Condition Assessment Techniques in Electrical Systems (CATCON), Durgapur, India, 17–19 December 2022; pp. 422–426. [Google Scholar] [CrossRef]

- Yuge, S.; Ning, Y.; Feng, P. A novel design of EEG signal amplifier. In Proceeding of 24th Chinese Control and Decision Conference (CCDC), Taiyuan, China, 23–25 May 2012. [Google Scholar] [CrossRef]

- Analog Devices, Inc. AD8428: High Gain, High Voltage Instrumentation Amplifier. Data Sheet. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ad8428.pdf (accessed on 10 February 2024).

- Tsavdaridis, G.; Papaodysseus, C.; Karadimas, N.V.; Papazafeiropoulos, G.; Delis, A. Methodologies and Handling Techniques of Large-Scale Information in Decision Support Systems for Complex Missions. Appl. Sci. 2024, 14, 1995. [Google Scholar] [CrossRef]

- Tsavdaridis, G. Adjustable and Adaptable Systems for Crisis Management Support, Monitoring, and Control of Operational Processes. Ph.D. Thesis, School of Electrical and Computer Engineering, National Technical University of Athens, Athens, Greece, March 2024. Available online: https://www.didaktorika.gr/eadd/handle/10442/56130 (accessed on 30 July 2024).

- Jobert, M.; Wilson, F.J.; Ruigt, G.S.F.; Brunovsky, M.; Prichep, L.S.; Drinkenburg, W.H.I.M. Guidelines for the Recording and Evaluation of Pharmaco-EEG Data in Man: The International Pharmaco-EEG Society (IPEG). Neuropsychobiology 2012, 66, 201–220. [Google Scholar] [CrossRef] [PubMed]

- Alizadeh-Taheri, B.; Smith, R.L.; Knight, R.T. An Active, Microfabricated, Scalp Electrode-array For EEG Recording. In Proceedings of the International Solid-State Sensors and Actuators Conference—TRANSDUCERS ’95, Stockholm, Sweden, 25–29 June 1995. [Google Scholar] [CrossRef]

- Zhang, L.; Guo, X.; Wu, X.; Zhou, B. Low-cost circuit design of EEG signal acquisition for the brain-computer interface system. In Proceedings of the 6th International Conference on Biomedical Engineering and Informatics, Hangzhou, China, 16–18 December 2013. [Google Scholar] [CrossRef]

- Analog Devices, Inc. AD8422: 1.8 nV/√Hz, Rail-to-Rail, Low Power Instrumentation Amplifier. Data Sheet. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ad8422.pdf (accessed on 10 February 2024).

- Zumbahlen, H. (Ed.) Analog Filters. In Linear Circuit Design Handbook; Newnes: Burlington, NJ, USA, 2008; pp. 581–679. [Google Scholar] [CrossRef]

- Wang, J.; Tang, L.; E Bronlund, J. Surface EMG Signal Amplification and Filtering. Int. J. Comput. Appl. 2013, 82, 15–22. [Google Scholar] [CrossRef]

- Hsueh, J.-J.; Chen, T.-S.; Chen, J.-J.; Shaw, F.-Z. Neurofeedback training of EEG alpha rhythm enhances episodic and working memory. Hum. Brain Mapp. 2016, 37, 2662–2675. [Google Scholar] [CrossRef]

- Texas Instruments. INA333 Low-Power, Precision Instrumentation Amplifier. Available online: https://www.ti.com/lit/ds/symlink/ina333.pdf (accessed on 12 February 2024).

| Common Mode Rejection Ratio (CMRR) | Circuit Bandwidth | Signal Quality | Common Mode Rejection Ratio (CMRR) |

|---|---|---|---|

| Greater than 90 dB | 0.5 Hz to 20 kHz |

|

|

| Requirements/Specifications | Case “1” [47] | Case “2” [48] | Case “3” [49] | Proposed Circuit EEG Design |

|---|---|---|---|---|

| Common Mode Rejection Ratio (CMRR) | >120 dB | 140 dB | Estimated at 110 dB | Greater than 90 dB below 110 Hz |

| Circuit Bandwidth | 0.3 to 40 Hz | 3.5 MHz | 0.5 to 33.86 Hz | 0.5 Hz to 48 kHz min (0.5 Hz to 21 kHz min 0 dB passband) |

| Signal Quality (Gain and Noise) |

|

|

|

|

| Circuits Comparison | Case “1” [47] Limitation | Case “2” [48] Limitation | Case “3” [49] Limitation | Proposed Circuit EEG Design Innovation |

|---|---|---|---|---|

| Point of interest |

|

|

|

|

|

|

|

| |

|

|

|

| |

|

|

|

| |

|

|

|

|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Delis, A.; Tsavdaridis, G.; Tsanakas, P. A Novel Battery-Supplied AFE EEG Circuit Capable of Muscle Movement Artifact Suppression. Appl. Sci. 2024, 14, 6886. https://doi.org/10.3390/app14166886

Delis A, Tsavdaridis G, Tsanakas P. A Novel Battery-Supplied AFE EEG Circuit Capable of Muscle Movement Artifact Suppression. Applied Sciences. 2024; 14(16):6886. https://doi.org/10.3390/app14166886

Chicago/Turabian StyleDelis, Athanasios, George Tsavdaridis, and Panayiotis Tsanakas. 2024. "A Novel Battery-Supplied AFE EEG Circuit Capable of Muscle Movement Artifact Suppression" Applied Sciences 14, no. 16: 6886. https://doi.org/10.3390/app14166886

APA StyleDelis, A., Tsavdaridis, G., & Tsanakas, P. (2024). A Novel Battery-Supplied AFE EEG Circuit Capable of Muscle Movement Artifact Suppression. Applied Sciences, 14(16), 6886. https://doi.org/10.3390/app14166886