A Fully Integrated High Linearity CMOS Dual-Band Power Amplifier for WLAN Applications in 55-Nm CMOS

Abstract

:1. Introduction

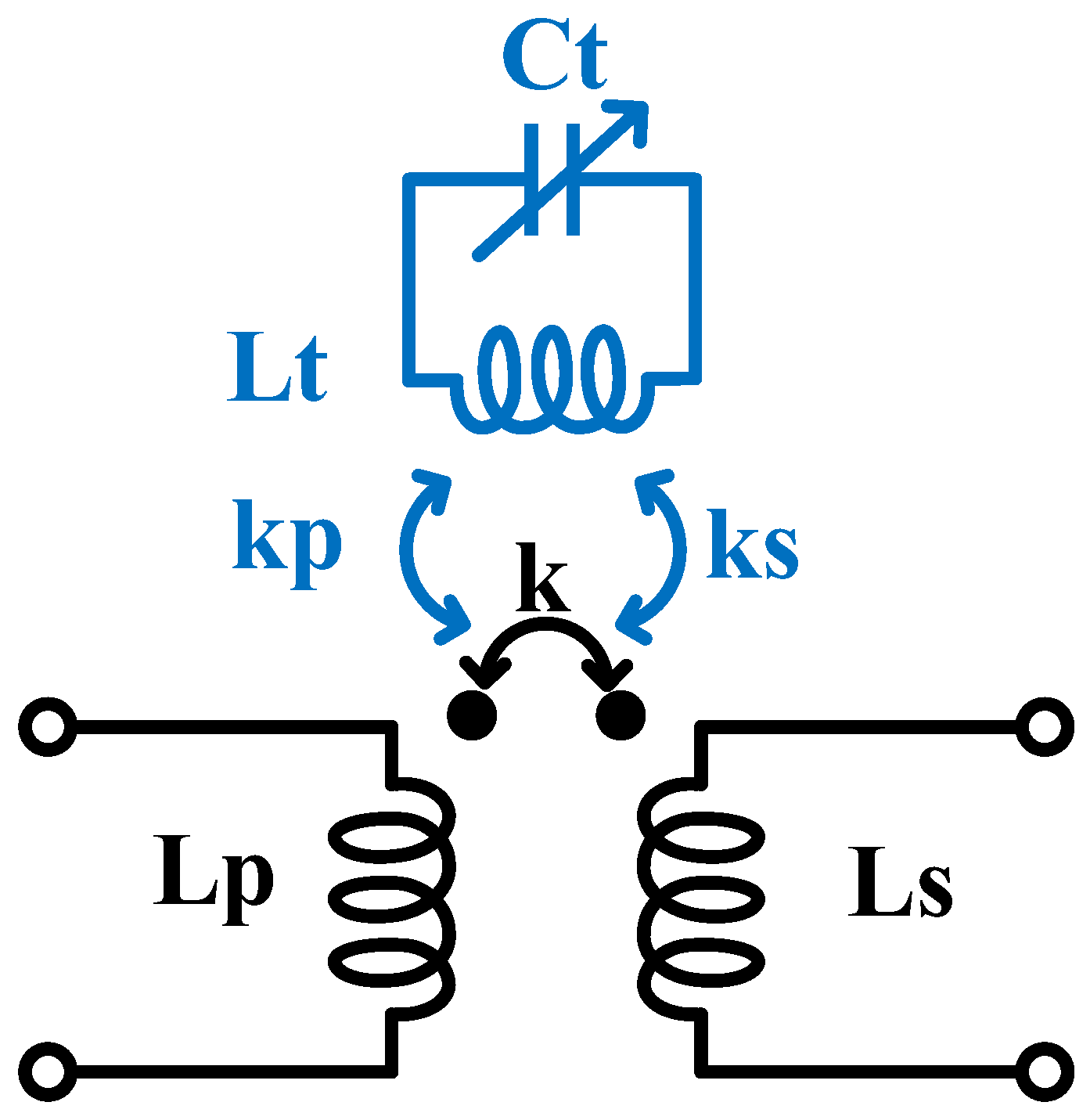

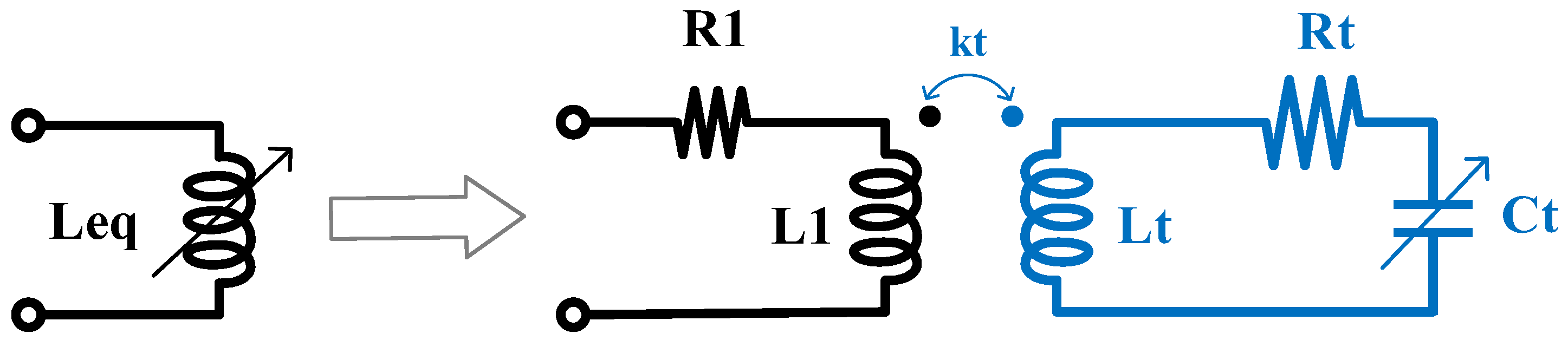

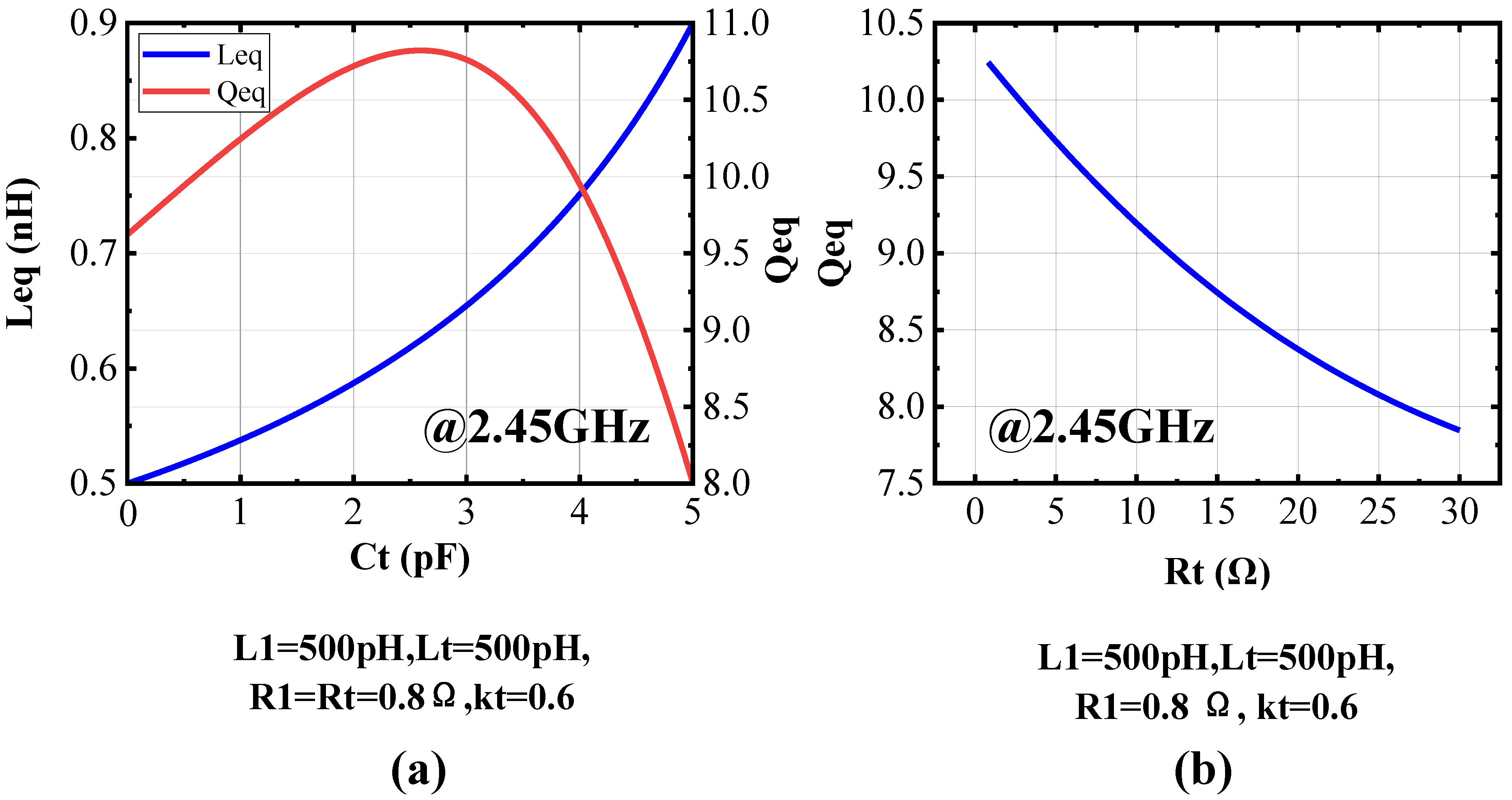

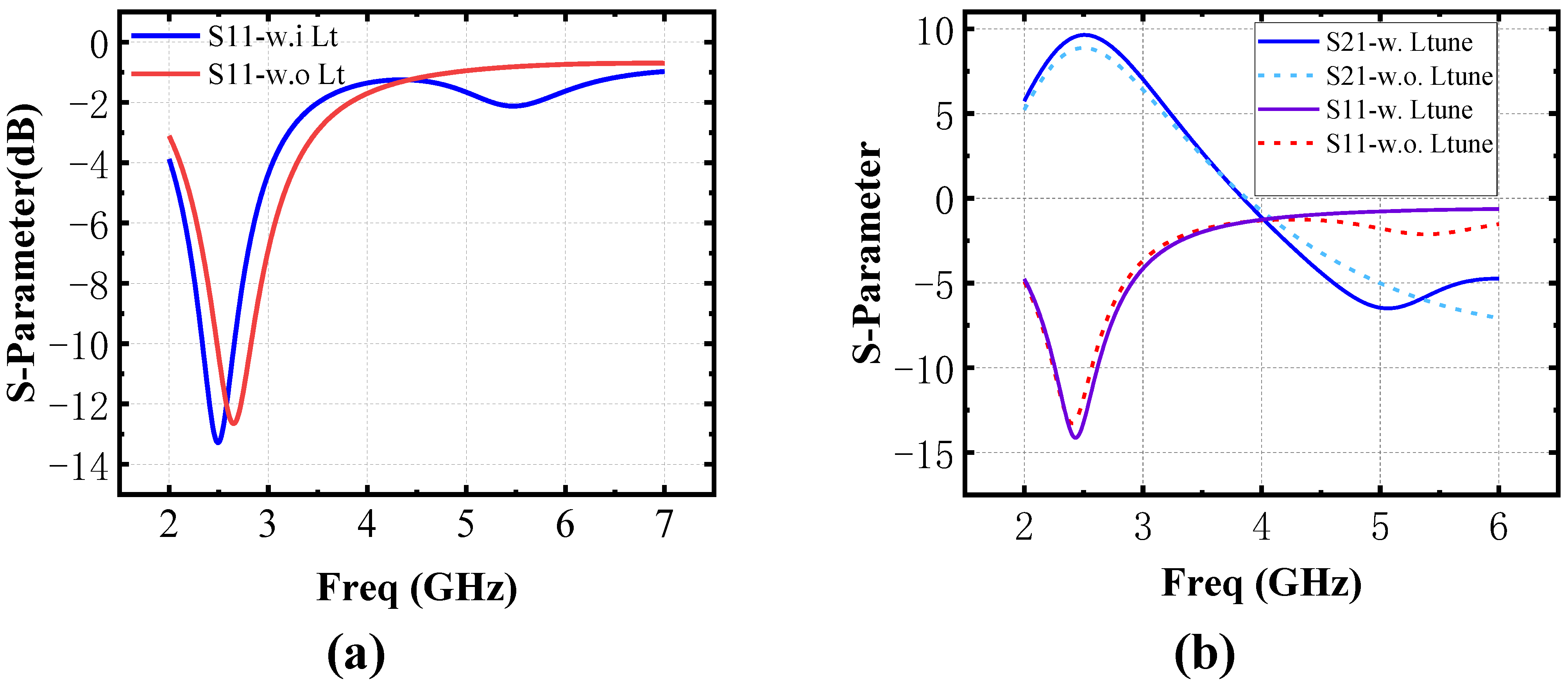

2. Design of Dual-Band Matching Networks

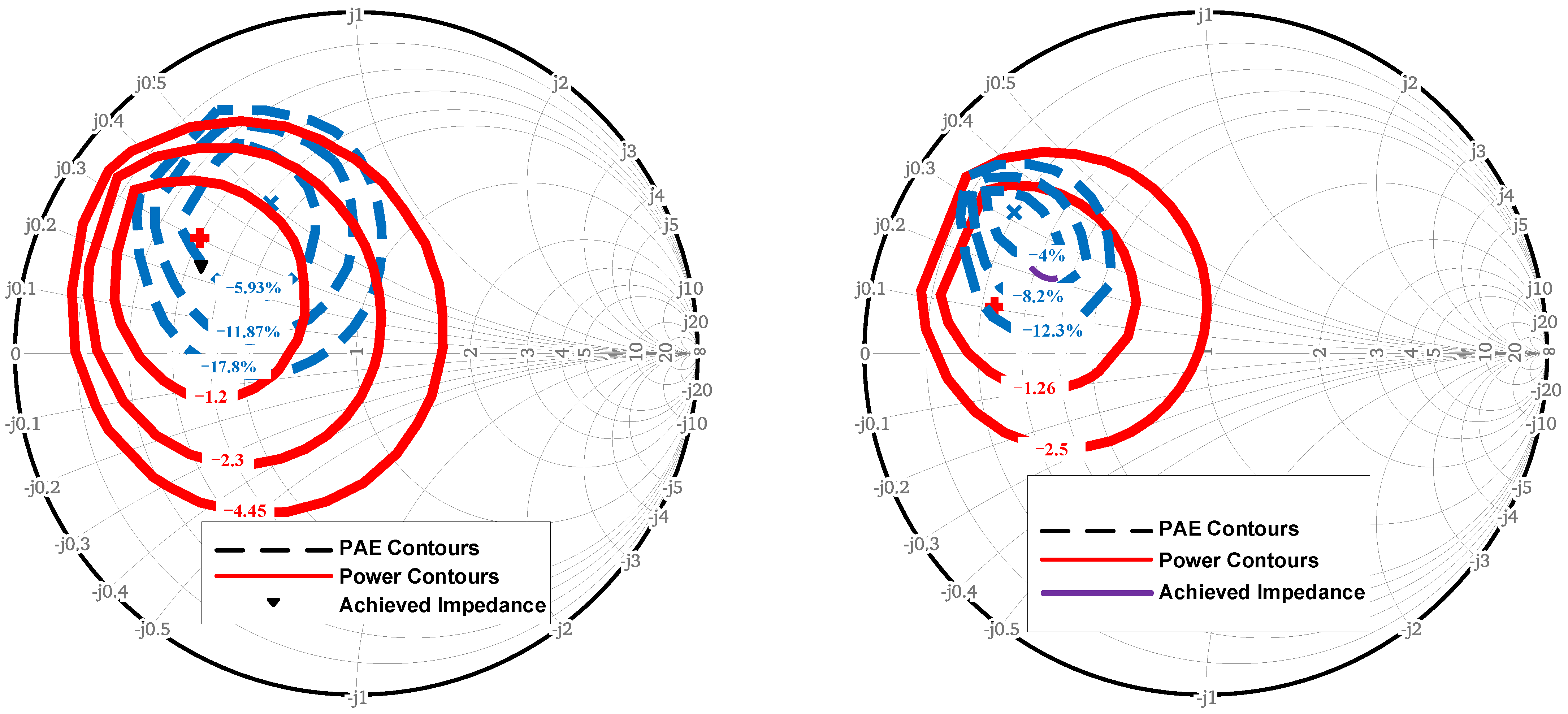

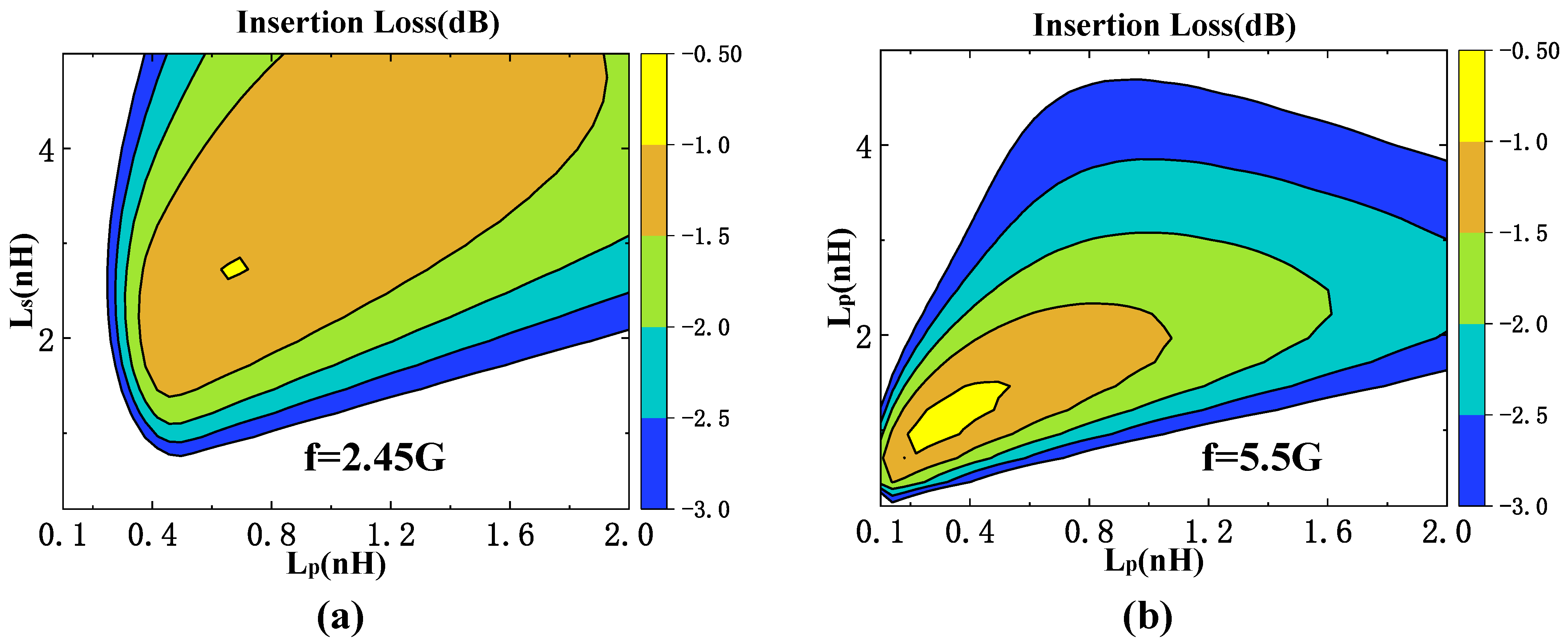

2.1. Design of Dual Band Output Matching Networks

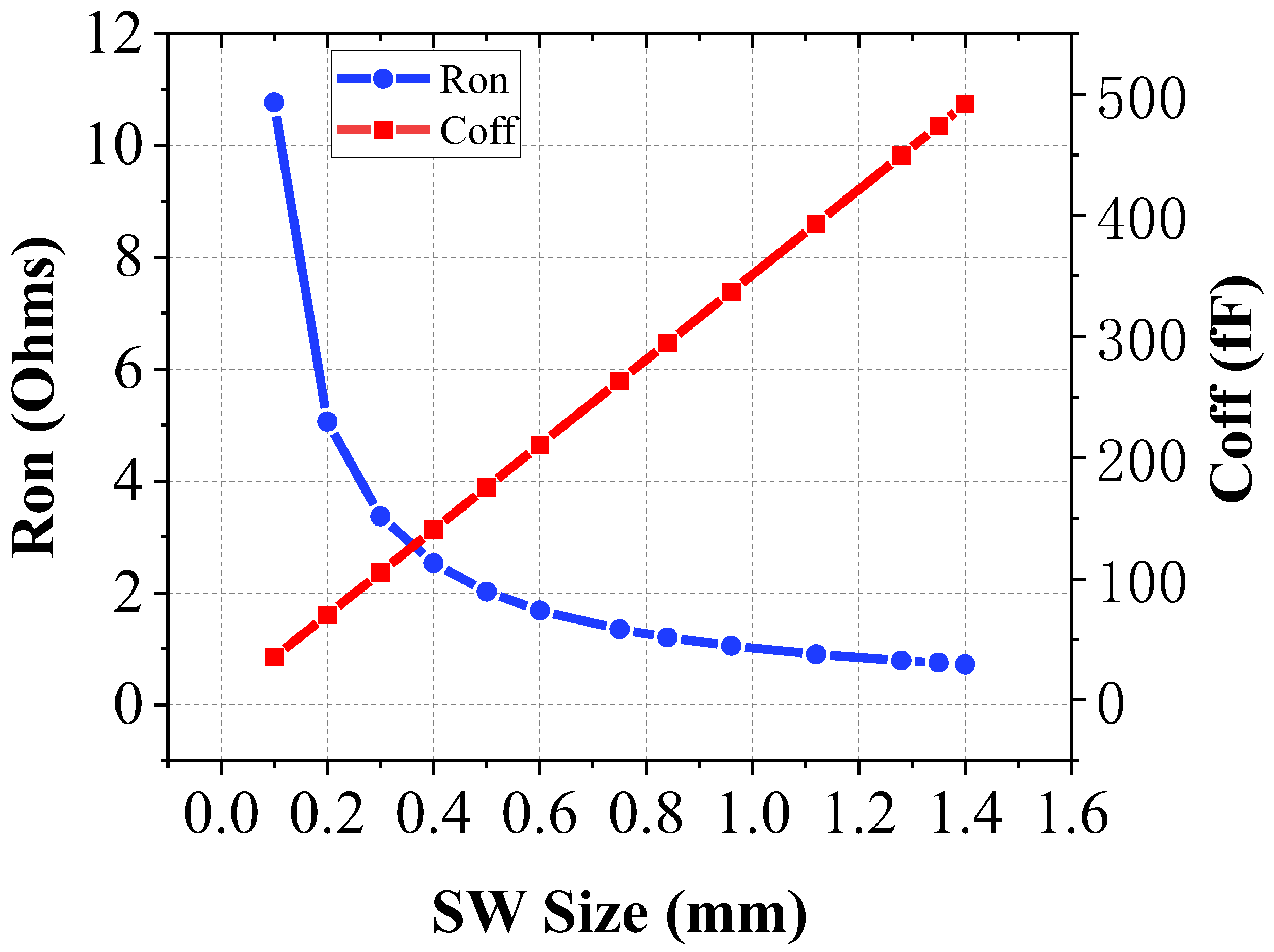

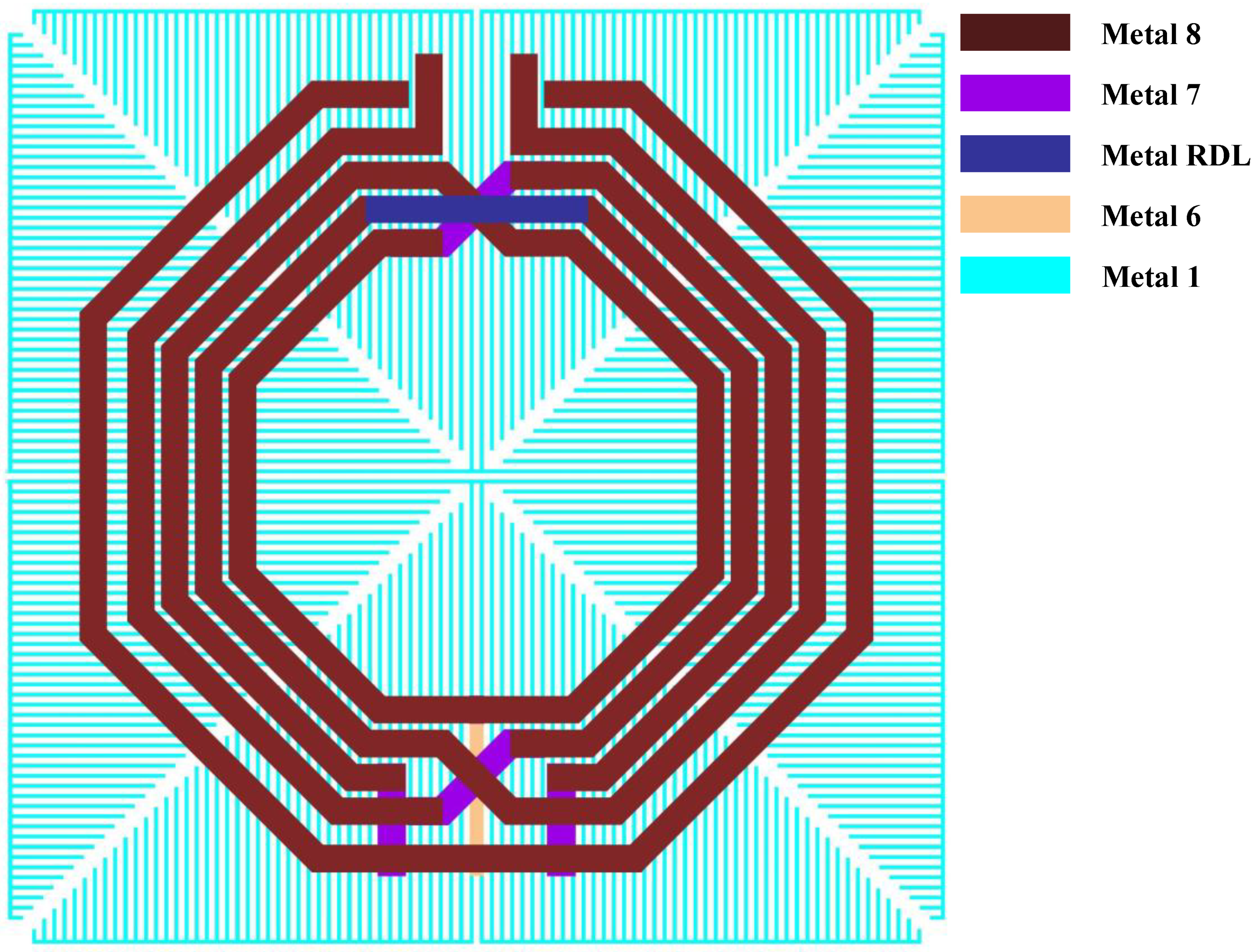

2.2. Implementation of Dual-Band Output Matching Network

2.3. Implementation of Dual-Band Input Matching Network

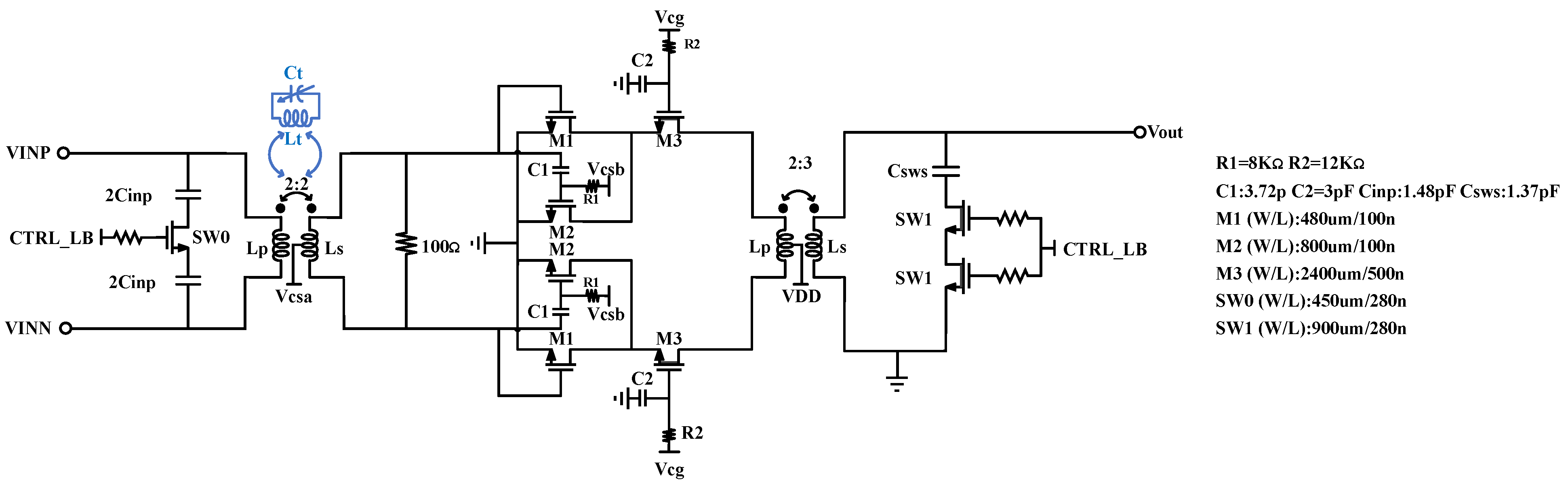

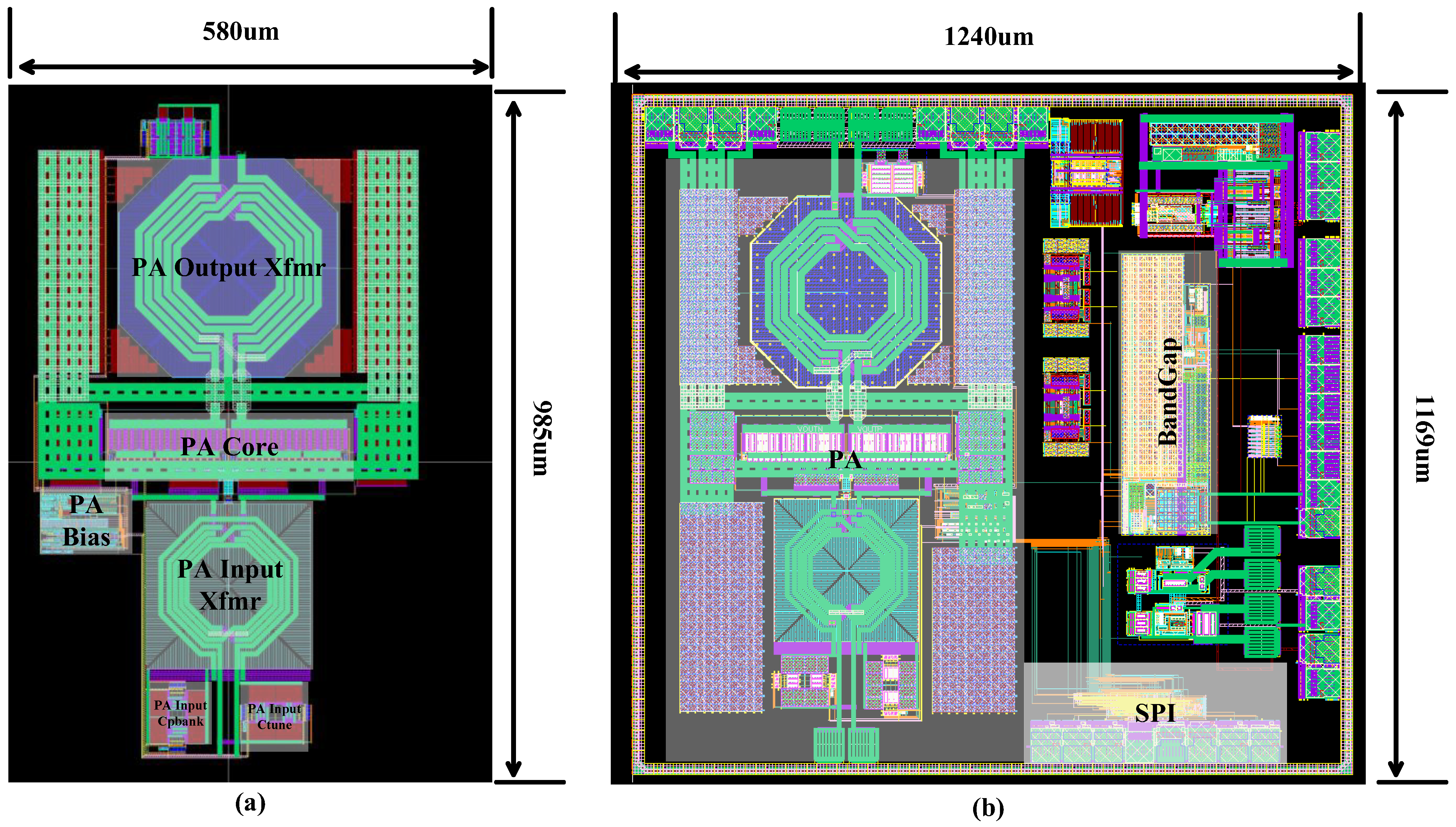

3. Circuit Implementation

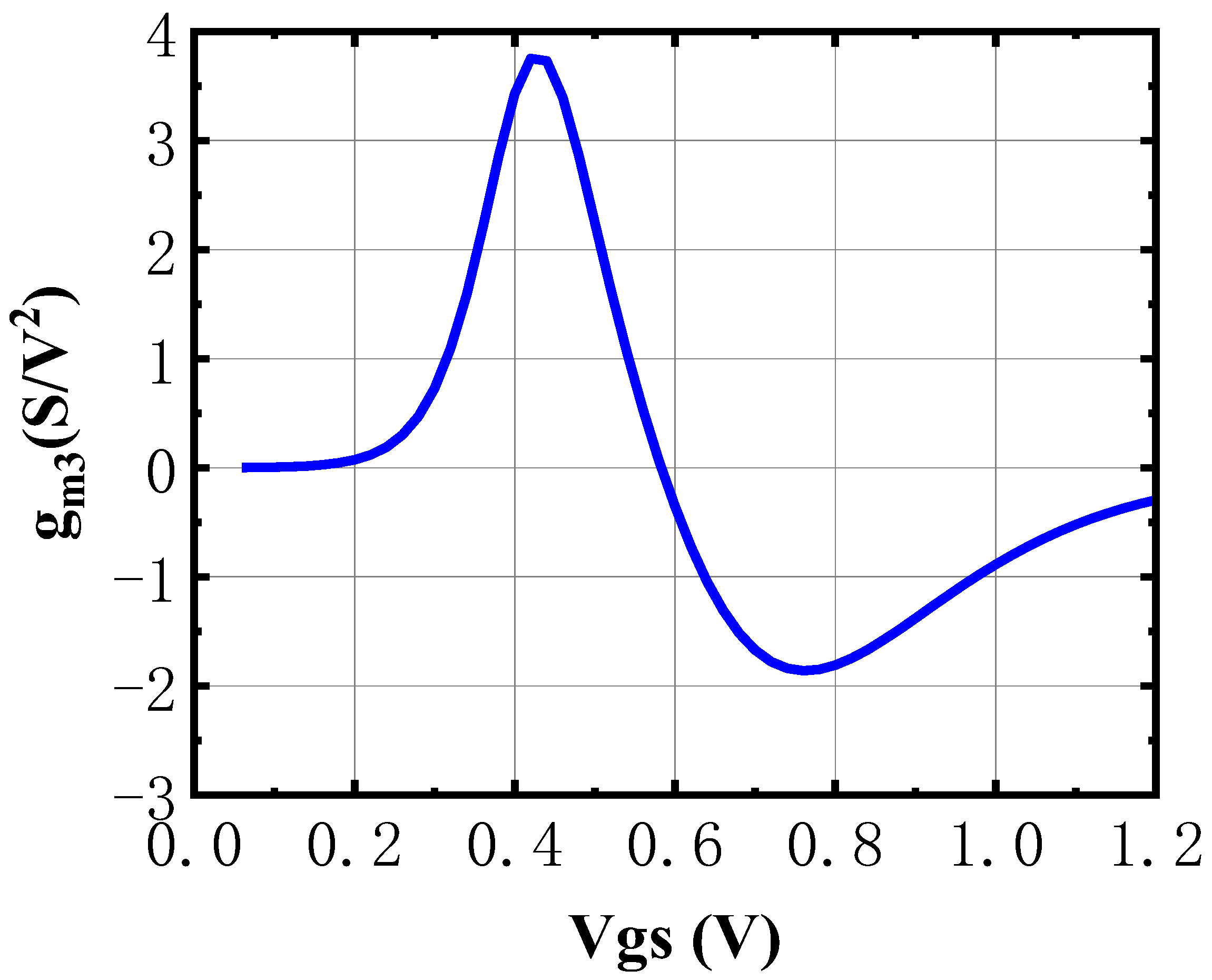

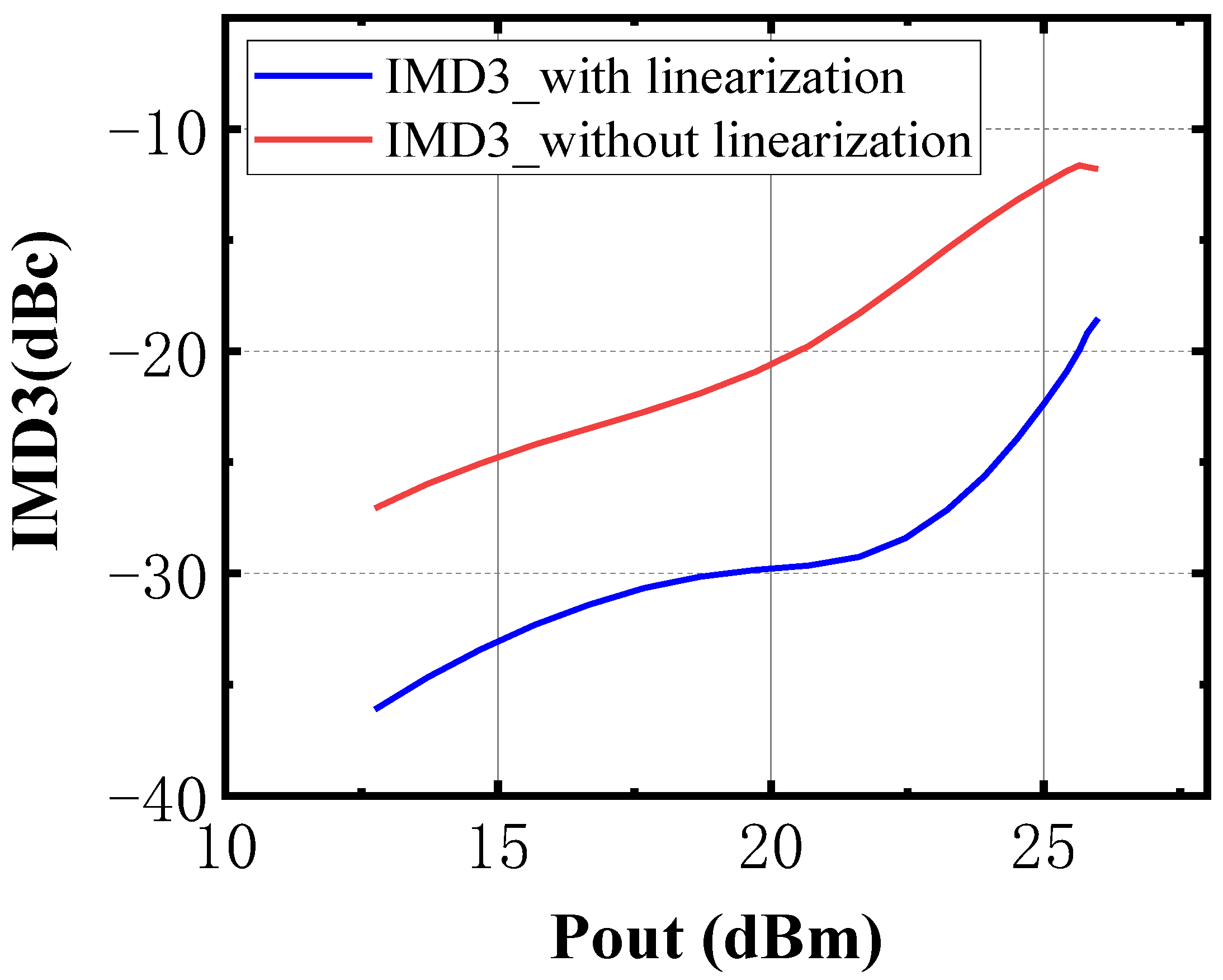

3.1. Cascode PA Power Cell

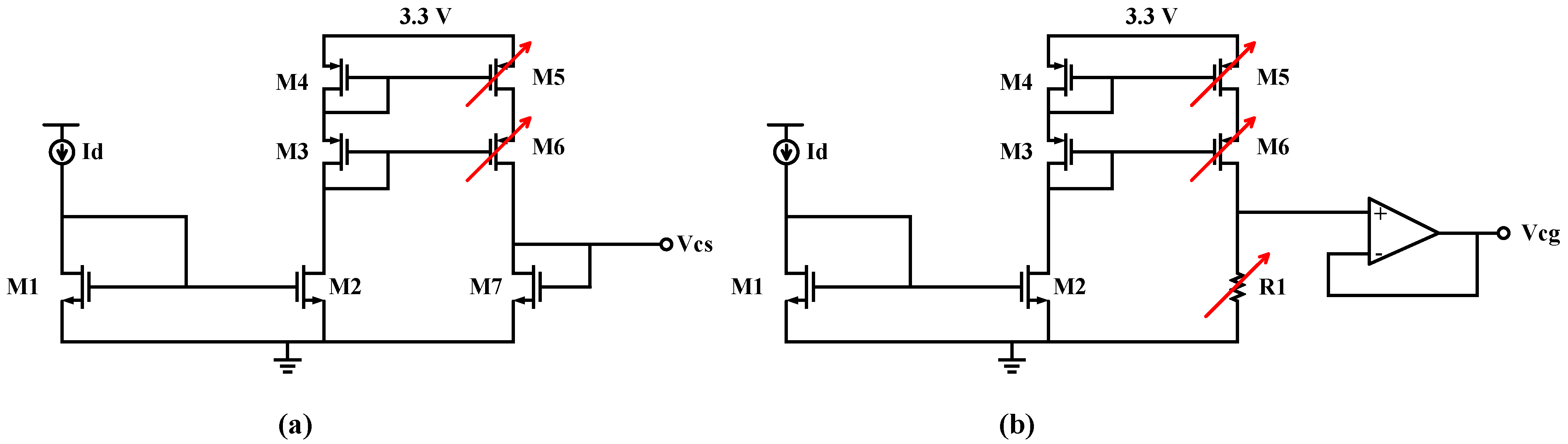

3.2. The Integrated Bias Circuit

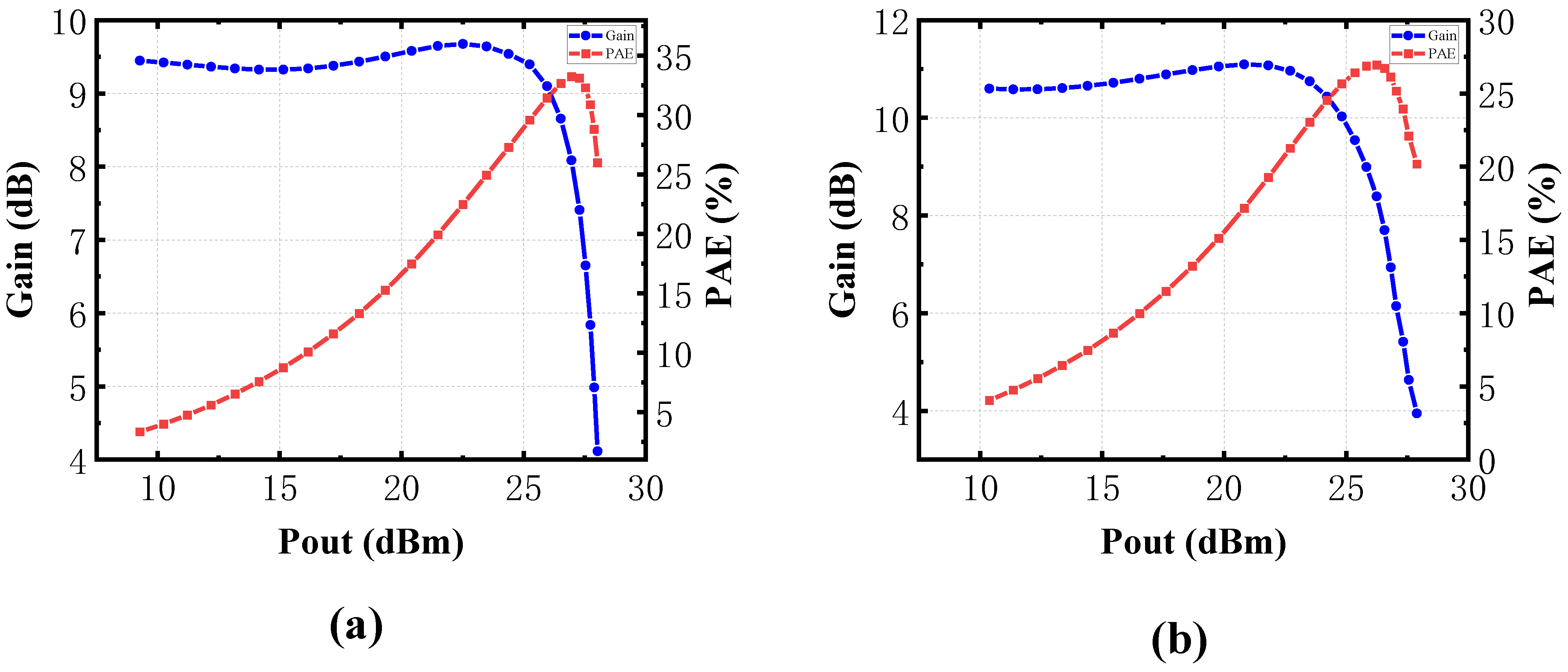

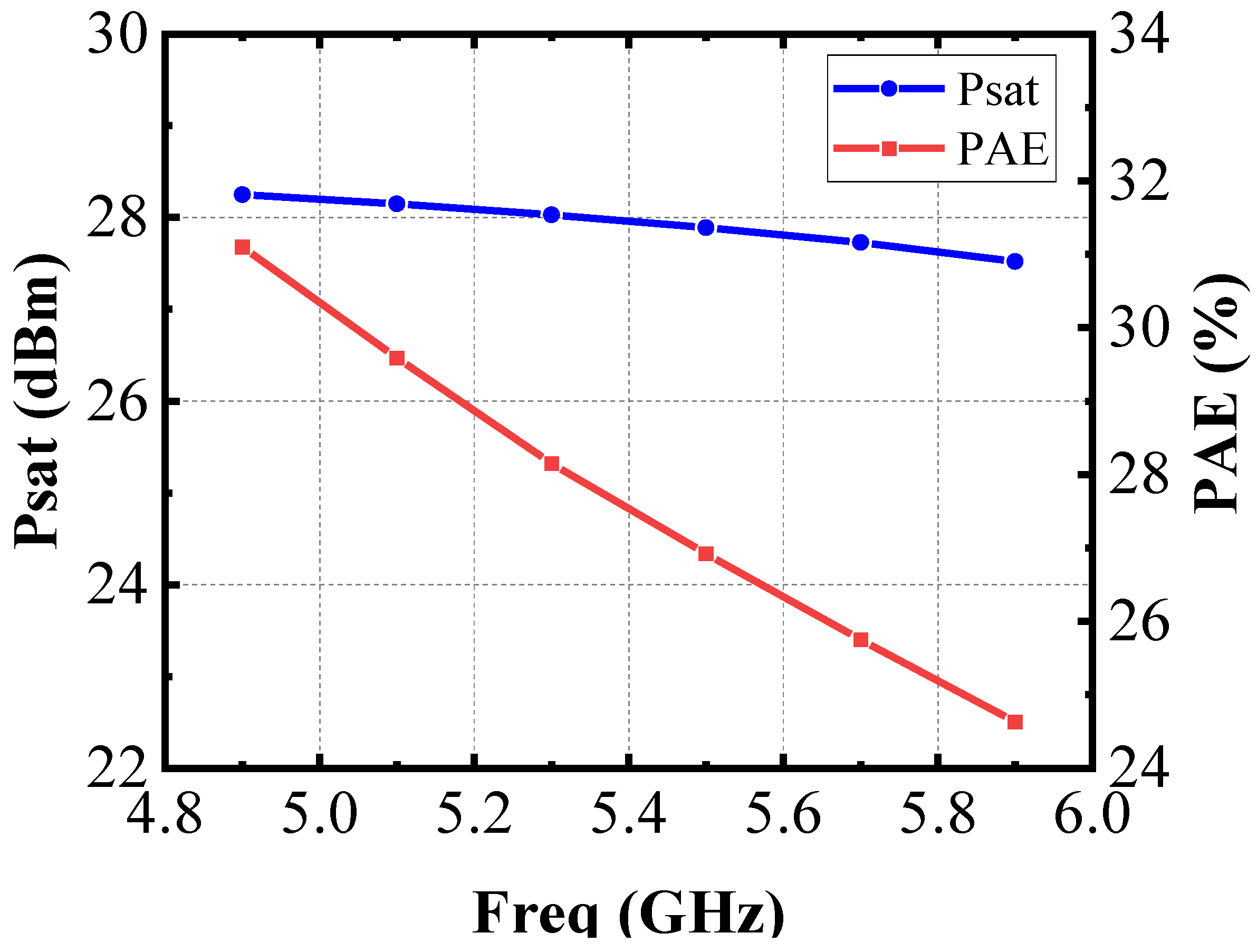

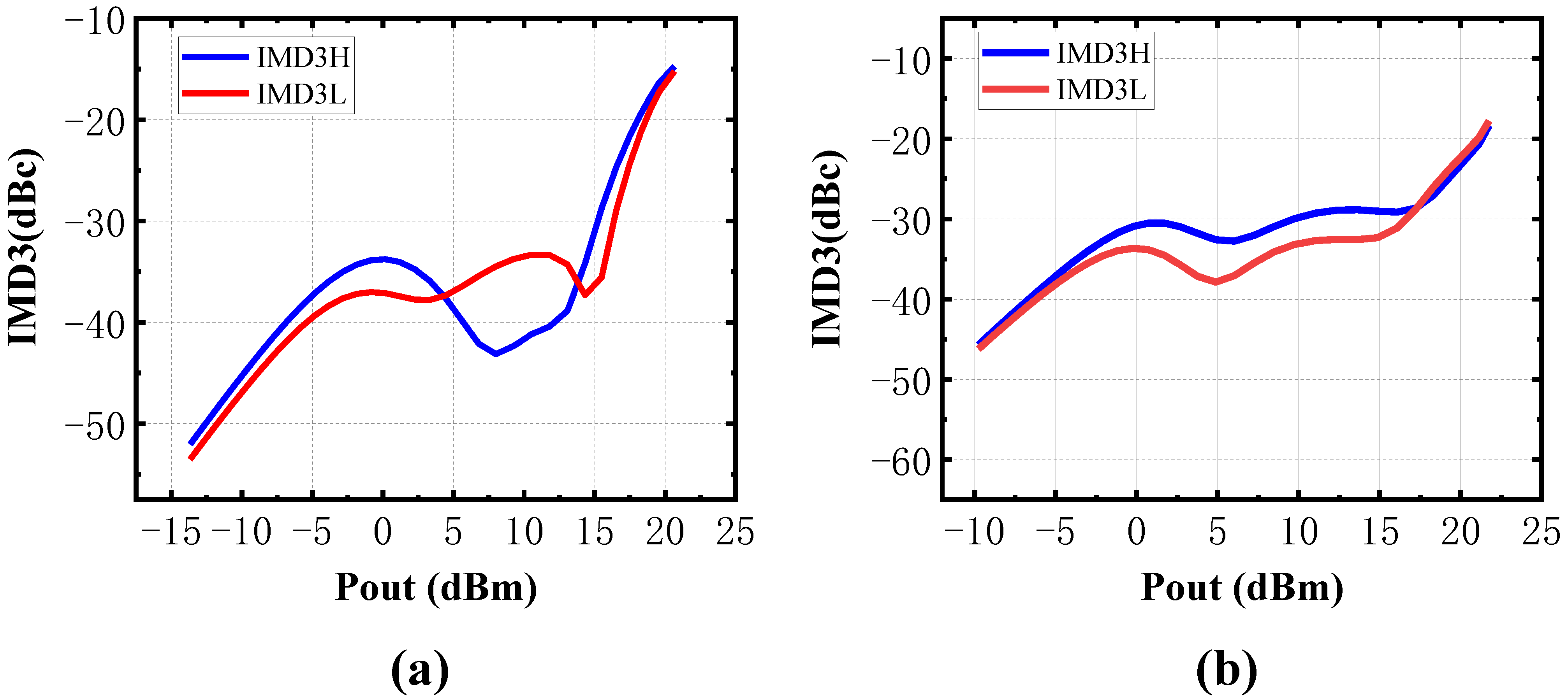

4. Simulation Results

5. Discussion

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kim, W.; Seok, H.G.; Lee, G.; Kim, S.; Lee, J.K.; Kim, C.; Kim, J. A Fully Integrated IEEE 802.15.4/4z-Compliant UWB System-on-Chip RF Transceiver Supporting Precision Positioning in a CMOS 28-nm Process. IEEE J. Solid-State Circuits 2023, 58, 3408–3420. [Google Scholar] [CrossRef]

- Lee, J.; Han, J.; Lo, C.L.; Lee, J.; Kim, W.; Kim, S.; Kang, I. NB-IoT and GNSS All-In-One System-On-Chip Integrating RF Transceiver, 23-dBm CMOS Power Amplifier, Power Management Unit, and Clock Management System for Low Cost Solution. IEEE J. Solid-State Circuits 2020, 55, 3400–3413. [Google Scholar] [CrossRef]

- Kim, N.-S. A Digital-Intensive Extended-Range Dual-Mode BLE5.0 and IEEE802.15.4 Transceiver SoC. IEEE Trans. Microw. Theory Tech. 2020, 68, 2020–2029. [Google Scholar] [CrossRef]

- Wang, D.; Liu, Z.; Tan, Y.; Xu, C.; Li, H.; Jiang, H.; Liao, H. A 2.85-mm2 Wideband RF Transceiver in 40-nm CMOS for IoT Micro-Hub Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 3930–3943. [Google Scholar] [CrossRef]

- Duan, Z.; Fang, Y.; Zhu, H.; Wu, B.; Wang, Y.; Dai, Y.; Gao, H. A S-band switchless bi-directional transceiver with a 52% fractional bandwidth in CMOS technology. Microelectron. J. 2023, 143, 106036. [Google Scholar] [CrossRef]

- Andersen, N.; Bagga, S.; Michaelsen, J.A.; Hjortland, H.A.; Leene, L.; Skår, T.; Wisland, D.T. 4.1 A 79.7μW Two-Transceiver Direct-RF 7.875GHz UWB Radar SoC in 40nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 18–22 February 2024; pp. 76–78. [Google Scholar] [CrossRef]

- Lu, C.; Chen, S.L.; Liu, J.; Bao, J.; Wang, Y.; Zhao, Y. Dual-Band 802.11ax Transceiver Design With 1024-QAM and 160-MHz CBW Support. IEEE Solid-State Circuits Lett. 2023, 6, 137–140. [Google Scholar] [CrossRef]

- Lu, E.; Li, W.K.; Deng, Z.; Rostami, E.; Wu, P.A.; Chang, K.M.; Shanaa, O. 10.4 A 4×4 Dual-Band Dual-Concurrent WiFi 802.11ax Transceiver with Integrated LNA, PA and T/R Switch Achieving +20dBm 1024-QAM MCS11 P out and −43dB EVM Floor in 55nm CMOS. In Proceedings of the IEEE Solid-state Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 16–20 February 2020. [Google Scholar] [CrossRef]

- Lee, J.; Jang, J.; Lee, W.; Suh, B.; Yoo, H.; Park, B.; Yoo, S. 4.2 A Tri-Band Dual-Concurrent Wi-Fi 802.11be Transceiver Achieving -46dB TX/RX EVM Floor at 7.1GHz for a 4K-QAM 320MHz Signal. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 18–22 February 2024. [Google Scholar] [CrossRef]

- Ben-Bassat, A.; Gross, S.; Lane, A.; Nazimov, A.; Khamaisi, B.; Solomon, E.; Degani, O. A Fully Integrated 27dBm Dual-Band All-Digital Polar Transmitter Supporting 160MHz for WiFi 6 Applications. IEEE Solid-State Circuits 2020, 55, 3414–3425. [Google Scholar] [CrossRef]

- Khamaisi, B.; Ben-Haim, D.; Nazimov, A.; Ben-Bassat, A.; Gross, S.; Shay, N.; Degani, O. A 16nm, +28dBm Dual-Band All-Digital Polar Transmitter Based on 4-core Digital PA for Wi-Fi6E Applications. In Proceedings of the IEEE Solid-state Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 20–26 February 2022. [Google Scholar] [CrossRef]

- Li, S.; Su, G.; Wang, X.; Liu, J. A 8–12 GHz power amplifier with high out-of-band rejection. Microelectron. J. 2024, 144, 106084. [Google Scholar] [CrossRef]

- Nikandish, G.R.; Staszewski, R.B.; Zhu, A. Broadband fully integrated GaN power amplifier with minmum-inductance BPF matching and two-transistors AM-PM compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 4211–4223. [Google Scholar] [CrossRef]

- Liu, B.; Boon, C.C.; Mao, M.; Choi, P.; Guo, T. A 2.4–6 GHz Broadband GaN Power Amplifier for 802.11ax Application. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2404–2417. [Google Scholar] [CrossRef]

- Nikandish, G.R.; Nasri, A.; Yousefi, A.; Zhu, A.; Staszewski, R.B. A Broadband Fully Integrated Power Amplifier Using Waveform Shaping Multi-Resonance Harmonic Matching Network. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 69, 2–15. [Google Scholar] [CrossRef]

- Meng, X.; Yu, C.; Liu, Y.; Wu, Y. Design approach for implementation of class-J broadband power amplifiers using synthesized band-pass and low pass matching topology. IEEE Trans. Microw. Theory Tech. 2017, 65, 4984–4996. [Google Scholar] [CrossRef]

- Liu, B.; Zhou, R.; Zhu, Z. Reconfigurable 2.4/5.0-GHz Dual-Band CMOS Power Amplifier for WLAN 802.11ax. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 3120–3133. [Google Scholar] [CrossRef]

- Lee, J.; Paek, J.S.; Hong, S. Millimeter-Wave Frequency Reconfigurable Dual-Band CMOS Power Amplifier for 5G Communication Radios. IEEE Trans. Microw. Theory Tech. 2021, 70, 801–812. [Google Scholar] [CrossRef]

- Ko, J.; Nam, S. A two-stage S-/X-band CMOS power amplifier for high-resolution radar transceivers. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 606–608. [Google Scholar] [CrossRef]

- Lee, M.; Park, C. A Triple-Band CMOS Power Amplifier Using Multi-Band and Switchable Matching Network for Wireless Mobile. IEEE Trans. Microw. Theory Tech. 2019, 67, 4220–4231. [Google Scholar] [CrossRef]

- Choi, H.W.; Choi, S.; Kim, C.Y. A 25-GHz Power Amplifier Using Three-Stage Antiphase Linearization in Bulk 65-nm CMOS Technology. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 489–491. [Google Scholar] [CrossRef]

- Lee, W.; Yoo, J.; Hong, S. A 28-GHz CMOS Power Amplifier Linearized by Dynamic Conductance Control and Body Carrier Injection. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 1071–1074. [Google Scholar] [CrossRef]

- Rawat, A.S.; Rajendran, J.; Mariappan, S.; Shasidharan, P.; Kumar, N.; Yarman, B.S. A 919 MHz—923 MHz, 21 dBm CMOS Power Amplifier with Bias Modulation Linearization Technique Achieving PAE of 29% for LoRa Application. IEEE Access 2022, 10, 79365–79378. [Google Scholar] [CrossRef]

- Joo, T.; Koo, B.; Hong, S. A WLAN RF CMOS PA with large-signal MGTR method. IEEE Trans. Microw. Theory Tech. 2013, 61, 1272–1279. [Google Scholar] [CrossRef]

- Pozar, D.M. Microwave Engineering; Wiley: Hoboken, NJ, USA, 2006. [Google Scholar]

- Trinh, V.S.; Park, J.D. Theory and Design of Impedance Matching Network Utilizing a Lossy On-Chip Transformer. IEEE Access 2019, 7, 140980–140989. [Google Scholar] [CrossRef]

- Yoon, Y.; Kim, H.; Park, Y.; Ahn, M.; Lee, C.H.; Laskar, J. A high power and highly linear CMOS switched capacitor. IEEE Microw. Wirel. Compon. Lett. 2010, 20, 619–621. [Google Scholar] [CrossRef]

- Liu, B.; Quan, X.; Boon, C.C.; Khanna, D.; Choi, P.; Yi, X. Reconfigurable 2.4-/5-GHz Dual-Band Transmitter Front-End Supporting 1024-QAM for WLAN 802.11ax Application in 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2020, 68, 4018–4030. [Google Scholar] [CrossRef]

- Singh, R.; Paramesh, J. A digitally-tuned triple-band transformer power combiner for CMOS power amplifiers. In Proceeding of the IEEE Radio Frequency Integrated Circuits Symposium, Honolulu, HI, USA, 4–6 June 2017; pp. 332–335. [Google Scholar] [CrossRef]

- Zhai, C.; Liu, H.Y.; Cheng, K.K.M. Single-Chip CMOS Reconfigurable Dual Band Tri-Mode High-Efficiency RF Amplifier Design. IEEE Trans. Circuits Syst. II Express Briefs 2020, 68, 868–872. [Google Scholar] [CrossRef]

- Lin, W.J.; Huang, P.S.; Cheng, J.H.; Tsai, J.H.; Alsuraisry, H.; Huang, T.W. A dual-band class-E power amplifier with concurrent matching network in 0.18-mu m CMOS. Microw. Opt. Technol. Lett. 2018, 60, 1672–1675. [Google Scholar] [CrossRef]

| Inductance | Quality Factor (Q) | Coupling Coefficient (k) | |

|---|---|---|---|

| 1.49 nH | 16.33 | 0.75 | |

| 2.83 nH | 19.39 |

| SW-Off | SW-On | ||

|---|---|---|---|

| 1.03 nH | 1.15 nH | ||

| 8.39 | 7.55 | ||

| 877.15 pH | 936.65 pH | ||

| 9.56 | 9.21 | ||

| k | 0.76 | k | 0.77 |

| This Work *** | [17] ** | [28] ** | [29] ** | [30] ** | [31] ** | |

|---|---|---|---|---|---|---|

| Freq (GHz) | 2.4/4.9–5.9 | 2.4/5–6 | 2.4/4.9–5.9 | 2.5/3/3.5 | 1.8/2.6 | 2.4/5 |

| Bandwidth (−3 dB) | 2.06–3.04/3.15–6.6 | 2.1–2.8/4–6 * | 2.2–3.2/3.8–6.5 * | 2.2–2.8/2.8–3.6/3.1–4.1 * | N. A | 2–5 * |

| Gain (dB) | 9.45/11.48–10.03 | 14/18–16 | 9.2/11.3–11.9 | ~15 | 10–11 * | 12.3/8.4 |

| (dBm) | 28.03/27.5–28.2 | 25.4/24.4–24.8 | 23/21.9–22.4 | 22.5/21.5 | 26.2/23.1 | 21.5/21.4 |

| PAE (%) | 33.25/24.6–31.1 | 25/20.8–27.3 | 27/24.2–28.2 | 16.5/15(DE) | 32.2/31.8 | 38.4/31 |

| VDD (V) | 3.3 | 2.5 | 2.5 | 1.2 | 3.3 | 3.6 |

| 0.57 | 1.14 | 0.72 | 2.97 | 1.4 | 0.5 | |

| Technology | 55 nm | 40 nm | 40 nm | 65 nm | 0.35 µm | 0.18 µm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shen, H.; Wu, B. A Fully Integrated High Linearity CMOS Dual-Band Power Amplifier for WLAN Applications in 55-Nm CMOS. Appl. Sci. 2024, 14, 10768. https://doi.org/10.3390/app142310768

Shen H, Wu B. A Fully Integrated High Linearity CMOS Dual-Band Power Amplifier for WLAN Applications in 55-Nm CMOS. Applied Sciences. 2024; 14(23):10768. https://doi.org/10.3390/app142310768

Chicago/Turabian StyleShen, Haoyu, and Bin Wu. 2024. "A Fully Integrated High Linearity CMOS Dual-Band Power Amplifier for WLAN Applications in 55-Nm CMOS" Applied Sciences 14, no. 23: 10768. https://doi.org/10.3390/app142310768

APA StyleShen, H., & Wu, B. (2024). A Fully Integrated High Linearity CMOS Dual-Band Power Amplifier for WLAN Applications in 55-Nm CMOS. Applied Sciences, 14(23), 10768. https://doi.org/10.3390/app142310768