Comparison of Cobalt Integration with Various Dielectric Materials under Thermal and Electrical Stress

Abstract

:1. Introduction

2. Experimental Details

2.1. Sample Preparation

2.2. Sample Characterization

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kriz, J.; Angelkort, C.; Czekalla, M.; Huth, S.; Meinhold, D.; Pohl, A.; Schulte, S.; Thamm, A.; Wallace, S. Overview of dual damascene integration schemes in Cu BEOL integration. Microelectron. Eng. 2008, 85, 2128–2132. [Google Scholar] [CrossRef]

- Murarka, S.P. Low dielectric constant material for interlayer dielectric applications. Solid State Technol. 1996, 3, 83–88. [Google Scholar]

- Maex, K.; Baklanov, M.R.; Shamiryan, D.; Iacopi, F.; Brongersma, S.H.; Yanovitskaya, Z.S. Low dielectric constant materials for microelectronics. J. Appl. Phys. 2003, 93, 8793–8841. [Google Scholar] [CrossRef]

- Grill, A.; Gates, S.M.; Ryan, T.E.; Nguyen, S.V.; Priyadarshini, D. Progress in the development and understanding of advanced low k and ultralow k dielectrics for very large-scale integrated interconnects—State of the art. Appl. Phys. Rev. 2014, 1, 011306. [Google Scholar] [CrossRef]

- Croes, K.; Wilson, C.J.; Lofrano, M.; Beyer, G.P.; Tokei, Z. Interconnect reliability—A study of the effect of dimensional and porosity scaling. Microelectron. Eng. 2011, 88, 614–619. [Google Scholar] [CrossRef]

- Lionti, K.; Volksen, W.; Magbitang, T.; Darnon, M.; Dubois, G. Toward Successful Integration of Porous Low-k Materials: Strategies Addressing Plasma Damage. ECS J. Solid State Sci. Technol. 2015, 4, N3071. [Google Scholar] [CrossRef]

- Grill, A. Porous pSiCOH ultralow-k dielectrics for chip interconnects prepared by PECVD. Annu. Rev. Mater. Res. 2009, 39, 49–69. [Google Scholar] [CrossRef]

- Havemann, R.H.; Antonelli, G.A.; Arendt, G.K.; Danek, M.; McKerrow, A.J.; Weinberg, R.S. Copper BEOL solutions for advanced memory. Solid State Technol. 2009, 31, 10–15. [Google Scholar]

- Schuegraf, K.; Abraham, M.C.; Brand, A.; Naik, M.; Thakur, R. Semiconductor logic technology innovation to achieve sub-10 nm manufacturing. IEEE J. Electron Devices Soc. 2013, 1, 66–75. [Google Scholar] [CrossRef]

- Dutta, S.; Beyne, S.; Gupta, A.; Kundu, S.; Van Elshocht, S.; Bender, H.; Jamieson, G.; Vandervorst, W.; Bommels, J.; Wilson, C.J.; et al. Sub-100 nm2 Cobalt Interconnects. IEEE Electron Device Lett. 2018, 39, 731–734. [Google Scholar] [CrossRef]

- Wu, K.C.; Tseng, J.Y.; Chen, W.J. Electroplated Ru and RuCo films as a copper diffusion barrier. Appl. Surf. Sci. 2020, 516, 146139. [Google Scholar] [CrossRef]

- Steinhogl, W.; Schindler, G.; Steinlesberger, G.; Traving, M.; Engelhardt, M. Comprehensive study of the resistivity of copper wires with lateral dimensions of 100 nm and smaller. J. Appl. Phys. 2005, 97, 0237061. [Google Scholar] [CrossRef]

- Gall, D. Electron mean free path in elemental metals electron mean free path in elemental metals. J. Appl. Phys. 2016, 119, 085101. [Google Scholar] [CrossRef]

- Wislicenus, M.; Liske, R.; Gerlich, L.; Vasilev, B.; Preusse, A. Cobalt advanced barrier metallization: A resistivity composition analysis. Microelectron. Eng. 2015, 137, 11–15. [Google Scholar] [CrossRef]

- Zheng, J.-F.; Chen, P.; Baum, T.H.; Lieten, R.R.; Hunks, W.; Lippy, S.; Frye, A.; Li, W.; O’Neill, J.; Xu, J.; et al. Selective co growth on cu for void-free via fill. In Proceedings of the IEEE Interconnect Technology Conference/Materials for Advanced Metallization Conference (IITC/MAM), Grenoble, France, 18–21 May 2015; pp. 265–267. [Google Scholar]

- Hosseini, M.; Ando, D.; Sutou, Y.; Koike, J. Co and CoTix for contact plug and barrier layer in integrated circuits. Microelectron. Eng. 2018, 189, 78–84. [Google Scholar] [CrossRef]

- Chen, F.; Gardner, D. Influence of line dimensions on the resistance of Cu interconnections. IEEE Electron Device Lett. 1998, 19, 508–510. [Google Scholar] [CrossRef]

- He, M.; Zhang, X.; Nogami, T.; Lin, X.; Kelly, J.; Kim, H.; Spooner, T.; Edelstein, D.; Zhao, L. Mechanism of Co Liner as enhancement layer for Cu interconnect gap-fill. J. Electrochem. Soc. 2013, 160, D3040. [Google Scholar] [CrossRef]

- Yang, C.-C.; Spooner, T.; Ponoth, S.; Chanda, K.; Simon, A.; Lavoie, C.; Lane, M.; Hu, C.-K.; Liniger, E.; Gignac, L.; et al. Physical, Electrical, and Reliability Characterization of Ru for Cu Interconnects. In Proceedings of the 2006 IEEE International Interconnect Technology Conference, Burlingame, CA, USA, 5–7 June 2006; pp. 187–190. [Google Scholar]

- Dutta, S.; Kundu, S.; Gupta, A.; Jamieson, G.; Granados, J.F.; Bommels, J.; Wilson, C.J.; Tőkei, Z.; Adelmann, C. Highly scaled ruthenium interconnects. IEEE Electron Device Lett. 2017, 38, 949–951. [Google Scholar] [CrossRef]

- Pedreira, O.V.; Croes, K.; Leśniewska, A.; Wu, C.; Van Der Veen, M.H.; de Messemaeker, J.; Vandersmissen, K.; Jourdan, N.; Wen, L.G.; Adelmann, C.; et al. Reliability study on cobalt and ruthenium as alternative metals for advanced interconnects. In Proceedings of the IEEE International Interconnect Technology Conference, San Jose, CA, USA, 20–23 May 2014; pp. 173–176. [Google Scholar]

- Tierno, D.; Pedreira, O.V.; Wu, C.; Jourdan, N.; Kljucar, L.; Tőkei, Z.; Croes, K. Cobalt and Ruthenium drift in ultra-thin oxides. Microelectron. Reliab. 2019, 100–101, 113407. [Google Scholar] [CrossRef]

- Cheng, Y.L.; Lee, C.Y.; Huang, J.W.; Chen, G.S.; Fang, J.S. Comparison of various low dielectric constant materials. Thin Solid Films 2018, 660, 871–878. [Google Scholar] [CrossRef]

- Cheng, Y.L.; Lee, C.Y.; Hung, W.J.; Chen, G.S.; Fang, J.S. Electrical and reliability characteristics of dielectric stack with low dielectric constant SiCOH and capping SiCNH films. Surf. Coat. Technol. 2018, 350, 57–63. [Google Scholar] [CrossRef]

- Zhao, L.; Volders, H.; Baklanov, M.; Tokei, Z.; Pantouvaki, M.; Wilson, C.J.; Besien, E.V.; Beyer, G.P.; Claeys, C. Study of metal barrier deposition-induced damage to porous low-k materials. Microelectron. Eng. 2011, 88, 3030–3034. [Google Scholar] [CrossRef]

- Kaloyeros, A.E.; Eisenbraun, E. Ultrathin diffusion barriers/liners for gigascale copper metallization. Annu. Rev. Mater. Sci. 2000, 30, 363–385. [Google Scholar] [CrossRef]

- Baklanov, M.R.; de Marneffe, J.-F.; Shamiryan, D.; Urbanowicz, A.M.; Shi, H.; Rakhimova, T.V.; Huang, H.; Ho, P.S. Plasma processing of low-k dielectrics. J. Appl. Phys. 2013, 113, 041101. [Google Scholar] [CrossRef]

- He, M.; Lu, T.-M. Metal-Dielectric Interfaces in Gigascale Electronics: Thermal and Electrical Stability; Springer Series in Materials Science; Springer: New York, NY, USA, 2012; Volume 157. [Google Scholar]

- Hosseini, M.; Koike, J. Amorphous CoTix as a liner/diffusion barrier material for advanced copper metallization. J. Alloys Compd. 2017, 721, 134–142. [Google Scholar] [CrossRef]

- Cheng, Y.L.; Huang, H.C.; Lee, C.Y.; Chen, G.S.; Fang, J.S. Comparison of Cu and Co Integration with Porous Low-k SiOCH Dielectrics. Thin Solid Films 2020, 704, 138010. [Google Scholar] [CrossRef]

- Tang, B.J.; Croes, K.; Barbarin, Y.; Wang, Y.Q.; Degraeve, R.; Li, Y.; Toledano-Luque, M.; Kauerauf, T.; Bommels, J.; Tokei, Z.; et al. As-grown donor-like traps in low-k dielectrics and their impact on intrinsic TDDB reliability. Microelectron. Reliab. 2014, 54, 1675–1679. [Google Scholar] [CrossRef]

- Chang, Y.M.; Chang, W.Y.; Leu, J.; Cheng, Y.L. Effect of thermal treatment on physical, electrical properties and reliability of porogen-containing and porogen-free ultralow-k dielectric. Thin Solid Films 2013, 528, 67–71. [Google Scholar] [CrossRef]

- Huang, H.; McLaughin, P.S.; Kelly, J.J.; Yang, C.-C.; Southwick, R.G.; Wang, M.; Bonilla, G.; Karve, G. Time dependent dielectric breakdown of cobalt and ruthenium interconnects at 36nm pitch. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; pp. 1–5. [Google Scholar]

- Zhao, L.; Volders, H.; Baklanov, M.; Tokei, Z.; Pantouvaki, M.; Wilson, C.J.; Besien, E.V.; Beyer, G.P.; Claeys, C. Impact of carbon-doping on time dependent dielectric breakdown of SiO2-based films. Appl. Phys. Lett. 2015, 106, 072902. [Google Scholar] [CrossRef]

- Mcpherson, J.W. Time dependent dielectric breakdown physics-Models revisited. Microelectron. Reliab. 2012, 52, 1753–1760. [Google Scholar] [CrossRef]

- Wu, E.Y.; Sune, J.; Vollertsen, R.P. Comprehensive physics-based breakdown model for reliability assessment of oxides with thickness ranging from 1 nm up to 12 nm. In Proceedings of the 2009 IEEE International Reliability Physics Symposium, Montreal, QC, Canada, 26-30 April 2009; pp. 708–717. [Google Scholar]

- Zhao, L.; Pantouvaki, M.; Croes, K.; Tőkei, Z.; Barbarin, Y.; Wilson, C.J.; Baklanov, M.R.; Beyer, G.P.; Claeys, C. Role of copper in time dependent dielectric breakdown of porous organo-silicate glass low-k materials. Appl. Phys. Lett. 2011, 99, 222110. [Google Scholar] [CrossRef]

- Fisher, I.; Eizenberg, M. Copper ion diffusion in porous and nonporous SiO2-based dielectrics using bias thermal stress and thermal stress tests. Thin Solid Films 2008, 516, 4111–4121. [Google Scholar] [CrossRef]

| Sample | Deposition Method | Precursor | UV Curing | Dielectric Constant (k) | Leakage Current Density at 1 MV/cm (×10−12A/cm2) | Breakdown Filed at 25 °C (MV/cm) | Porosity (%) | Pore Size (nm) |

|---|---|---|---|---|---|---|---|---|

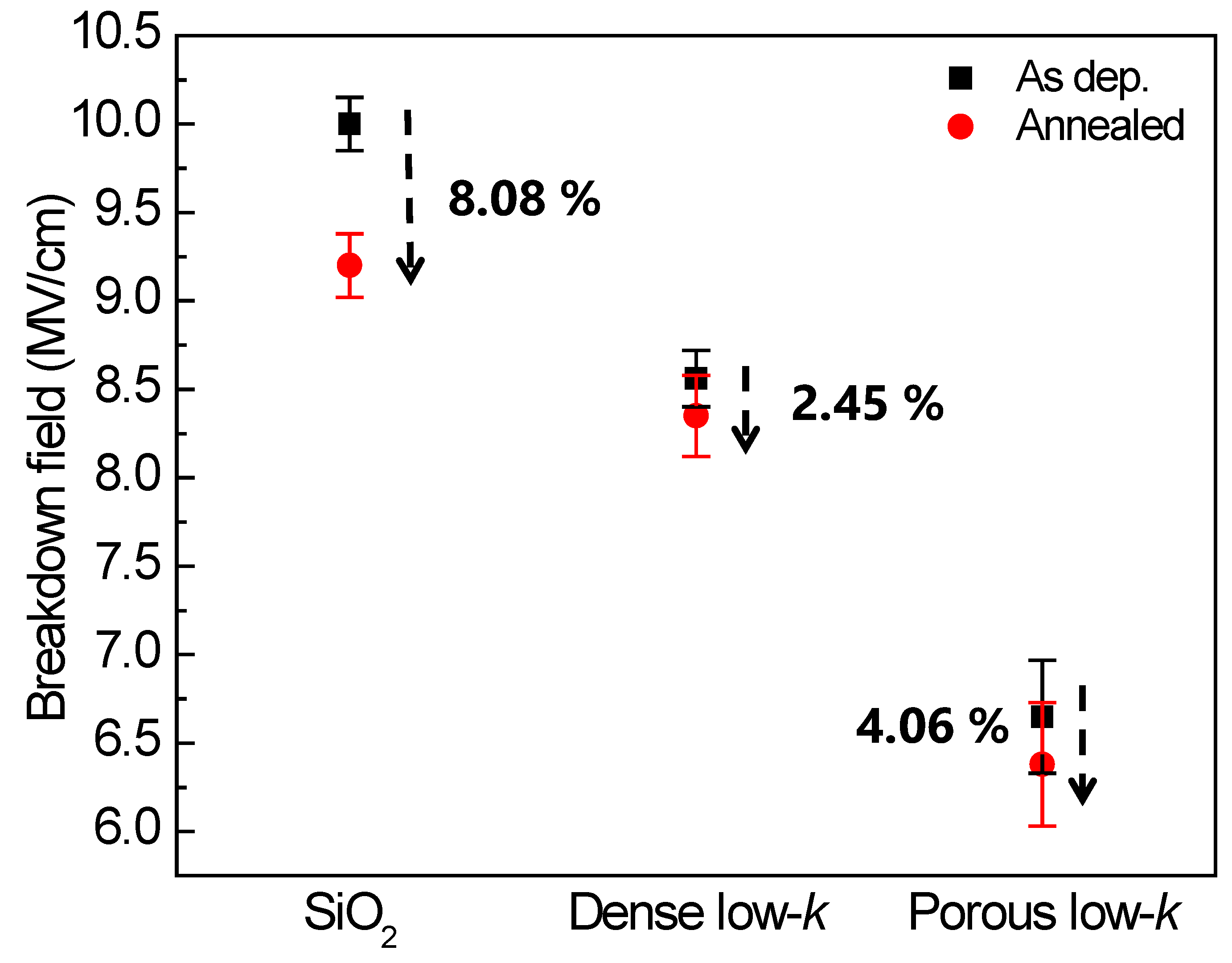

| SiO2 | Dry oxidation | O2 | No | 4.02 ± 0.03 | 2.46 ± 0.35 | 9.98 ± 0.15 | N/D | N/D |

| Dense low-k | PECVD | DEMS + O2 | No | 3.02 ± 0.05 | 5.66 ± 0.7 | 8.56 ±0.16 | N/D | N/D |

| Porous low-k | PECVD | DEMS + O2 + ATRP | Yes | 2.56 ± 0.08 | 2.69 ± 0.33 | 6.67 ± 0.30 | 15 | 1.35 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cheng, Y.-L.; Huang, H.-C.; Peng, W.-F.; Chen, G.-S.; Fang, J.-S. Comparison of Cobalt Integration with Various Dielectric Materials under Thermal and Electrical Stress. Coatings 2023, 13, 1818. https://doi.org/10.3390/coatings13101818

Cheng Y-L, Huang H-C, Peng W-F, Chen G-S, Fang J-S. Comparison of Cobalt Integration with Various Dielectric Materials under Thermal and Electrical Stress. Coatings. 2023; 13(10):1818. https://doi.org/10.3390/coatings13101818

Chicago/Turabian StyleCheng, Yi-Lung, Hong-Chang Huang, Wei-Fan Peng, Giin-Shan Chen, and Jau-Shiung Fang. 2023. "Comparison of Cobalt Integration with Various Dielectric Materials under Thermal and Electrical Stress" Coatings 13, no. 10: 1818. https://doi.org/10.3390/coatings13101818