High-Rate Epitaxial Growth of Silicon Using Electron Beam Evaporation at High Temperatures

Abstract

1. Introduction

2. Materials and Methods

2.1. High-Temperature Electron Beam Evaporation

2.2. Characterization

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Syvertsen, M.; Halvorsen, T.; Mørk, K.; Nordmark, A.; Kaden, T.; Ulyashin, A. Remelting and Purification of Si-Kerf for PV Wafers. In Proceedings of the 33rd European Photovoltaic Solar Energy Conference and Exhibition, Amsterdam, The Netherlands, 25–29 September 2017; pp. 1882–1885. [Google Scholar] [CrossRef]

- Van Mierlo, F.; Jonczyk, R.; Qian, V. Next Generation Direct Wafer® Technology Delivers Low Cost, High Performance to Silicon Wafer Industry. Energy Procedia 2017, 130, 2–6. [Google Scholar] [CrossRef]

- Bruel, M.; Aspar, B.; Auberton-Hervé, A.-J. Smart-Cut: A New Silicon on Insulator Material Technology Based on Hydrogen Implantation and Wafer Bonding. Jpn. J. Appl. Phys. Part 1 Regul. Pap. Short Notes Rev. Pap. 1997, 36, 1636–1641. [Google Scholar] [CrossRef]

- Tanielian, M.; Blackstone, S.; Lajos, R. A New Technique of Forming Thin Free Standing Single-Crystal Films. J. Electrochem. Soc. 1985, 132, 507. [Google Scholar] [CrossRef]

- Solanki, C.S.; Carnel, L.; Van Nieuwenhuysen, K.; Ulyashin, A.; Posthuma, N.; Beaucarne, G.; Poortmans, J. Thin-Film Free-Standing Monocrystalline Si Solar Cells with Heterojunction Emitter. Prog. Photovolt. Res. Appl. 2005, 13, 201–208. [Google Scholar] [CrossRef]

- LaBelle, H.E., Jr.; Mlavsky, A.I. Growth of Controlled Profile Crystals from the Melt: Part I—Sapphire Filaments. Mater. Res. Bull. 1971, 6, 571–579. [Google Scholar] [CrossRef]

- Assaf, H.; Ntsoenzok, E. Transfer of Thin Silicon Layers by MeV Hydrogen Implantation. Nucl. Instrum. Methods Phys. Res. Sect. B 2005, 240, 183–187. [Google Scholar] [CrossRef]

- Kuisseu, P.S.P.; Pingault, T.; Ntsoenzok, E.; Regula, G.; Mazen, F.; Sauldubois, A.; Andreazza, C. Silicon Exfoliation by Hydrogen Implantation: Actual Nature of Precursor Defects. Nucl. Instrum. Methods Phys. Res. Sect. B Beam Interact. Mater. At. 2017, 401, 38–44. [Google Scholar] [CrossRef]

- Schoenfelder, S.; Breitenstein, O.; Rissland, S.; De Donno, R.; Bagdahn, J. Kerfless Wafering for Silicon Wafers by Using a Reusable Metal Layer. Energy Procedia 2013, 38, 942–949. [Google Scholar] [CrossRef]

- Dross, F.; Robbelein, J.; Vandevelde, B.; Van Kerschaver, E.; Gordon, I.; Beaucarne, G.; Poortmans, J. Stress-Induced Large-Area Lift-off of Crystalline Si Films. Appl. Phys. A Mater. Sci. Process. 2007, 89, 149–152. [Google Scholar] [CrossRef]

- Swoboda, M.; Beyer, C.; Rieske, R.; Drescher, W.; Richter, J. Laser Assisted SiC Wafering Using COLD SPLIT. Mater. Sci. Forum 2017, 897, 403–406. [Google Scholar] [CrossRef]

- Bedell, S.W.; Fogel, K.; Lauro, P.; Shahrjerdi, D.; Ott, J.A.; Sadana, D. Layer Transfer by Controlled Spalling. J. Phys. D Appl. asPhys. 2013, 46, 152002. [Google Scholar] [CrossRef]

- Milenkovic, N.; Driessen, M.; Steinhauser, B.; Benick, J.; Lindekugel, S.; Hermle, M.; Janz, S.; Reber, S. 20% Efficient Solar Cells Fabricated from Epitaxially Grown and Freestanding N-Type Wafers. Sol. Energy Mater. Sol. Cells 2017, 159, 570–575. [Google Scholar] [CrossRef]

- Press Release IMEC. Imec and Crystal Solar Demonstrate 22.5 Percent nPERT Si Solar Cells on Kerfless Epitaxial Wafers. 2016. Available online: https://www.Imec-Int.Com/En/Articles/Imec-and-Crystal-Solar-Demonstrate-22-5-Percent-Npert-Si-Solar-Cells-on-Kerfless-Epitaxial-Wafers (accessed on 20 September 2023).

- Becker, C.; Sontheimer, T.; Steffens, S.; Scherf, S.; Rech, B. Polycrystalline Silicon Thin Films by High-Rate Electronbeam Evaporation for Photovoltaic Applications—Influence of Substrate Texture and Temperature. Energy Procedia 2011, 10, 61–65. [Google Scholar] [CrossRef]

- Gorka, B.; Dogan, P.; Sieber, I.; Fenske, F.; Gall, S. Low-Temperature Epitaxy of Silicon by Electron Beam Evaporation. Thin Solid Film. 2007, 515, 7643–7646. [Google Scholar] [CrossRef]

- Saager, S.; Scheffel, B.; Heinß, J.-P. High-rate deposition of high-pure silicon thin films for PV Absorber layers by crucible-free electron beam physical vapor deposition. Surf. Coat. Technol. 2019, 378, 125019. [Google Scholar] [CrossRef]

- Heinß, J.P.; Pfefferling, B.; Saager, S.; Temmler, D. High Purity Deposition of Silicon Layers with Rates ≥ 300 nm/s. In Proceedings of the 31st European Photovoltaic Solar Energy Conference and Exhibition, Hamburg, Germany, 14–18 September 2015. [Google Scholar] [CrossRef]

- Ellert, C.; Wachtendorf, C.; Hedler, A.; Klindworth, M.; Martinek, M. Influence of Raman Crystallinity on the Performance of Micromorph Thin Film Silicon Solar Cells. Sol. Energy Mater. Sol. Cells 2012, 96, 71–76. [Google Scholar] [CrossRef]

- Ledinský, M.; Vetushka, A.; Stuchlík, J.; Mates, T.; Fejfar, A.; Kožka, J.; Ŝtêpánek, J. Crystallinity of the mixed phase silicon thin films by Raman spectroscopy. J. Non-Cryst. Solids 2008, 354, 2253–2257. [Google Scholar] [CrossRef]

- Flamant, G.; Kurtcuoglu, V.; Murray, J.; Steinfeld, A. Purification of Metallurgical Grade Silicon by a Solar Process. Sol. Energy Mater. Sol. Cells 2006, 90, 2099–2106. [Google Scholar] [CrossRef]

- Kivambe, M.M.; Powell, D.M.; Castellanos, S.; Jensen, M.A.; Morishige, A.E.; Lai, B.; Hao, R.; Ravi, T.S.; Buonassisi, T. Characterization of High-Quality Kerfless Epitaxial Silicon for Solar Cells: Defect Sources and Impact on Minority-Carrier Lifetime. J. Cryst. Growth 2018, 483, 57–64. [Google Scholar] [CrossRef]

- Sturm, J.C.; Chung, K.H. Chemical Vapor Deposition Epitaxy of Silicon-Based Materials Using Neopentasilane. ECS Trans. 2009, 16, 799–805. [Google Scholar] [CrossRef]

- Rosenits, P.; Kopp, F.; Reber, S. Epitaxially Grown Crystalline Silicon Thin-Film Solar Cells Reaching 16.5% Efficiency with Basic Cell Process. Thin Solid Film. 2011, 519, 3288–3290. [Google Scholar] [CrossRef]

- Gemmel, C.; Hensen, J.; Kajari-Schröder, S.; Brendel, R. Lifetime Analysis for Defect Characterization in Kerfless Epitaxial Silicon from the Porous Silicon Process. Energy Procedia 2016, 92, 29–36. [Google Scholar] [CrossRef][Green Version]

- Niepelt, R.; Hensena, J.; Knorr, A.; Steckenreiter, V.; Kajari-Schoder, S.; Brendel, R. High-Quality Exfoliated Crystalline Silicon Foils for Solar Cell Applications. Energy Procedia 2014, 55, 570–577. [Google Scholar] [CrossRef][Green Version]

- Huang, L.-J.; Tong, Q.-Y.; Chao, Y.-L.; Lee, T.-H.; Martini, T.; Gösele, U. Onset of Blistering in Hydrogen-Implanted Silicon. Appl. Phys. Lett. 1999, 74, 982–984. [Google Scholar] [CrossRef]

- Sedani, S.H.; Yasar, O.F.; Karaman, M.; Turan, R. Effects of Boron Doping on Solid Phase Crystallization of in Situ Doped Amorphous Silicon Thin Films Prepared by Electron Beam Evaporation. Thin Solid Film. 2020, 694, 137639. [Google Scholar] [CrossRef]

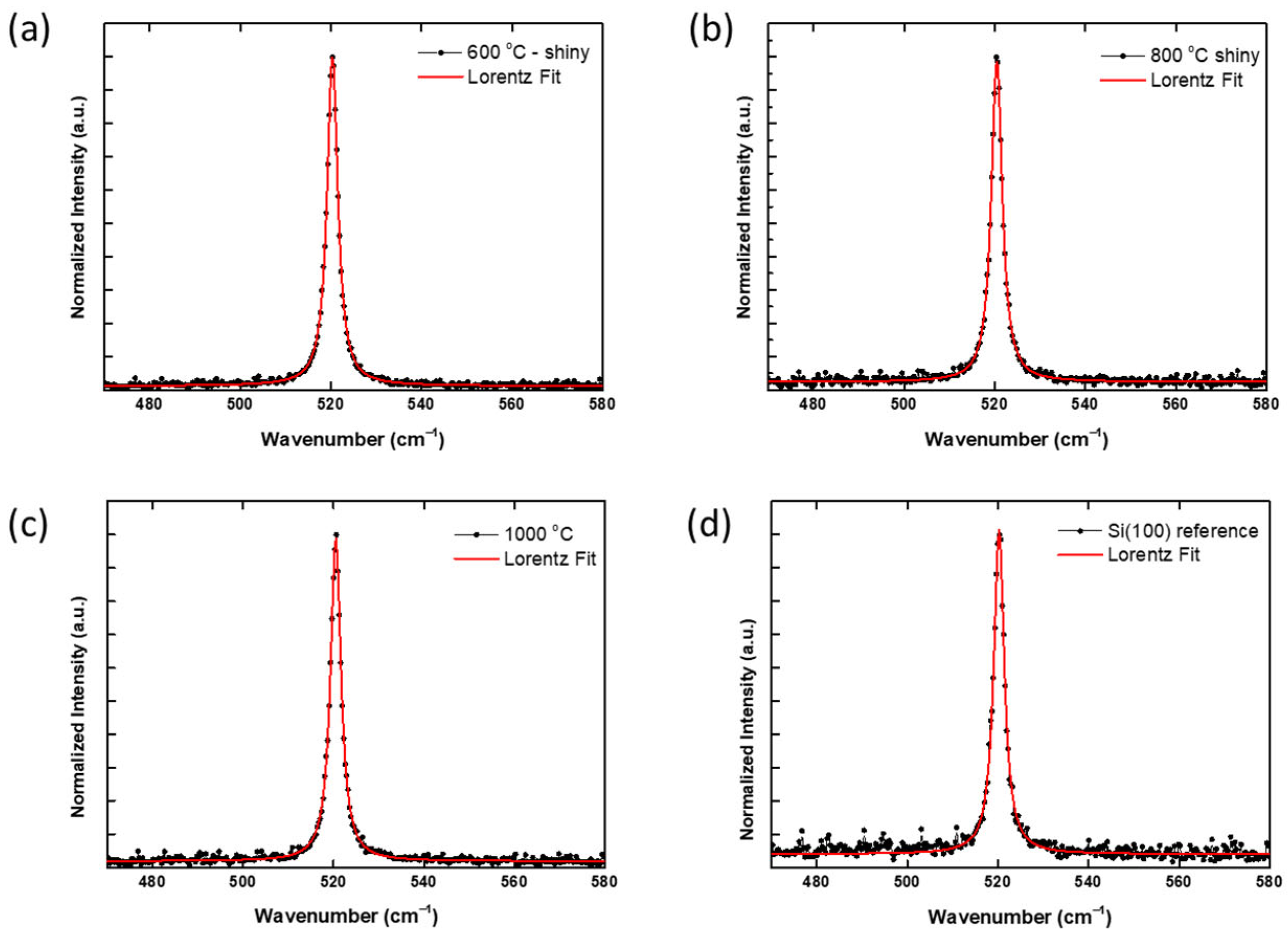

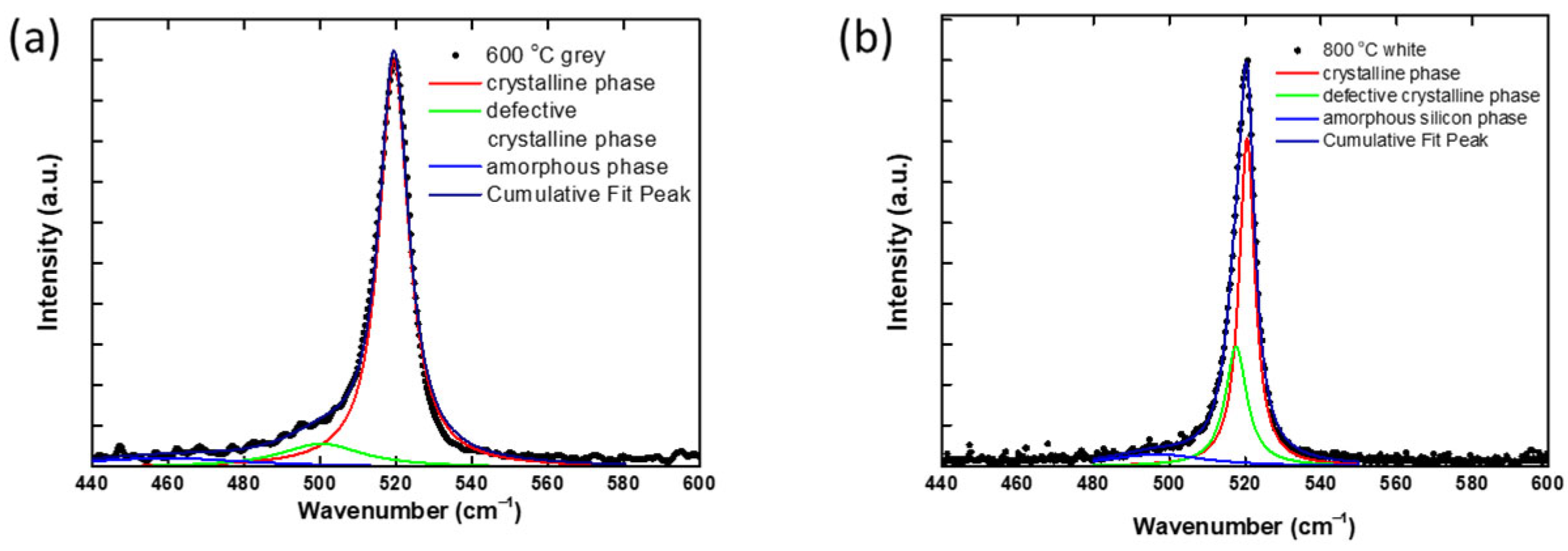

| Sample | Si Crystalline [cm−1] | Si Defective [cm−1] | Si Amorphous [cm−1] |

|---|---|---|---|

| Si (100) ref | 520.24 | - | - |

| Si 1000 °C | 520.49 | - | - |

| Si 800 °C shiny | 520.48 | - | - |

| Si 600 °C shiny | 520.36 | - | - |

| Si 800 °C grey | 520.52 | 517.62 | 496.69 |

| Si 600 °C grey | 519.42 | 500.35 | 459.33 |

| Sample | Resistivity [Ω·cm] | Carrier Density [1/cm3] | Mobility [cm2/(V·s)] |

|---|---|---|---|

| 800 °C | 28.4 | 9.17 × 1014 | 240 |

| 1000 °C | 5.01 | 4.93 × 1015 | 253 |

| Reference values for Si feedstock | 5.5–5.7 | 2.7 × 1015 * | 408.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Stange, M.; Sunde, T.O.; Dahl-Hansen, R.; Rajput, K.; Seland Graff, J.; Belle, B.D.; Ulyashin, A.G. High-Rate Epitaxial Growth of Silicon Using Electron Beam Evaporation at High Temperatures. Coatings 2023, 13, 2030. https://doi.org/10.3390/coatings13122030

Stange M, Sunde TO, Dahl-Hansen R, Rajput K, Seland Graff J, Belle BD, Ulyashin AG. High-Rate Epitaxial Growth of Silicon Using Electron Beam Evaporation at High Temperatures. Coatings. 2023; 13(12):2030. https://doi.org/10.3390/coatings13122030

Chicago/Turabian StyleStange, Marit, Tor Olav Sunde, Runar Dahl-Hansen, Kalpna Rajput, Joachim Seland Graff, Branson D. Belle, and Alexander G. Ulyashin. 2023. "High-Rate Epitaxial Growth of Silicon Using Electron Beam Evaporation at High Temperatures" Coatings 13, no. 12: 2030. https://doi.org/10.3390/coatings13122030

APA StyleStange, M., Sunde, T. O., Dahl-Hansen, R., Rajput, K., Seland Graff, J., Belle, B. D., & Ulyashin, A. G. (2023). High-Rate Epitaxial Growth of Silicon Using Electron Beam Evaporation at High Temperatures. Coatings, 13(12), 2030. https://doi.org/10.3390/coatings13122030