An Investigation of the Operating Principles and Power Consumption of Digital-Based Analog Amplifiers

Abstract

:1. Introduction

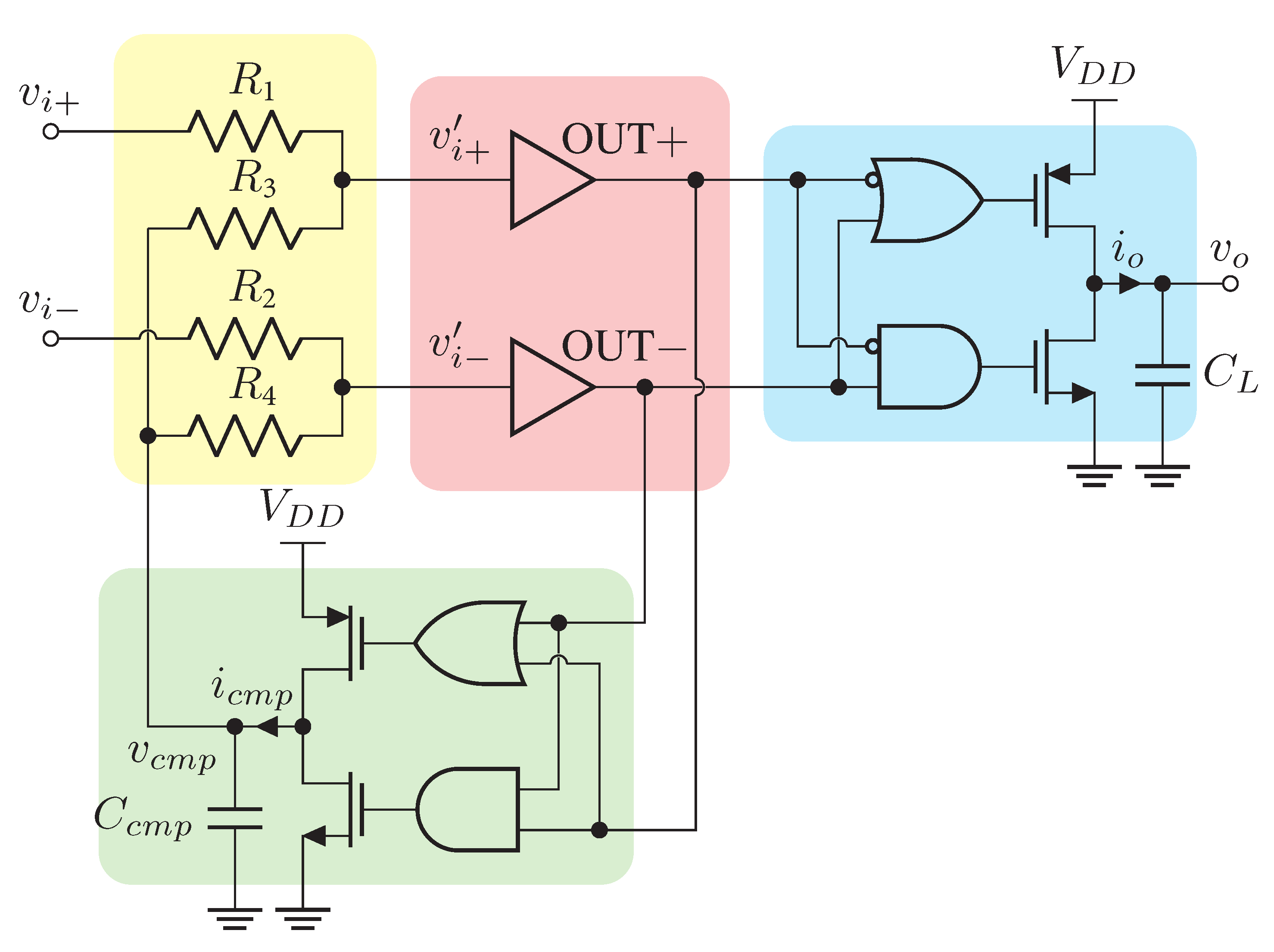

2. Operating Principle of the DDA

- At , both and cross , and , switch from L to H. It takes a certain amount of time for the signal to propagate through the CMFB;

- Before , although , are high, the CM compensation inverter has not yet changed its state, and is still charging with as when ;

- At , the CMFB changes its state: the pull-down switches on, and the capacitor is discharged with a constant current ;

- From to , while is discharging, both and fall below the threshold ;

- At , , switch from H to L;

- Before , the CM compensation inverter has not yet changed its state and is still discharging;

- At , the CM compensation inverter changes state, the pull-up switches on, and the capacitor is charged with the current ;

- This cycle is repeated every .

- The differential voltage corresponds to a small mismatch between and that, in turn, causes to cross the threshold voltage with a small delay ; during , the differential voltage is positive, , and the outputs (, ) = (). After , it is , that crosses the threshold voltage with a small delay respect to .

- is a triangular wave with the same period , as in Figure 2 but, during the interval , the voltage is clamped since the buffer is in the high impedance region.

- During the interval , the output buffer charges and steps up of .

- The charge on is incremented by , twice every .

3. Design and Simulations of the DDA

3.1. Sizing of the DDA in UMC 180 nm CMOS Process

3.2. Simulation Results

3.2.1. Open Loop

- In regions 1 and 5, the differential voltage is large, and are well separated and opposite with respect to the logic threshold . In these regions, the output voltage saturates to or 0, the common-mode compensation network is not active, and only the pull-up or the pull-down of the output inverter turns on. In Figure 4, , are the gate voltages of the pull-up and pull-down, respectively. In Figure 6, regions 1 and 5 are limited by the equations and :Furthermore, since the CMFB is not active, , i.e., ( + )/2, regions 1 and 5 read:

- In region 3, the differential voltage is small enough to activate the CMFB. The compensation voltage oscillates and the digital outputs and commute between L and H. Both the pull-up and the pull-down of the output inverter are active; if is positive, steps up, if is negative, steps down. This region is defined by the condition , i.e., .

- In regions 2 and 4, the differential voltage is small, but not as small as in region 3. In region 2, and holds the low logic state, while quickly commutes from H to L due to the CMFB. The pull-down of the output stage switches on. In region 4, and holds the low logic state, while quickly commutes from H to L due to the CMFB. The pull-up of the output stage switches on. Hence, the pull-up or the pull-down switches on, but are not always active as in regions 1 and 5.

3.2.2. Closed Loop

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| DDA | Digital-based Differential Amplifier |

| CAD | Computer-aided Design |

| UMC | United Microelectronics Corporation |

| CMOS | Complementary Metal Oxide Semiconductor |

| CM | Common Mode |

| GBW | Gain Bandwidth |

| CMFB | Common Mode Feedback |

| DC | Direct Coupling |

| VCO | Voltage Controlled Oscillator |

| FFT | Fast Fourier Transform |

| G | Loop Gain |

| THD | Total Harmonic Distortion |

| IoT | Internet of Things |

References

- Nauta, B. A CMOS transconductance-C filter technique for very high frequencies. IEEE J.-Solid Circuits 1992, 27, 2. [Google Scholar] [CrossRef]

- Rodovalho, L.H.; Toledo, P.; Mir, F.; Ebrahimi, F. Hybrid Inverter-Based Fully Differential Operational Transconductance Amplifiers. Chips 2023, 2, 1–19. [Google Scholar] [CrossRef]

- Nicholson, A.P.; Iberzanov, A.; Jenkins, J.; Hamilton, T.J.; Lehmann, T. A Statistical Design Approach for a Digitally Programmable Mismatch-Tolerant High-Speed Nauta Structure Differential OTA in 65-nm CMOS. IEEE Trans. Very Large Scale Integr. (Vlsi) Syst. 2016, 24, 2899–2910. [Google Scholar] [CrossRef]

- Manfredini, G.; Catania, A.; Benvenuti, L.; Cicalini, M.; Piotto, M.; Bruschi, P. Ultra-Low-Voltage Inverter-Based Amplifier with Novel Common-Mode Stabilization Loop. Electronics 2020, 9, 1019. [Google Scholar] [CrossRef]

- Wei, J.; Yao, Y.; Luo, L.; Ma, S.; Ye, F.; Ren, J. A Novel Nauta Transconductor for Ultra-Wideband gm-C Filter with Temperature Calibration. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019. [Google Scholar]

- Toledo, P.; Rubino, R.; Musolino, F.; Crovetti, P. Re-Thinking Analog Integrated Circuits in Digital Terms: A New Design Concept for the IoT Era. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 816–822. [Google Scholar] [CrossRef]

- Crovetti, P.S.; Musolino, F.; Aiello, O.; Toledo, P.; Rubino, R. Breaking the boundaries between analogue and digital. Electron. Lett. 2019, 55, 672–673. [Google Scholar] [CrossRef]

- Guanziroli, F.; Bassoli, R.; Crippa, C.; Devecchi, D.; Nicollini, G. A 1 W 104 dB SNR filter-less fully-digital open-loop class D audio amplifier with EMI reduction. IEEE J.-Solid Circuits 2012, 47, 686–698. [Google Scholar] [CrossRef]

- Kalani, S.; Bertolini, A.; Richelli, A.; Kinget, P.R. A 0.2V 492nW VCO-based OTA with 60kHz UGB and 207 μVrms noise. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Kalani, S.; Kinget, P.R. Zero-crossing-time-difference model for stability analysis of VCO-based OTAS. IEEE Trans. Circuits Syst. Reg. Pap. 2020, 67, 839–851. [Google Scholar] [CrossRef]

- Kalani, S.; Tanbir, H.; Rupal, G.; Kinget, P.R. Benefits of using VCO-OTAs to construct TIAs in wideband current-mode receivers over inverter-based OTAs. IEEE Trans. Circuits Syst. Regul. Pap. 2018, 66, 1681–1691. [Google Scholar] [CrossRef]

- Richelli, A.; Colalongo, L.; Kovacs-Vajna, Z.M. EMI Effect in Voltage-to-Time Converters. IEEE Trans. Circuits Syst. II Express Briefs 2021, 8, 1078–1082. [Google Scholar] [CrossRef]

- Unnikrishnan, V.; Vesterbacka, M. Time-mode analog-to-digital conversion using standard cells. IEEE Trans. Circuits Syst. Reg. Pap. 2014, 61, 3348–3357. [Google Scholar] [CrossRef]

- Song, Y.; Smith, S.; Karlinsey, B.; Hawkins, A.R.; Chiang, S.H.W. The digital-assisted charge amplifier: A digital-based approach to charge amplification. IEEE Trans. Circuits Syst. Regul. Pap. 2022, 69, 3114–3123. [Google Scholar] [CrossRef]

- Brooks, L.; Lee, H.S. A 12b, 50 MS/s, fully differential zero-crossing based pipelined ADC. IEEE J.-Solid Circuits 2009, 44, 3329–3343. [Google Scholar] [CrossRef]

- Fahmy, A.; Liu, J.; Kim, T.; Maghari, N. An all-digital scalable and reconfigurable wide-input range stochastic ADC using only standard cells. IEEE Trans. Circuits Syst. Express Briefs 2015, 62, 731–735. [Google Scholar] [CrossRef]

- Weaver, S.; Hershberg, B.; Moon, U.-K. Digitally synthesized stochastic flash ADC using only standard digital cells. IEEE Trans. Circuits Syst. Reg. Pap. 2014, 61, 84–91. [Google Scholar] [CrossRef]

- Gielen, G.G.E.; Hernandez, L.; Rombouts, P. Time-encoding analog-to-digital converters: Bridging the analog gap to advanced digital CMOS-Part 1: Basic principles. IEEE-Solid Circuits Mag. 2020, 12, 47–55. [Google Scholar] [CrossRef]

- Gielen, G.G.E.; Hernandez, L.; Rombouts, P. Time-encoding analog-to-digital converters: Bridging the analog gap to advanced digital CMOS-Part 2: Architectures and circuits. IEEE Solid-State Circuits Mag. 2020, 12, 18–27. [Google Scholar] [CrossRef]

- Rubino, R.; Musolino, F.; Chen, Y.; Richelli, A.; Crovetti, P. A 880 nW, 100 kS/s, 13 bit Differential Relaxation-DAC in 180 nm. In Proceedings of the 2023 18th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Valencia, Spain, 18–21 June 2023; pp. 269–272. [Google Scholar]

- Crovetti, P.S. A digital-based virtual voltage reference. IEEE Trans. Circuits Syst. I Reg. Pap. 2015, 62, 1315–1324. [Google Scholar] [CrossRef]

- Cai, G.; Zhan, C.; Lu, Y. A fast-transient-response fully-integrated digital LDO with adaptive current step size control. IEEE Trans. Circuits Syst. Reg. Pap. 2019, 66, 3610–3619. [Google Scholar] [CrossRef]

- Privitera, M.; Crovetti, P.S.; Grasso, A.D. A novel Digital OTA topology with 66-dB DC Gain and 12.3-kHz Bandwidth. IEEE Trans. Circuits Syst. II Express Briefs 2023. [Google Scholar] [CrossRef]

- Crovetti, P. A digital-based analog differential circuit. IEEE Trans. Circuits Syst. Regul. Pap. 2013, 60, 3107–3116. [Google Scholar] [CrossRef]

- Palumbo, G.; Scotti, G. A Novel Standard-Cell-Based Implementation of the Digital OTA Suitable for Automatic Place and Route. J. Low Power Electron. Appl. 2021, 11, 42. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.; Aiello, O.; Alioto, M. Fully Digital Rail-to-Rail OTA with Sub-1000-μm2 Area, 250-mV Minimum Supply, and nW Power at 150-pF Load in 180 nm. IEEE-Solid Circuits Lett. 2020, 3, 474–477. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.; Aiello, O.; Alioto, M. Design of Digital OTAs with Operation Down to 0.3 V and nW Power for Direct Harvesting. IEEE Trans. Circuits Syst. Regul. Pap. 2021, 68, 3693–3706. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.; Klimach, H.; Bampi, S.; Aiello, O.; Alioto, M. A 300mV-Supply, Sub-nW-Power Digital-Based Operational Transconductance Amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 3073–3077. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.S.; Klimach, H.D.; Musolino, F.; Bampi, S. Low-Voltage, Low-Area, nW-Power CMOS Digital-Based Biosignal Amplifier. IEEE Access 2022, 10, 44106–44115. [Google Scholar] [CrossRef]

- Toledo, P.; Aiello, O.; Crovetti, P.S. A 300mV-Supply Standard-Cell-Based OTA with Digital PWM Offset Calibration. In Proceedings of the 2019 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC), Helsinki, Finland, 29–30 October 2019. [Google Scholar]

- Toledo, P.; Crovetti, P.; Klimach, H.; Bampi, S. A 300mV-Supply, 2nW-Power, 80pF-Load CMOS Digital-Based OTA for IoT Interfaces. In Proceedings of the 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Genoa, Italy, 27–29 November 2019; pp. 170–173. [Google Scholar]

- Rubino, R.; Carrara, S.; Crovetti, P. Direct Digital Sensing Potentiostat targeting Body-Dust. In Proceedings of the 2022 IEEE Biomedical Circuits and Systems Conference (BioCAS), Taipei, Taiwan, 13–15 October 2022. [Google Scholar]

- Lv, L.; Zhou, X.; Qiao, Z.; Li, Q. Inverter-based subthreshold amplifier techniques and their application in 0.3 V ΔΣ-modulators. IEEE-Solid Circuits 2019, 54, 1436–1445. [Google Scholar] [CrossRef]

- Ferreira, L.H.C.; Sonkusale, S.R. A 60-dB gain OTA operating at 0.25-V power supply in 130-nm digital CMOS process. IEEE Tran. Circuits Syst. Reg. Pap. 2014, 61, 1609–1617. [Google Scholar] [CrossRef]

- Dessouky, M.; Kaiser, A. Very low-voltage digital-audio ΔΣ-modulator with 88-db dynamic range using local switch bootstrapping. IEEE-Solid Circuits 2001, 36, 349–355. [Google Scholar] [CrossRef]

| Architecture | DDA [28] | Inv-Based [33] | Bulk-Driven [34] | Gate-Driven [35] |

|---|---|---|---|---|

| Biasing | dynamic | static | static | static |

| Tecn. | 180 nm | 130 nm | 130 nm | 180 nm |

| Area | 1.4 m | - | 83 m | 0.08 mm |

| 0.3 V | 0.3 V | 0.25 V | 0.4 V | |

| DC gain | 31 dB | 49.8 dB | 60 dB | 60 dB |

| 80 pF | 2 pF | 15 pF | 1 pF | |

| GBW | 0.23 kHz | 9 kHz | 1.88 kHz | 1.2 MHz |

| Power | 0.4 nW | 1.8 nW | 18 nW | 10 W |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Richelli, A.; Faustini, P.; Rosa, A.; Colalongo, L. An Investigation of the Operating Principles and Power Consumption of Digital-Based Analog Amplifiers. J. Low Power Electron. Appl. 2023, 13, 51. https://doi.org/10.3390/jlpea13030051

Richelli A, Faustini P, Rosa A, Colalongo L. An Investigation of the Operating Principles and Power Consumption of Digital-Based Analog Amplifiers. Journal of Low Power Electronics and Applications. 2023; 13(3):51. https://doi.org/10.3390/jlpea13030051

Chicago/Turabian StyleRichelli, Anna, Paolo Faustini, Andrea Rosa, and Luigi Colalongo. 2023. "An Investigation of the Operating Principles and Power Consumption of Digital-Based Analog Amplifiers" Journal of Low Power Electronics and Applications 13, no. 3: 51. https://doi.org/10.3390/jlpea13030051