0.7 V Supply SC Circuits with Relaxed Slew Rate Requirements Using GB-Enhanced Multiple-Output Class AB/AB Op-Amps

Abstract

1. Introduction

2. Circuit Description

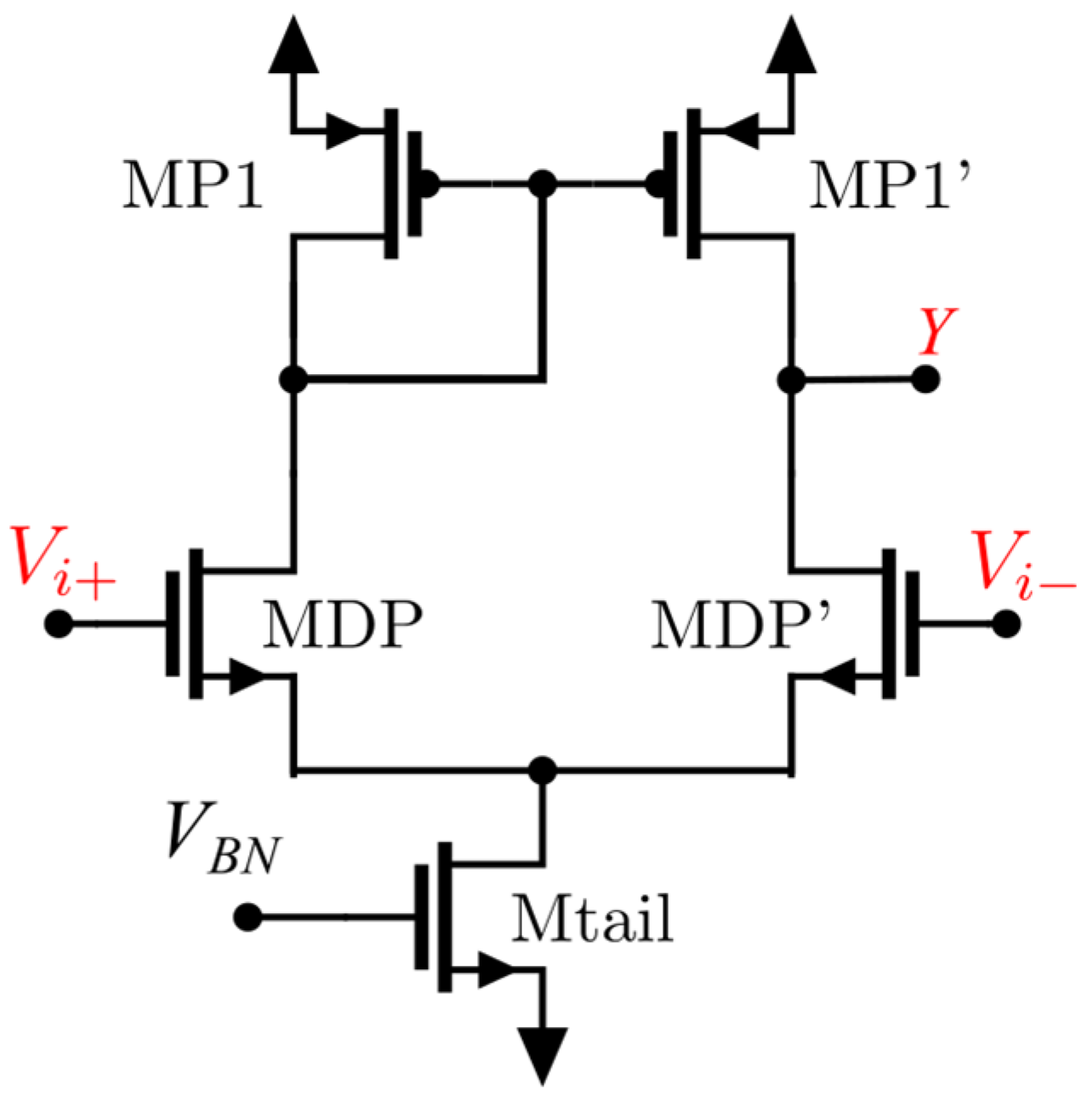

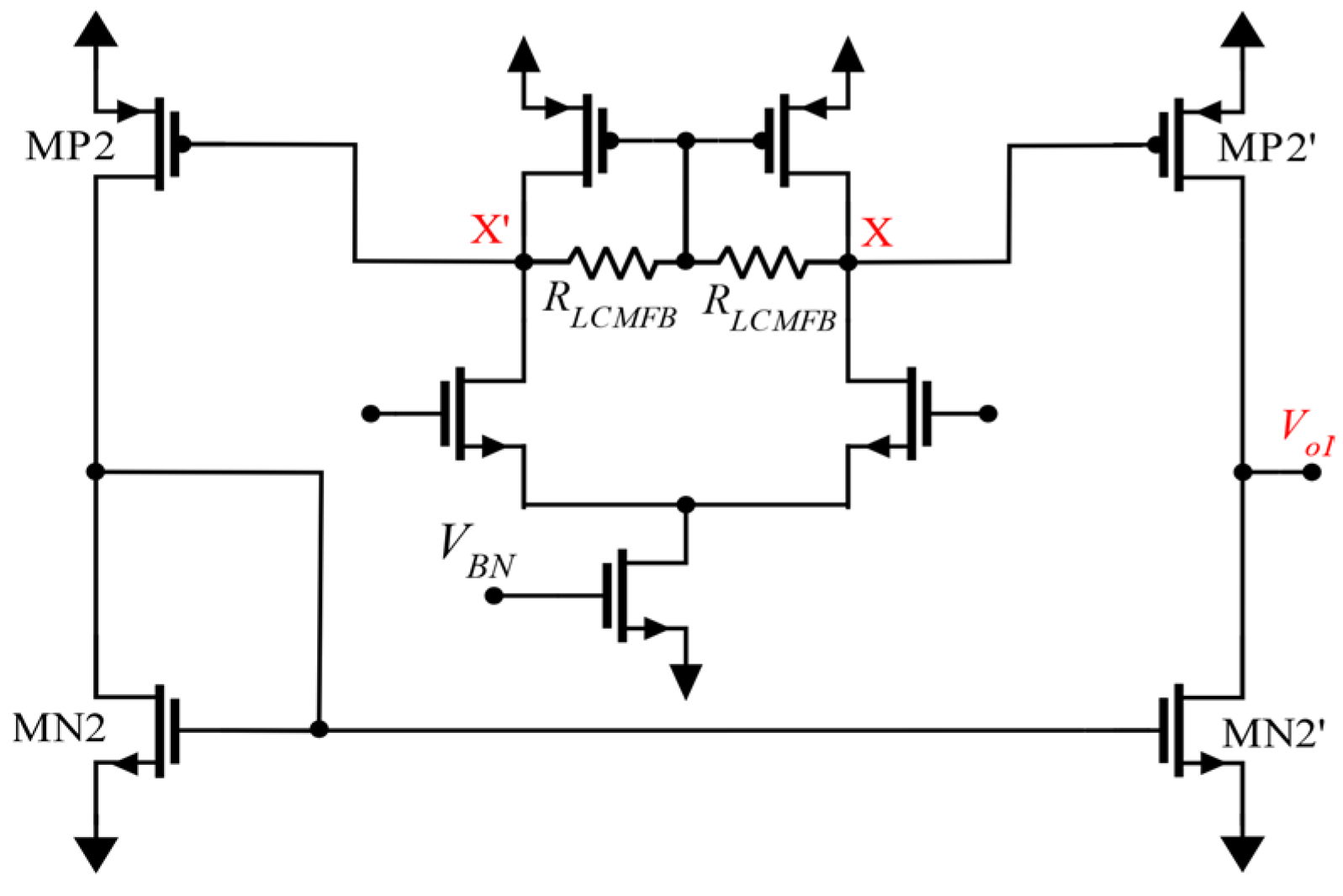

2.1. GB-Enhanced AB/AB Op-Amp with Dual Ouputs

2.2. Operation of the Composite Input State

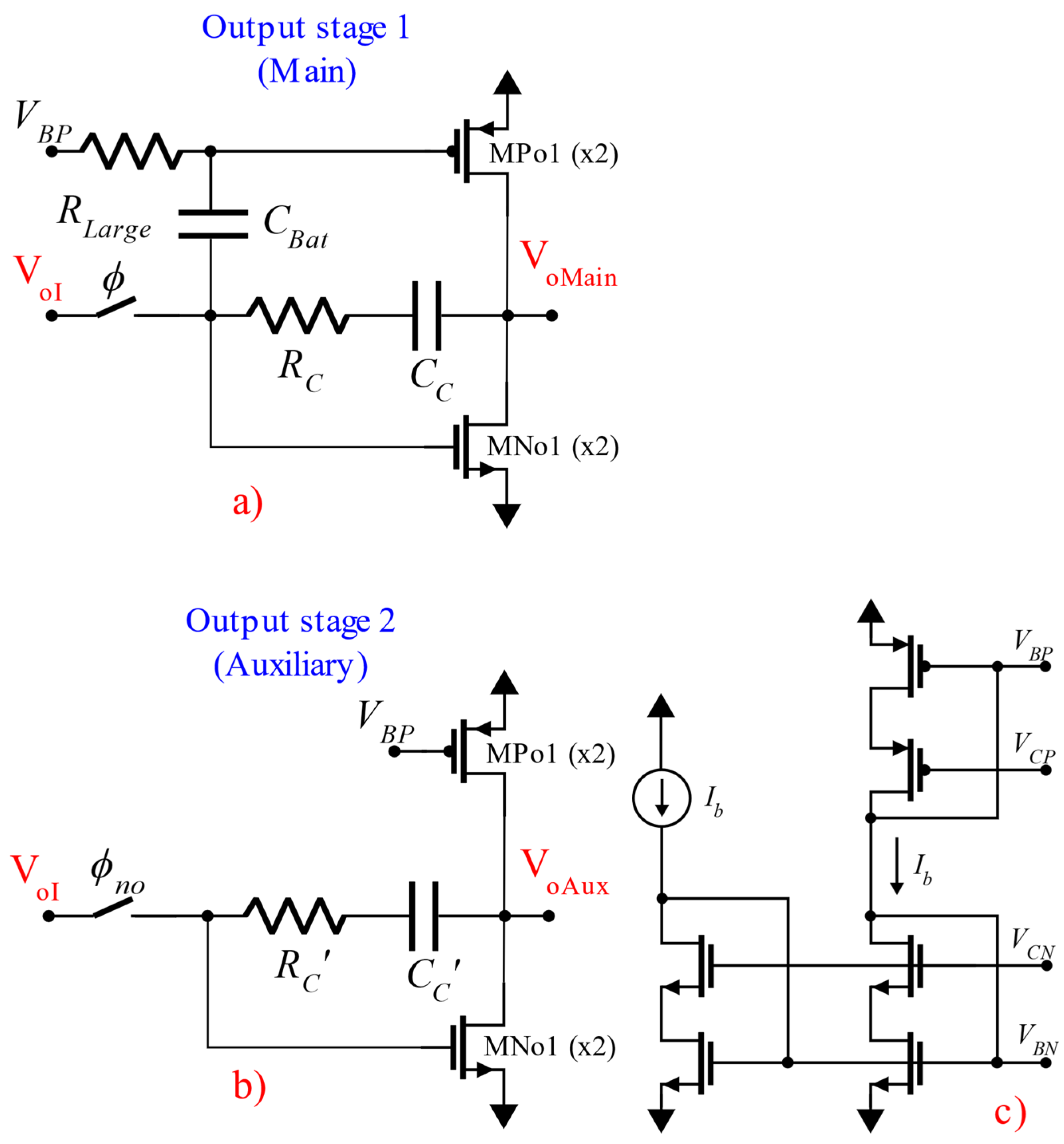

2.3. Operation of Output Stages

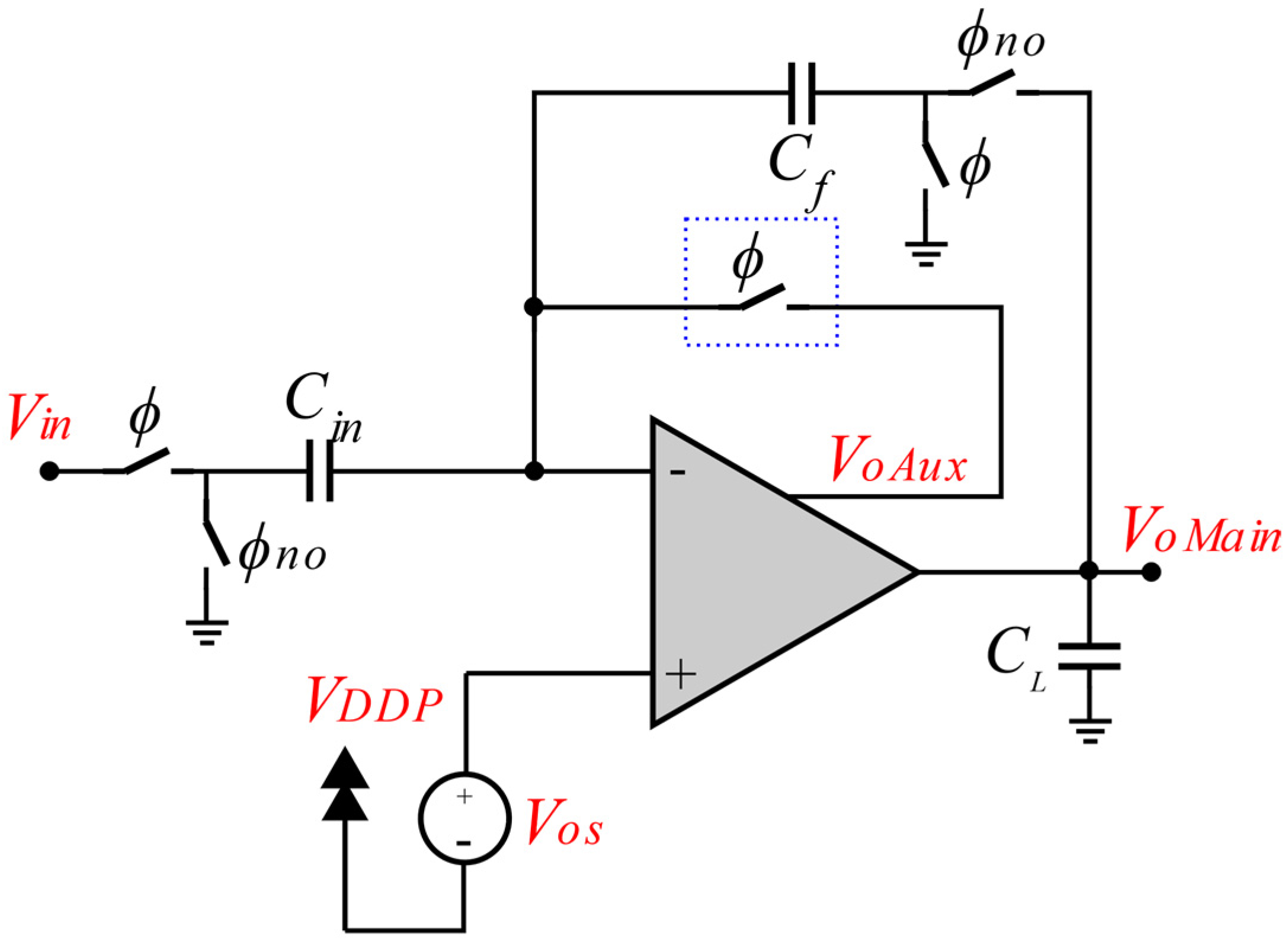

2.4. Low-Voltage SC Amplifier

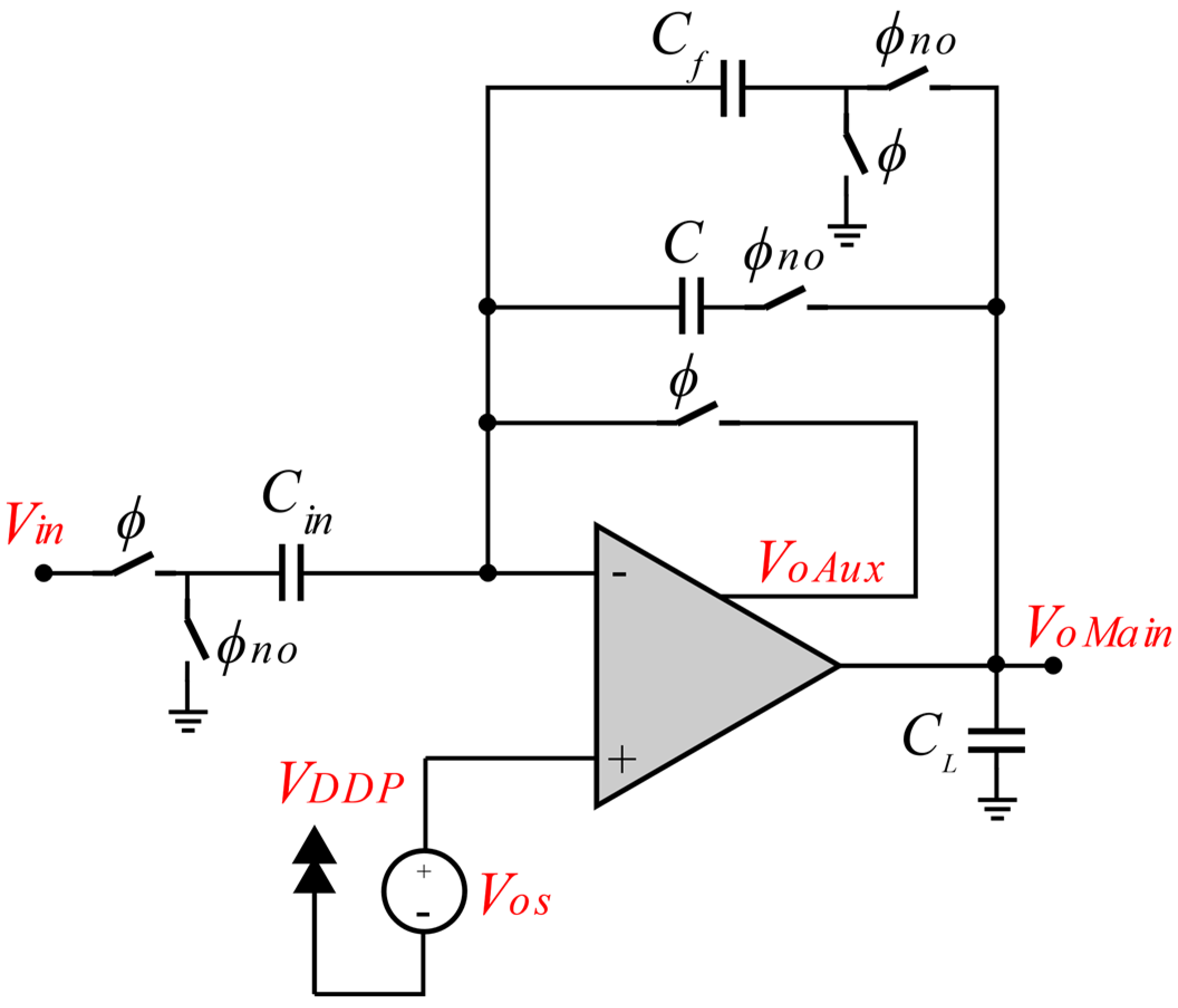

2.5. Low-Voltage SC Low-Pass Filter

3. Simulation Results

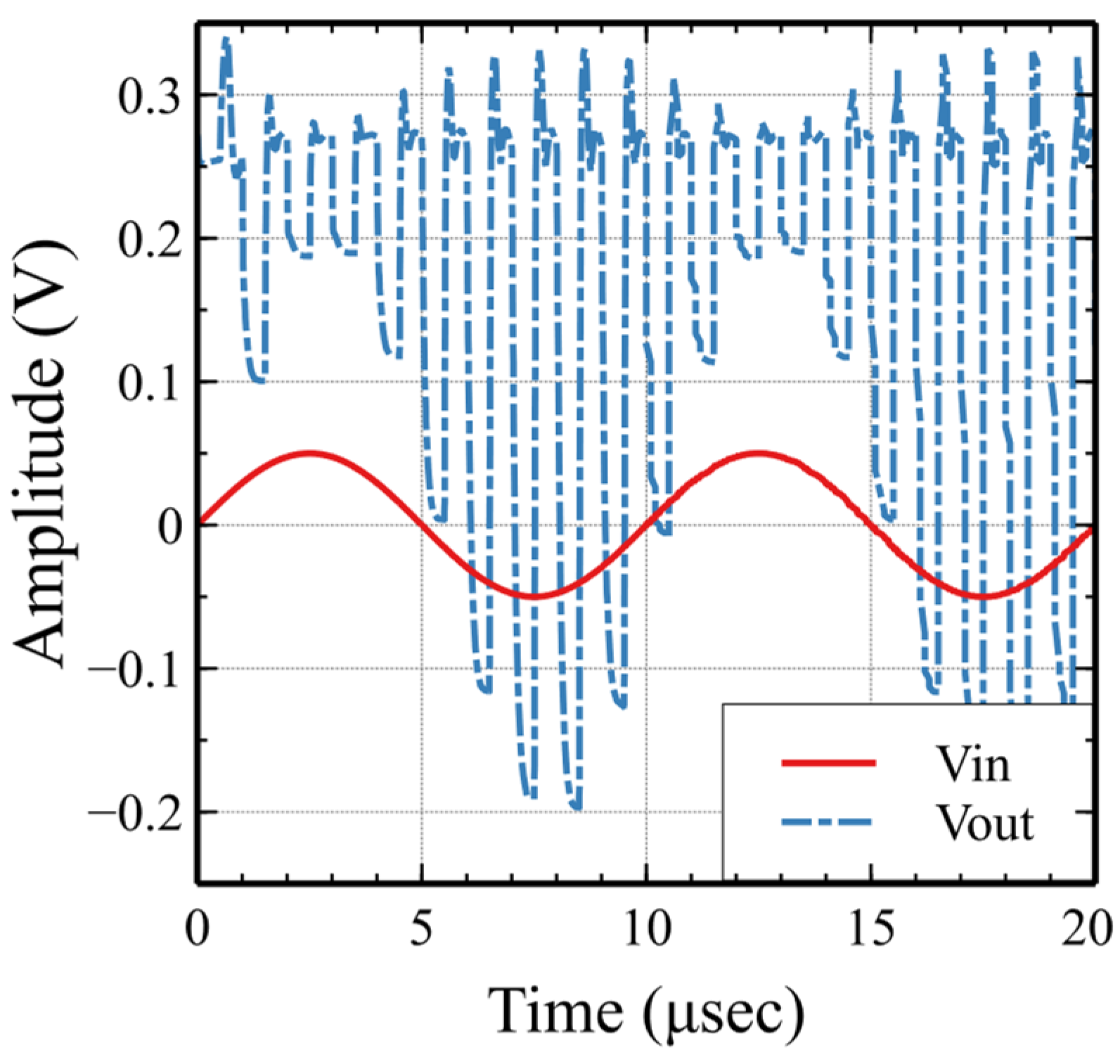

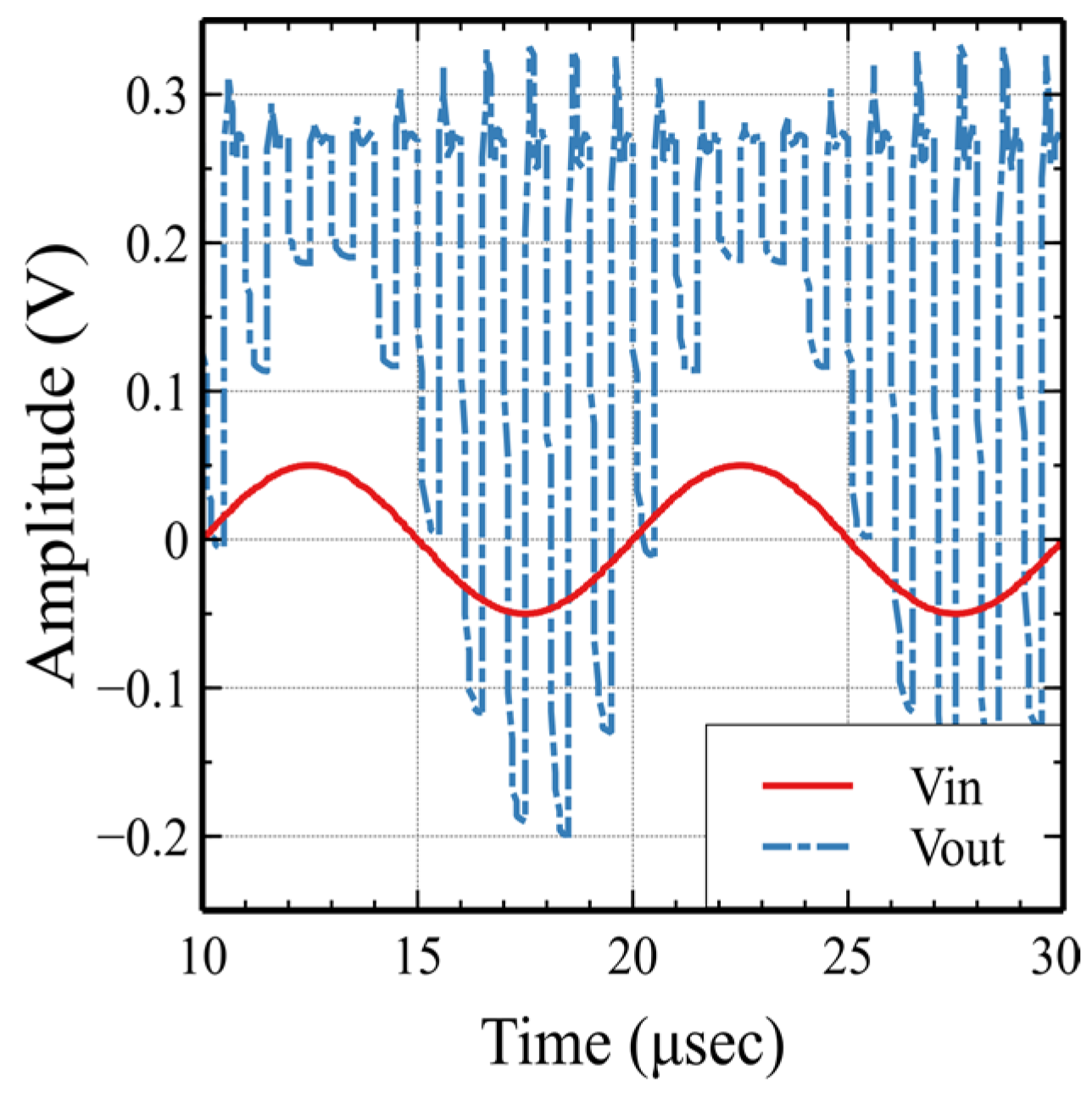

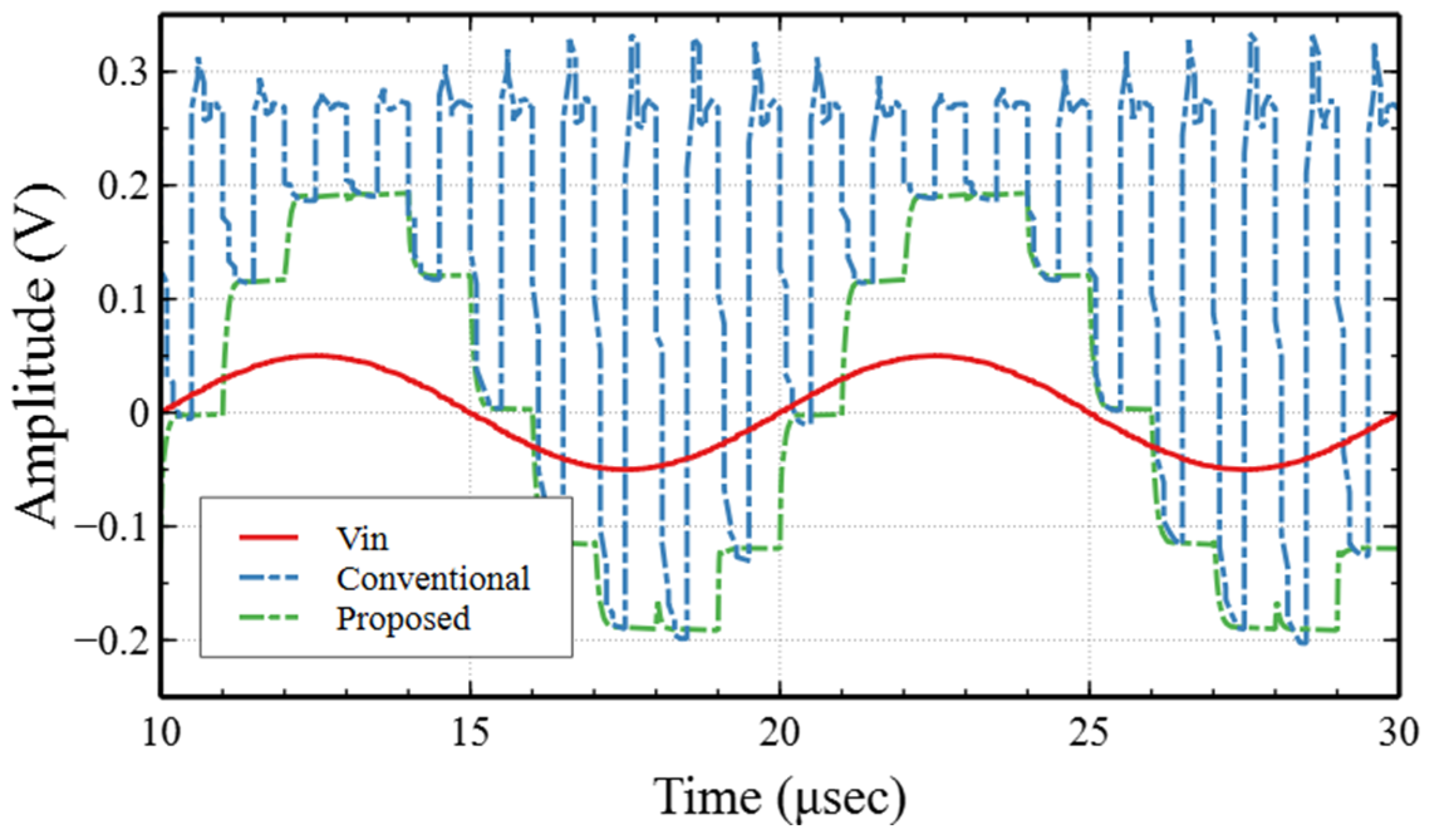

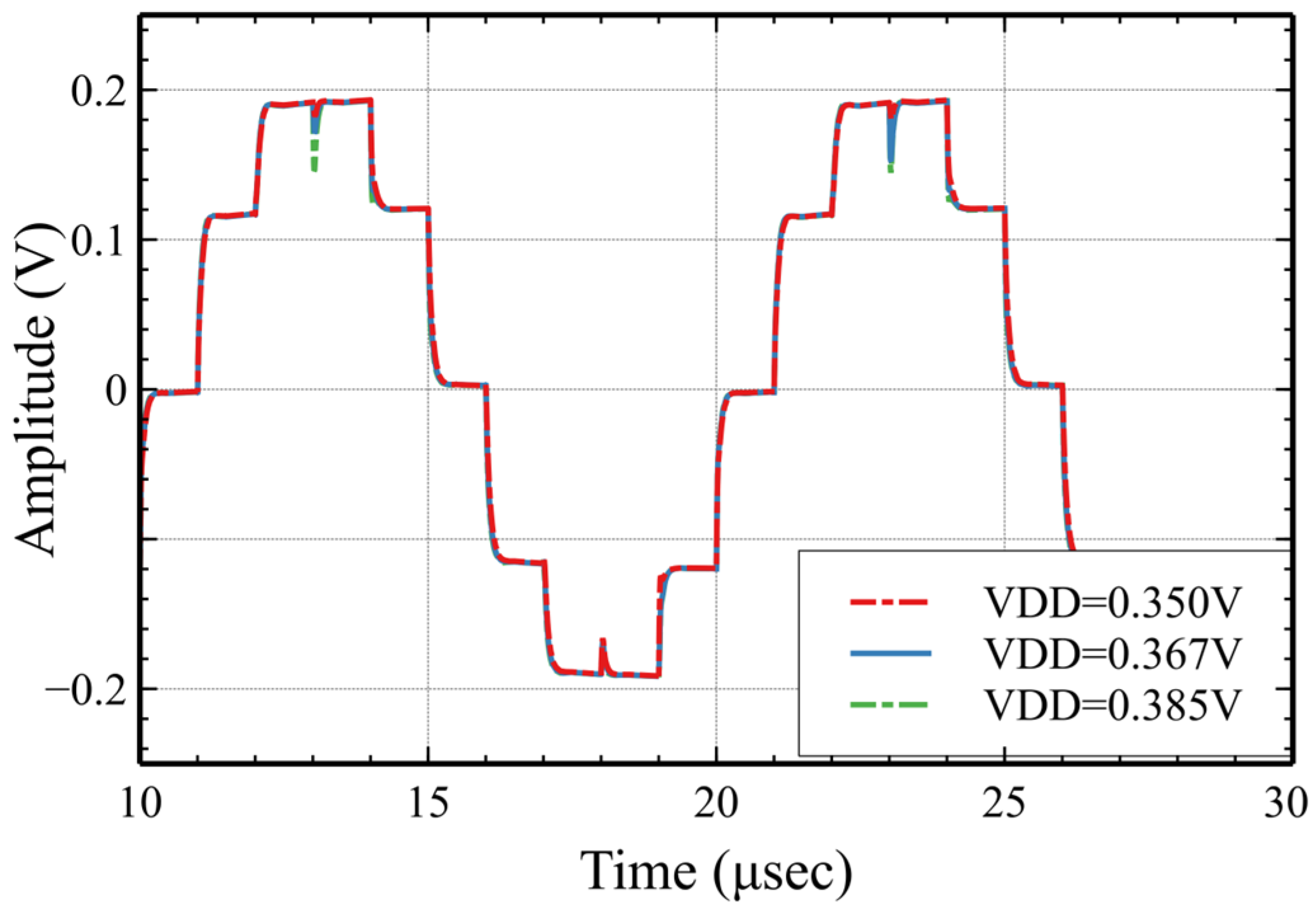

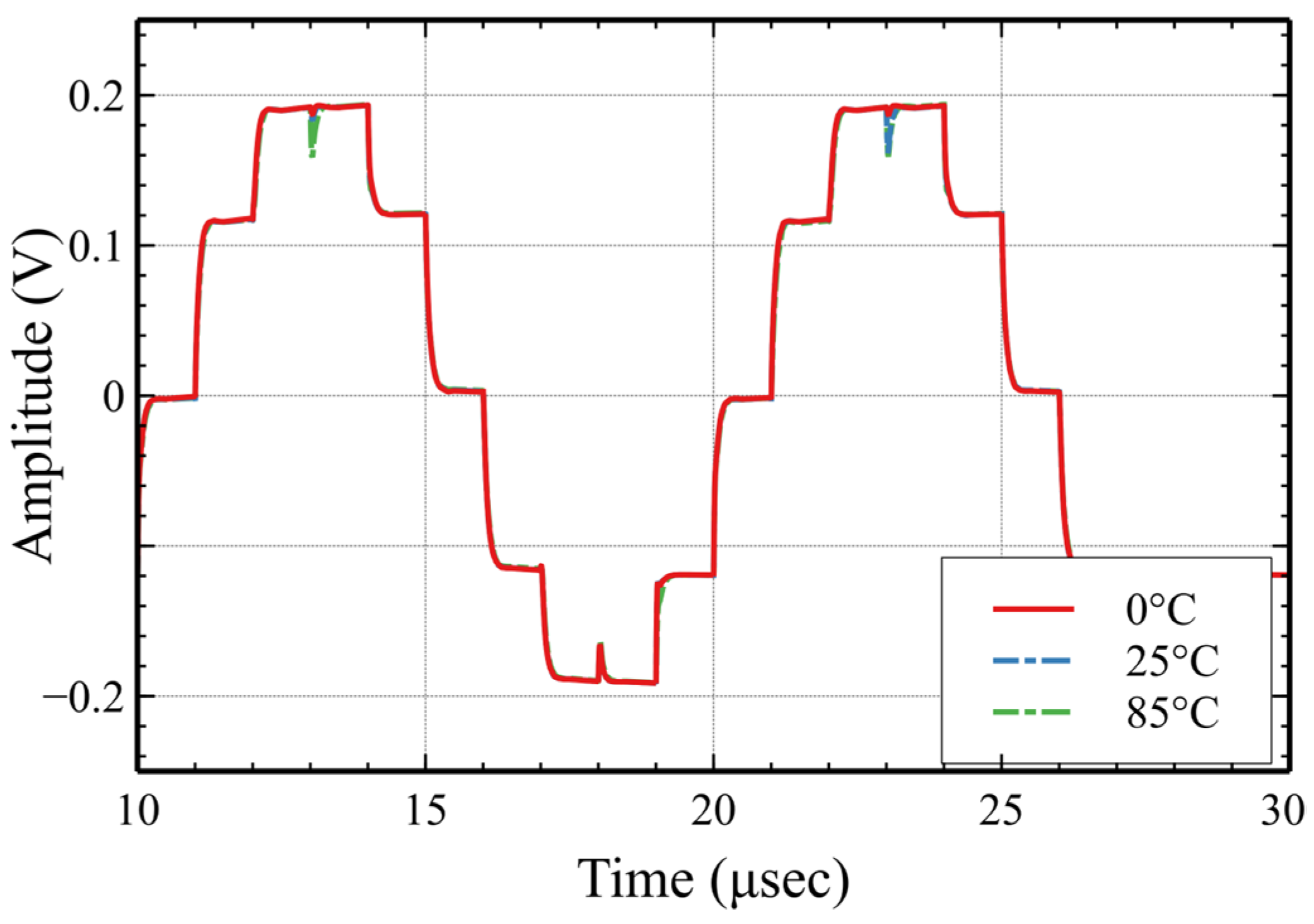

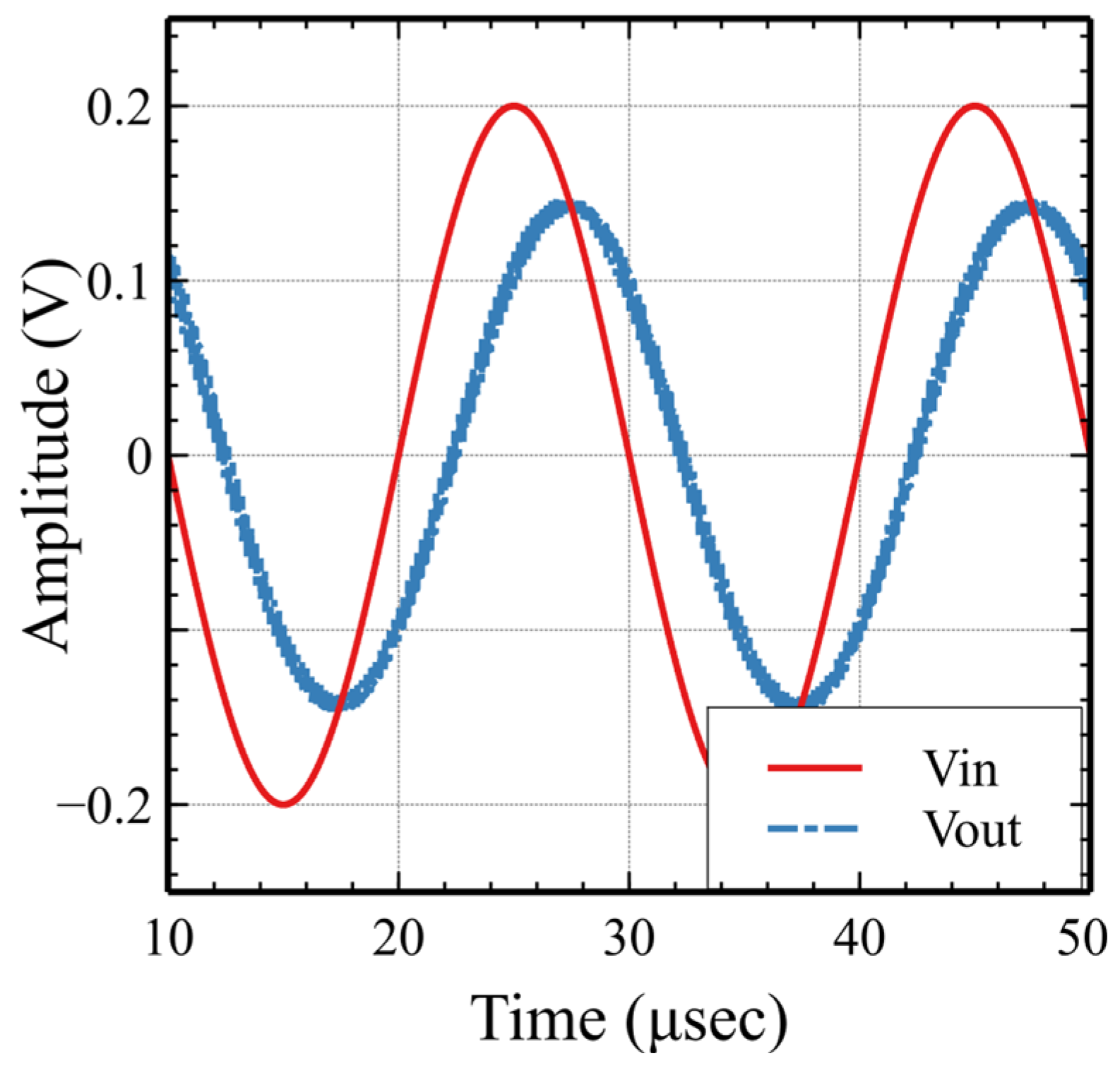

3.1. Low-Voltage SC Amplifier Results

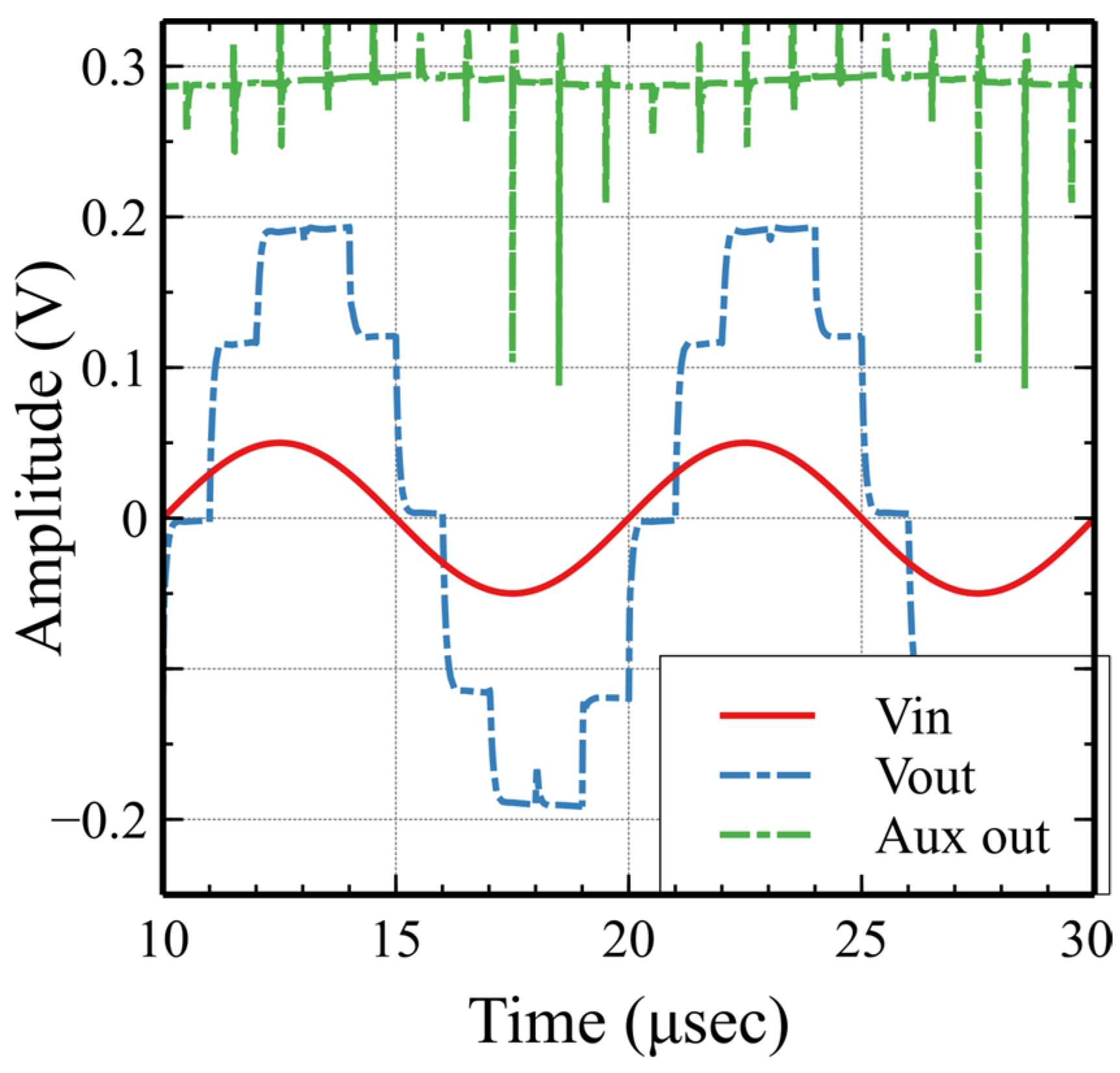

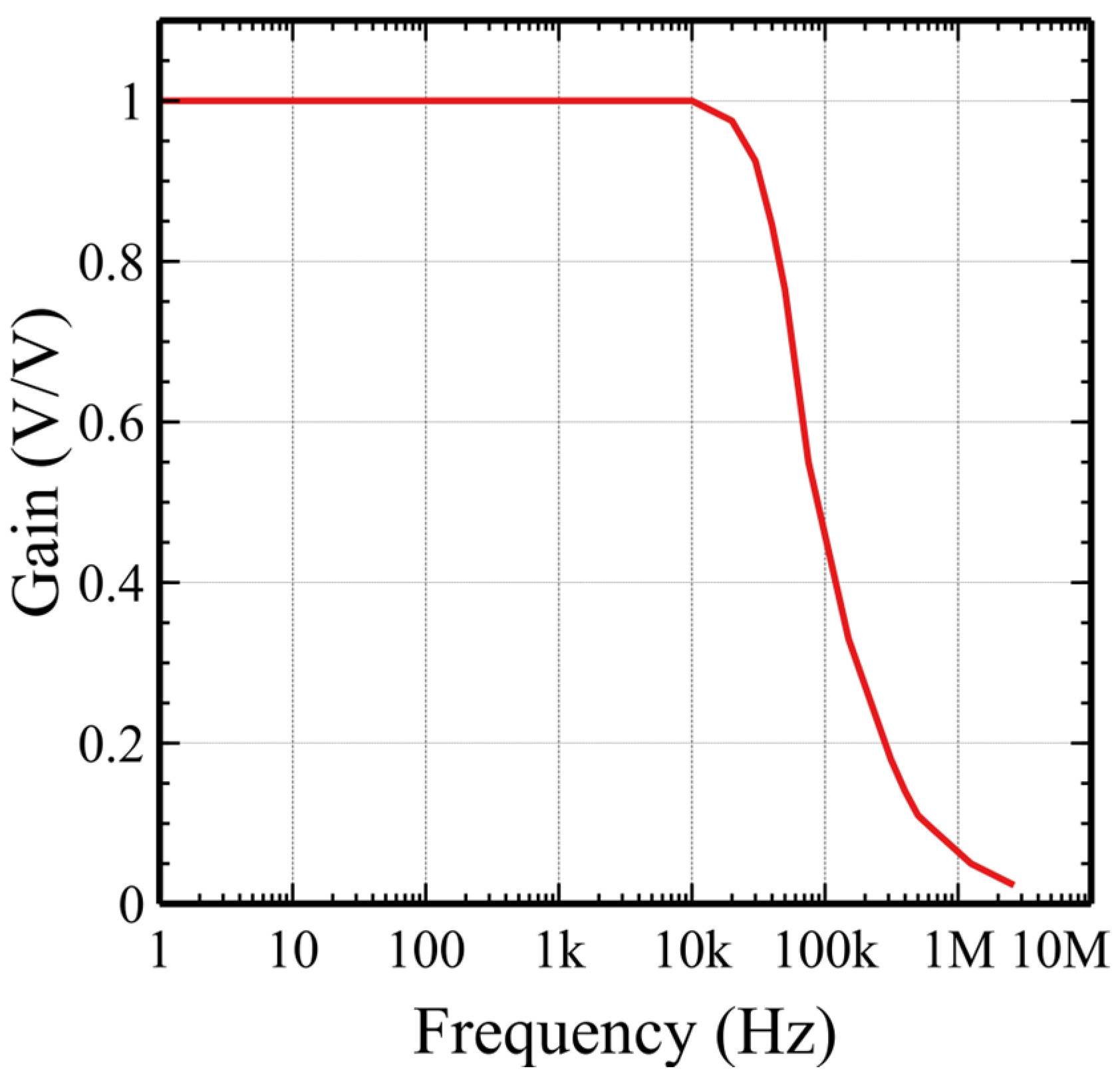

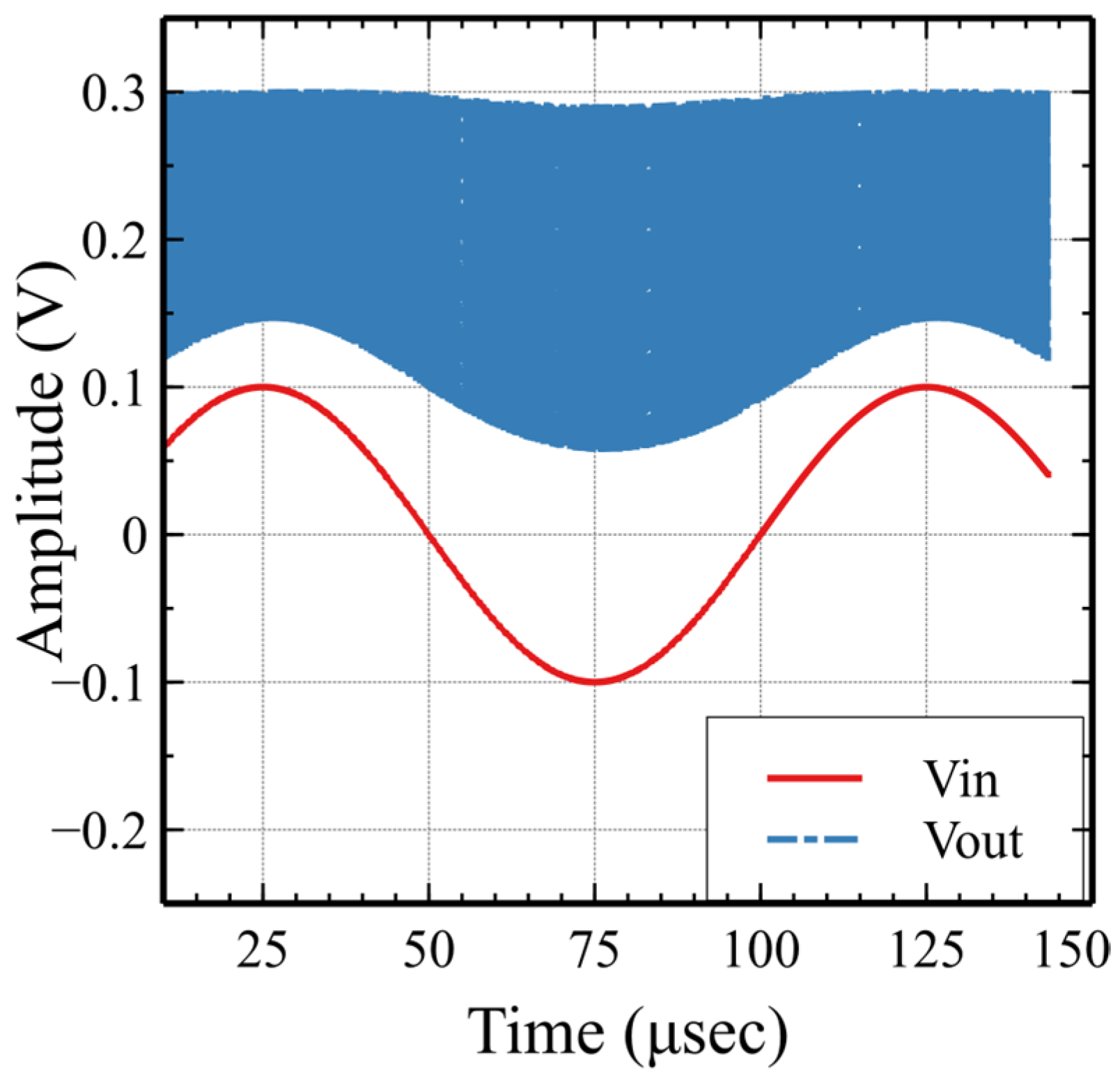

3.2. Low-Voltage SC Low-Pass Filter

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Hosticka, B.J.; Brodersen, R.W.; Gray, P.R. MOS sampled data recursive filters using switched capacitor integrators. IEEE J. Solid-State Circuits 1977, 12, 600–608. [Google Scholar] [CrossRef]

- Lee, K.-L.; Meyer, R.G. Low-distortion switched-capacitor filter design techniques. IEEE J. Solid-State Circuits 1985, SC-20, 1103–1113. [Google Scholar] [CrossRef]

- Nakayama, K.; Kuraishi, Y. Present and future applications of switched-capacitor circuits. IEEE Circuits Devices Mag. 1987, 3, 10–21. [Google Scholar] [CrossRef]

- Temes, G.; Moon, U.-K.; Allstot, D. Switched-Capacitor Circuits [Education]. IEEE Circuits Syst. Mag. 2021, 21, 40–42. [Google Scholar] [CrossRef]

- Allstot, D.J.; Moon, U.-K.; Temes, G.C. Switched-Capacitor Circuits. In Proceedings of the 2022 IEEE Custom Integrated Circuits Conference (CICC), Newport Beach, CA, USA, 24–27 April 2022; pp. 1–8. [Google Scholar]

- Gregorian, R. High-resolution switched-capacitor D/A converter. Microelectron. J. 1981, 12, 10–13. [Google Scholar] [CrossRef]

- Temes, G.C.; Haug, K. Improved offset-compensation schemes for switched-capacitor circuits. Electron. Lett. 1984, 20, 508–509. [Google Scholar] [CrossRef]

- Cabrera-Bernal, E. Performance Enhancement in the Design of Amplifier and Amplifier-Less Circuits in Modern CMOS Technologies. Ph.D. Thesis, Electronic Engineering Department Higher Technical School of Engineering, University of Seville, Seville, Spain, 18 May 2018. [Google Scholar]

- Fiorenza, J.K.; Sepke, T.; Holloway, P.; Sodini, C.G.; Lee, H.S. Comparator-based switched capacitor circuits for scaled CMOS technologies. IEEE J. Solid-State Circuits 2006, 41, 2658–2668. [Google Scholar] [CrossRef]

- Chae, Y.; Han, G. Low Voltage, Low Power, Inverter-Based Switched-Capacitor Delta-Sigma Modulator. IEEE J. Solid-State Circuits 2009, 44, 458–472. [Google Scholar] [CrossRef]

- Gagliardi, F.; Catania, A.; Piotto, M.; Bruschi, P.; Dei, M. Parallel Slew-Rate Enhancer With Current-Recycling Core for Switched-Capacitors Circuits. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 4814–4818. [Google Scholar] [CrossRef]

- Roh, J. High-Gain Class-AB OTA with Low Quiescent Current. Analog. Integr. Circuits Signal Process. 2006, 47, 225–228. [Google Scholar] [CrossRef]

- Yan, Z.; Mak, P.-I.; Law, M.-K.; Martins, R.P.; Maloberti, F. Nested-Current-Mirror Rail-to-Rail-Output Single-Stage Amplifier With Enhancements of DC Gain, GBW and Slew Rate. IEEE J. Solid-State Circuits 2015, 50, 2353–2366. [Google Scholar] [CrossRef]

- Rashtian, M.; Hashemipour, O.; Navi, K. Design of a Low-Voltage High-Speed Switched-Capacitor Filters Using Improved Auto Zeroed Integrator. J. Appl. Sci. 2008, 8, 1771–1775. [Google Scholar] [CrossRef]

- Ghasemi, R.; Charkhkar, H.; Asadi, A.; Lotfi, R.; Mafinejad, K. Design of Low-Voltage MOSFET-Only Switched-Capacitor Filters. In Proceedings of the 2005 International Conference on Microelectronics, Islamabad, Pakistan, 13–15 December 2005; pp. 24–29. [Google Scholar]

- McCarroll, B.; Sodini, C.; Lee, H.-S. A high-speed CMOS comparator for use in an ADC. IEEE J. Solid-State Circuits 1988, 23, 159–165. [Google Scholar] [CrossRef]

- Peluso, V.; Vancorenland, P.; Marques, A.M.; Steyaert, M.S.J.; Sansen, W. A 900-mV low-power Δ∑ A/D converter with 77-dB dynamic range. IEEE J. Solid-State Circuits 1998, 33, 1887–1897. [Google Scholar] [CrossRef]

- Bidari, E.; Keskin, M.; Maloberti, F.; Moon, U.; Steensgaard, J.; Temes, G.C. Low-voltage switched-capacitor circuits. In Proceedings of the 1999 IEEE International Symposium on Circuits and Systems (ISCAS), Orlando, FL, USA, 30 May–2 June 1999; pp. 49–52. [Google Scholar]

- Dessouky, M.; Kaiser, A. Rail-to-rail operation of very low voltage CMOS switched-capacitor circuits. In Proceedings of the 1999 IEEE International Symposium on Circuits and Systems (ISCAS), Orlando, FL, USA, 30 May–2 June 1999; pp. 144–147. [Google Scholar]

- Ramirez-Angulo, J.; Holmes, M. Simple technique using local CMFB to enhance slew rate and bandwidth of one-stage CMOS op-amps. Electron. Lett. 2002, 38, 1409–1411. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Carvajal, R.G.; Galan, J.A.; Lopez-Martin, A. A free but efficient low-voltage class-AB two-stage operational amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2006, 53, 568–571. [Google Scholar] [CrossRef]

- Pourashraf, S.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G. Super Class-AB OTA without open-loop gain degradation based on dynamic cascode biasing. Int. J. Circuit Theory Appl. (IJCTA) 2017, 45, 2111–2118. [Google Scholar] [CrossRef]

- Cabrera-Bernal, E.; Pennisi, S.; Grasso, A.D.; Torralba, A.; Carvajal, R.G. 0.7-V Three-Stage Class-AB CMOS Operational Transconductance Amplifier. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1807–1815. [Google Scholar] [CrossRef]

- Akbari, M. Single-stage fully recycling folded cascode OTA for switched-capacitor circuits. Electron. Lett. 2015, 51, 977–979. [Google Scholar] [CrossRef]

- Abdelfattah, O.; Roberts, G.W.; Shih, I.; Shih, Y.C. An ultra-low-voltage CMOS process-insensitive self-biased OTA with rail-to-rail input range. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2380–2390. [Google Scholar] [CrossRef]

- Meng, X.; Temes, G.C. Bootstrapping techniques for floating switches in switched-capacitor circuits. In Proceedings of the 2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS), College Station, TX, USA, 3–6 August 2014; pp. 398–401. [Google Scholar]

| Parameters | [22] 2017 | [23] 2016 | [24] 2015 | [25] 2015 | Class AB Miller Op-Amp | This Work With Enhanced Class AB Miller Op-Amp |

|---|---|---|---|---|---|---|

| CMOS Tech. Process (nm) | 180 | 180 | 90 | 65 | 180 | 180 |

| Configuration | SE | SE a | FD b | SE a | SE a | SE a |

| Supply (V) | ±0.9 | 0.7 | 1.2 | 0.35 | ±0.35 | ±0.35 |

| VDDP (V) | - | - | - | 0.27 | 0.27 | |

| Ibias (uA) | 1 | 4 | - | - | 10 | 10 |

| Isupply (uA) | 8 | 36.28 | 483.33 | 49 | 40 | 60 |

| Pdiss (uW) | 14.5 | 25.4 | 580 | 17.15 | 28 | 43.4 |

| AOLDC (dB) | 67 | 57.5 | 59.1 | 43 | 49 | 56 |

| CL (pF) | 20 | 20 | 5 | 3 | 20 | 20 |

| CC (pF) | 0.58 c | - | 0.6 c | 2 | 2 | |

| RC (kOhm) | - | - | - | 15 | 32 | |

| SR (V/us) | 24.11 | 1.8 | 115.2 | 5.6 | 0.8 | 9.41 |

| GB (MHz) | 0.57 | 3 | 650 | 3.6 | 5.72 | 23 |

| PM (o) | 82 | 60 | 50 | 56 | 63 | 45 |

| FOMLS ([V/us*pF/mW]) | 37,300 | 2200 | 990 | 980 | 571 | 4376 |

| FOMSS (MHz*pF/mW) | 900 | 2.360 | 5600 | 630 | 4085 | 10,698 |

| FOMGlobal | 5794 | 2278 | 2354 | 785 | 1527 | 6842 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rico-Aniles, H.D.; Paul, A.; Ramirez-Angulo, J.; Lopez-Martin, A.; Carvajal, R.G. 0.7 V Supply SC Circuits with Relaxed Slew Rate Requirements Using GB-Enhanced Multiple-Output Class AB/AB Op-Amps. J. Low Power Electron. Appl. 2025, 15, 24. https://doi.org/10.3390/jlpea15020024

Rico-Aniles HD, Paul A, Ramirez-Angulo J, Lopez-Martin A, Carvajal RG. 0.7 V Supply SC Circuits with Relaxed Slew Rate Requirements Using GB-Enhanced Multiple-Output Class AB/AB Op-Amps. Journal of Low Power Electronics and Applications. 2025; 15(2):24. https://doi.org/10.3390/jlpea15020024

Chicago/Turabian StyleRico-Aniles, Hector Daniel, Anindita Paul, Jaime Ramirez-Angulo, Antonio Lopez-Martin, and Ramon G. Carvajal. 2025. "0.7 V Supply SC Circuits with Relaxed Slew Rate Requirements Using GB-Enhanced Multiple-Output Class AB/AB Op-Amps" Journal of Low Power Electronics and Applications 15, no. 2: 24. https://doi.org/10.3390/jlpea15020024

APA StyleRico-Aniles, H. D., Paul, A., Ramirez-Angulo, J., Lopez-Martin, A., & Carvajal, R. G. (2025). 0.7 V Supply SC Circuits with Relaxed Slew Rate Requirements Using GB-Enhanced Multiple-Output Class AB/AB Op-Amps. Journal of Low Power Electronics and Applications, 15(2), 24. https://doi.org/10.3390/jlpea15020024