A 1.93-pJ/Bit PCI Express Gen4 PHY Transmitter with On-Chip Supply Regulators in 28 nm CMOS

Abstract

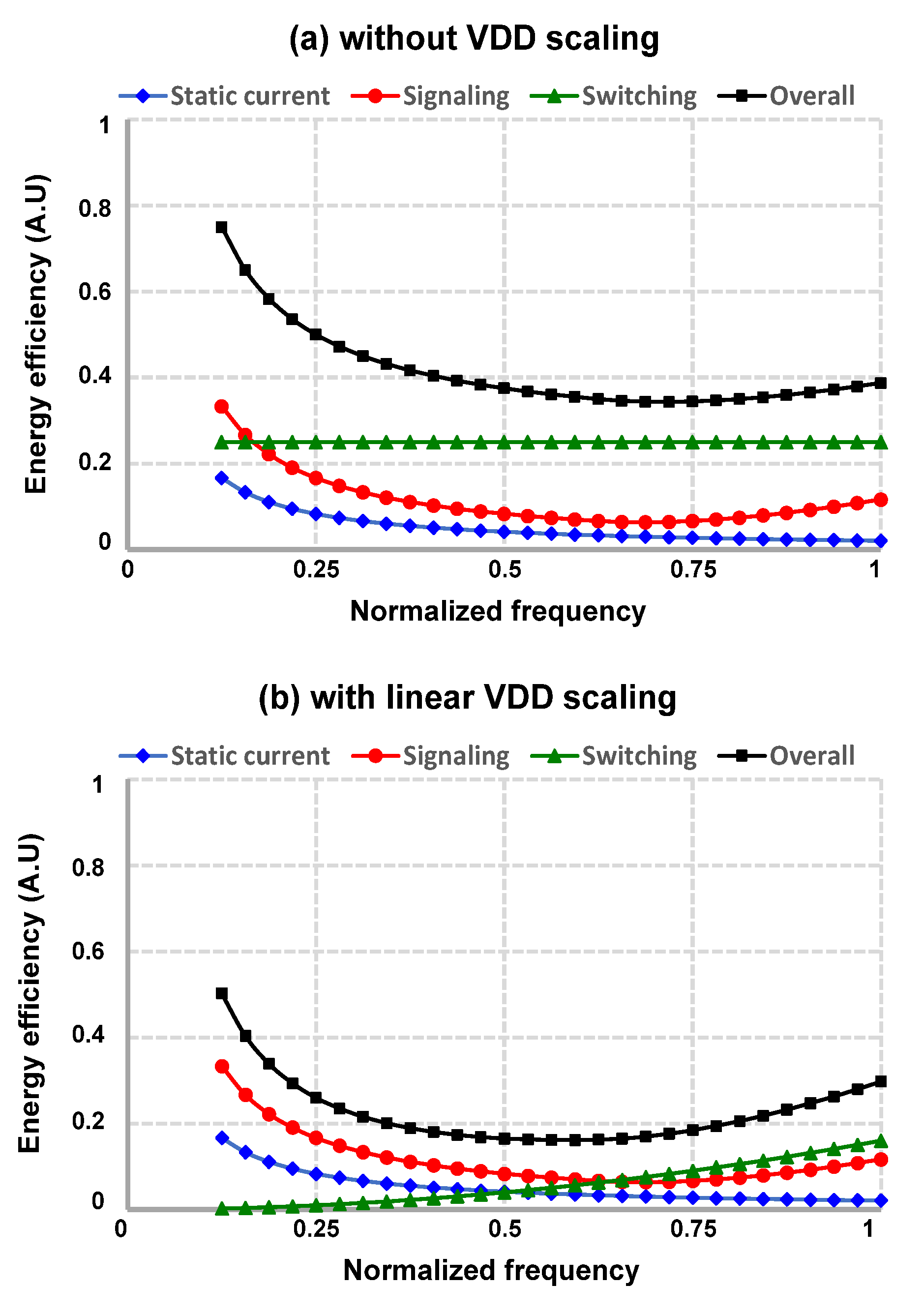

1. Introduction

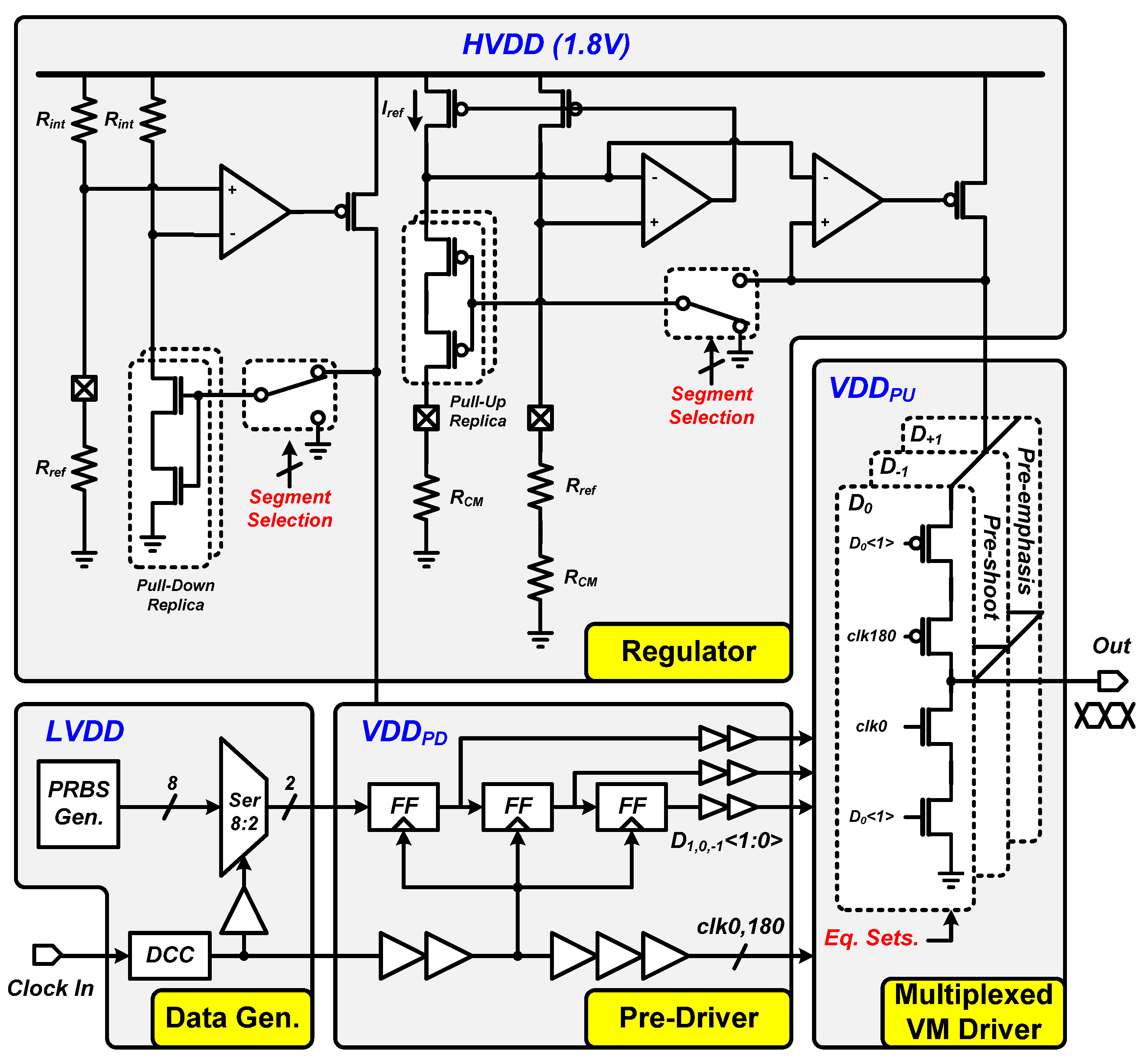

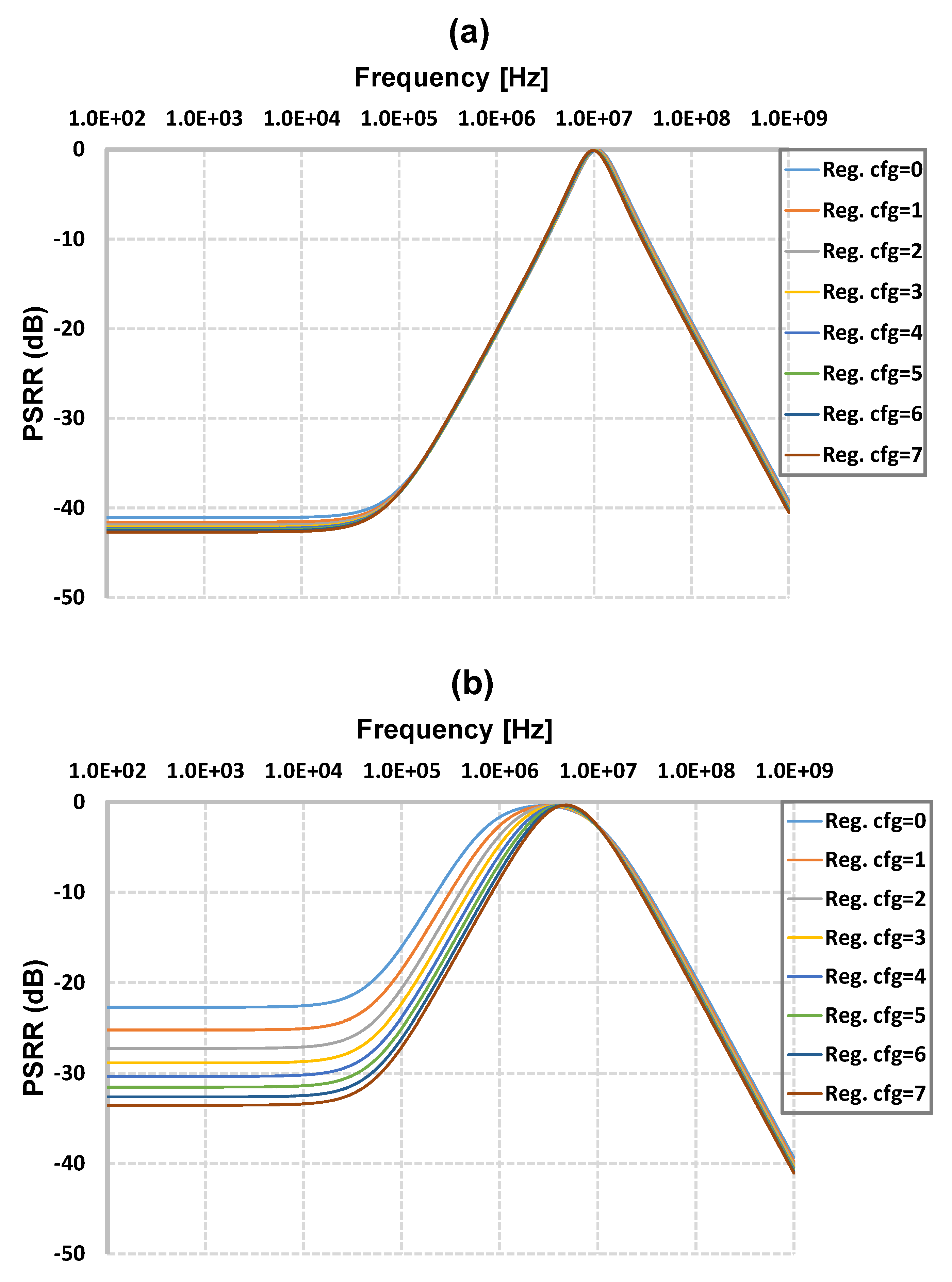

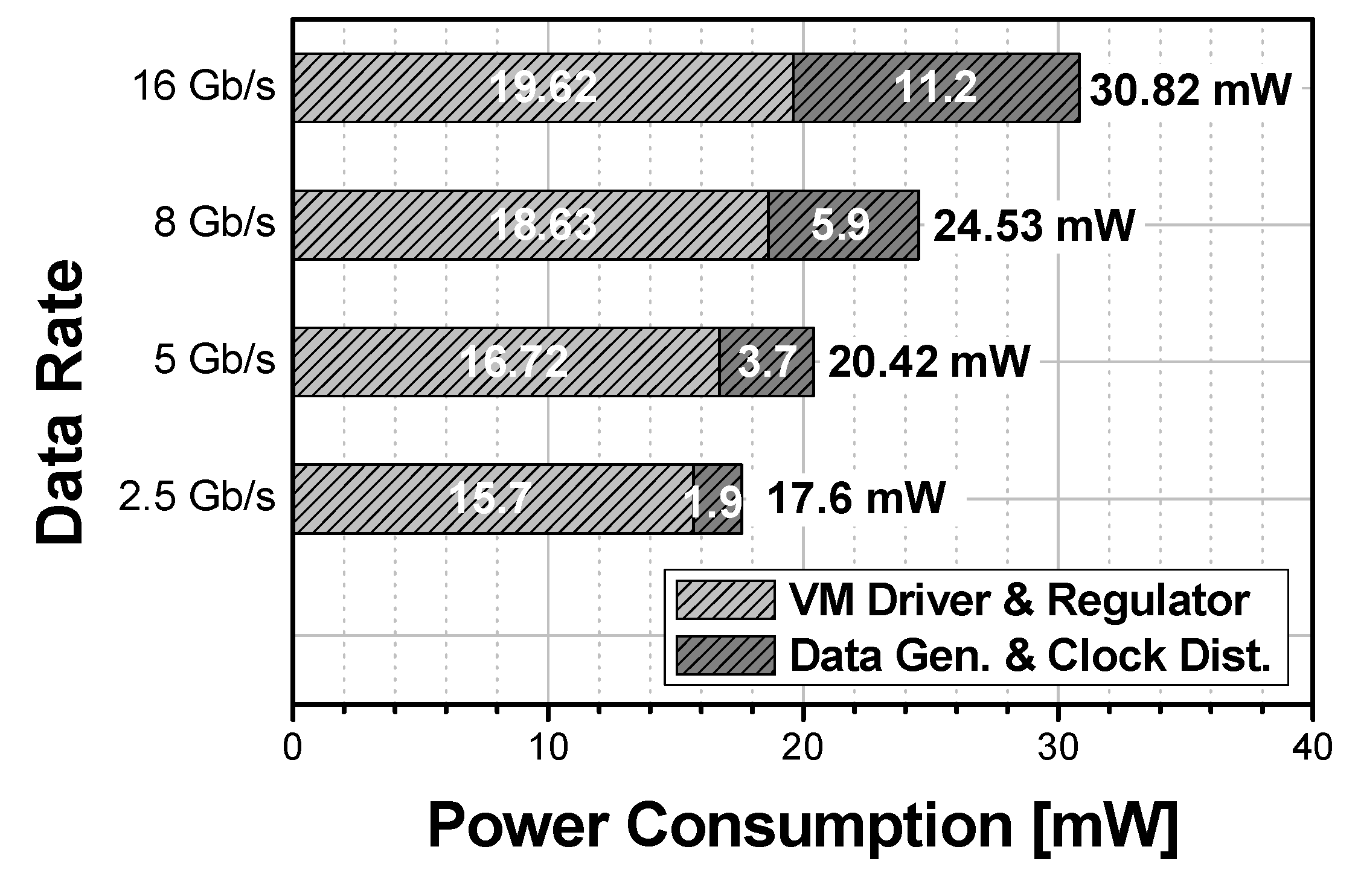

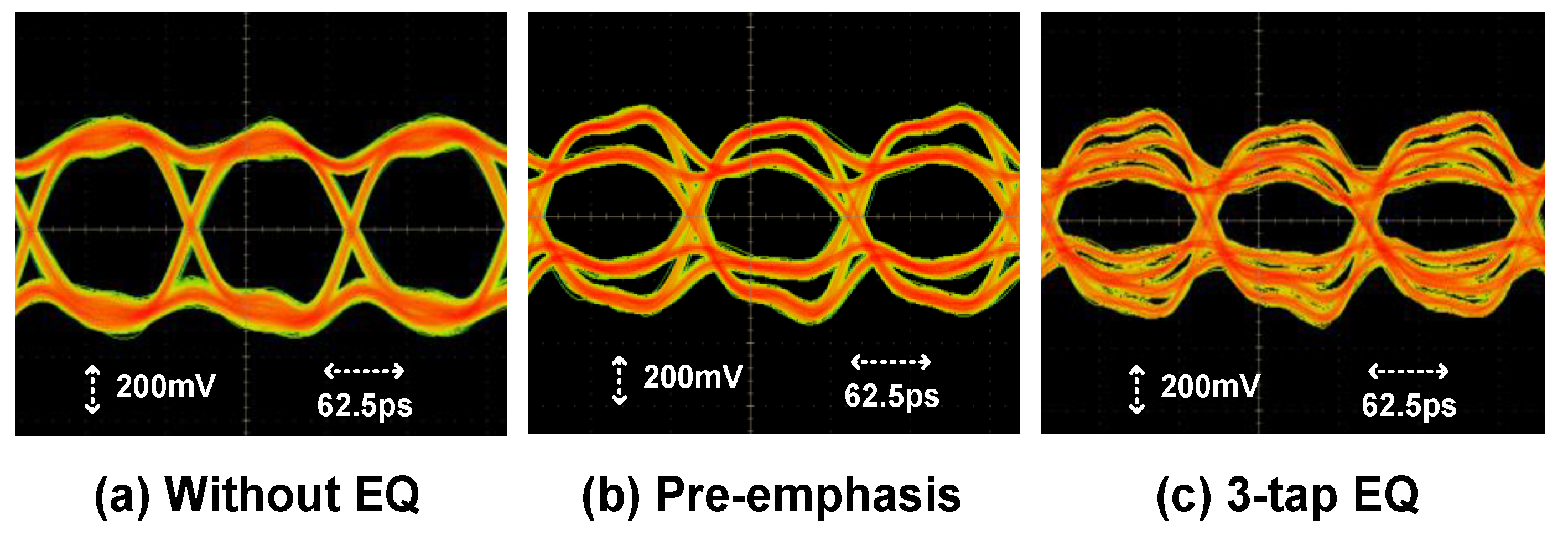

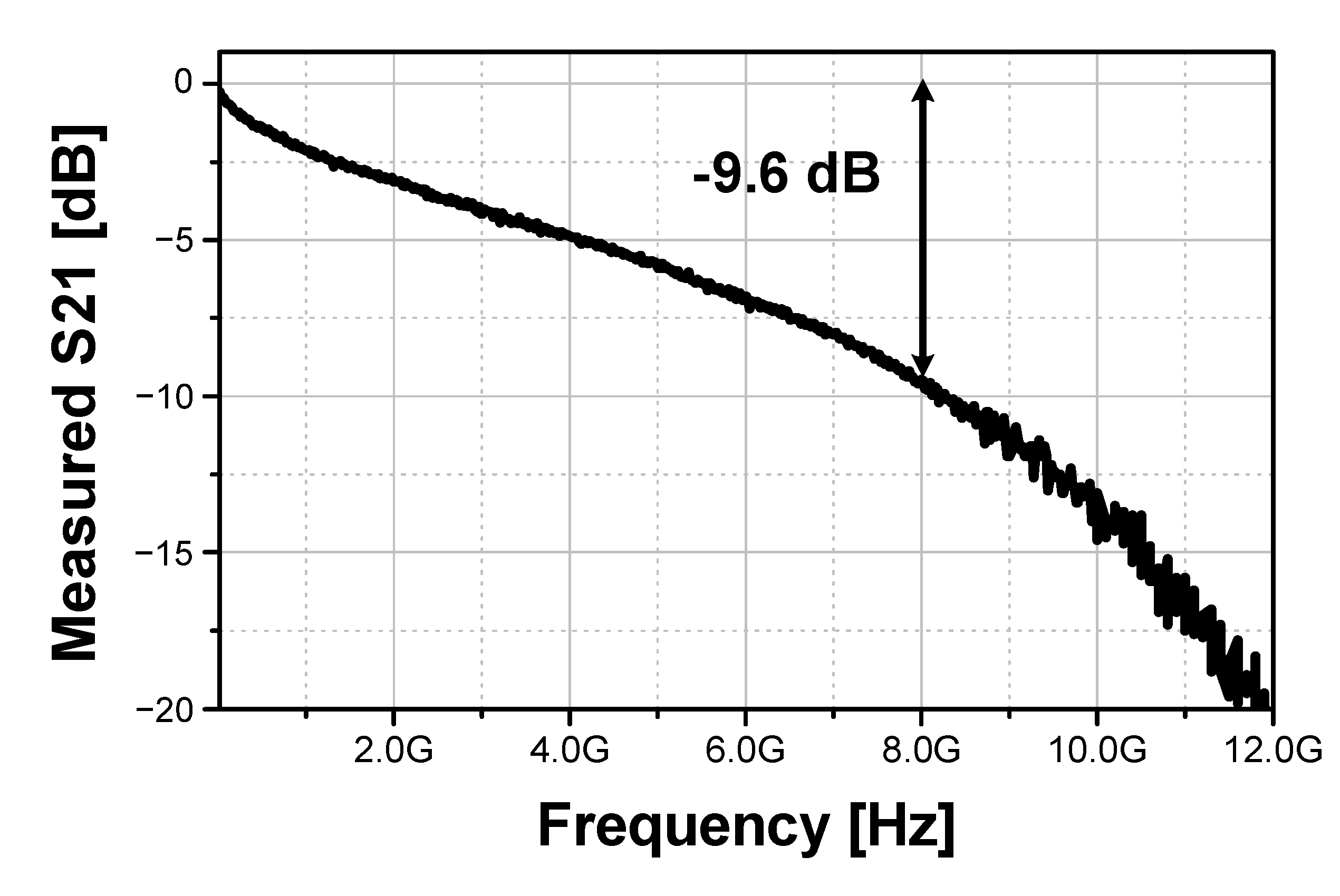

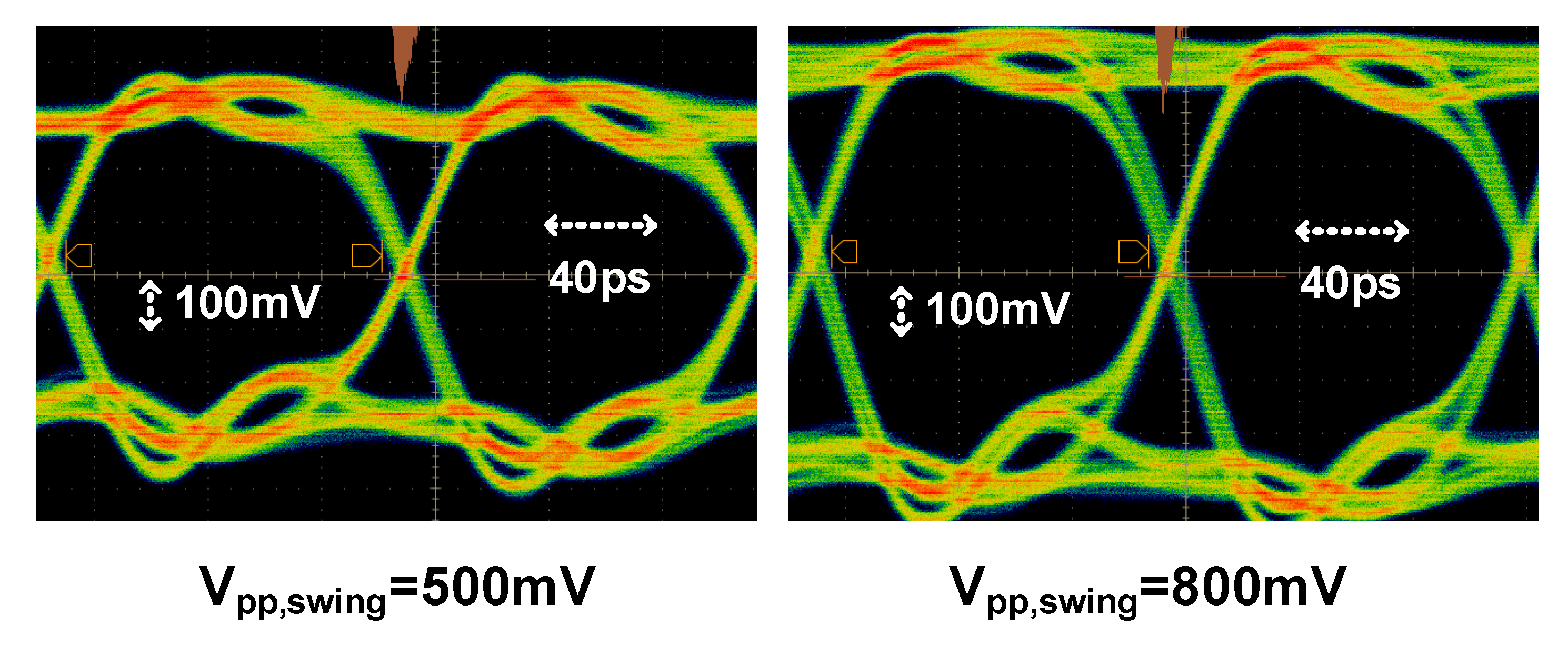

2. Implementation of the Proposed PCIe Gen4 Transmitter

3. Measurement Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Daly, D.C.; Fujino, L.C.; Smith, K.C. Through the Looking Glass-The 2018 Edition: Trends in Solid-State Circuits from the 65th ISSCC. IEEE Solid State Circuits Mag. 2018, 10, 30–46. [Google Scholar] [CrossRef]

- Li, S.; Spagna, F.; Chen, J.; Wang, X.; Tong, L.; Gowder, S.; Jia, W.; Lyer, S.; Song, R.; Li, L.; et al. A Power and Area Efficient 2.5–16 Gbps Gen4 PCIe PHY in 10 nm FinFET CMOS. In Proceedings of the 2018 IEEE Asian Solid-State Circuits Conference (A-SSCC), Tainan, Taiwan, 5–7 November 2018; pp. 5–8. [Google Scholar]

- Shang, L.; Peh, L.-S.; Jha, N.K. Dynamic Voltage Scaling with Links for Power Optimization of Interconnection Networks. In Proceedings of the International Symposium on High.-Performance Computer Architecture (HPCA), Anaheim, CA, USA, 12 February 2003; pp. 91–102. [Google Scholar]

- Shin, D.; Kim, J. Power-Aware Communication Optimization for Networks-On-Chips with Voltage Scalable Links. In Proceedings of the IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis, Stockholm, Sweden, 8–10 September 2004; pp. 170–175. [Google Scholar]

- Barroso, L.A.; Hölzle, U. The Case for Energy-Proportional Computing. Computer 2007, 40, 33–37. [Google Scholar] [CrossRef]

- Abts, D.; Marty, M.R.; Wells, P.M.; Klausler, P.; Liu, H. Energy Proportional Datacenter Networks. In Proceedings of the International Symposium on Computer Architecture (ISCA), Saint Malo, France, 19–23 June 2010; pp. 338–347. [Google Scholar]

- Shu, G.; Choi, W.; Saxena, S.; Kim, S.; Talegaonkar, M.; Nandwana, R.; Wei, D.; Nandi, T. A 16Mb/s-to-8Gb/s 14.1-to-5.9pJ/b Source Synchronous Transceiver Using DVFS and Rapid On/Off in 65 nm CMOS. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 398–399. [Google Scholar]

- Ramachandran, A.; Anand, T. A 0.5-to-0.9V, 3-to-16Gb/s, 1.6-to-3.1pJ/b Wireline Transceiver Equalizing 27dB Loss at 10Gb/s with Clock-Domain Encoding Using Integrated Pulse-Width Modulation (iPWM) in 65nm CMOS. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 268–269. [Google Scholar]

- Wei, G.-Y.; Kim, J.; Liu, D.; Sidiropoulos, S.; Horowitz, M.A. A variable-frequency parallel I/O interface with adaptive power-supply regulation. IEEE J. Solid State Circuits 2000, 35, 1600–1610. [Google Scholar]

- Kim, J.; Horowitz, M.A. Adaptive supply serial links with sub-1-V operation and per-pin clock recovery. IEEE J. Solid State Circuits 2002, 37, 1403–1413. [Google Scholar] [CrossRef]

- Balamurugan, G.; Kennedy, J.; Banerjee, G.; Jaussi, J.E.; Mansuri, M. A scalable 5-15 Gbps, 14-75 mW low-power I/O transceiver in 65 nm CMOS. IEEE J. Solid State Circuits 2008, 43, 1010–1019. [Google Scholar] [CrossRef]

- Bae, W.; Ju, H.; Park, K.; Han, J.; Jeong, D. A Supply-Scalable Serializing Transmitter with Controllable Output Swing and Equalization for Next Generation Standards. IEEE Trans. Ind. Electron. 2018, 65, 5979–5989. [Google Scholar] [CrossRef]

- Mansuri, M.; Jaussi, J.E.; Kennedy, J.T.; Hsueh, T.-C.; Shekhar, S.; Balamurugan, G.; Robarts, F.; Casper, P. A Scalable 0.128–1 Tb/s, 0.8–2.6 pJ/bit, 64-Lane Parallel I/O in 32-nm CMOS. IEEE J. Solid State Circuits 2013, 48, 3229–3242. [Google Scholar] [CrossRef]

- Chen, X.; Wei, G.; Peh, L.-S. Design of Low-Power Short-Distance Opto-Electronic Transceiver Front-Ends with Scalable Supply Voltages and Frequencies. In Proceedings of the 2008 International Symposium on Low Power Electronics & Design, Bangalore, India, 11–13 August 2008; pp. 277–282. [Google Scholar]

- Chang, K.-Y.K.; Wei, J.; Huang, C.; Li, S.; Donnelly, K.; Horowitz, M.; Li, Y.; Sidiropoulos, S. A 0.4–4-Gb/s CMOS Quad Transceiver Cell Using On-Chip Regulated Dual-Loop PLLs. IEEE J. Solid State Circuits 2003, 38, 747–754. [Google Scholar] [CrossRef]

- Eble, J.C.; Best, S.; Leibowitz, B.; Luo, L.; Palmer, R.; Wilson, J.; Zerbe, J.; Amirkhany, A.; Nguyen, N. Power-Efficient I/O Design Considerations for High-Bandwidth Applications. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 19–21 September 2011; pp. 1–4. [Google Scholar]

- Bae, W. Supply-Scalable High-Speed I/O Interfaces. Electronics 2020, 9, 1315. [Google Scholar] [CrossRef]

- Bohr, M.T.; Young, I.A. CMOS Scaling Trends and Beyond. IEEE Mirco 2017, 37, 20–29. [Google Scholar] [CrossRef]

- Chen, S.; Zhou, L.; Zhuang, I.; Im, J.; Melek, D.; Namkoong, J.; Raj, M.; Shin, J.; Frans, Y.; Chang, K. A 4-to-16 GHz inverter-based injection-locked quadrature clock generator with phase interpolators for multi-standard I/Os in 7 nm FinFET. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 390–392. [Google Scholar]

- Ker, M.D. Whole-chip ESD protection design with efficient VDD-to-VSS ESD clamp circuits for submicron CMOS VLSI. IEEE Trans. Electron. Devices 1999, 46, 173–183. [Google Scholar]

- Vashchenko, V.A.; Scholz, M.; Jansen, P.; Peterson, R.; Natarajan, M.I.; Tremouilles, D.; Sawada, M.; Nakaei, T.; Hasebe, T.; Beek, T.; et al. Turn-off characteristics of the CMOS snapback ESD protection devices-new insights and its implications. In Proceedings of the 2006 Electrical Overstress/Electrostatic Discharge Symposium, Anaheim, CA, USA, 10–15 September 2006; pp. 39–45. [Google Scholar]

- Bae, W.; Ju, H.; Park, K.; Cho, S.; Jeong, D. A 7.6 mW, 414 fs RMS-Jitter 10 GHz Phase-Locked Loop for a 40 Gb/s Serial Link Transmitter Based on a Two-Stage Ring Oscillator in 65 nm CMOS. IEEE J. Solid State Circuits 2016, 51, 2357–2367. [Google Scholar] [CrossRef]

- Savoj, J.; An, F.; Gong, J.; Im, J.; Jiang, X.; Jose, A.; Kireev, V.; Lim, S.; Roldan, A.; Turker, D.Z.; et al. A Low-Power 0.5–6.6 Gb/s Wireline Transceiver Embedded in Low-Cost 28 nm FPGAs. IEEE J. Solid State Circuits 2013, 48, 2582–2594. [Google Scholar] [CrossRef]

- Bae, W. CMOS Inverter as Analog Circuit: An Overview. J. Low Power Electron. Appl. 2019, 9, 26. [Google Scholar] [CrossRef]

- Menolfi, C.; Toifl, T.; Buchmann, P.; Kossel, M.; Morf, T.; Weiss, J.; Schmatz, M. A 16Gb/s Source-Series Terminated Transmitter in 65nm CMOS SOI. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2007; pp. 446–614. [Google Scholar]

- Bae, W.; Jeong, D.-K. Analysis and Design of CMOS Clocking Circuit for Low Phase Noise; Institute of Engineering and Technology: London, UK, 2020. [Google Scholar]

| Process (nm) | Min. Rate (Gb/s) | Max. Rate (Gb/s) | Equalizer | Clocking | Supply Scaling | Min. TX Swing (Vppd) | Max. TX Swing (Vppd) | Power (mW) @Max Rate | Area (mm2) | FoM (pJ/bit) @Max Rate | |

|---|---|---|---|---|---|---|---|---|---|---|---|

| [7] | 65 | 3 | 8 | 3-tap FFE (feed-forward equalizer) | Half rate | DC–DC + regulator | N/A | N/A | 38.4 | N/A | 4.8 |

| [8] | 65 | 3 | 16 | PWM (pulse-width modulation) | Quarter rate | External source | N/A | N/A | 38.78 | N/A | 2.42 |

| [9] | 350 | 0.2 | 0.8 | None | Half rate | DC–DC | 0.1 | 0.15 | 21.5 | N/A | 26.875 |

| [10] | 250 | 0.65 | 5 | None | 1/5 rate | DC–DC | 0.1 | 0.3 | 216.6 | N/A | 43.3 |

| [11] | 65 | 5 | 15 | 3-tap FFE | Half rate | External source | 0.1 | 0.72 | 34 | 0.033 | 2.3 |

| [12] | 65 | 5 | 32 | 2-tap FFE | Quarter rate | On-chip regulator | 0.4 | 1.3 | 87.7 | 0.17 | 2.74 |

| [13] | 32 | 2 | 16 | 3-tap FFE | Quarter rate | External source | 0.36 | 0.5 | 25 | 0.014 | 1.56 |

| This work | 28 | 2.5 | 16 | 3-tap FFE | Half rate | On-chip regulator | 0.5 | 0.8 | 30.82 | 0.023 | 1.93 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bae, W.; Cho, S.-Y.; Jeong, D.-K. A 1.93-pJ/Bit PCI Express Gen4 PHY Transmitter with On-Chip Supply Regulators in 28 nm CMOS. Electronics 2021, 10, 68. https://doi.org/10.3390/electronics10010068

Bae W, Cho S-Y, Jeong D-K. A 1.93-pJ/Bit PCI Express Gen4 PHY Transmitter with On-Chip Supply Regulators in 28 nm CMOS. Electronics. 2021; 10(1):68. https://doi.org/10.3390/electronics10010068

Chicago/Turabian StyleBae, Woorham, Sung-Yong Cho, and Deog-Kyoon Jeong. 2021. "A 1.93-pJ/Bit PCI Express Gen4 PHY Transmitter with On-Chip Supply Regulators in 28 nm CMOS" Electronics 10, no. 1: 68. https://doi.org/10.3390/electronics10010068

APA StyleBae, W., Cho, S.-Y., & Jeong, D.-K. (2021). A 1.93-pJ/Bit PCI Express Gen4 PHY Transmitter with On-Chip Supply Regulators in 28 nm CMOS. Electronics, 10(1), 68. https://doi.org/10.3390/electronics10010068