Design and Implementation of RF Front-End Module Based on 3D Heterogenous-Integrated Wafer-Level Packaging

Abstract

:1. Introduction

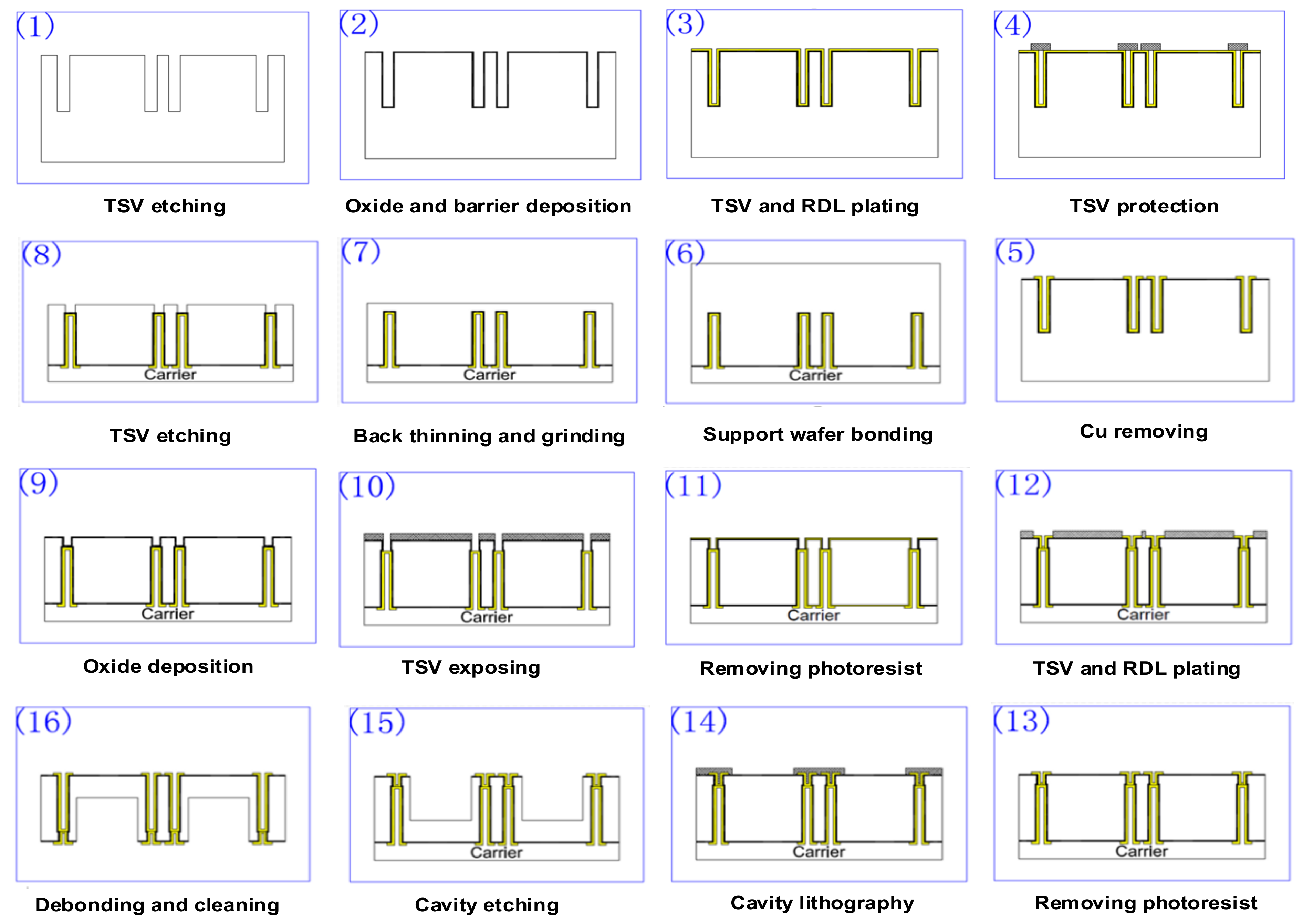

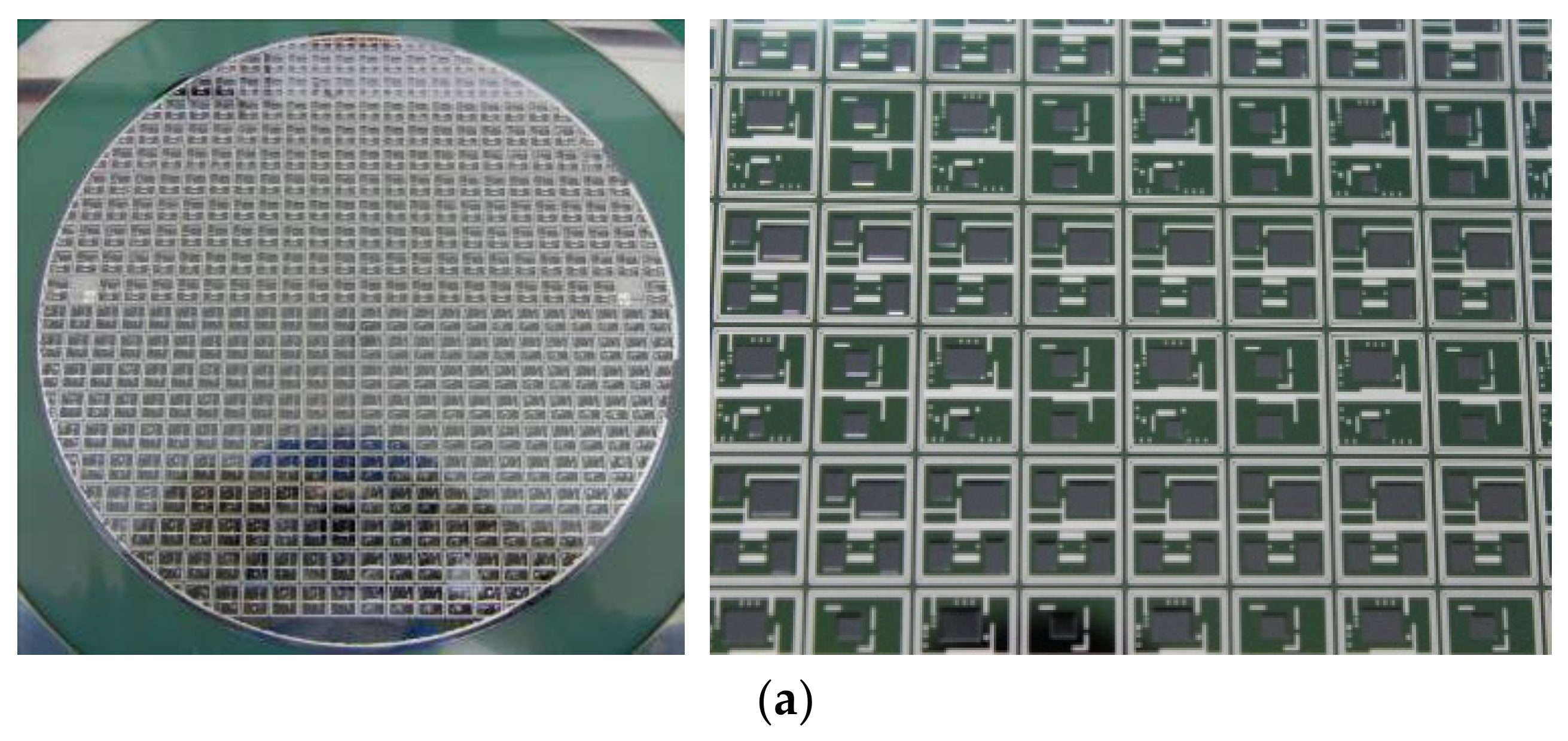

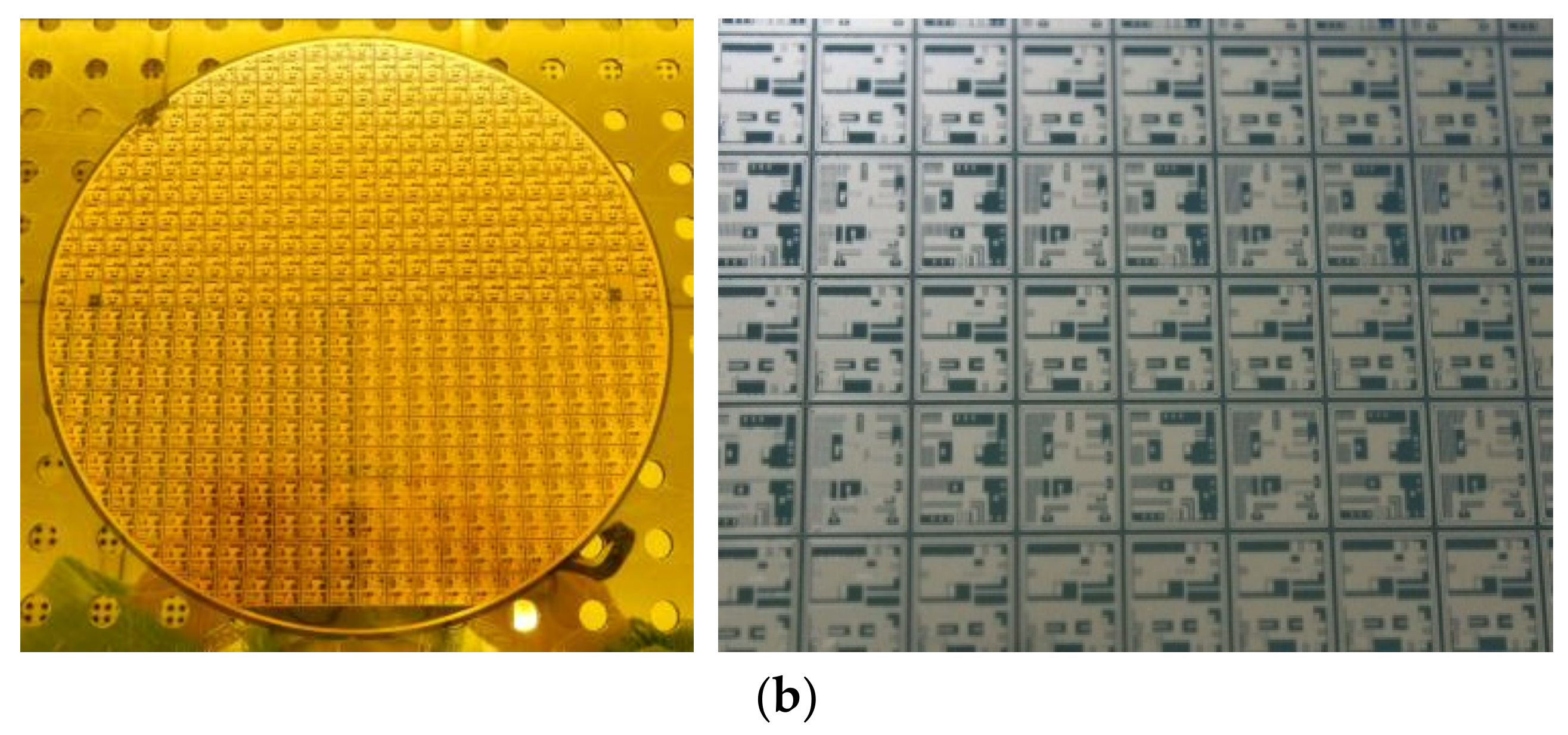

2. Process Flow of the 3DHI WLP

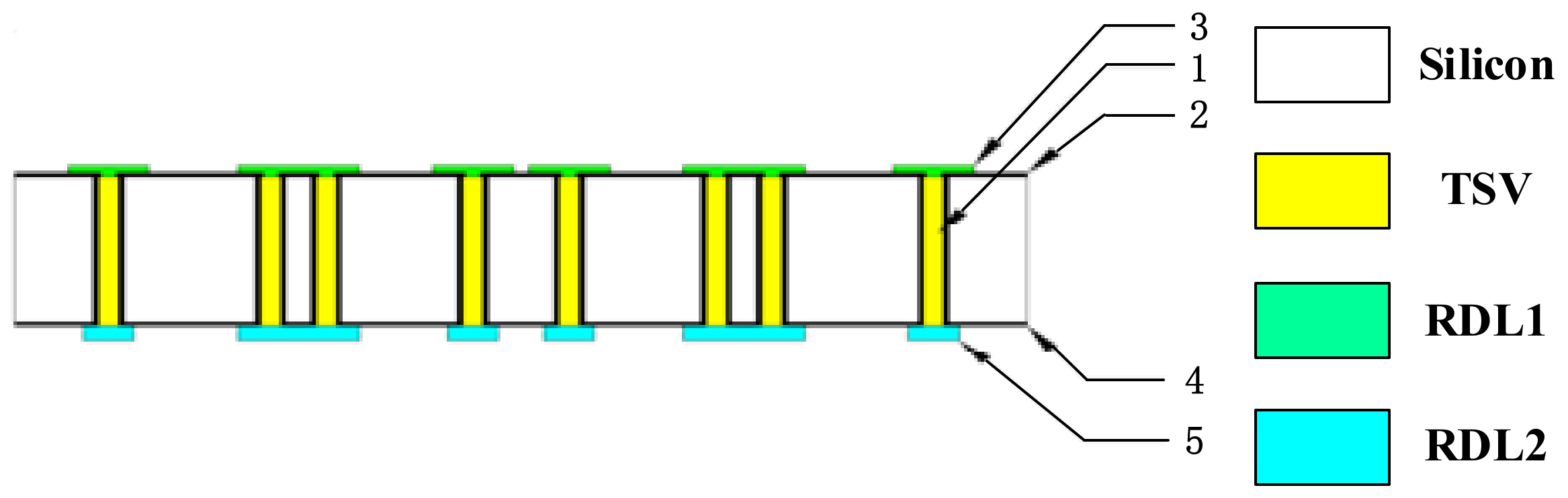

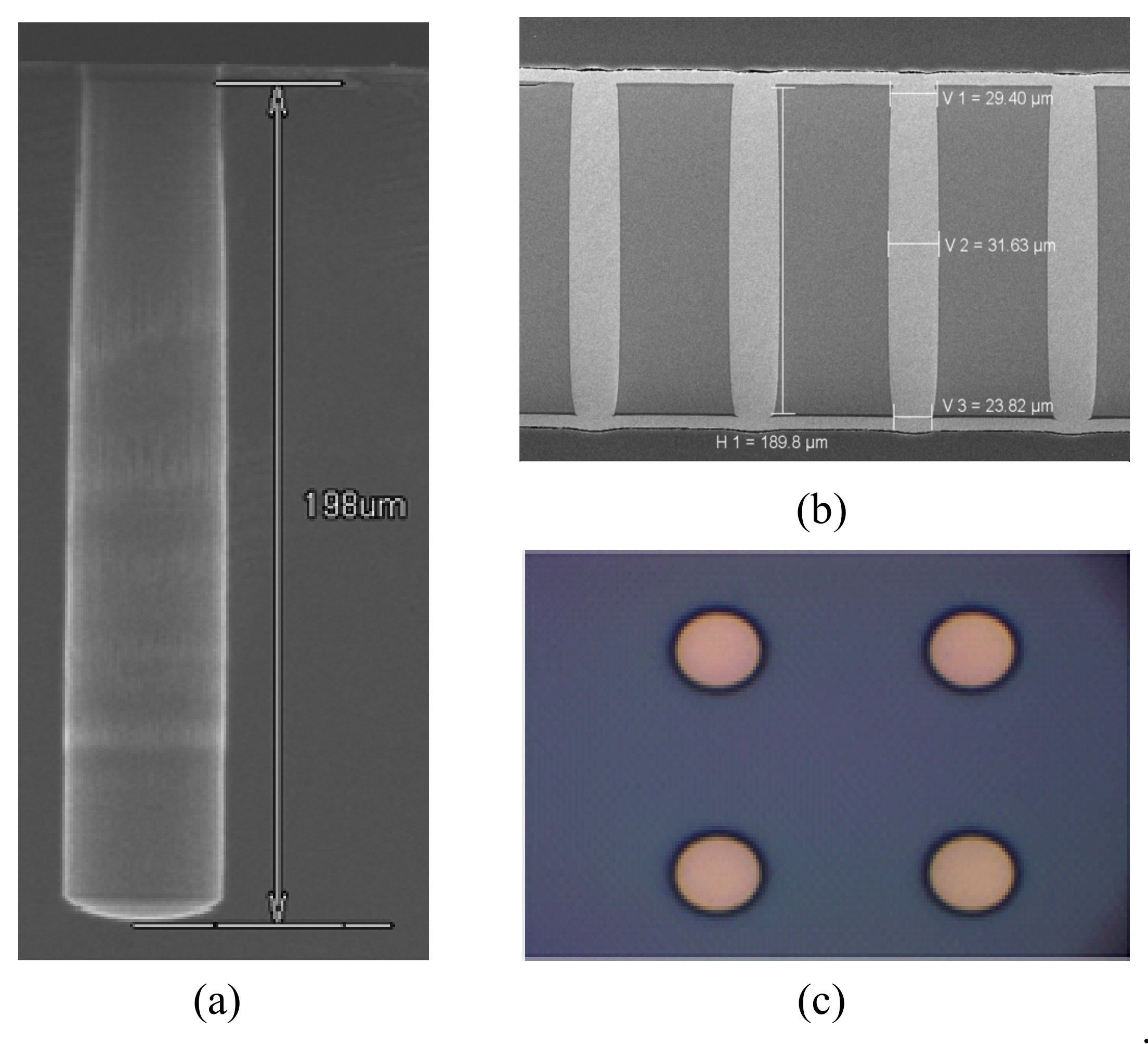

2.1. Process of the Bottom Interposer Wafer

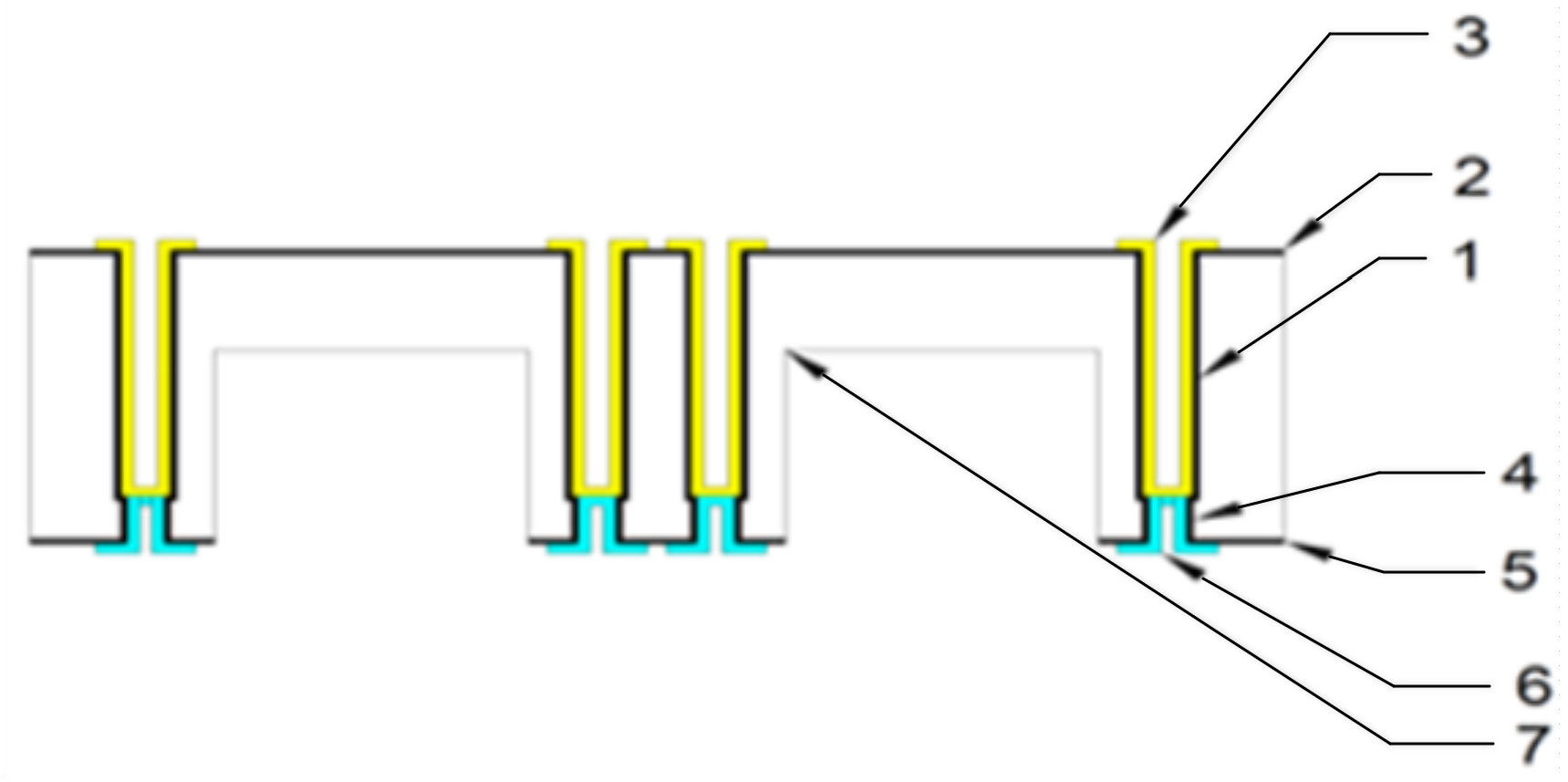

2.2. Process of the Cap Interposer Wafer

2.3. Chip Embedding with W2W Bonding

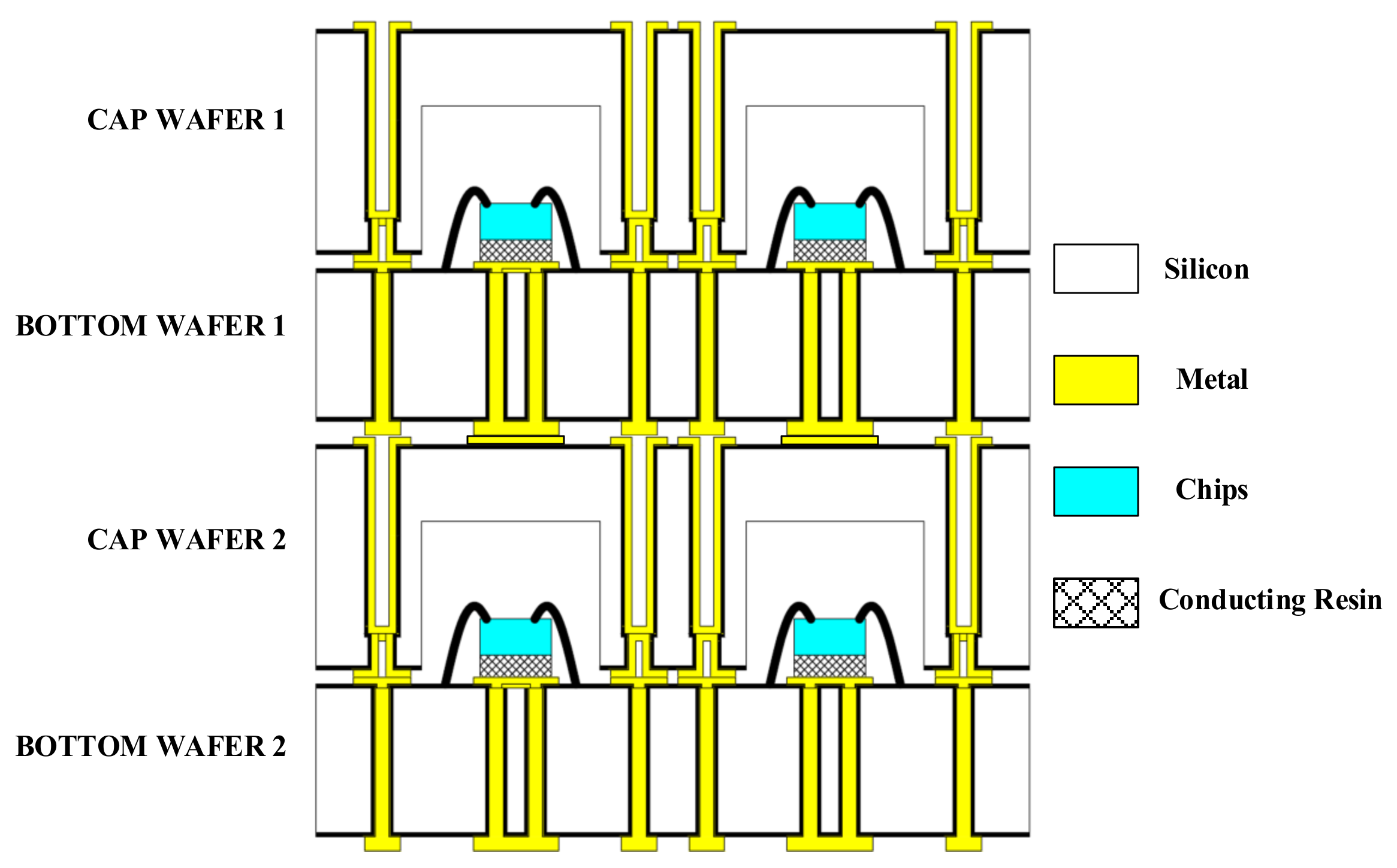

2.4. Assemblies Stacking with C2C Bonding

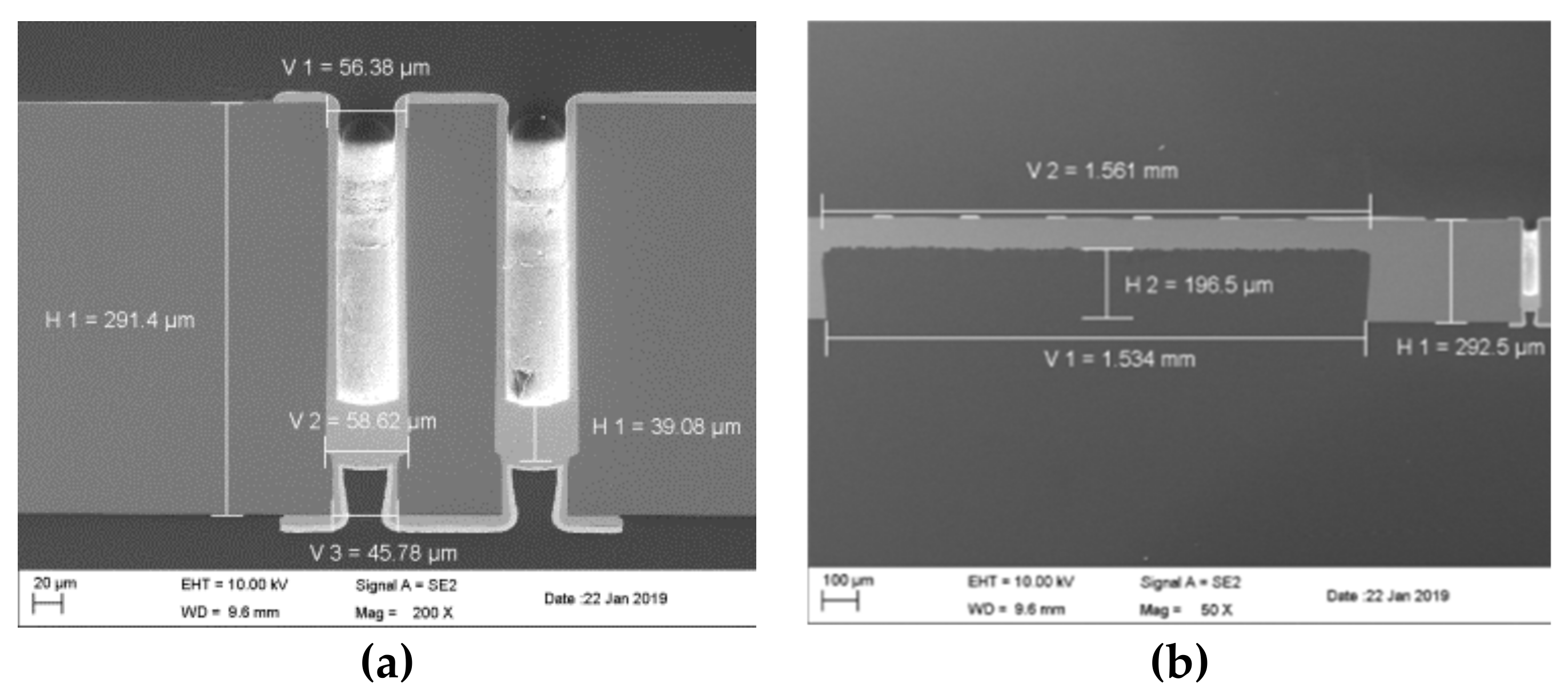

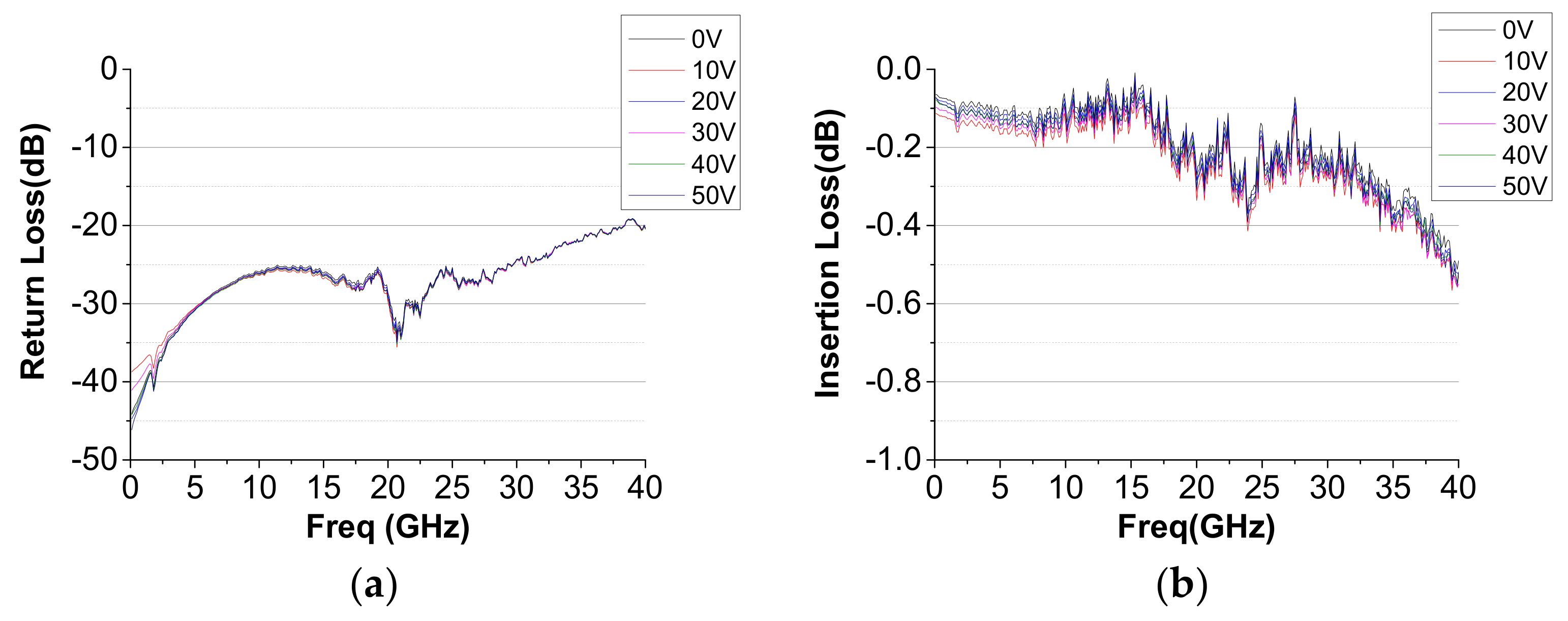

2.5. Process Verification by PCM Test

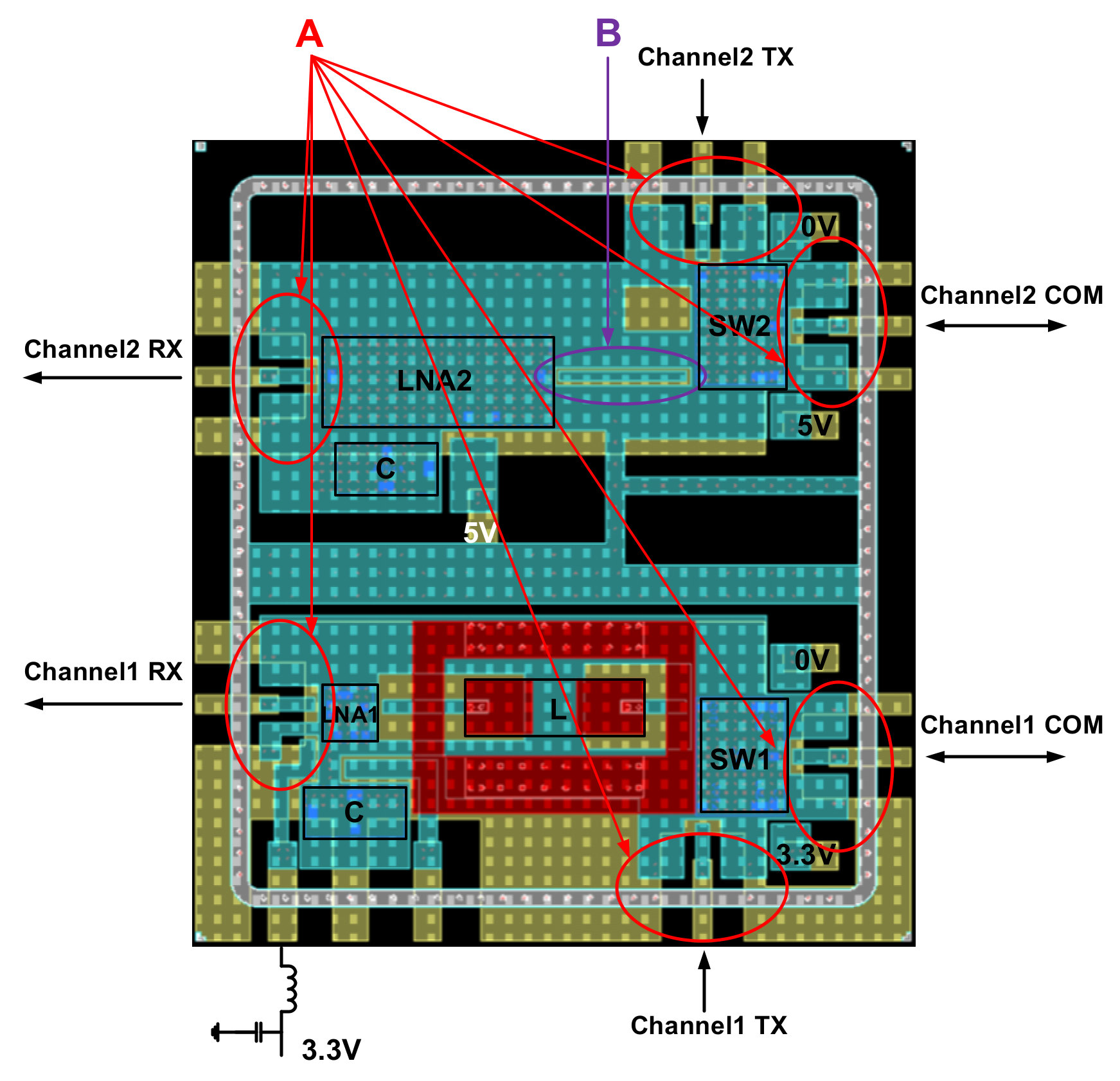

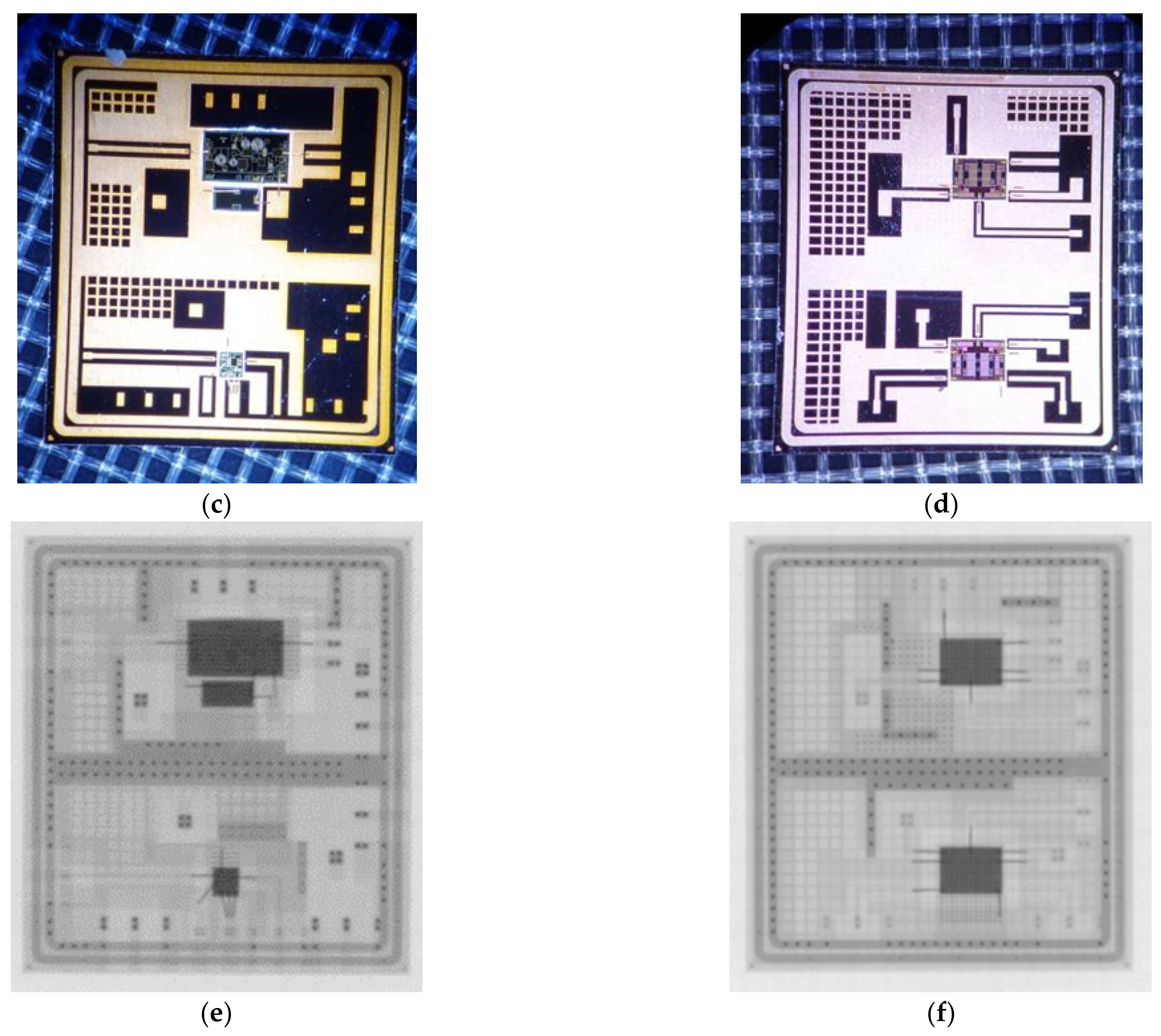

3. The Design of Double Layers Stacked RF Module

3.1. System Architecture of the RF Module

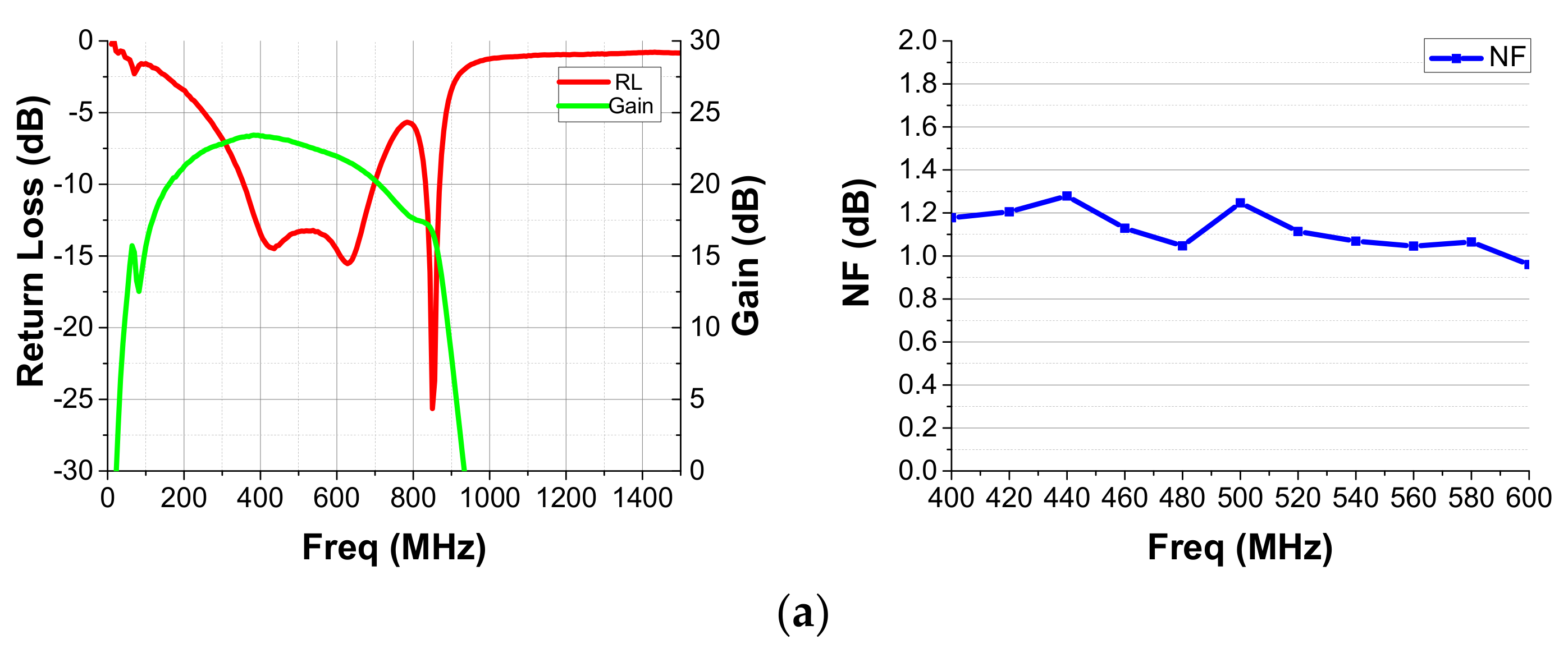

3.2. Simulation of the Key Structures

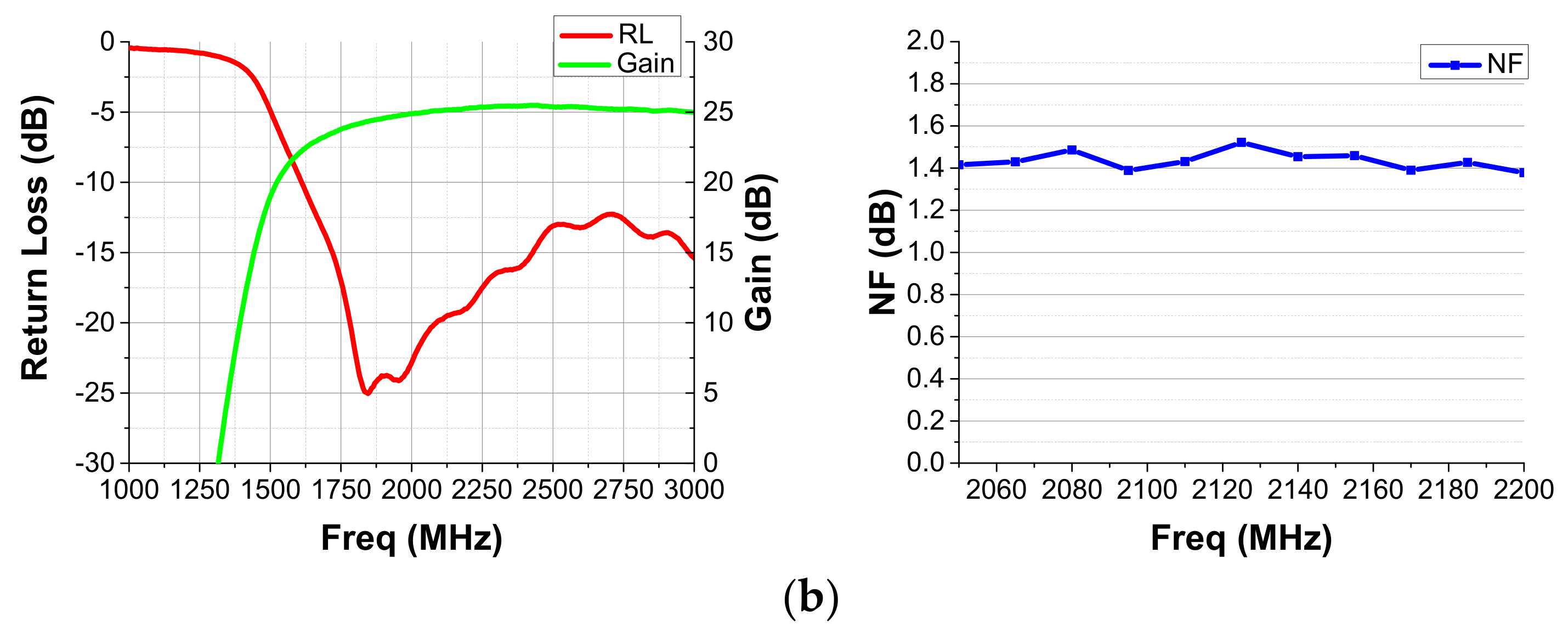

3.3. Measured Result

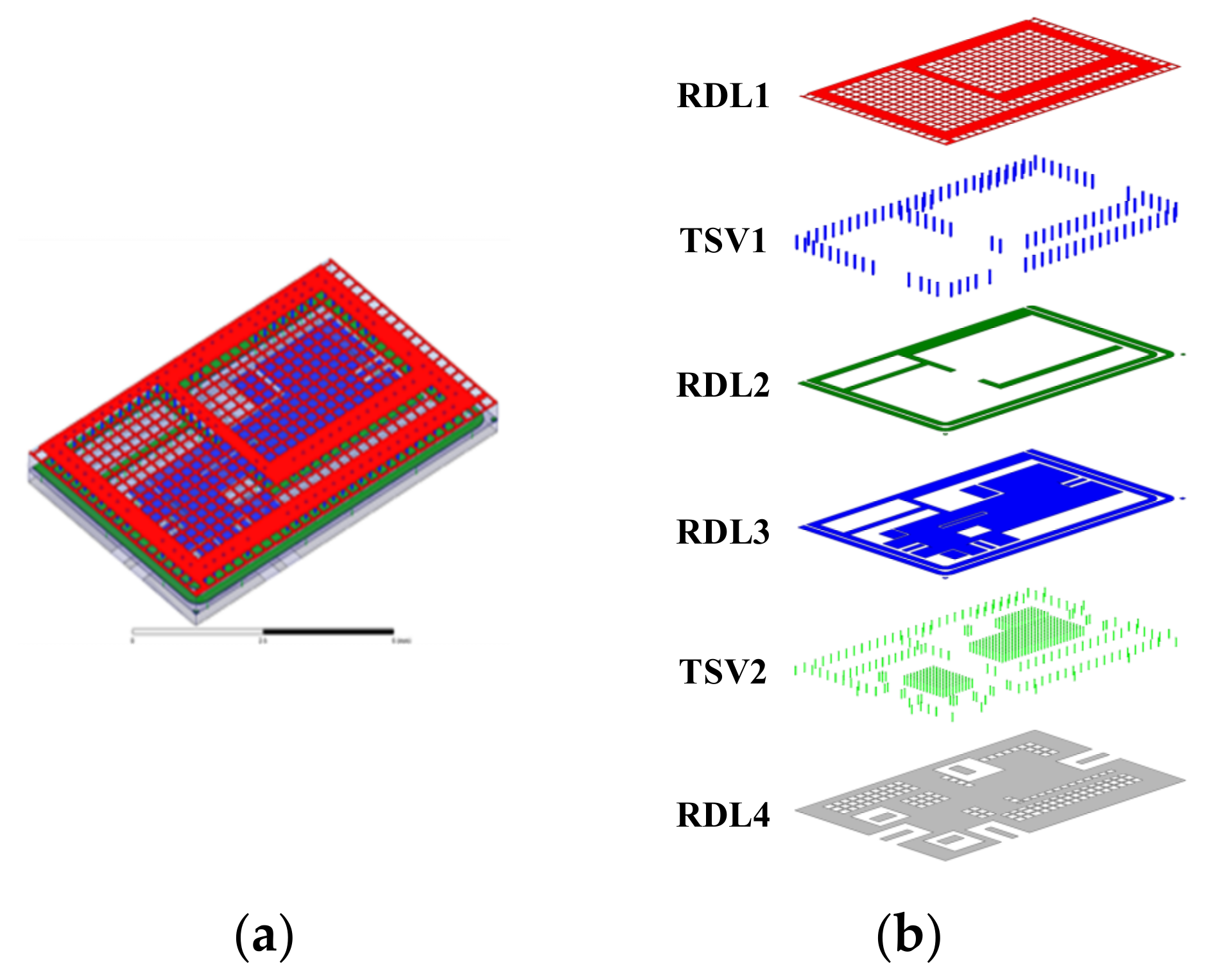

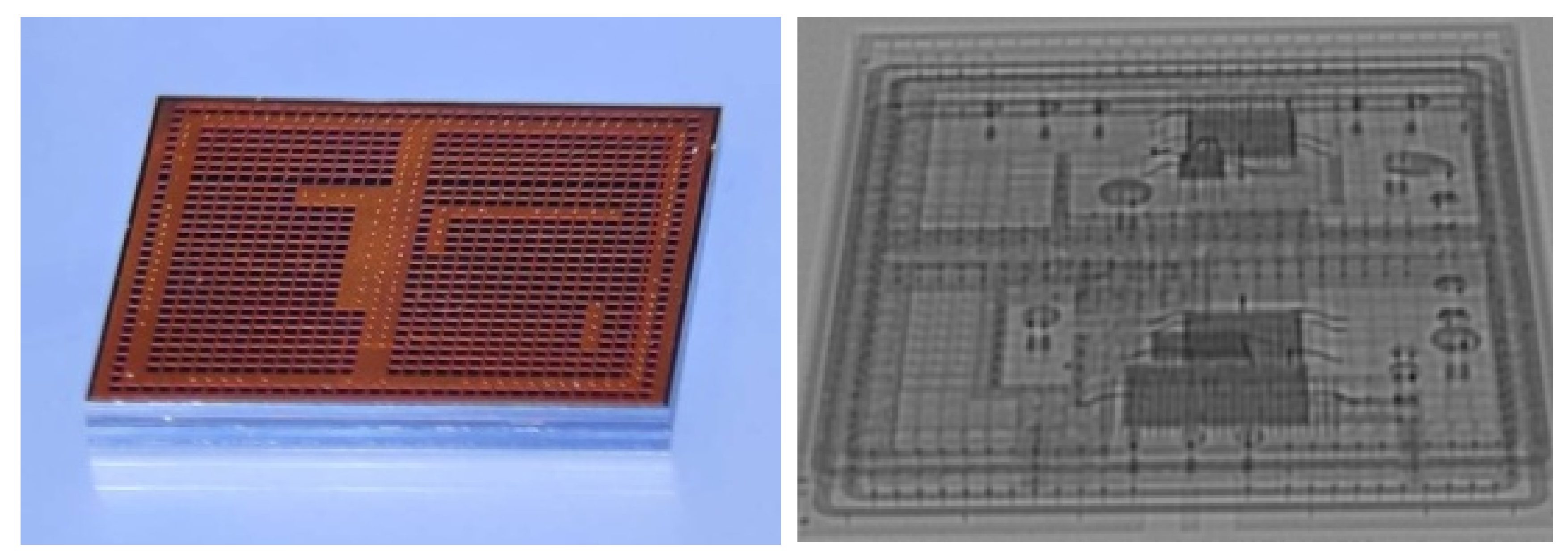

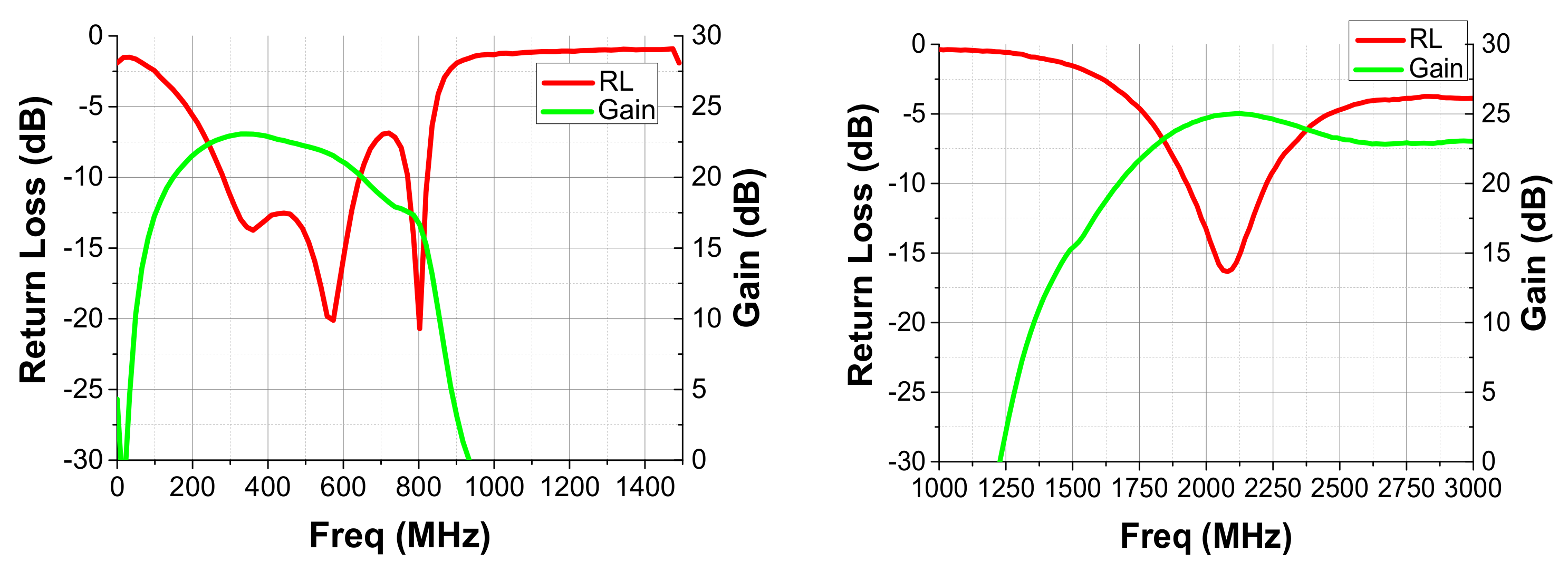

4. The Design of Four Layers Stacked RF Module

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Sturdivant, R.L.; Ly, C.; Benson, J.F.; Hauhe, M.S. Design and performance of a high density 3D microwave module. In Proceedings of the 1997 IEEE MTT-S International Microwave Symposium Digest, Denver, CO, USA, 8–13 June 1997; Volume 2, pp. 501–504. [Google Scholar] [CrossRef]

- Winser, M. A single package X-Band T/R module. In Proceedings of the 2005 European Microwave Conference, Paris, France, 4–6 October 2005; p. 4. [Google Scholar] [CrossRef]

- Comparini, M.; Leone, C.; Montanucci, P.; Tursini, M. HTCC based Ku/IF/BB Down Converter for satellite on board processing applications. In Proceedings of the 2002 32nd European Microwave Conference, Milan, Italy, 23–26 September 2002; pp. 1–4. [Google Scholar] [CrossRef] [Green Version]

- Fina, A.; Di Carlofelice, A.; De Paulis, F. High Power, Thermally Efficient, X-band 3D T/R Module with Calibration Capability for Space Radar. IEEE Access 2018, 6, 60921–60929. [Google Scholar] [CrossRef]

- Zhou, L.; Feng, W.; Wang, D.; Shi, Y. A Compact Millimeter-Wave Frequency Conversion SOP (System on Package) Module Based on LTCC Technology. IEEE Trans. Veh. Technol. 2020, 69, 5923–5932. [Google Scholar] [CrossRef]

- Yu, Z.J.; Xu, Z.; Deng, Y.-K.; Zhang, Z.-G. An Overall Ltcc Package Solution for X-band Tile T/R Module. Prog. Electromagn. Res. Lett. 2013, 38, 181–192. [Google Scholar] [CrossRef] [Green Version]

- Khan, W.T.; Lopez, A.L.V.; Ulusoy, A.C.; Papapolymerou, J. Packaging a $W$-Band Integrated Module with an Optimized Flip-Chip Interconnect on an Organic Substrate. IEEE Trans. Microw. Theory Tech. 2013, 62, 64–72. [Google Scholar] [CrossRef]

- Tan, M.C.; Li, M.; Abbasi, Q.H.; Imran, M.A. Design and Characterization of T/R Module for Commercial Beamforming Applications. IEEE Access 2020, 8, 130252–130262. [Google Scholar] [CrossRef]

- Titz, D.; Pilard, R.; Gianesello, F.; Ferrero, F.; Luxey, C.; Brachat, P.; Jacquemod, G.; Gloria, D. Industrial HTCC Antenna-Module SiP for 60-GHz Applications. IEEE Antennas Wirel. Propag. Lett. 2012, 11, 576–579. [Google Scholar] [CrossRef]

- Di Carlofelice, A.; De Paulis, F.; Fina, A.; Di Marcantonio, U.; Orlandi, A.; Tognolatti, P. Compact and Reliable T/R Module Prototype for Advanced Space Active Electronically Steerable Antenna in 3-D LTCC Technology. IEEE Trans. Microw. Theory Tech. 2018, 66, 2746–2756. [Google Scholar] [CrossRef]

- Bang, Y.-S.; Kim, J.-M.; Kim, J.-M.; Kim, Y.-K.; Jang, Y.-H. LTCC-based vertical via interconnects for RF MEMS packaging. Microw. Opt. Technol. Lett. 2009, 52, 252–257. [Google Scholar] [CrossRef]

- Choi, K.-S.; Moon, S.H.; Eom, Y.-S.; Bae, H.-C.; Lee, J.H. Thermal and Electrical Designs of RF 3D Module Based on Si Interposers with Redundant TSVs. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 2051–2057. [Google Scholar] [CrossRef]

- Lheurette, E.; Mounaix, P.; Salzenstein, P.; Mollot, F.; Lippens, D. High performance InP-based heterostructure barrier varactors in single and stack configuration. Electron. Lett. 1996, 32, 1417. [Google Scholar] [CrossRef]

- Baba, T.; Kokubin, Y.; Sakaki, T.; Iga, K. Loss reduction of an ARROW waveguide in shorter wavelength and its stack configuration. J. Lightwave Technol. 1988, 6, 1440–1445. [Google Scholar] [CrossRef]

- Ranganathan, N.; Lee, D.Y.; Youhe, L.; Lo, G.-Q.; Prasad, K.; Pey, K.L. Influence of Bosch Etch Process on Electrical Isolation of TSV Structures. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 1497–1507. [Google Scholar] [CrossRef]

- Tsai, W.L.; Chang, H.H.; Chien, C.H.; Lau, J.H.; Fu, H.C.; Chiang, C.W.; Kuo, T.Y.; Chen, Y.H.; Lo, R.; Kao, M.J. How to select adhesive materials for temporary bonding and de-bonding of 200 mm and 300 mm thin-wafer handling for 3D IC integration? In Proceedings of the 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2011; pp. 989–998. [Google Scholar] [CrossRef]

- Pelzer, R.; Kirchberger, H.; Kettner, P. Wafer-to-Wafer Bonding Techniques: From MEMS Packaging to IC Integration Applications. In Proceedings of the 2005 6th International Conference on Electronic Packaging Technology, Shenzhen, China, 30 August–2 September 2006; pp. 1–6. [Google Scholar] [CrossRef]

- Lee, J.S.; Byun, K.Y.; Chung, Q.H.; Suh, M.S.; Kim, S.C.; Kim, Y. Chip to chip bonding using micro-cu bumps with Sn capping layers. In Proceedings of the 2009 European Microelectronics and Packaging Conference, Rimini, Italy, 15–18 June 2009; pp. 1–5. [Google Scholar]

- Makita, T.; Tamai, I.; Seki, S. Coplanar Waveguides on High-Resistivity Silicon Substrates with Attenuation Constant Lower Than 1 dB/mm for Microwave and Millimeter-Wave Bands. IEEE Trans. Electron Devices 2011, 58, 709–715. [Google Scholar] [CrossRef]

- Schollhorn, C.; Zhao, W.; Morschbach, M.; Kasper, E. Attenuation mechanisms of aluminum millimeter-wave coplanar waveguides on silicon. IEEE Trans. Electron Devices 2003, 50, 740–746. [Google Scholar] [CrossRef]

- Wu, Y.; Gamble, S.; Armstrong, B.; Fusco, V.; Stewart, J. SiO2/interface layer effects on microwave loss of high-resistivity CPW line. IEEE Microw. Guid. Wave Lett. 1999, 9, 10–12. [Google Scholar] [CrossRef]

- Gamble, H.; Armstrong, B.; Mitchell, S.; Wu, Y.; Fusco, V.; Stewart, J. Low-loss CPW lines on surface stabilized high-resistivity silicon. IEEE Microw. Guid. Wave Lett. 1999, 9, 395–397. [Google Scholar] [CrossRef]

- Costello, S.; Desmulliez, M.P.Y.; McCracken, S.; Abraham, E.; Lowrie, C.; Cargill, S. Electrical Test Structure for the Measurement of Hermeticity in Electronic and MEMS Packages With Small Cavity Volumes. IEEE Trans. Semicond. Manuf. 2013, 26, 281–287. [Google Scholar] [CrossRef]

| Num in Figure 2 | Layer/Via | Material | Thickness (µm) |

|---|---|---|---|

| 1 | φ30 µm TSV | Cu | 190 |

| 2 | SiO2 (PECVD) | SiO2 | 1.6 |

| 3 | RDL1 | Cu | 5 |

| Ni/Pd/Au | 3/0.1/0.05 | ||

| 4 | PI | PI | 4 |

| 5 | RDL2 | Cu | 5 |

| Ni/Au | 3/0.05 |

| Num in Figure 6 | Layer | Material | Thickness (µm) |

|---|---|---|---|

| 1 | φ60 µm TSV | Cu | 250 |

| 2 | SiO2 (Thermal oxidation) | SiO2 | 0.1 |

| 3 | RDL1 | Cu | 5 |

| Ni/Au | 3/0.05 | ||

| 4 | φ50 µm TSV | Cu | 40 |

| 5 | SiO2 (PECVD) | SiO2 | 1 |

| 6 | RDL2 | Cu | 5 |

| Ni | 1 | ||

| SnAg | 5 | ||

| 7 | Cavity | 200 |

| Sample Number | Measured Result (Pa.cm3)/s | Reject Limit (Pa.cm3)/s |

|---|---|---|

| #01 | 9.2 × 10−4 | 5 × 10−3 |

| #02 | 7.7 × 10−4 | |

| #03 | 7.5 × 10−4 | |

| #04 | 6.2 × 10−4 | |

| #05 | 2.2 × 10−4 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yu, F.; Zhou, Q.; Wang, Z.; Mo, J.; Chen, H. Design and Implementation of RF Front-End Module Based on 3D Heterogenous-Integrated Wafer-Level Packaging. Electronics 2021, 10, 1893. https://doi.org/10.3390/electronics10161893

Yu F, Zhou Q, Wang Z, Mo J, Chen H. Design and Implementation of RF Front-End Module Based on 3D Heterogenous-Integrated Wafer-Level Packaging. Electronics. 2021; 10(16):1893. https://doi.org/10.3390/electronics10161893

Chicago/Turabian StyleYu, Faxin, Qi Zhou, Zhiyu Wang, Jiongjiong Mo, and Hua Chen. 2021. "Design and Implementation of RF Front-End Module Based on 3D Heterogenous-Integrated Wafer-Level Packaging" Electronics 10, no. 16: 1893. https://doi.org/10.3390/electronics10161893

APA StyleYu, F., Zhou, Q., Wang, Z., Mo, J., & Chen, H. (2021). Design and Implementation of RF Front-End Module Based on 3D Heterogenous-Integrated Wafer-Level Packaging. Electronics, 10(16), 1893. https://doi.org/10.3390/electronics10161893