A Remedial Control for Short-Circuit Fault in NPC/H-Bridge Inverters without Redundant Component

Abstract

:1. Introduction

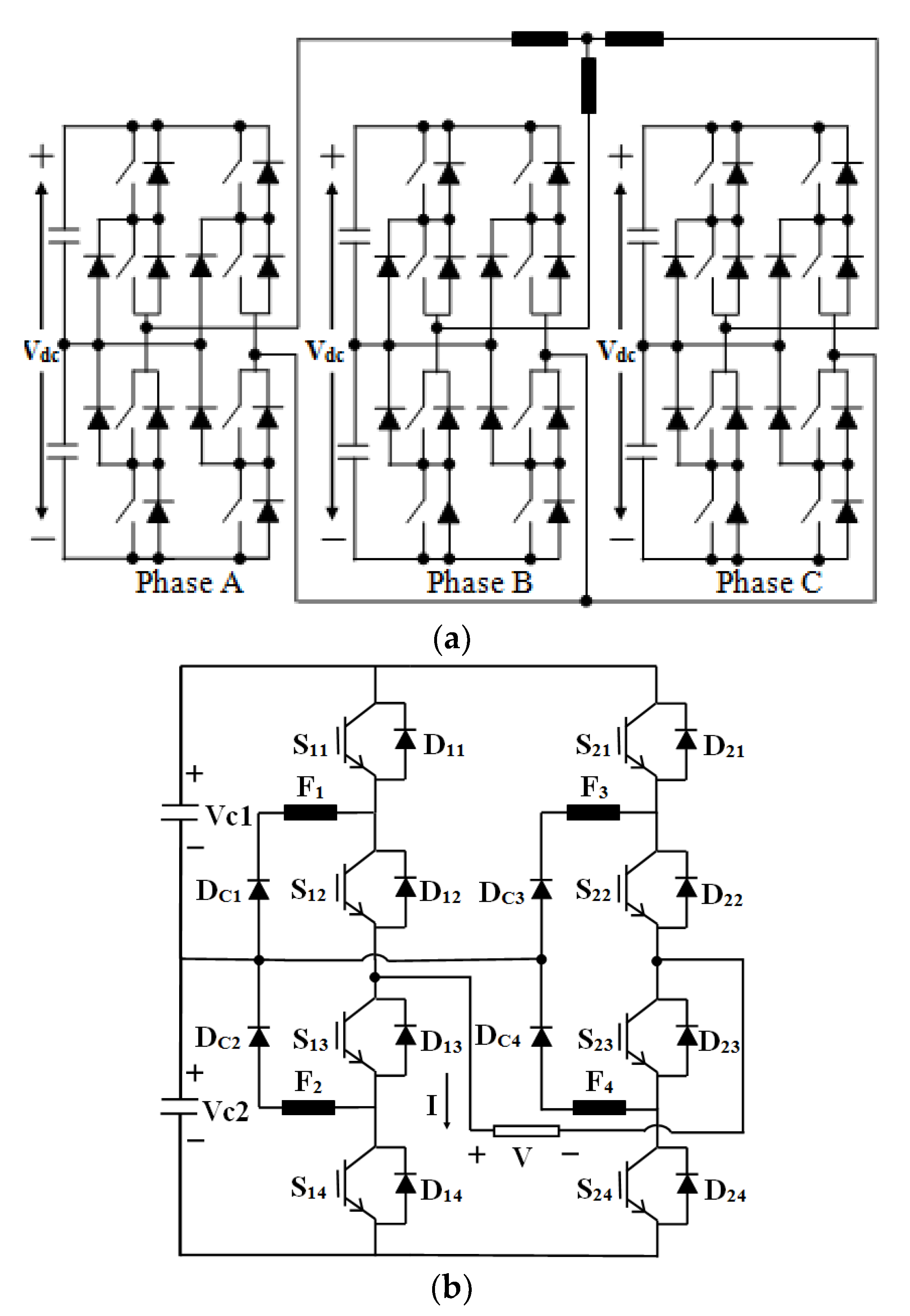

2. Operation of the Inverter under Short-Circuit Fault Condition

3. Principle of the Proposed Remedial Strategy

3.1. Remedial Strategy in the Case of Blowing Fuse F1 or Fuse F2

3.2. Remedial Strategy in the Case of Blowing Fuse F3 or Fuse F4

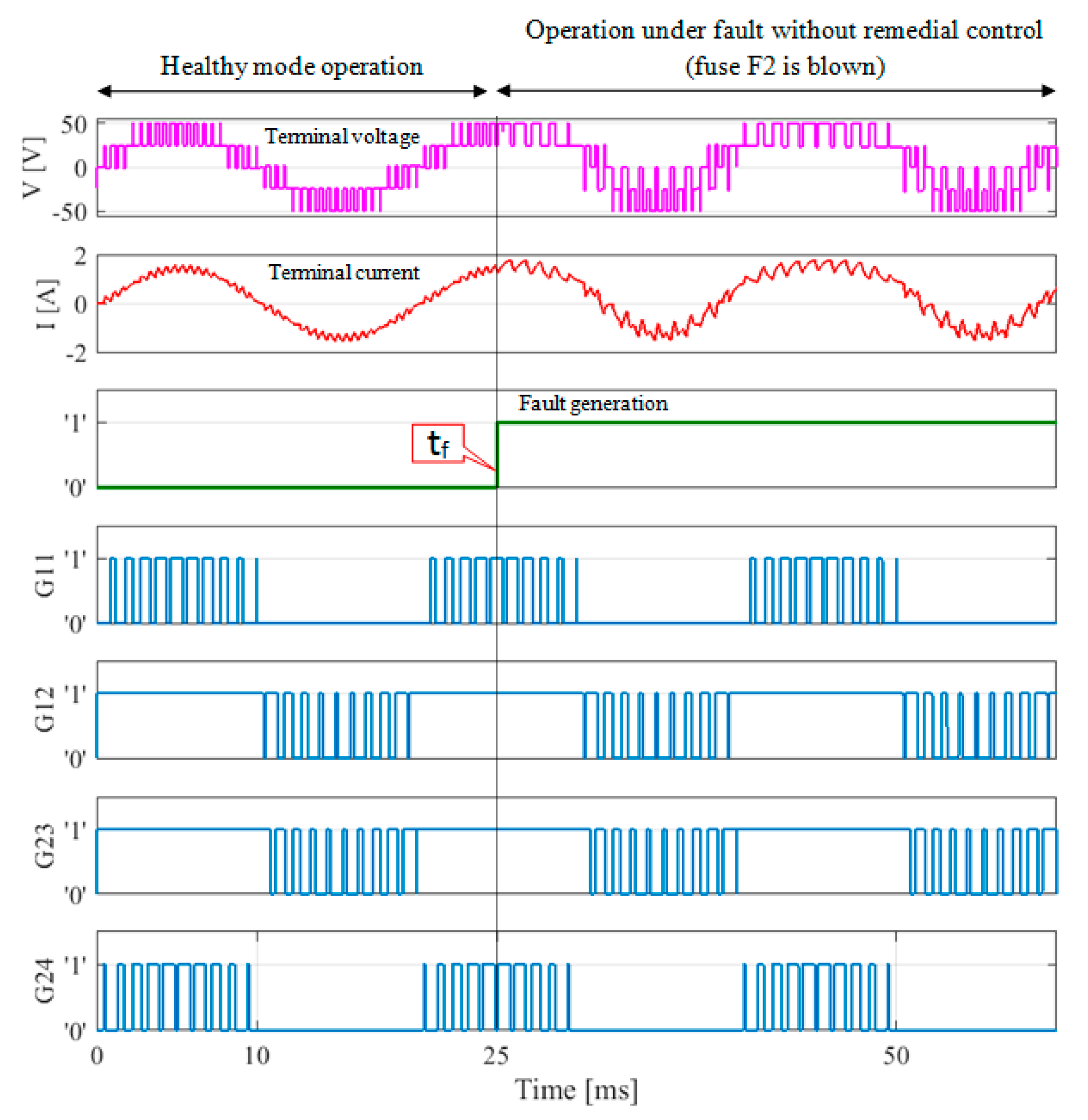

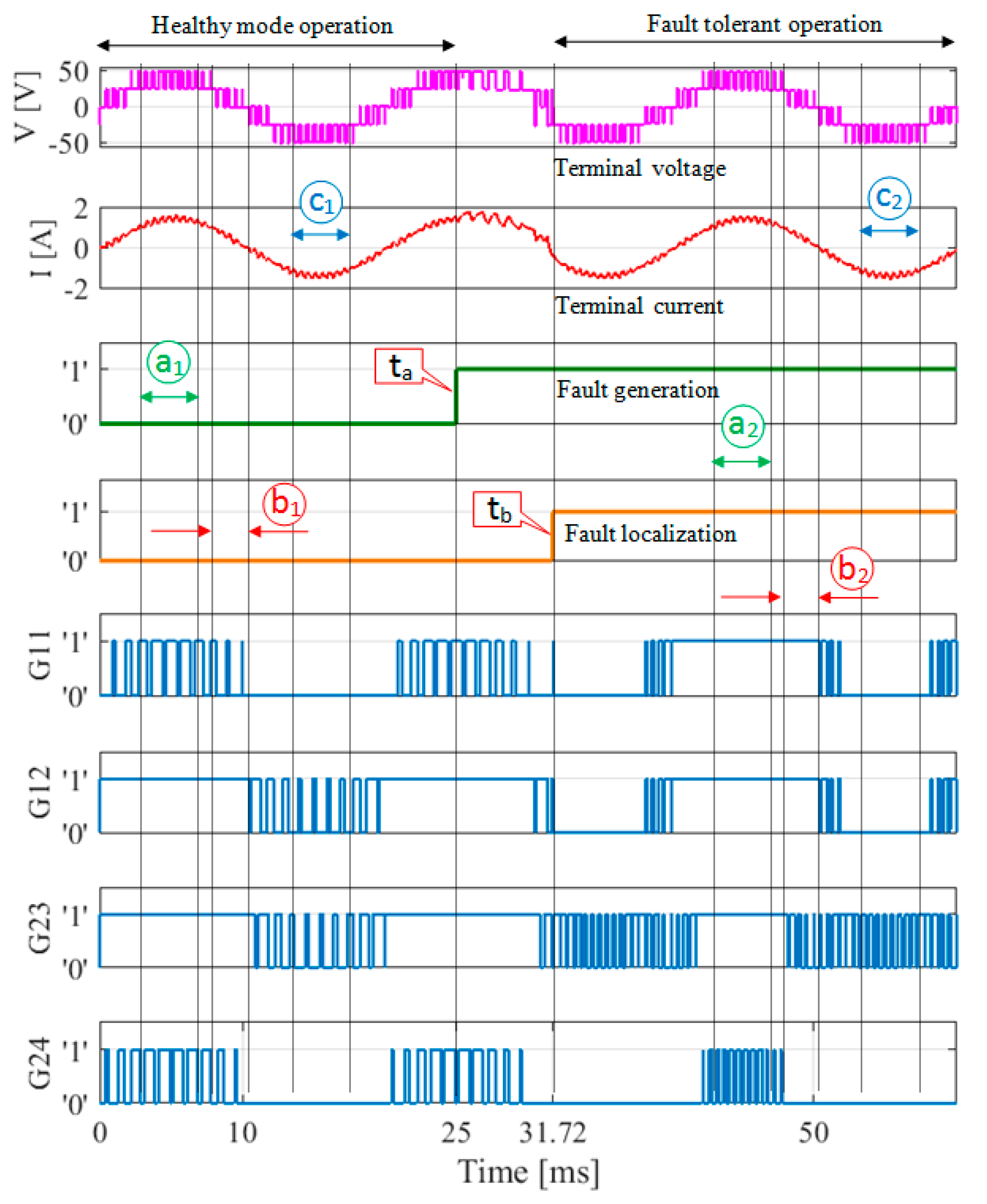

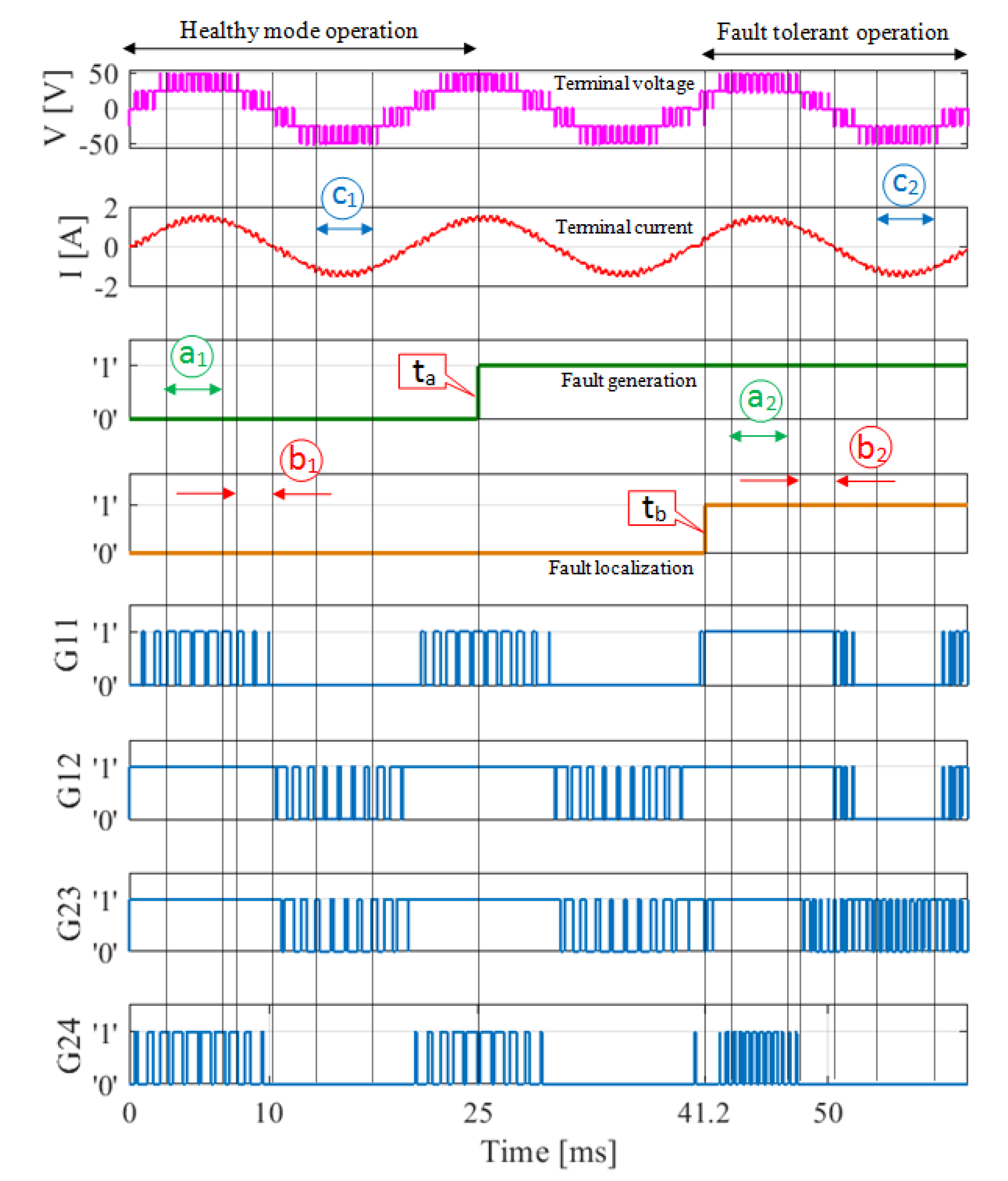

4. Simulation Results

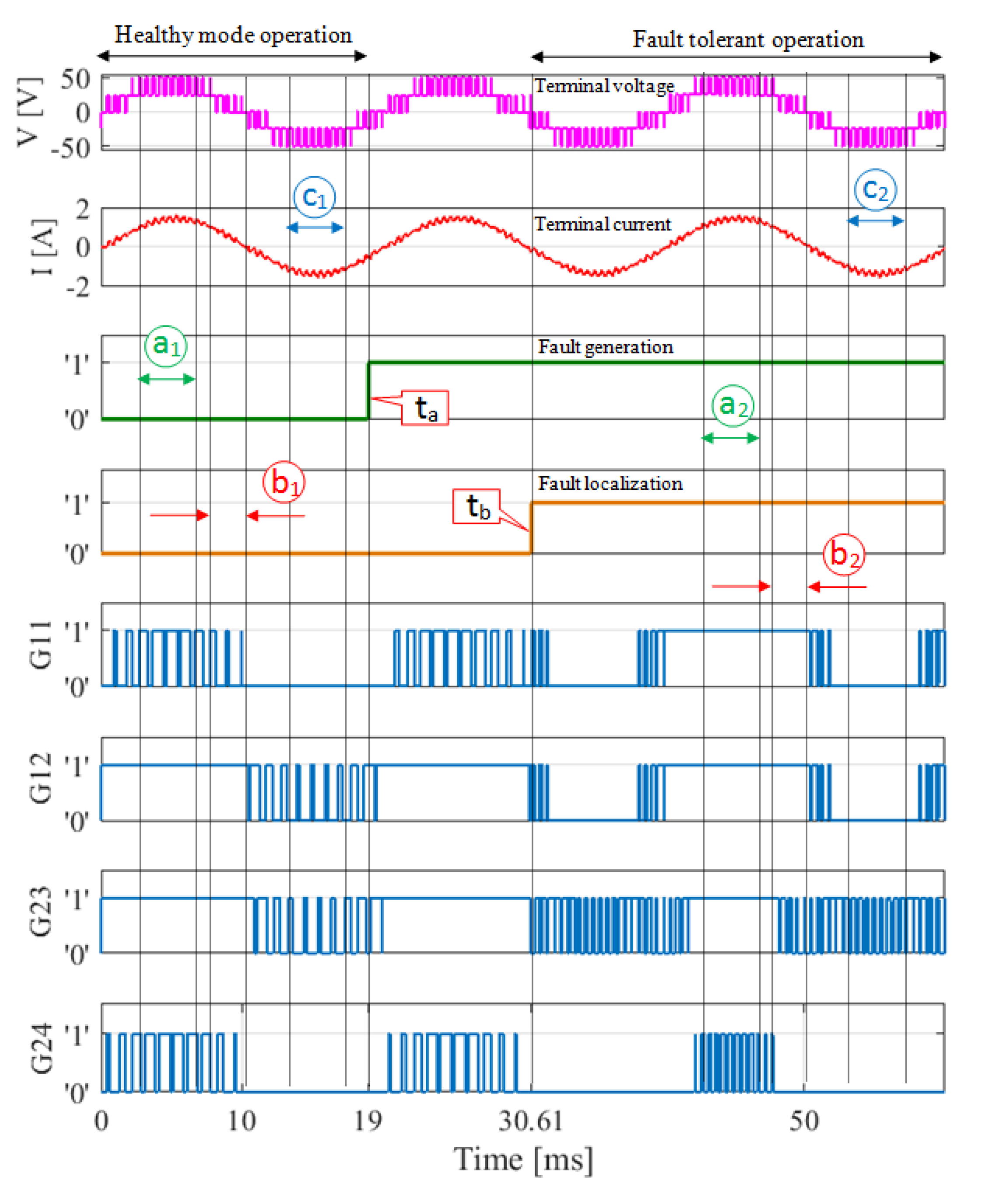

4.1. Simulation Results Regarding Service Continuity in the Case of Blowing Fuse F1 or Fuse F2

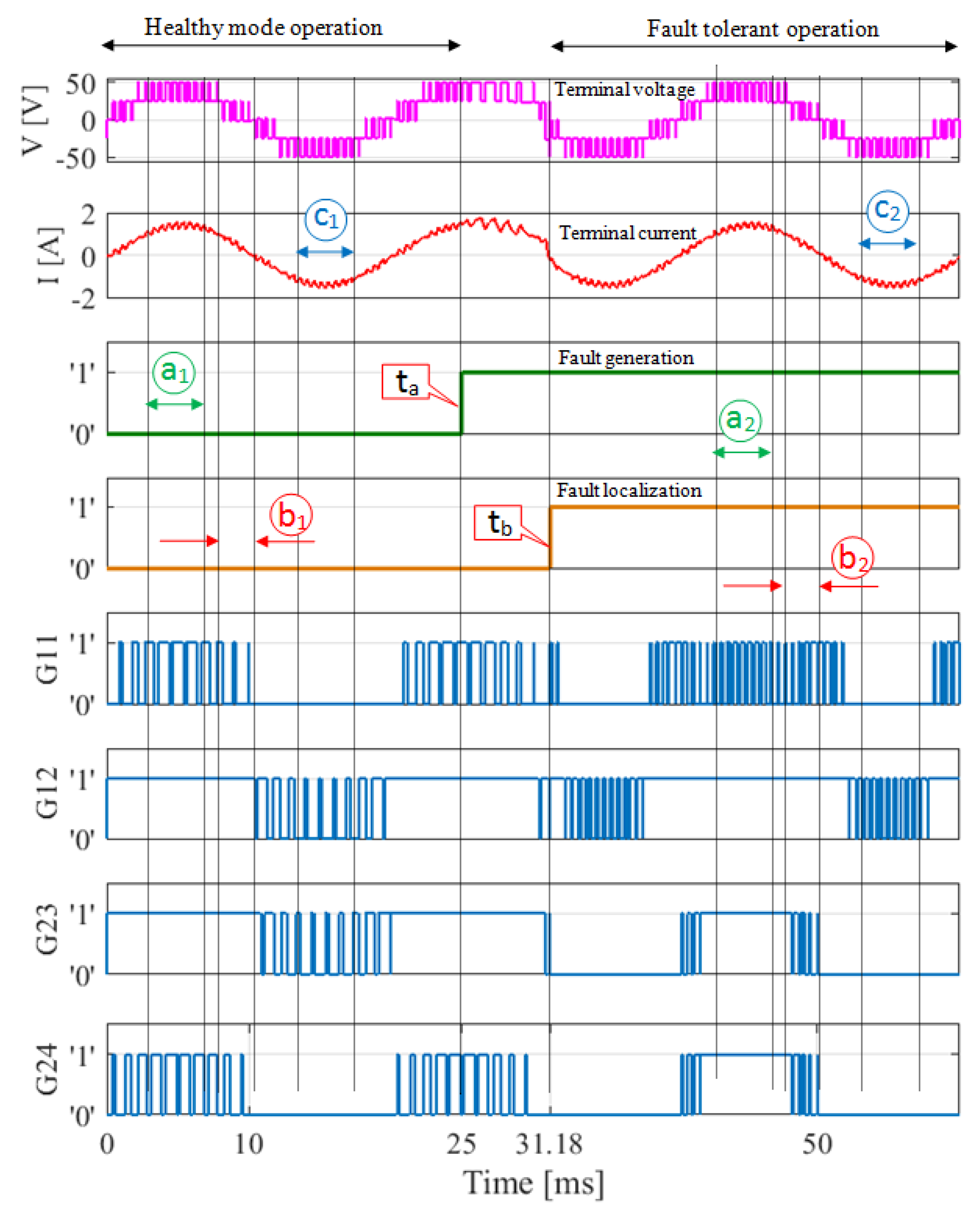

4.2. Simulation Results Regarding Service Continuity in the Case of Blowing Fuse F3 or Fuse F4

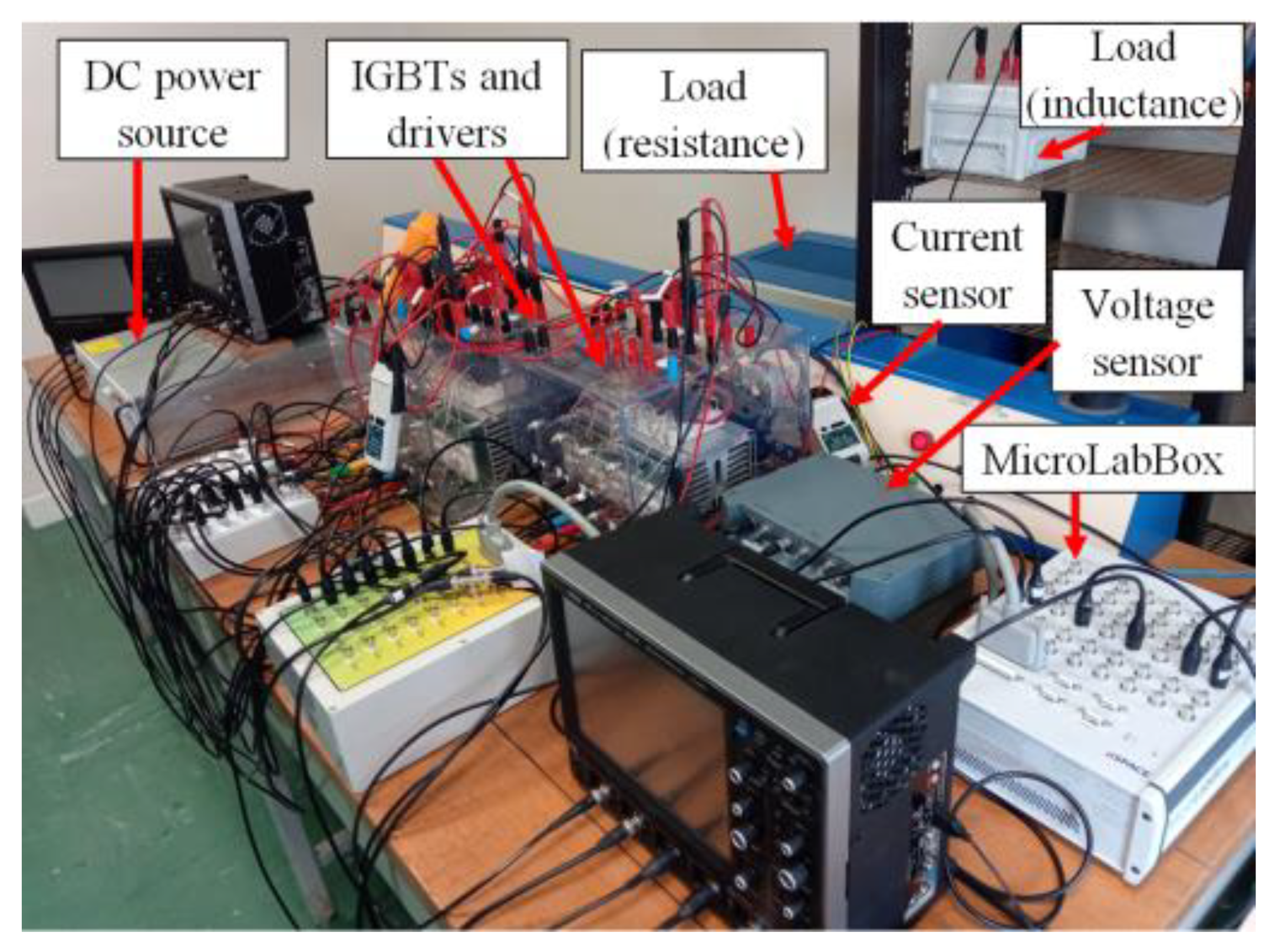

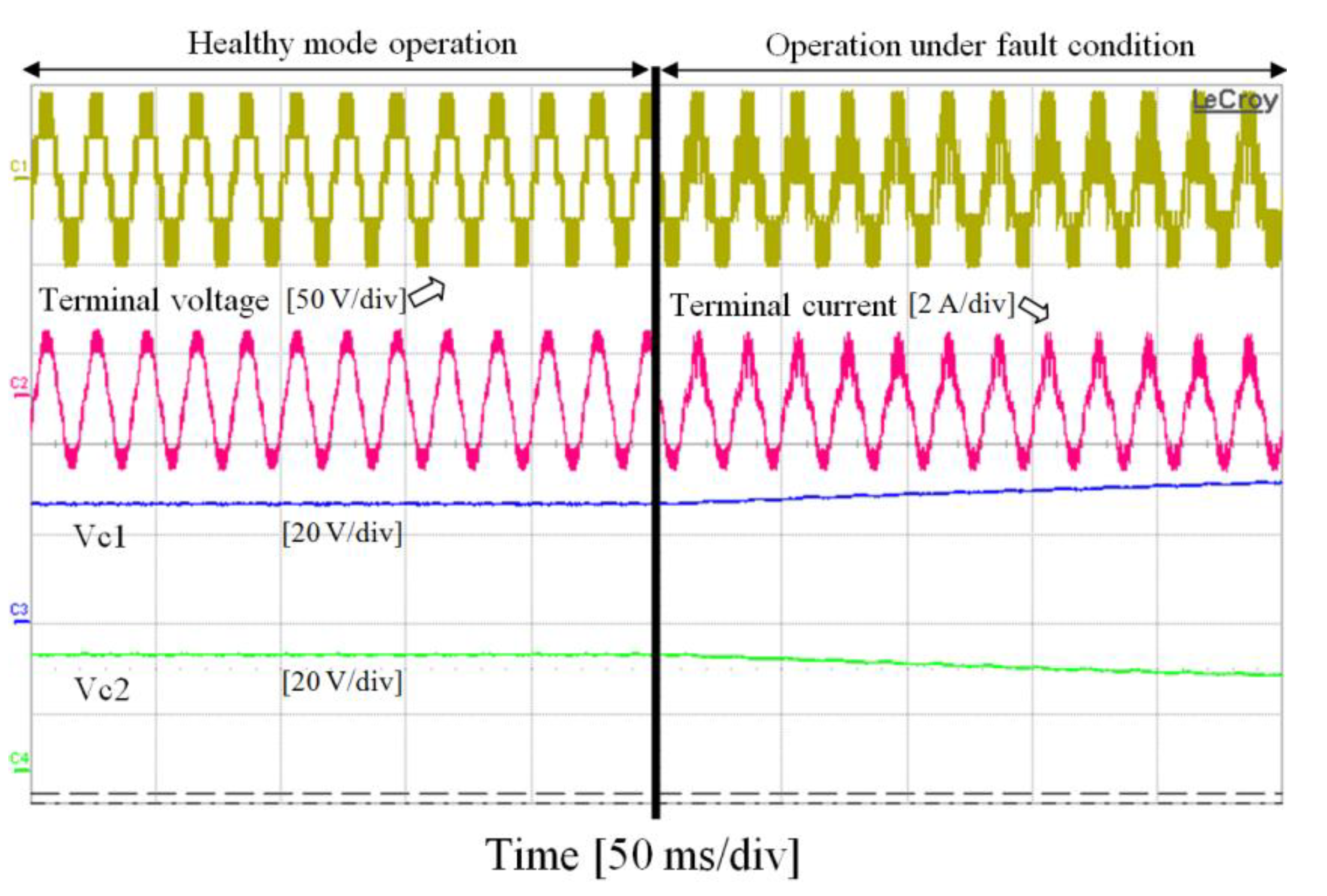

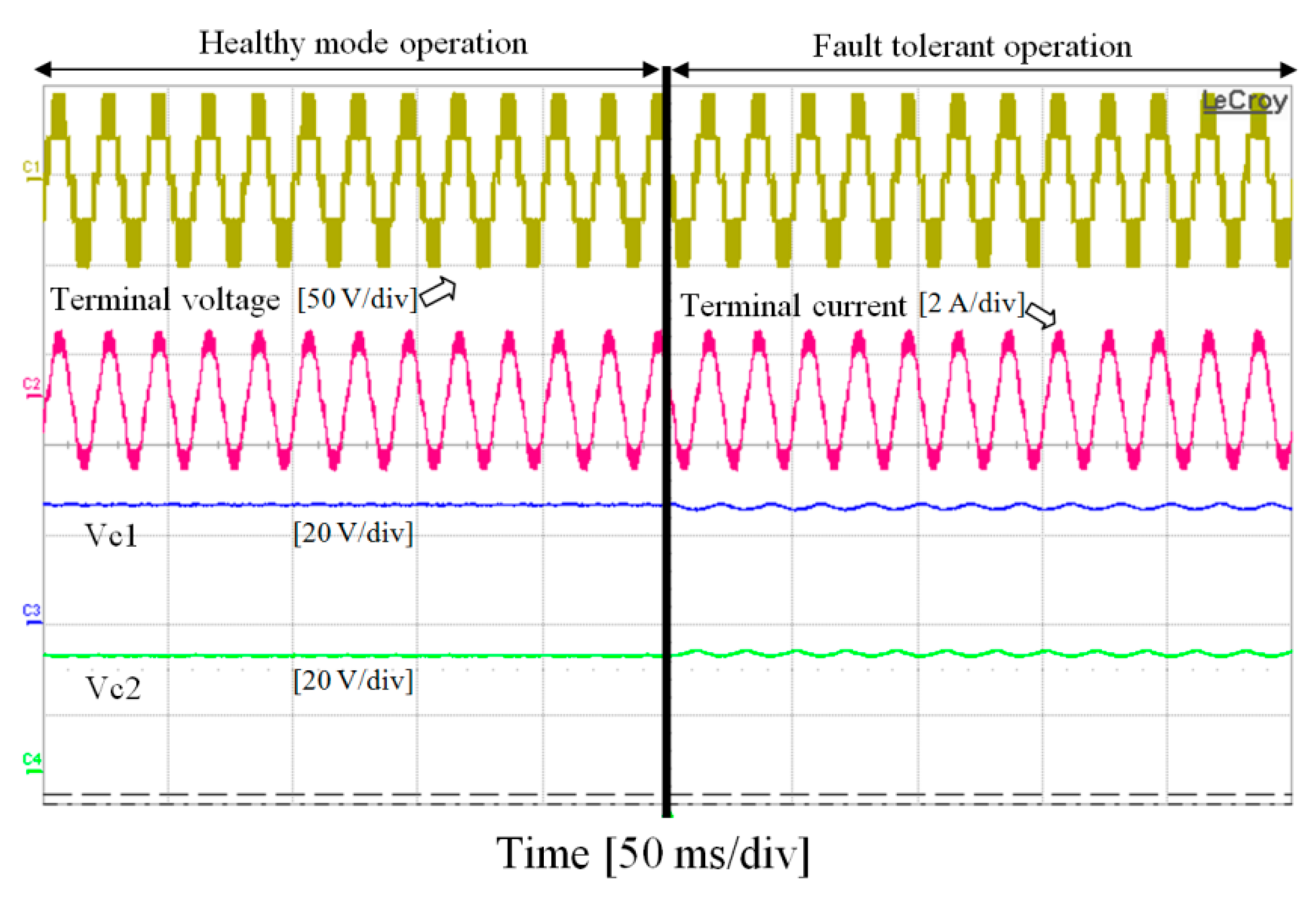

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Gautam, S.P.; Kumar, L.; Gupta, S.; Agrawal, N. A single-phase five-level inverter topology with switch fault-tolerance capabilities. IEEE Trans. Ind. Electron. 2017, 64, 2004–2014. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef] [Green Version]

- Jung, J.; Ku, H.; Son, Y.; Kim, J. Open-switch fault diagnosis algorithm and tolerant control method of the three-phase three-level NPC active rectifier. Energies 2019, 12, 2495. [Google Scholar] [CrossRef] [Green Version]

- Wu, B. High-Power Converters AC Drives; Wiley: Hoboken, NJ, USA, 2006. [Google Scholar]

- Baek, S.; Shin, H.; Kang, S.; Park, C.; Lee, K. Open fault detection and tolerant control for a five phase inverter driving system. Energies 2016, 9, 335. [Google Scholar] [CrossRef] [Green Version]

- Lezana, P.; Pou, J.; Meynard, T.; Rodríguez, J.; Ceballos, S.; Richardeau, F. Survey on fault operation on multilevel inverters. IEEE Trans. Ind. Electron. 2010, 57, 2207–2218. [Google Scholar] [CrossRef] [Green Version]

- Blinov, A.; Kosenko, R.; Chub, A.; Ivakhno, V. Analysis of fault-tolerant operation capabilities of an isolated bidirectional current-source DC-DC converter. Energies 2019, 12, 3203. [Google Scholar] [CrossRef] [Green Version]

- Lamb, J.; Mirafzal, B. Open-circuit IGBT fault detection and location isolation for cascaded multilevel converters. IEEE Trans. Ind. Electron. 2017, 64, 4846–4856. [Google Scholar] [CrossRef]

- Ouni, S.; Zolgadri, M.R.; Khodabandeh, M.; Shahbazi, M.; Rodriguez, J.; Oraee, H.; Lezana, P.; Schmeisser, A.U. Improvement of post-fault performance of a cascaded H-bridge multilevel inverter. IEEE Trans. Ind. Electron. 2017, 64, 2779–2788. [Google Scholar] [CrossRef] [Green Version]

- Salimian, H.; Iman-Eini, H. Fault-tolerant operation of three-phase cascaded H-bridge converters using an auxiliary module. IEEE Trans. Ind. Electron. 2017, 64, 1018–1027. [Google Scholar] [CrossRef]

- Aleenejad, M.; Mahmoudi, H.; Moamaei, P.; Ahmadi, R. A new fault-tolerant strategy based on a modifies selective harmonic technique for three-phase multilevel converters with a single faulty cell. IEEE Trans. Power Electron. 2016, 31, 3141–3150. [Google Scholar] [CrossRef]

- Abdelsalam, M.; Marei, M.I.; Tennakoon, S.B. An integrated control strategy with fault detection and tolerant control capability based on capacitor voltage estimation for modular multilevel converters. IEEE Trans. Ind. Appl. 2017, 53, 2840–2851. [Google Scholar] [CrossRef]

- Ghazanfari, A.; Mohamed, Y.A.I. A resilient framework for fault-tolerant operation of modular multilevel converters. IEEE Trans. Ind. Electron. 2016, 63, 2669–2678. [Google Scholar] [CrossRef]

- Li, B.; Shi, S.; Wang, B.; Wang, G.; Wang, W.; Xu, D. Fault diagnosis and tolerant control of single IGBT open-circuit failure in modular multilevel converters. IEEE Trans. Power Electron. 2016, 31, 3165–3176. [Google Scholar] [CrossRef]

- Deng, F.; Tian, Y.; Zhu, R.; Chen, Z. Fault-tolerant approach for modular multilevel converters under submodule faults. IEEE Trans. Ind. Electron. 2016, 63, 7253–7263. [Google Scholar] [CrossRef]

- Yang, S.; Tang, Y.; Wang, P. Seamless fault-tolerant operation of a modular multilevel converter with switch open-circuit fault diagnosis in a distributed control architecture. IEEE Trans. Power Electron. 2017, 33, 7058–7070. [Google Scholar] [CrossRef]

- Lee, J.S.; Lee, K. Open-switch fault tolerance control for a three-level NPC/T-type rectifier in wind turbine systems. IEEE Trans. Ind. Electron. 2015, 62, 1012–1021. [Google Scholar] [CrossRef]

- Choi, U.; Lee, J.; Blaabjerg, F.; Lee, K. Open-circuit fault diagnosis and fault-tolerant control for a grid-connected NPC inverter. IEEE Trans. Power Electron. 2016, 31, 7234–7247. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Zaragoza, J.; Robles, E.; Villate, J.L.; Martín, J.L. Fault-tolerant neutral-point-clamped converter solutions based on including a fourth resonant leg. IEEE Trans. Ind. Electron. 2011, 58, 2293–2303. [Google Scholar] [CrossRef]

- Li, S.; Xu, L. Strategies of fault tolerant operation for three-level PWM inverters. IEEE Trans. Ind. Electron. 2006, 21, 933–940. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Robles, E.; Gabiola, I.; Zaragoza, J.; Villate, J.L.; Boroyevich, D. Three-level converter topologies with switch breakdown fault-tolerance capability. IEEE Trans. Ind. Electron. 2008, 55, 982–995. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Robles, E.; Zaragoza, J.; Martín, J.L. Performance evaluation of fault-tolerant neutral-point-clamped converters. IEEE Trans. Ind. Electron. 2010, 57, 2709–2718. [Google Scholar] [CrossRef]

- Lee, J.; Lee, K. Open-circuit fault-tolerant control for outer switches of three-level rectifiers in wind turbine systems. IEEE Trans. Power Electron. 2016, 31, 3806–3815. [Google Scholar] [CrossRef]

- Katebi, R.; He, J.; Weise, N. An advanced three-level active neutral-point-clamped converter with improved fault-tolerant capabilities. IEEE Trans. Power Electron. 2018, 33, 6897–6909. [Google Scholar] [CrossRef] [Green Version]

- Azer, P.; Ouni, S.; Narimani, M. A novel fault-tolerant technique for active neutral point clamped inverter using carrier-based PWM. IEEE Trans. Ind. Electron. 2020, 67, 1792–1803. [Google Scholar] [CrossRef]

- Xu, S.; Zhang, J.; Hang, J. Investigation of a fault-tolerant three-level T-type inverter system. IEEE Trans. Ind. Appl. 2017, 53, 4613–4623. [Google Scholar] [CrossRef]

- Choi, U.M.; Blaabjerg, F.; Lee, K.B. Reliability improvement of a T-type three-level inverter with fault-tolerant control strategy. IEEE Trans. Power Electron. 2015, 30, 2660–2673. [Google Scholar] [CrossRef]

- Choi, U.; Lee, K.; Blaabjerg, F. Diagnosis and tolerant strategy of an open-switch fault for T-type three-level inverter systems. IEEE Trans. Ind. Appl. 2014, 50, 495–508. [Google Scholar] [CrossRef]

- Lee, T.; Li, B.; Yang, M.; Tsai, Y. A Carrier-Based PWM for Three-Level T-Type Inverter to Tolerate Open-Circuit Fault. IEEE Trans. Power Electron. 2018, 33, 8787–8796. [Google Scholar] [CrossRef]

- He, J.; Katebi, R.; Weise, N.; Demerdash, N.A.O.; Wei, L. A fault-tolerant T-type multilevel inverter topology with increased overload capability and soft-switching characteristics. IEEE Trans. Ind. Appl. 2017, 53, 2826–2839. [Google Scholar] [CrossRef]

- Li, J. Design and Control Optimisation of A Novel Bypass-Embedded Multilevel Multicell Inverter for Hybrid Electric Vehicle Drives. In Proceedings of the 2020 IEEE 11th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Dubrovnik, Croatia, 28 September–1 October 2020; pp. 382–385. [Google Scholar]

- Braun, G.; Pixler, D.; Lemay, P. IGBT Module Rupture Categorization and Testing. In Proceedings of the IEEE Industry Application Socity Annual Meeting, New Orleans, LA, USA, 5–9 October 1997. [Google Scholar]

- Blaabjerg, F.; Iov, F.; Ries, K. Fuse protection of IGBT modules against explosions. J. Power Electron. 2002, 2, 88–94. [Google Scholar]

- Iov, F.; Abrahamsen, F.; Blaabjerg, F.; Ries, K.; Rasmussen, H.; Bjornaa, P. Fusing IGBT Based Inverters. In Proceedings of the PCIM 2001: International Conference on Power Electronics, Intelligent Motion and Power Quality, Nurenberg, Germany, 19–21 June 2001. [Google Scholar]

- Duong, S.; Schaeffer, C.; Rouve, L.; Palma, J.; Mullert, C. Fuses for Power IGBT Converters. In Proceedings of the IEEE Industry Applications Society Annual Meeting, Denver, CO, USA, 2–6 October 1994. [Google Scholar]

- Mendes, A.M.S.; Abadi, M.B.; Cruz, S.M.A. Method to diagnose open-circuit faults in active power switches and clamp-diodes of three-level neutral-point clamped inverters. IET Elect. Power Appl. 2016, 10, 623–632. [Google Scholar]

- Ge, X.; Pu, J.; Geo, B.; Liu, Y. An open-circuit fault diagnosis approach for single-phase three-level neutral-point-clamped converters. IEEE Trans. Power. Electron. 2018, 33, 2559–2570. [Google Scholar] [CrossRef]

| Switching State | Terminal Voltage | S11 | S12 | S13 | S14 | S21 | S22 | S23 | S24 |

|---|---|---|---|---|---|---|---|---|---|

| 1 | +Vdc | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 2 | +Vdc/2 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

| 3 | +Vdc/2 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 5 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| 6 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 7 | −Vdc/2 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 8 | −Vdc/2 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 9 | −Vdc | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| Switching State | Terminal Voltage | Conducting Components (I > 0) | Conducting Components (I < 0) |

|---|---|---|---|

| 1 | +Vdc | S11, S12, S23, S24 | D11, D12, D23, D24 |

| 2 | +Vdc/2 | S11, S12, S23, DC4 | D11, D12, S22, DC3 |

| 3 | +Vdc/2 | DC1, S12, S23, S24 | DC2, S13, D23, D24 |

| 4 | 0 | S11, S12, D22, D21 | D11, D12, S21, S22 |

| 5 | 0 | DC1, S12, S23, DC4 | DC2, S13, S22, DC3 |

| 6 | 0 | D14, D13, S23, S24 | S13, S14, D24, D23 |

| 7 | −Vdc/2 | DC1, S12, D22, D21 | DC2, S13, S22, S21 |

| 8 | −Vdc/2 | D14, D13, S23, DC4 | S13, S14, DC3, S22 |

| 9 | −Vdc | D14, D13, D22, D21 | S13, S14, S22, S21 |

| Faulty Component | Switching States (Table 1) Making Short-Circuit Current Loop | Blown Fuse |

|---|---|---|

| S11 | 3, 5, 7 | F2 |

| S12 | 6, 8, 9 | F1 |

| S13 | 1, 2, 4 | F2 |

| S14 | 3, 5, 7 | F1 |

| S21 | 2, 5, 8 | F4 |

| S22 | 1, 3, 6 | F3 |

| S23 | 4, 7, 9 | F4 |

| S24 | 2, 5, 8 | F3 |

| Blown Fuse | Clamping Diode in Series with the Blown Fuse | Infeasible Switching State | Substituted Switching State |

|---|---|---|---|

| F1 | DC1 | 3 | 2 |

| 5 | 4 or 6 | ||

| 7 | 8 | ||

| F2 | DC2 | 3 | 2 |

| 5 | 4 or 6 | ||

| 7 | 8 | ||

| F3 | DC3 | 2 | 3 |

| 5 | 4 or 6 | ||

| 8 | 7 | ||

| F4 | DC4 | 2 | 3 |

| 5 | 4 or 6 | ||

| 8 | 7 |

| Parameter | Value |

|---|---|

| Load resistance | 27.7 Ω |

| Load inductance | 9 mH |

| DC link voltage | 50 V |

| DC link capacitor | 2.2 mF |

| Switching frequency | 1 kHz |

| Modulation index | 0.8 |

| Interval | Applied Switching States |

|---|---|

| a1 | 1, 2, 3 |

| b1 | 2, 3, 5 |

| c1 | 7, 8, 9 |

| a2 | 1, 2 |

| b2 | 2, 4 |

| c2 | 8, 9 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ahmadi, S.; Poure, P.; Khaburi, D.A.; Saadate, S. A Remedial Control for Short-Circuit Fault in NPC/H-Bridge Inverters without Redundant Component. Electronics 2021, 10, 2411. https://doi.org/10.3390/electronics10192411

Ahmadi S, Poure P, Khaburi DA, Saadate S. A Remedial Control for Short-Circuit Fault in NPC/H-Bridge Inverters without Redundant Component. Electronics. 2021; 10(19):2411. https://doi.org/10.3390/electronics10192411

Chicago/Turabian StyleAhmadi, Sajjad, Philippe Poure, Davood Arab Khaburi, and Shahrokh Saadate. 2021. "A Remedial Control for Short-Circuit Fault in NPC/H-Bridge Inverters without Redundant Component" Electronics 10, no. 19: 2411. https://doi.org/10.3390/electronics10192411

APA StyleAhmadi, S., Poure, P., Khaburi, D. A., & Saadate, S. (2021). A Remedial Control for Short-Circuit Fault in NPC/H-Bridge Inverters without Redundant Component. Electronics, 10(19), 2411. https://doi.org/10.3390/electronics10192411