A Low Phase Noise Dual-Loop Dual-Output Frequency Synthesizer in SiGe BiCMOS

Abstract

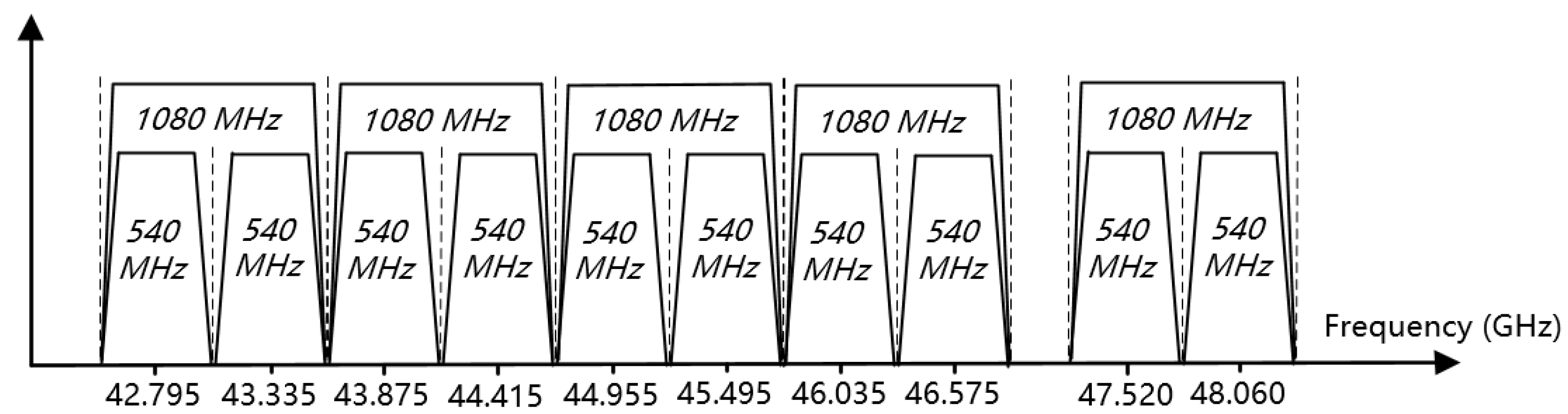

:1. Introduction

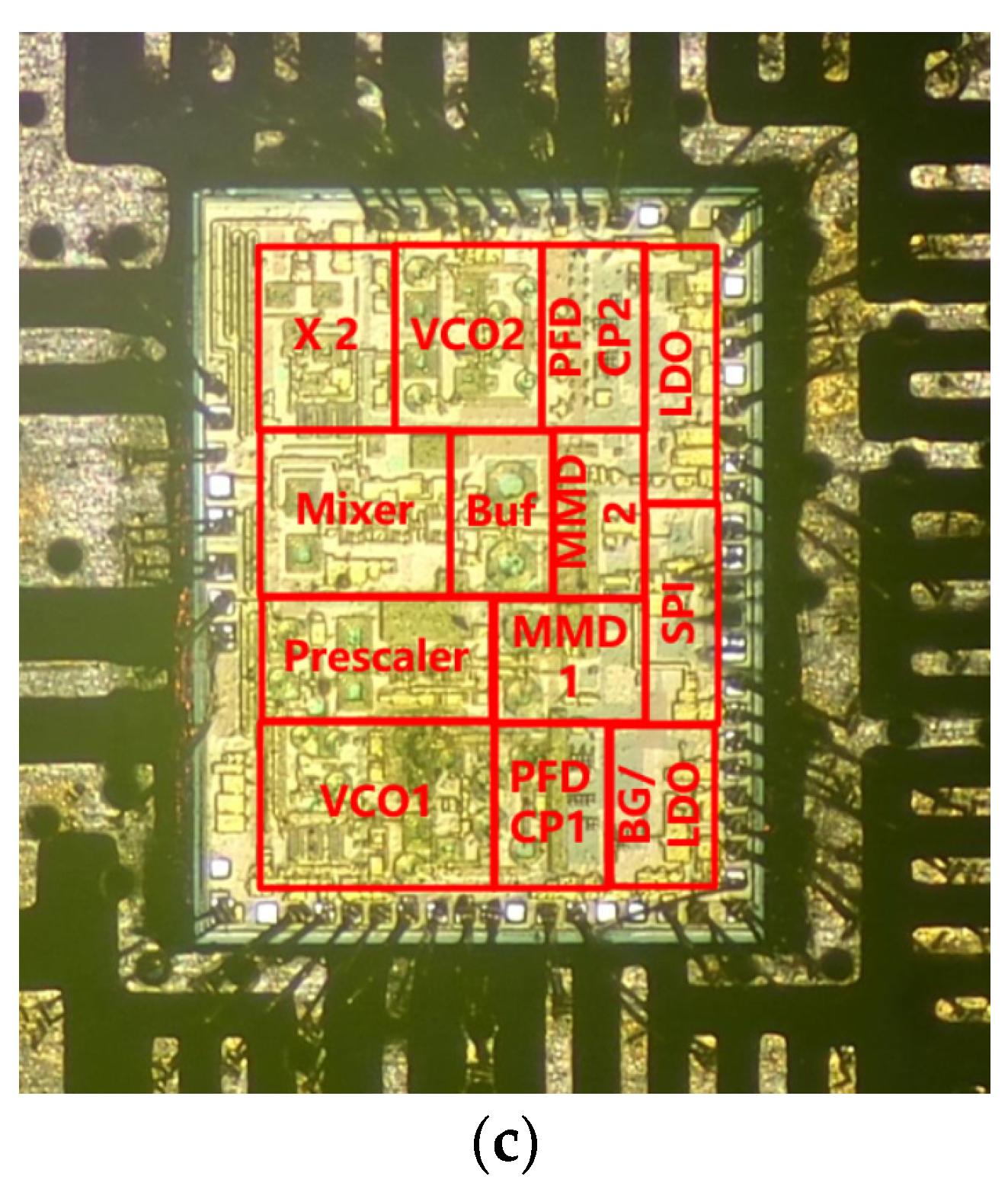

2. Design and Implementation of the Dual-Loop Dual-Output Frequency Synthesizer

2.1. Voltage Controlled Oscillator using Cap Bank and Ka-Band Doubler

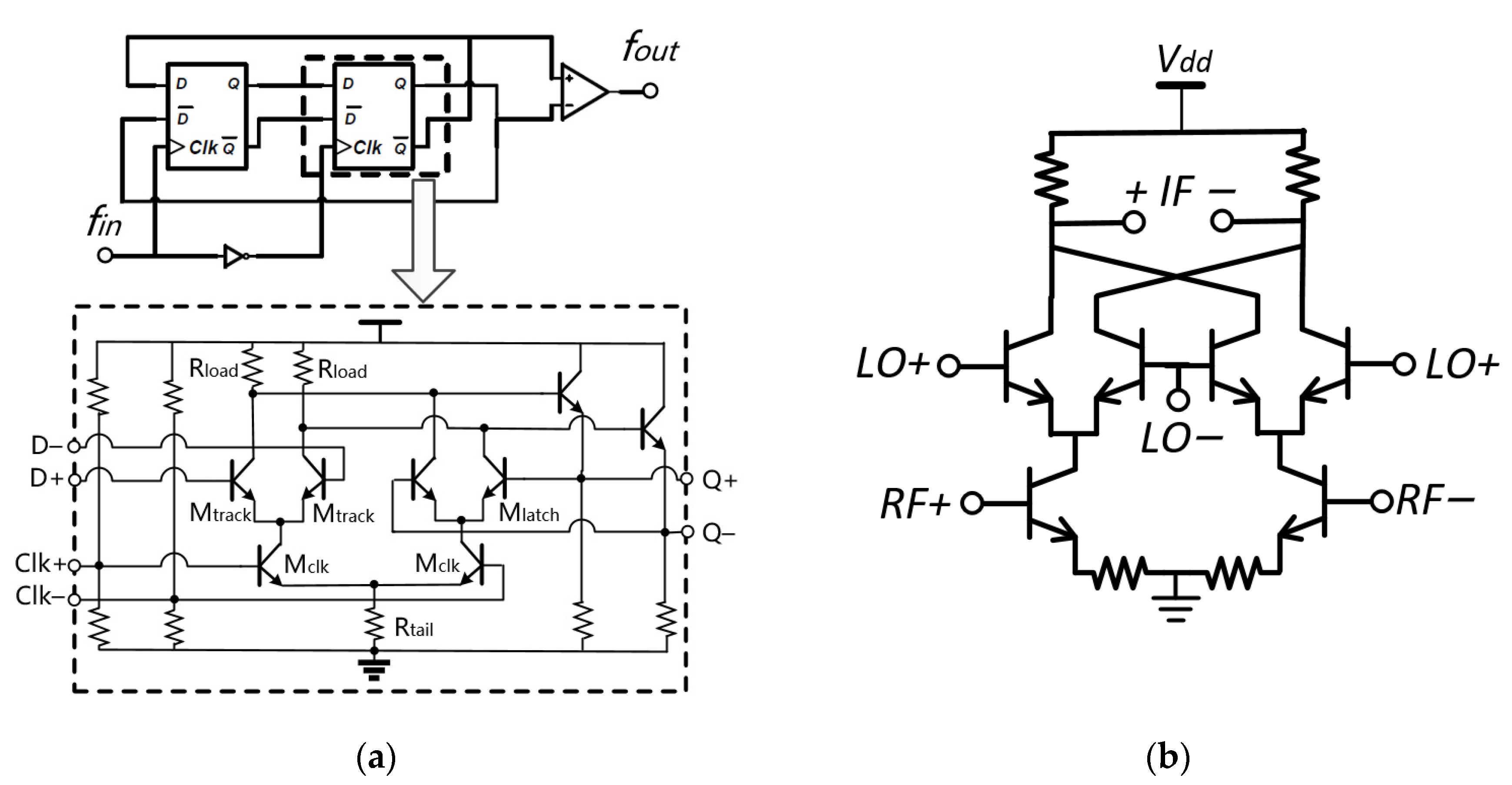

2.2. High-Speed Prescaler and Double-Balanced Down-Conversion Mixer

2.3. Phase-Frequency Detector and Charge Pump

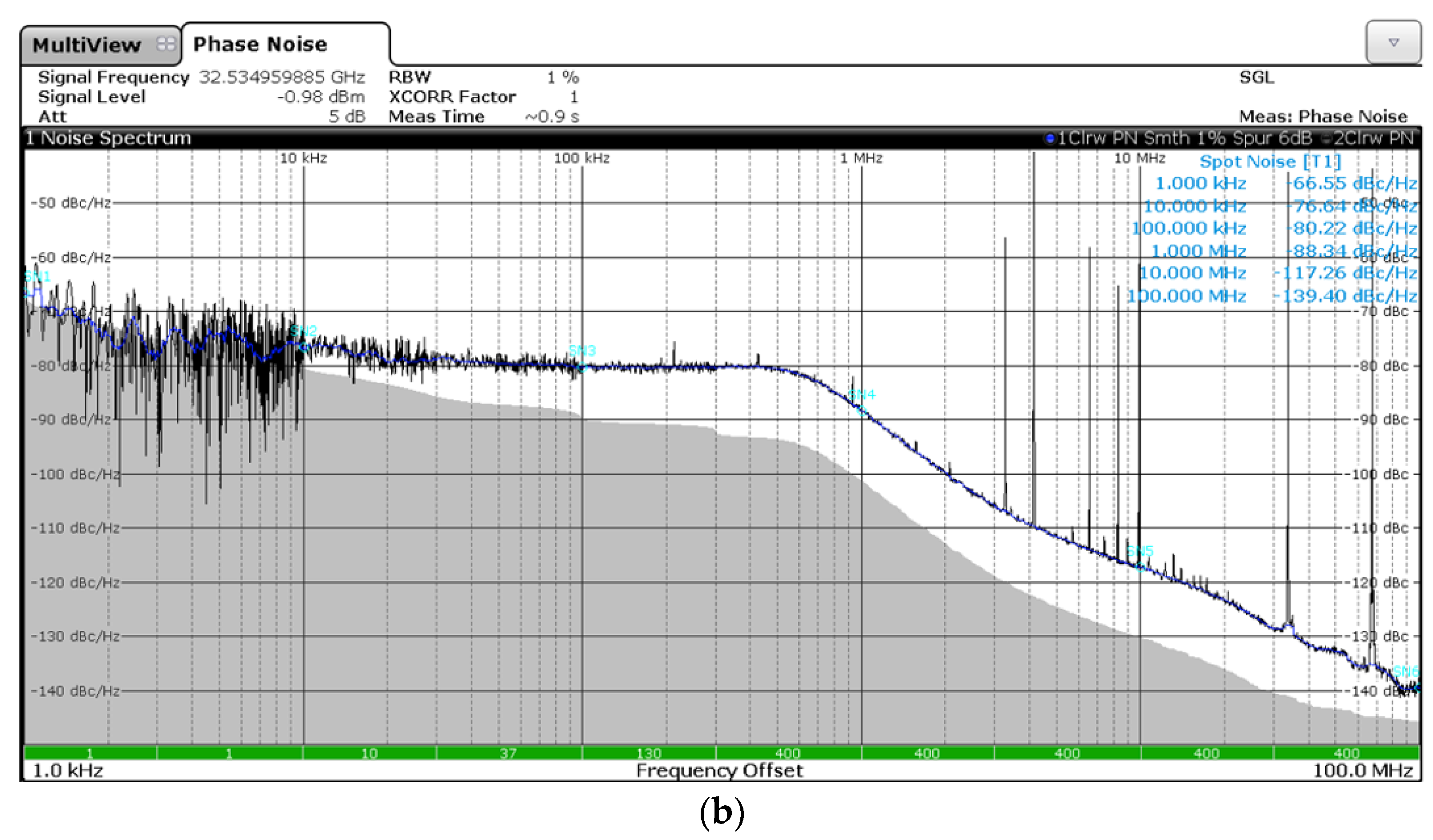

3. Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Pang, J.; Wu, R.; Wang, Y.; Dome, M.; Kato, H.; Huang, H.; Narayanan, A.T.; Liu, H.; Liu, B.; Nakamura, T.; et al. A 28-GHz CMOS phased-array transceiver based on LO phase-shifting architecture with gain invariant phase tuning for 5G new radio. IEEE J. Solid-State Circuits 2019, 54, 1228–1242. [Google Scholar] [CrossRef]

- Fang, S.J.; Zhang, F.; Bellaouar, A.; Embabi, S. A 28 GHz Sliding-IF Receiver in 22 nm FDSOI. In Proceedings of the IEEE 45th European Solid State Circuits Conference (ESSCIRC), Cracow, Poland, 23–26 September 2019; pp. 385–388. [Google Scholar]

- Wang, Y.; Wu, R.; Pang, J.; You, D.; Fadila, A.A.; Saengchan, R.; Fu, X.; Matsumoto, D.; Nakamura, T.; Kubozoe, R.; et al. A 39-GHz 64-element phased-array transceiver with built-in phase and amplitude calibrations for large-array 5G NR in 65-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 1249–1269. [Google Scholar] [CrossRef]

- Park, H.C.; Kang, D.; Lee, S.M.; Park, B.; Kim, K.; Lee, J.; Aoki, Y.; Yoon, Y.; Lee, S.; Lee, D.; et al. 4.1 A 39 GHz-band CMOS 16-channel phased array transceiver IC with a companion dual-stream IF transceiver IC for 5G NR base-station applications. In Proceedings of the 2020 IEEE International Solid- State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 76–78. [Google Scholar]

- Bozzola, S.; Guermandi, D.; Vecchi, F.; Repossi, M.; Pozzoni, M.; Mazzanti, A.; Svelto, F. A sliding IF receiver for mm-wave WLANs in 65 nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 13–16 September 2009; pp. 669–672. [Google Scholar]

- Sun, Y.; Schmalz, K.; Glisic, S.; Wang, R.; Scheytt, C.J. An integrated differential 60 GHz sliding-IF receiver in SiGe BiCMOS. In Proceedings of the 3rd International Conference on Computer Research and Development, Shanghai, China, 11–13 March 2011; pp. 297–300. [Google Scholar]

- IEEE Standard 802.11aj-2018; IEEE Standard for Information Technology–Telecommunications and Information Exchange Between Systems Local and Metropolitan Area Networks–Specific Requirements Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications Amendment 3: Enhancements for Very High Throughput to Support Chinese Millimeter Wave Frequency Bands (60 GHz and 45 GHz). Amendment to IEEE Standard 802.11-2016 as amended by IEEE Standard 802.11ai-2016 IEEE Standard 802.11ah-2016; IEEE: New York, NY, USA, 2018; pp. 1–306.

- Hong, W.; Wang, H.; Chen, J.; Zhang, N.; Zhang, Y.; Yang, G.; Yan, P.; Yu, C.; Chen, Z.; Liang, W.; et al. Recent advances in Q-LINKPAN/IEEE 802.11aj (45 GHz) millimeter wave communication technologies. In Proceedings of the 2013 Asia-Pacific Microwave Conference Proceedings (APMC), Seoul, Korea, 5–8 November 2013; pp. 227–229. [Google Scholar]

- Chen, H.-K.; Wang, T.; Lu, S.-S. A Millimeter-Wave CMOS Triple-Band Phase-Locked Loop with A Multimode LC-Based ILFD. IEEE Trans. Microw. Theory Tech. 2011, 59, 1327–1338. [Google Scholar] [CrossRef]

- Barale, F.; Sen, P.; Sarkar, S.; Pinel, S.; Laskar, J. A 60 GHz-Standard Compatible Programmable 50 GHz Phase-Locked Loop in 90 nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2010, 20, 411–413. [Google Scholar] [CrossRef]

- Richard, O.; Siligaris, A.; Badets, F.; Dehos, C.; Dufis, C.; Busson, P.; Vincent, P.; Belot, D.; Urard, P. A 17.5-to-20.94 GHz and 35-to-41.88 GHz PLL in 65 nm CMOS for Wireless HD Applications. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference-(ISSCC), 7–11 February 2010; pp. 252–254. [Google Scholar]

- Murphy, D.; Gu, Q.J.; Wu, Y.C.; Jian, H.Y.; Xu, Z.; Tang, A.; Wang, F.; Chang, M.C.F. A Low Phase Noise, Wideband and Compact CMOS PLL for Use in a Heterodyne 802.15.3c Transceiver. IEEE J. Solid-State Circuits 2011, 46, 1606–1617. [Google Scholar] [CrossRef]

- Park, J.; Ryu, H.; Ha, K.-W.; Kim, J.-G.; Baek, D. 76–81-GHz CMOS transmitter with a phase-locked-loopbased multichirp modulator for automotive radar. IEEE Transections Microw. Theory Tech. 2015, 63, 1399–1408. [Google Scholar] [CrossRef]

- Milosavljevic, I.M.; Glavonjic, D.P.; Krcum, D.P.; Jovanovic, S.P.; Mihajlovic, V.R.; Milovanovic, V.M. A 55–64-GHz Fully Integrated Miniaturized FMCW Radar Sensor Module for Short-Range Applications. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 677–679. [Google Scholar] [CrossRef]

- Ergintav, A.; Herzel, F.; Fischer, G.; Kissinger, D. Multiplexed Twin PLLs for Wide-Band FMCW Chirp Generation in 130-nm BiCMOS. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 483–485. [Google Scholar] [CrossRef]

- Chen, Z.; Wang, M.; Chen, J.-X.; Liang, W.-F.; Yan, P.-P.; Zhai, J.-F.; Hong, W. Linear CMOS LC-VCO Based on Triple-Coupled Inductors and Its Application to 40-GHz Phase-Locked Loop. IEEE Trans. Microw. Theory Tech. 2017, 65, 2977–2989. [Google Scholar] [CrossRef]

- Chen, Z.; Hou, D.; Chen, J.-X.; Yan, P.; Bao, L.; Hong, Z.; Zheng, Y. A K-Band FMCW Frequency Synthesizer Using Q-Boosted Switched Inductor VCO in SiGe BiCMOS for 77 GHz Radar Applications. Electronics 2020, 9, 1933. [Google Scholar] [CrossRef]

| Ref. | Tech. | Topology | Freq. (GHz) | Phase Noise 1 @100 kHz | Phase Noise 1 @10 MHz | Ref. Spur (dBc) | Power (mW) |

|---|---|---|---|---|---|---|---|

| [9] | 90 nm CMOS | Single Loop | 39.7~41.2 | −62.3 | −111.5 | −38 | 110 |

| [10] | 90 nm CMOS | Single Loop | 39.1~41.6 | −60.6 | −114.5 | −54 | 64 2 |

| [11] | 65 nm CMOS | Single Loop | 35~41.88 | −67.9 | −122.1 | −50 | 80 |

| [16] | 90 nm CMOS | Single Loop | 38.61~44.55 | −84.9 | −116.9 | −46 | 76 2 |

| This Work (Loop1) | 0.13-μm SiGe | Dual Loop | 12.96 | −81.6 | −121.8 | −69 | 153 2 |

| This Work (Loop2) | 0.13-μm SiGe | 29.835~35.1 | −81.2 | −118.1 | −68 | 167 2 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, Z.; Hou, D.; Chen, J.; Yan, P. A Low Phase Noise Dual-Loop Dual-Output Frequency Synthesizer in SiGe BiCMOS. Electronics 2022, 11, 1828. https://doi.org/10.3390/electronics11121828

Chen Z, Hou D, Chen J, Yan P. A Low Phase Noise Dual-Loop Dual-Output Frequency Synthesizer in SiGe BiCMOS. Electronics. 2022; 11(12):1828. https://doi.org/10.3390/electronics11121828

Chicago/Turabian StyleChen, Zhe, Debin Hou, Jixin Chen, and Pinpin Yan. 2022. "A Low Phase Noise Dual-Loop Dual-Output Frequency Synthesizer in SiGe BiCMOS" Electronics 11, no. 12: 1828. https://doi.org/10.3390/electronics11121828

APA StyleChen, Z., Hou, D., Chen, J., & Yan, P. (2022). A Low Phase Noise Dual-Loop Dual-Output Frequency Synthesizer in SiGe BiCMOS. Electronics, 11(12), 1828. https://doi.org/10.3390/electronics11121828