A 0.17 pJ/bit 28 Gb/s/pin Single-Ended PAM-4 Transmitter for On-Chip Short-Reach Unterminated Channels

Abstract

:1. Introduction

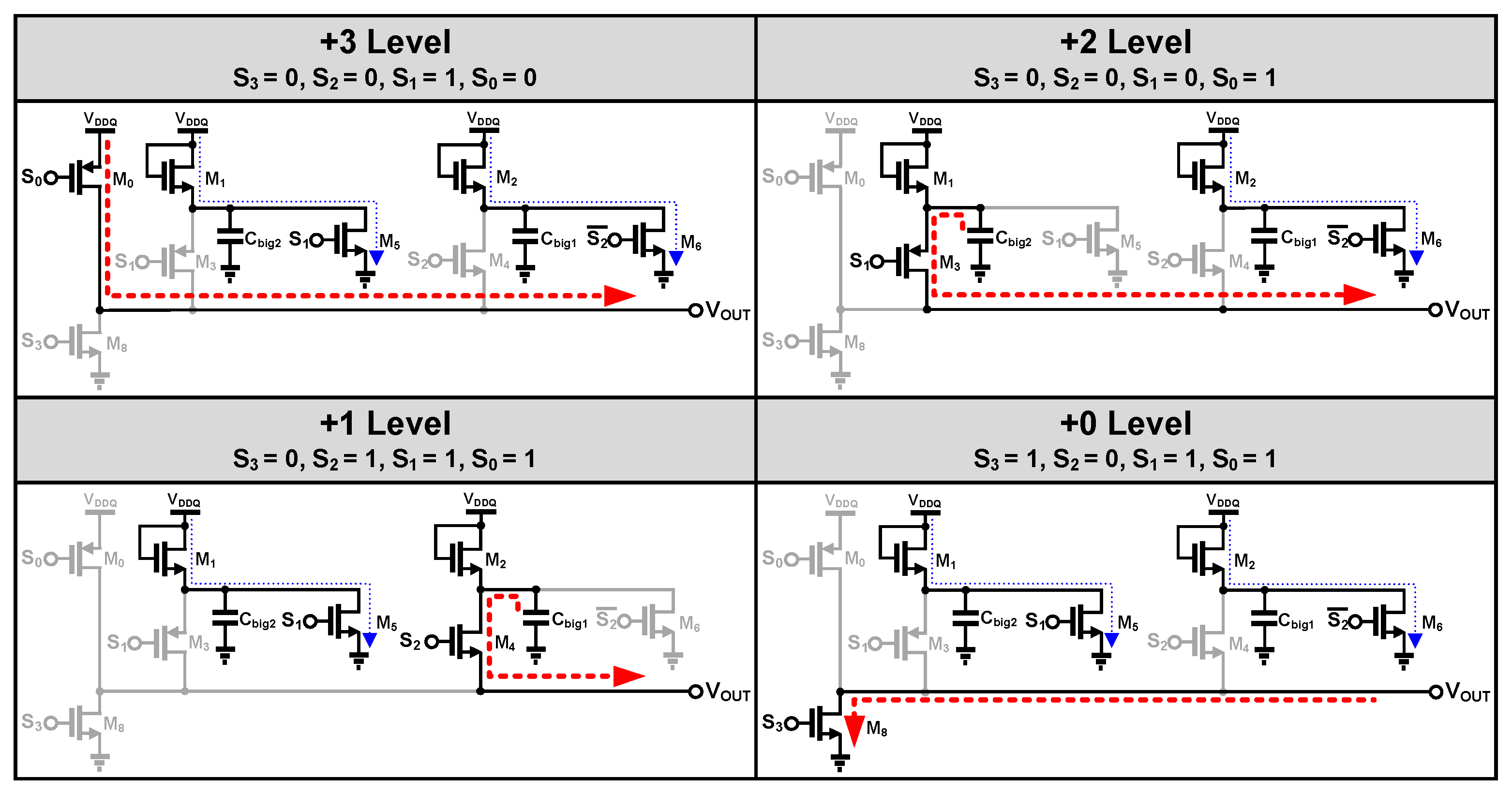

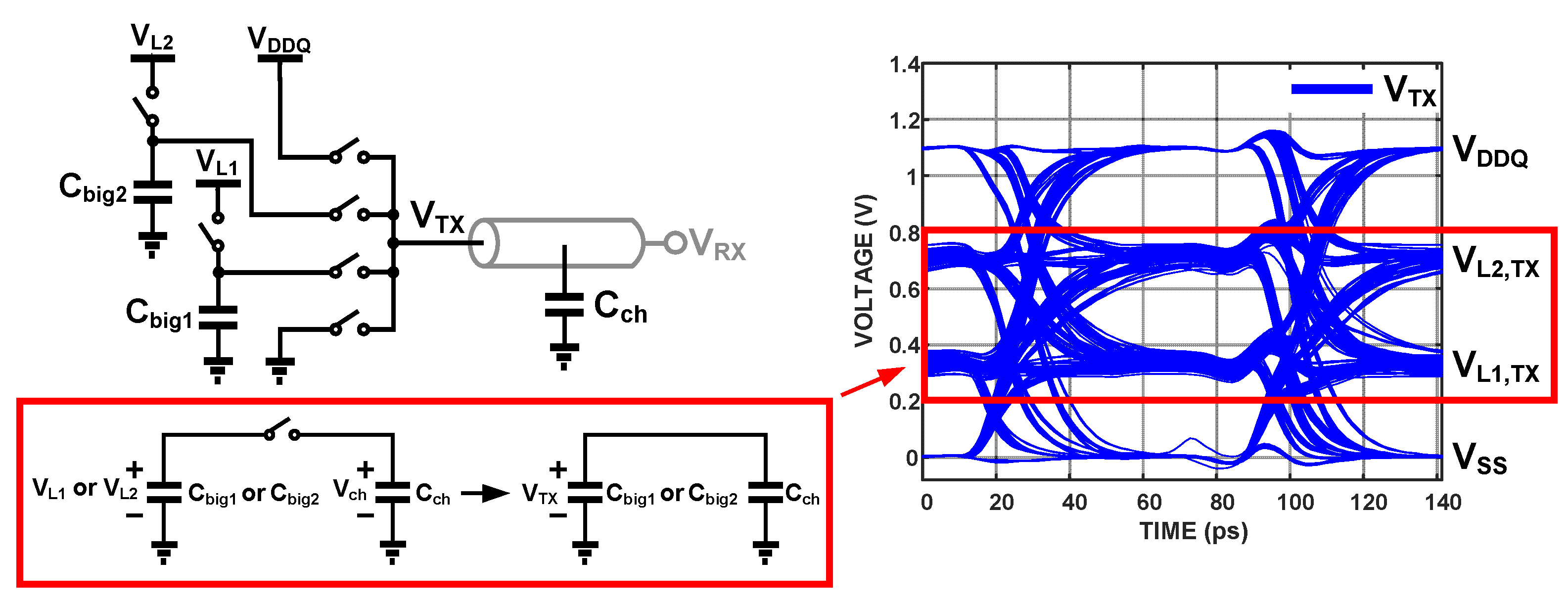

2. Transmitter Architecture

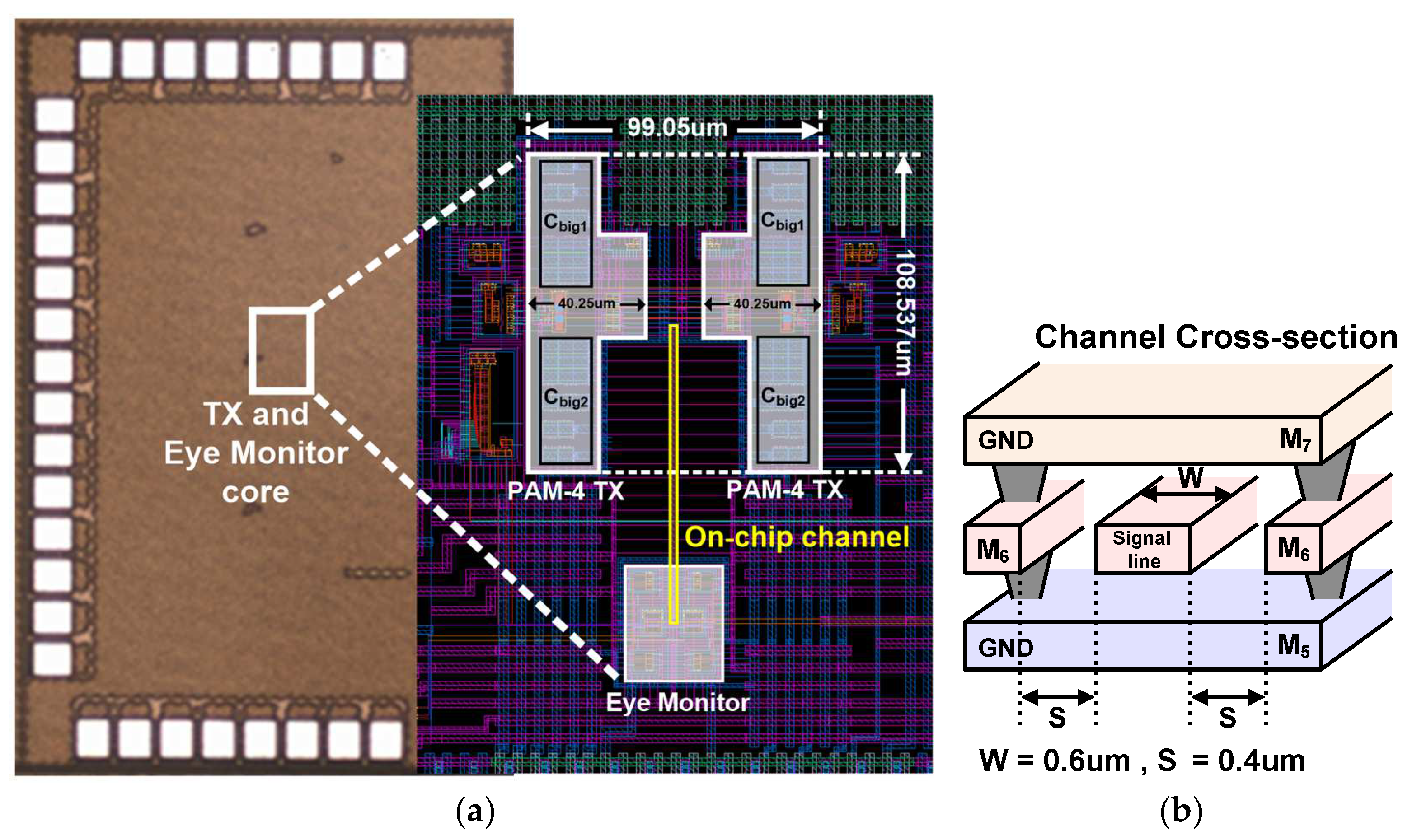

3. Circuit Implementation

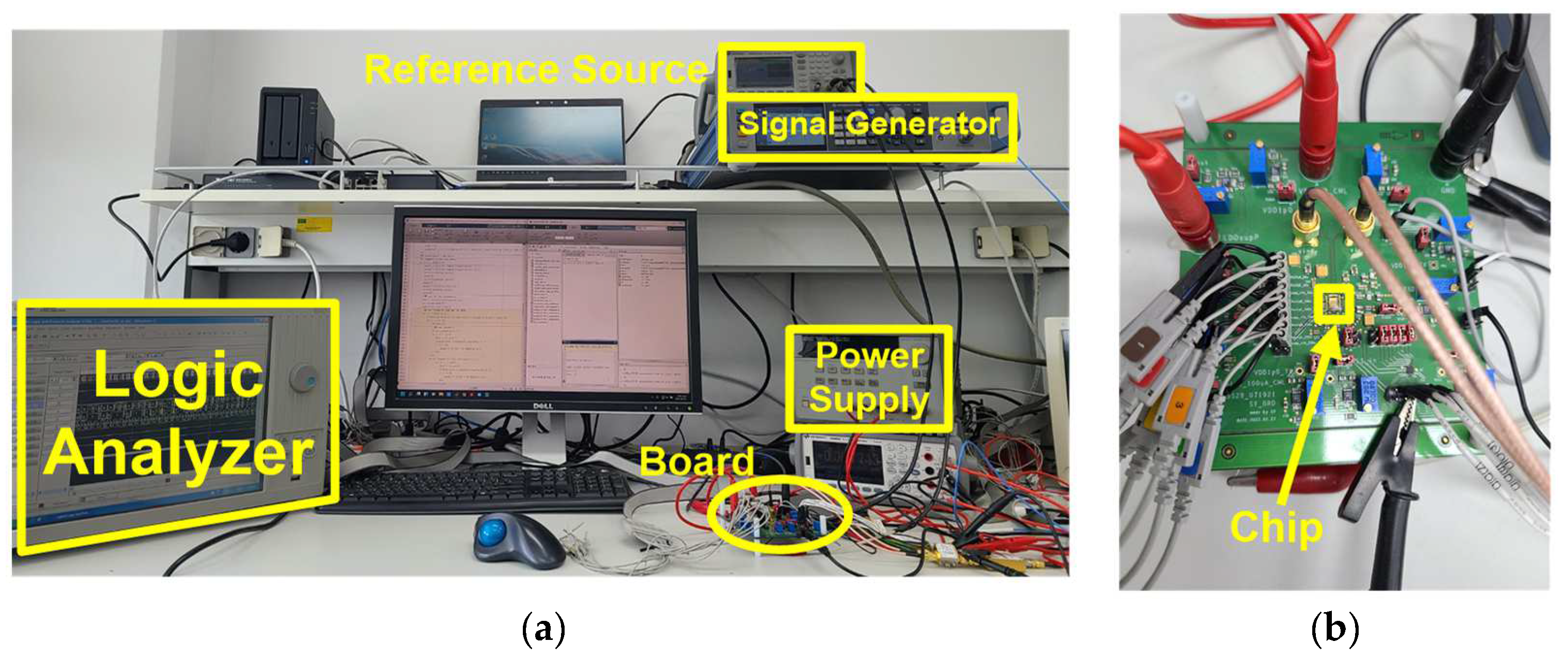

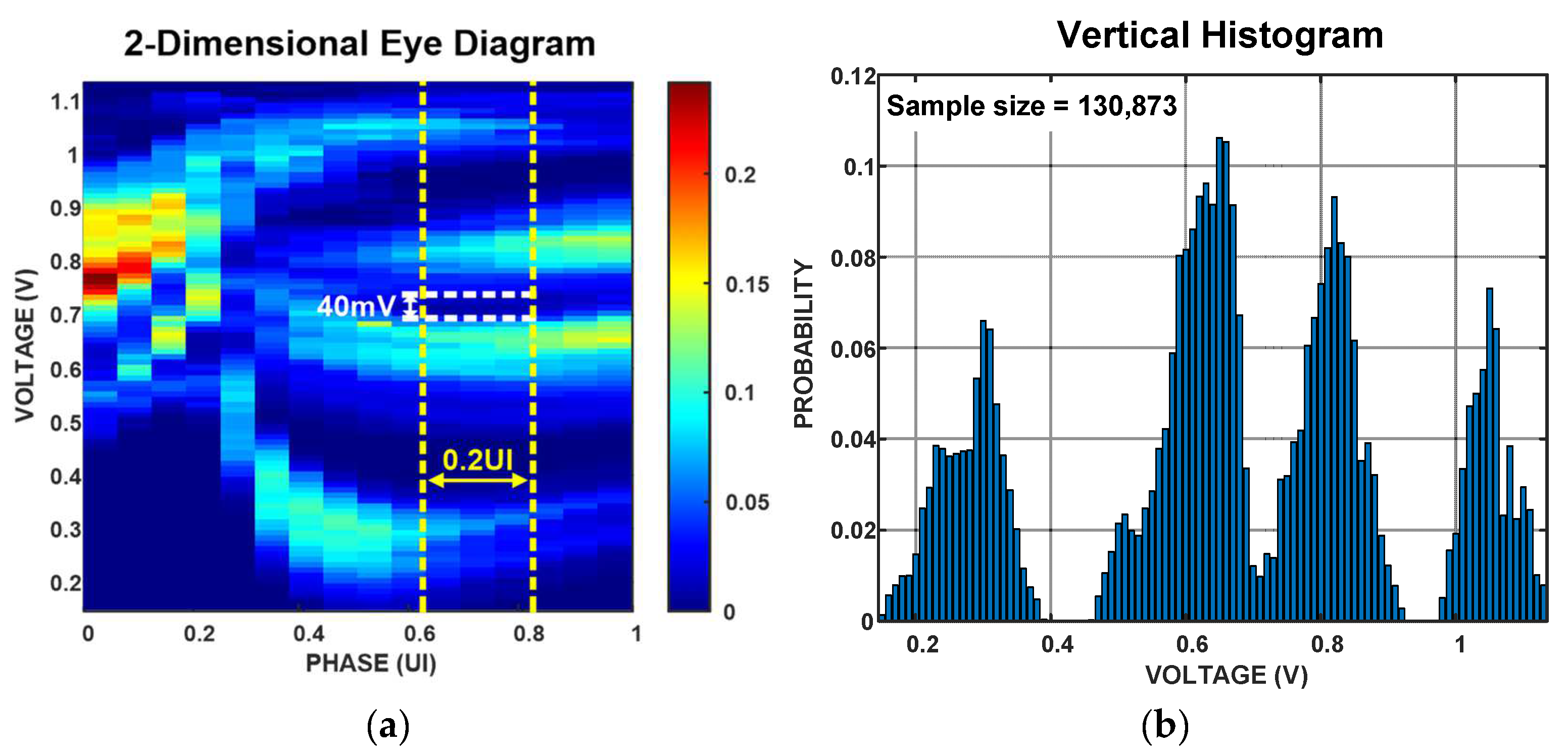

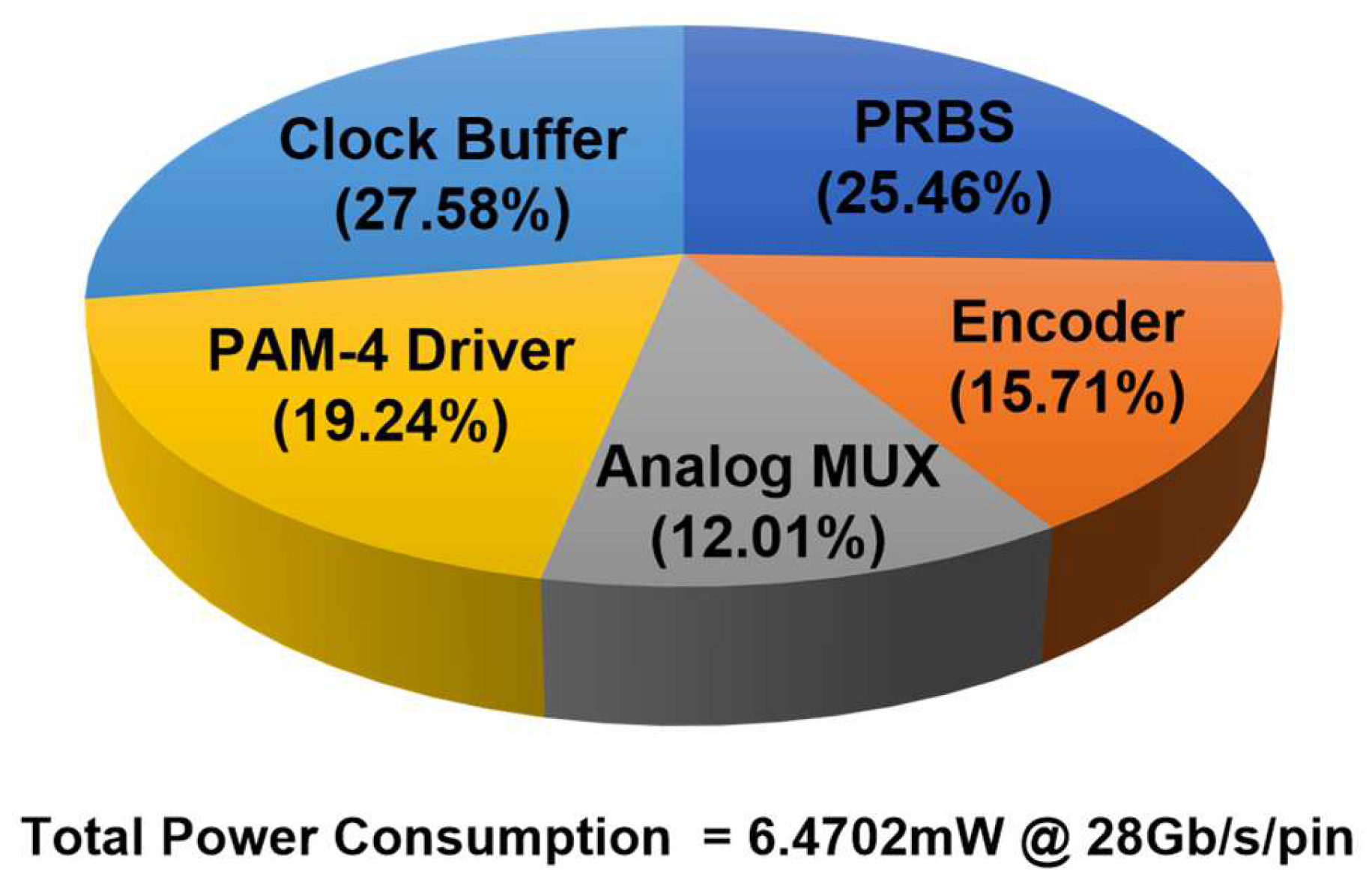

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Hollis, T.M.; Schneider, R.; Brox, M.; Hein, T.; Spirkl, W.; Bach, M.; Balakrishnan, M.; Dietrich, S.; Funfrock, F.; Ivanov, M.; et al. An 8-Gb GDDR6X DRAM Achieving 22 Gb/s/pin With Single-Ended PAM-4 Signaling. IEEE J. Solid-State Circuits 2022, 57, 224–235. [Google Scholar] [CrossRef]

- Kim, J.; Kundu, S.; Balankutty, A.; Beach, M.; Kim, B.C.; Kim, S.; Liu, Y.; Murthy, S.K.; Wali, P.; Yu, K.; et al. A 224 Gb/s DAC-Based PAM-4 Transmitter with 8-Tap FFE in 10 nm CMOS. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 126–128. [Google Scholar] [CrossRef]

- Hyun, C.; Jeong, Y.-U.; Kim, S.; Chae, J.-H. An 18-Gb/s/pin Single-Ended PAM-4 Transmitter for Memory Interfaces with Adaptive Impedance Matching and Output Level Compensation. Electronics 2021, 10, 1768. [Google Scholar] [CrossRef]

- Seo, J.; Lee, S.; Lee, M.; Moon, C.; Kim, B. A 20-Gb/s/pin 0.0024-mm2 Single-Ended DECS TRX with CDR-less Self-Slicing/Auto-Deserialization to Improve Tolerance on Duty Cycle Error and RX Supply Noise for DCC/CDR-less Short-Reach Memory Interfaces. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 1–3. [Google Scholar] [CrossRef]

- Kossel, M.; Toifl, T.; Francese, P.A.; Brändli, M.; Menolfi, C.; Buchmann, P.; Kull, L.; Andersen, T.M.; Morf, T. An 8Gb/s 1.5 mW/Gb/s 8-tap 6b NRZ/PAM-4 Tomlinson-Harashima precoding transmitter for future memory-link applications in 22 nm CMOS. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 408–409. [Google Scholar] [CrossRef]

- Lee, J.; Lee, W.; Cho, S. A 2.5-Gb/s On-Chip Interconnect Transceiver with Crosstalk and ISI Equalizer in 130 nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 124–136. [Google Scholar] [CrossRef]

- Kulkarni, V.V.; Lim, W.Y.; Zhao, B.; Yan, D.L.; Wang, Y.S.; Zhou, J.; Arasu, M.A. A 5.1 Gb/s 60.3 fJ/bit/mm PVT tolerant NoC transceiver. In Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; pp. 141–144. [Google Scholar] [CrossRef]

- Lee, S.; Yun, J.; Kim, S. A 78.8 fJ/b/mm 12.0 Gb/s/Wire Capacitively Driven On-Chip Link Over 5.6 mm with an FFE-Combined Ground-Forcing Biasing Technique for DRAM Global Bus Line in 65 nm CMOS. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 454–456. [Google Scholar] [CrossRef]

- Mensink, E.; Schinkel, D.; Klumperink, E.A.M.; van Tuijl, E.; Nauta, B. Power Efficient Gigabit Communication Over Capacitively Driven RC-Limited On-Chip Interconnects. IEEE J. Solid-State Circuits 2010, 45, 447–457. [Google Scholar] [CrossRef]

- Hsu, Y.-Y.; Kuo, P.-C.; Chuang, C.-L.; Chang, P.-H.; Shen, H.-H.; Chiang, C.-F. A 7 nm 0.46 pJ/bit 20 Gbps with BER 1E-25 Die-to-Die Link Using Minimum Intrinsic Auto Alignment and Noise-Immunity Encode. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [Google Scholar]

- Park, H.; Choi, Y.; Sim, J.; Choi, J.; Kwon, Y.; Song, J.; Kim, C. A 0.385-pJ/bit 10-Gb/s TIA-Terminated Di-Code Transceiver with Edge-Delayed Equalization, ECC, and Mismatch Calibration for HBM Interfaces. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 1–3. [Google Scholar] [CrossRef]

| Low Speed On-Chip Transmitter | High Speed On-Chip Transmitter | ||||||

|---|---|---|---|---|---|---|---|

| [9] JSSC’10 | [6] TCAS-Ⅰ’12 | [7] ASSCC’16 | [10] VLSI’21 | [11] ISSCC’22 | [4] ISSCC’22 | This work | |

| Technology | 90 nm CMOS | 130 nm CMOS | 28 nm CMOS | 7 nm CMOS | 28 nm CMOS | 28 nm CMOS | 28 nm CMOS |

| Signaling | NRZ | NRZ | RZ/NRZ | NRZ | Di-code | NRZ (* DECS) | PAM-4 |

| Line Type | On-chip metal | On-chip metal | On-chip metal | Si-interposer | On-chip Metal | On-chip metal | On-chip metal |

| Supply Voltage(V) | 1.2 | N/A | 0.9/1 | 0.8 | 1.0 (TX)/1.2 (RX) | N/A | 1.1 |

| Data Rate (Gb/s) | 2 | 2.5 | 4.4 | 20 | 10 | 20 | 28 |

| Energy Efficiency | ** 0.28 pJ/b | 0.06 pJ/b | 0.0524 pJ/b/mm | ** 0.46 pJ/b | ** 0.385 pJ/b | 1.09 pJ/b | 0.17 pJ/b |

| Channel Length | 10 mm | 10 mm | 1 mm | 1 mm | 6 mm | 1 mm | |

| Area (mm2) | N/A | 0.0034 | 0.015 | N/A | ** 0.0046 | 0.002428 | 0.008673 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, S.; Kim, J. A 0.17 pJ/bit 28 Gb/s/pin Single-Ended PAM-4 Transmitter for On-Chip Short-Reach Unterminated Channels. Electronics 2022, 11, 2525. https://doi.org/10.3390/electronics11162525

Park S, Kim J. A 0.17 pJ/bit 28 Gb/s/pin Single-Ended PAM-4 Transmitter for On-Chip Short-Reach Unterminated Channels. Electronics. 2022; 11(16):2525. https://doi.org/10.3390/electronics11162525

Chicago/Turabian StylePark, Soyeon, and Jintae Kim. 2022. "A 0.17 pJ/bit 28 Gb/s/pin Single-Ended PAM-4 Transmitter for On-Chip Short-Reach Unterminated Channels" Electronics 11, no. 16: 2525. https://doi.org/10.3390/electronics11162525

APA StylePark, S., & Kim, J. (2022). A 0.17 pJ/bit 28 Gb/s/pin Single-Ended PAM-4 Transmitter for On-Chip Short-Reach Unterminated Channels. Electronics, 11(16), 2525. https://doi.org/10.3390/electronics11162525