Recent Trends in Copper Metallization

Abstract

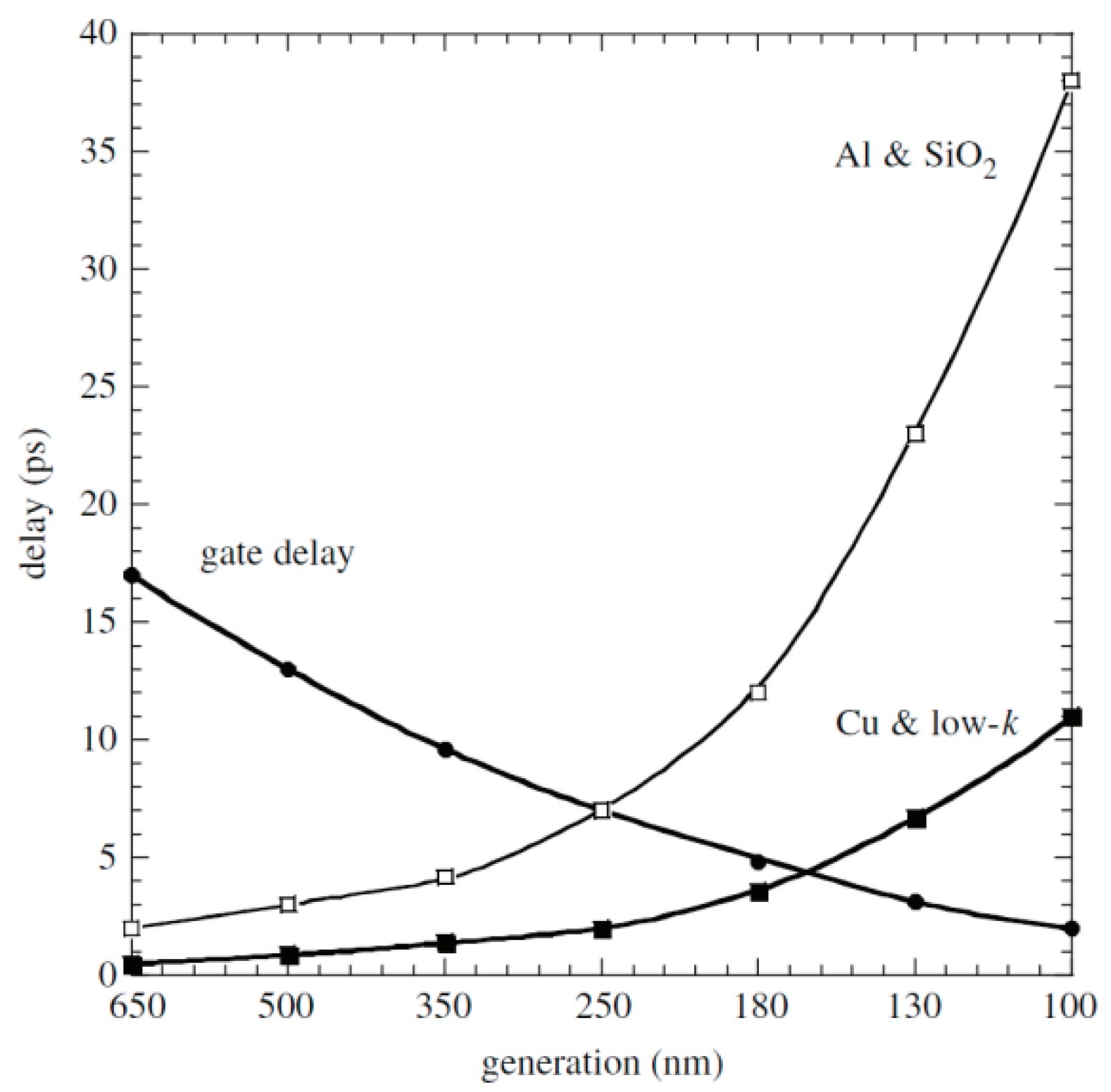

:1. Introduction

2. Cu Dual-Damascene Interconnects

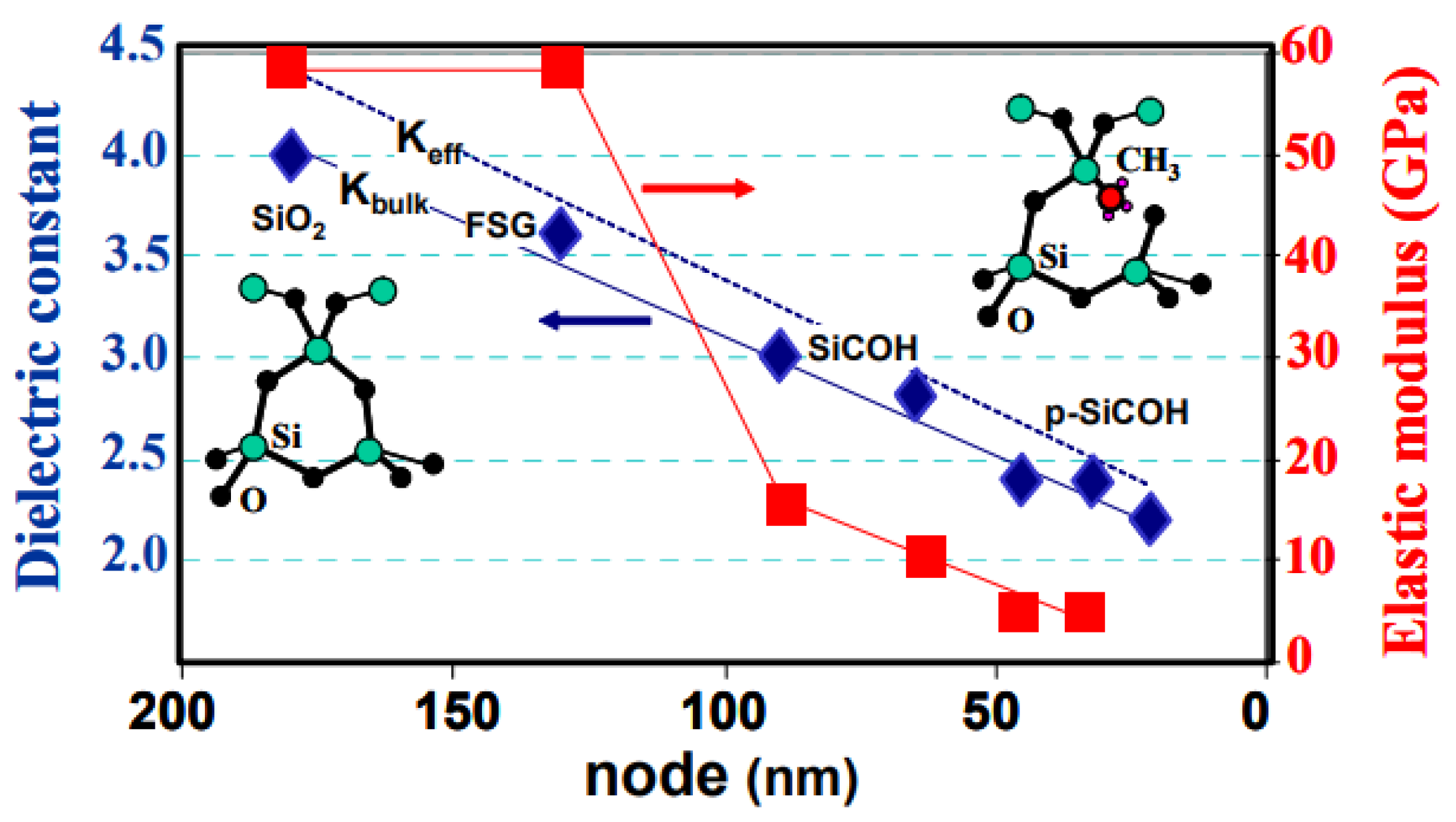

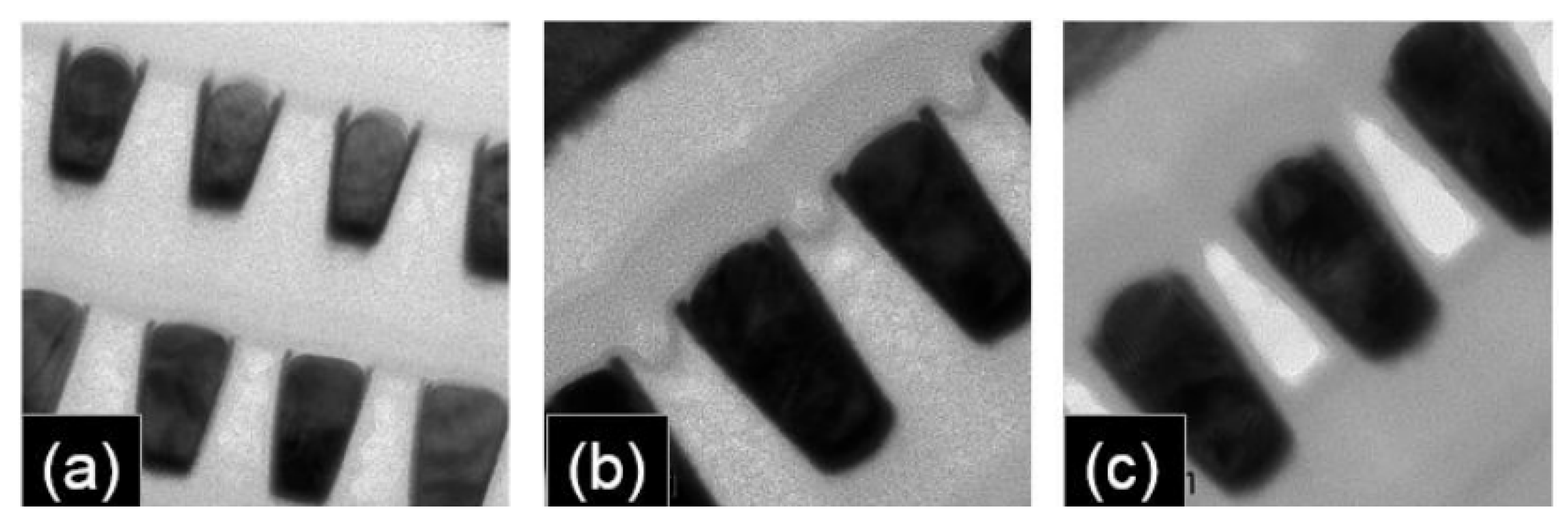

3. Low-k Dielectric Materials

4. Metallization

4.1. TaN Barrier/Liner Scaling

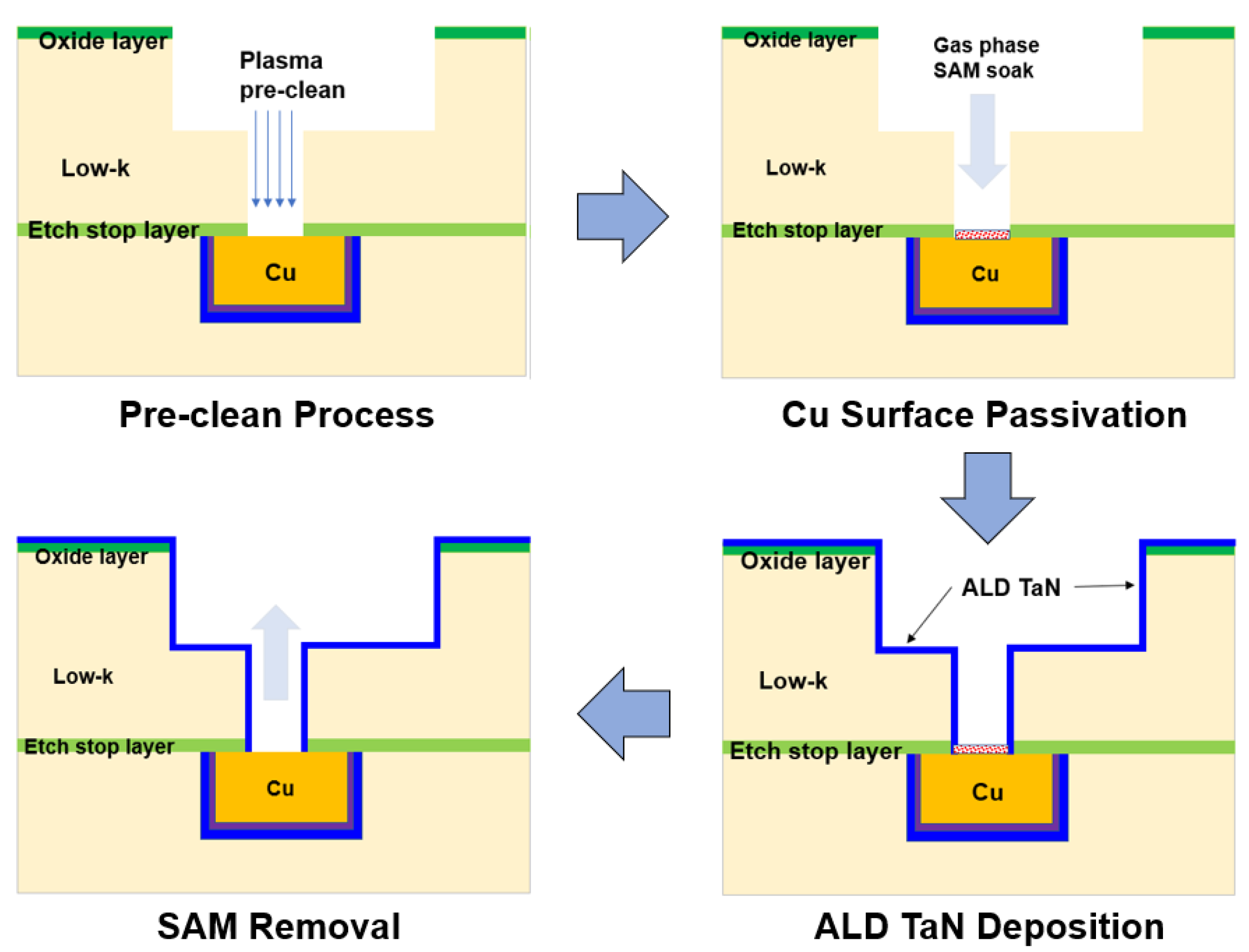

4.2. Selective Barrier Schemes

4.3. Self-Forming Barriers

4.4. Hybrid Metallization

4.5. Alternative Metals

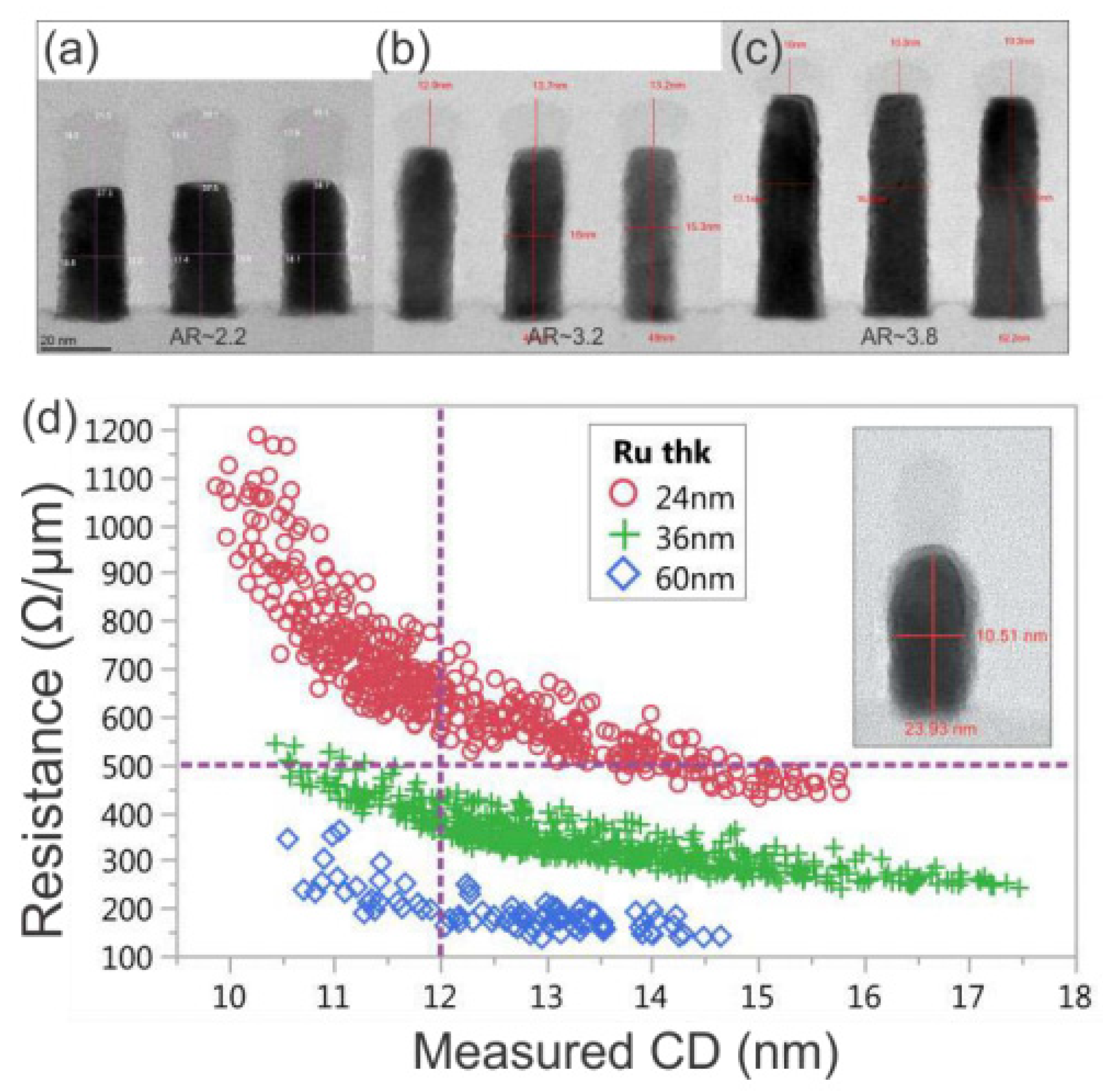

4.6. Ru Semi-Damascene Schemes

5. Reliability

5.1. Electromigration

5.2. Time-Dependent Dielectric Breakdown

6. Summary

Funding

Data Availability Statement

Conflicts of Interest

References

- Davis, J.A.; Venkatesan, R.; Kaloyeros, A.; Beylansky, M.; Souri, S.; Banerjee, K.; Saraswat, K.; Rahman, A.; Reif, R.; Meindl, J. Interconnect limits on gigascale integration (GSI) in the 21st century. Proc. IEEE 2001, 89, 305–324. [Google Scholar] [CrossRef]

- Bonilla, G.; Lanzillo, N.; Hu, C.-K.; Penny, C.; Kumar, A. Interconnect scaling challenges, and opportunities to enable system-level performance beyond 30 nm pitch. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020. [Google Scholar] [CrossRef]

- Theis, T.N. The future of interconnection technology. IBM J. Res. Dev. 2000, 44, 379–390. [Google Scholar] [CrossRef]

- Havemann, R.; Hutchby, J. High-performance interconnects: An integration overview. Proc. IEEE 2001, 89, 586–601. [Google Scholar] [CrossRef]

- Baccarani, G.; Wordeman, M.; Dennard, R. Generalized scaling theory and its application to a ¼ micrometer MOSFET design. IEEE Trans. Electron Devices 1984, 31, 452–462. [Google Scholar] [CrossRef]

- Cheng, Y.-L.; Lee, C.-Y. Porous low-dielectric-constant material for semiconductor microelectronics. In Nanofluid Flow in Porous Media; IntechOpen: London, UK, 2018. [Google Scholar] [CrossRef]

- Saito, T.; Imai, T.; Noguchi, J.; Kubo, M.; Ito, Y.; Omori, S.; Ohashi, N.; Tamaru, T.; Yamaguchi, H. A high performance liner for copper damascene interconnects. In Proceedings of the IEEE 2001 International Interconnect Technology Conference (Cat. No. 01EX461), Burlingame, CA, USA, 6 June 2001. [Google Scholar] [CrossRef]

- Edelstein, D.; Heidenreich, J.; Goldblatt, R.; Cote, W.; Uzoh, C.; Lustig, N.; Roper, P.; McDevitt, T.; Motsiff, W.; Simon, A.; et al. Full copper wiring in a sub-0.25/spl mu/m CMOS ULSI technology. In Proceedings of the International Electron Devices Meeting. IEDM Technical Digest, Washington, DC, USA, 10 December 1997. [Google Scholar] [CrossRef]

- Grill, A.; Gates, S.M.; Ryan, T.E.; Nguyen, S.V.; Priyadarshini, D. Progress in the development and understanding of advanced low k and ultralow k dielectrics for very large-scale integrated interconnects—State of the art. Appl. Phys. Rev. 2014, 1, 011306. [Google Scholar] [CrossRef]

- Grill, A. Porous pSiCOH ultralow-k dielectrics for chip interconnects prepared by PECVD. Annu. Rev. Mater. Res. 2009, 39, 49–69. [Google Scholar] [CrossRef]

- Lionti, K.; Volksen, W.; Magbitang, T.; Darnon, M.; Dubois, G.; Lyu, Y.-R.; Hsieh, T.-E. Toward successful integration of porous low-k materials: Strategies addressing plasma damage. ECS J. Solid State Sci. Technol. 2014, 4, N3071. [Google Scholar] [CrossRef]

- Cheng, Y.-L.; Lee, C.-Y.; Huang, Y.-L. Copper metal for semiconductor interconnects. In Noble and Precious Metals-Properties, Nanoscale Effects and Applications; IntechOpen: London, UK, 2018; pp. 220–221. [Google Scholar] [CrossRef]

- Simon, A.; van der Straten, O.; Lanzillo, N.A.; Yang, C.-C.; Nogami, T.; Edelstein, D.C. Role of high aspect-ratio thin-film metal deposition in Cu back-end-of-line technology. J. Vac. Sci. Technol. A Vac. Surf. Film. 2020, 38, 053402. [Google Scholar] [CrossRef]

- Croes, K.; Adelmann, C.; Wilson, C.J.; Zahedmanesh, H.; Pedreira, O.V.; Wu, C.; Leśniewska, A.; Oprins, H.; Beyne, S.; Ciofi, I.; et al. Interconnect metals beyond copper: Reliability challenges and opportunities. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018. [Google Scholar] [CrossRef]

- Decoster, S.; Camerotto, E.; Murdoch, G.; Kundu, S.; Le, Q.T.; Tőkei, Z.; Jurczak, G.; Lazzarino, F. Patterning challenges for direct metal etch of ruthenium and molybdenum at 32 nm metal pitch and below. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2022, 40, 032802. [Google Scholar] [CrossRef]

- Paolillo, S.; Wan, D.; Lazzarino, F.; Rassoul, N.; Piumi, D.; Tőkei, Z. Direct metal etch of ruthenium for advanced interconnect. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2018, 36, 03E103. [Google Scholar] [CrossRef]

- Murdoch, G.; O’Toole, M.; Marti, G.; Pokhrel, A.; Tsvetanova, D.; Decoster, S.; Kundu, S.; Oniki, Y.; Thiam, A.; Le, Q.; et al. First demonstration of Two Metal Level Semi-damascene Interconnects with Fully Self-aligned Vias at 18MP. In Proceedings of the 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 13–17 June 2022. [Google Scholar] [CrossRef]

- Gambino, J.; Chen, F.; He, J. Copper interconnect technology for the 32 nm node and beyond. In Proceedings of the 2009 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 13–16 September 2009. [Google Scholar] [CrossRef]

- Kriz, J.; Angelkort, C.; Czekalla, M.; Huth, S.; Meinhold, D.; Pohl, A.; Schulte, S.; Thamm, A.; Wallace, S. Overview of dual damascene integration schemes in Cu BEOL integration. Microelectron. Eng. 2008, 85, 2128–2132. [Google Scholar] [CrossRef]

- Lloyd, J.; Murray, C.; Ponoth, S.; Cohen, S.; Liniger, E. The effect of Cu diffusion on the TDDB behavior in a low-k interlevel dielectrics. Microelectron. Reliab. 2006, 46, 1643–1647. [Google Scholar] [CrossRef]

- Tsu, R.; McPherson, J.W.; McKee, W.R. Leakage and breakdown reliability issues associated with low-k dielectrics in a dual-damascene Cu process. In Proceedings of the 2000 IEEE International Reliability Physics Symposium Proceedings 38th Annual (Cat. No. 00CH37059), San Jose, CA, USA, 10–13 April 2000. [Google Scholar] [CrossRef]

- McPherson, J.W. Time dependent dielectric breakdown in copper low-k interconnects: Mechanisms and reliability models. Materials 2012, 5, 1602–1625. [Google Scholar] [CrossRef]

- Edelstein, D.; Uzoh, C.; Cabral, C.; DeHaven, P.; Buchwalter, P.; Simon, A.; Cooney, E.; Malhotra, S.; Klaus, D.; Rathore, H.; et al. A high performance liner for copper damascene interconnects. In Proceedings of the IEEE 2001 International Interconnect Technology Conference (Cat. No. 01EX461), Burlingame, CA, USA, 6 June 2001. [Google Scholar] [CrossRef]

- Shamiryan, D.; Abell, T.; Iacopi, F.; Maex, K. Low-k dielectric materials. Mater. Today 2004, 7, 34–39. [Google Scholar] [CrossRef]

- Maex, K.; Baklanov, M.R.; Shamiryan, D.; Lacopi, F.; Brongersma, S.H.; Yanovitskaya, Z.S. Low dielectric constant materials for microelectronics. J. Appl. Phys. 2003, 93, 8793–8841. [Google Scholar] [CrossRef]

- Cheng, Y.; Wang, Y.; Liu, C.; Wu, Y.; Lo, K.; Lan, J. Characterization and reliability of low dielectric constant fluorosilicate glass and silicon rich oxide process for deep sub-micron device application. Thin Solid Films 2001, 398, 533–538. [Google Scholar] [CrossRef]

- Hoofman, R.; Verheijden, G.; Michelon, J.; Iacopi, F.; Travaly, Y.; Baklanov, M.; Tökei, Z.; Beyer, G. Challenges in the implementation of low-k dielectrics in the back-end of line. Microelectron. Eng. 2005, 80, 337–344. [Google Scholar] [CrossRef]

- Sankaran, S.; Arai, S.; Augur, R.; Beck, M.; Biery, G.; Bolom, T.; Bonilla, G.; Bravo, O.; Chanda, K.; Chae, M.; et al. A 45 nm CMOS node Cu/Low-k/Ultra Low-k PECVD SiCOH (k = 2.4) BEOL technology. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006. [Google Scholar] [CrossRef]

- Travaly, Y.; van Aelst, J.; Truffert, V.; Verdonck, P.; Dupont, T.; Camerotto, E.; Richard, O.; Bender, H.; Kroes, C.; de Roest, D.; et al. Key factors to sustain the extension of a MHM-based integration scheme to medium and high porosity PECVD low-k materials. In Proceedings of the 2008 International Interconnect Technology Conference, Burlingame, CA, USA, 1–4 June 2008. [Google Scholar] [CrossRef]

- King, S.W. Dielectric barrier, etch stop, and metal capping materials for state of the art and beyond metal interconnects. ECS J. Solid State Sci. Technol. 2014, 4, N3029. [Google Scholar] [CrossRef]

- Cheng, Y.-L.; Chen, S.-A.; Chiu, T.-J.; Wu, J.; Wei, B.-J.; Chang, H.-J. Electrical and reliability performances of nitrogen-incorporated silicon carbide dielectric by chemical vapor deposition. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2010, 28, 573–576. [Google Scholar] [CrossRef]

- Cheng, Y.-L.; Chiu, T.-J.; Wei, B.-J.; Wang, H.-J.; Wu, J.; Wang, Y.-L. Effect of copper barrier dielectric deposition process on characterization of copper interconnect. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2010, 28, 567–572. [Google Scholar] [CrossRef]

- Nitta, S.; Edelstein, D.; Ponoth, S.; Clevenger, L.; Liu, X.; Standaert, T. Performance and reliability of airgaps for advanced BEOL interconnects. In Proceedings of the 2008 International Interconnect Technology Conference, Burlingame, CA, USA, 1–4 June 2008. [Google Scholar] [CrossRef]

- Chen, H.-W.; Jeng, S.-P.; Tsai, H.-Y.; Liu, Y.-W.; Yu, C.; Sun, Y. A self-aligned air gap interconnect process. In Proceedings of the 2008 International Interconnect Technology Conference, Burlingame, CA, USA, 1–4 June 2008. [Google Scholar] [CrossRef]

- Nakamura, N.; Matsunaga, N.; Kaminatsui, T.; Watanabe, K.; Shibata, H. Cost-effective air-gap interconnects by all-in-one post-removing process. In Proceedings of the 2008 International Interconnect Technology Conference, Burlingame, CA, USA, 1–4 June 2008. [Google Scholar] [CrossRef]

- Uno, S.; Noguchi, J.; Ashihara, H.; Oshima, T.; Sato, K.; Konishi, N.; Saito, T.; Hara, K. Dual damascene process for air-gap Cu interconnects using conventional CVD films as sacrificial layers. In Proceedings of the IEEE 2005 International Interconnect Technology Conference, Burlingame, CA, USA, 6–8 June 2005. [Google Scholar] [CrossRef]

- Noguchi, J.; Sato, K.; Konishi, N.; Uno, S.; Oshima, T.; Ishikawa, K.; Ashihara, H.; Saito, T.; Kubo, M.; Tamaru, T.; et al. Process and reliability of air-gap Cu interconnect using 90-nm node technology. IEEE Trans. Electron Devices 2005, 52, 352–359. [Google Scholar] [CrossRef]

- Fischer, K.; Agostinelli, M.; Allen, C.; Bahr, D.; Bost, M.; Charvat, P.; Chikarmane, V.; Fu, Q.; Ganpule, C.; Haran, M.; et al. Low-k interconnect stack with multi-layer air gap and tri-metal-insulator-metal capacitors for 14nm high volume manufacturing. In Proceedings of the 2015 IEEE International Interconnect Technology Conference and 2015 IEEE Materials for Advanced Metallization Conference (IITC/MAM), Grenoble, France, 18–21 May 2015. [Google Scholar] [CrossRef]

- Fischer, K.; Chang, H.; Ingerly, D.; Jin, I.; Kilambi, H.; Longun, J.; Patel, R.; Pelto, C.; Petersburg, C.; Plekhanov, P.; et al. Performance enhancement for 14nm high volume manufacturing microprocessor and system on a chip processes. In Proceedings of the 2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), San Jose, CA, USA, 23–26 May 2016. [Google Scholar] [CrossRef]

- Penny, C.; Gates, S.; Peethala, B.; Lee, J.; Priyadarshini, D.; Nguyen, S.; McLaughlin, P.; Liniger, E.; Hu, C.-K.; Clevenger, L.; et al. Reliable airgap BEOL technology in advanced 48 nm pitch copper/ULK interconnects for substantial power and performance benefits. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017. [Google Scholar] [CrossRef]

- Lo, C.-L.; Helfrecht, B.A.; He, Y.; Guzman, D.M.; Onofrio, N.; Zhang, S.; Weinstein, D.; Strachan, A.; Chen, Z. Opportunities and challenges of 2D materials in back-end-of-line interconnect scaling. J. Appl. Phys. 2020, 128, 080903. [Google Scholar] [CrossRef]

- Chang, S.Y.; Wan, C.C.; Wang, Y.Y. Selectivity enhancement of electroless Co deposition for Cu capping process via spontaneous diazonium ion reduction. Electrochem. Solid-State Lett. 2007, 10, D43. [Google Scholar] [CrossRef]

- Shimada, M.; Moriyama, M.; Ito, K.; Tsukimoto, S.; Murakami, M. Electrical resistivity of polycrystalline Cu interconnects with nano-scale linewidth. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. Process. Meas. Phenom. 2006, 24, 190–194. [Google Scholar] [CrossRef]

- Steinhögl, W.; Schindler, G.; Steinlesberger, G.; Engelhardt, M. Size-dependent resistivity of metallic wires in the mesoscopic range. Phys. Rev. B 2002, 66, 075414. [Google Scholar] [CrossRef]

- Witt, C.; Yeap, K.; Lesniewska, A.; Wan, D.; Jordan, N.; Ciofi, I.; Wu, C.; Tokei, Z. Testing the limits of TaN barrier scaling. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018. [Google Scholar] [CrossRef]

- Motoyama, K.; van der Straten, O.; Maniscalco, J.; Huang, H.; Kim, Y.; Choi, J.; Lee, J.; Hu, C.-K.; McLaughlin, P.; Standaert, T.; et al. Ru liner scaling with ALD TaN barrier process for low resistance 7 nm Cu interconnects and beyond. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018. [Google Scholar] [CrossRef]

- Wu, Z.; Li, R.; Xie, X.; Suen, W.; Tseng, J.; Bekiaris, N.; Vinnakota, R.; Kashefizadeh, K.; Naik, M. PVD-treated ALD TaN for Cu interconnect extension to 5 nm node and beyond. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018. [Google Scholar] [CrossRef]

- Bhosale, P.S.; Maniscalco, J.; Lanzillo, N.; Nogami, T.; Canaperi, D.; Motoyama, K.; Huang, H.; McLaughlin, P.; Shaviv, R.; Stolfi, M.; et al. Modified ALD TaN barrier with Ru liner and dynamic Cu reflow for 36nm pitch interconnect integration. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018. [Google Scholar] [CrossRef]

- Yang, C.-C.; Spooner, T.; Ponoth, S.; Chanda, K.; Simon, A.; Lavoie, C.; Lane, M.; Hu, C.-K.; Liniger, E.; Gignac, L.; et al. Physical, electrical, and reliability characterization of Ru for Cu interconnects. In Proceedings of the 2006 International Interconnect Technology Conference, Burlingame, CA, USA, 5–7 June 2006. [Google Scholar] [CrossRef]

- Abe, M.; Ueki, M.; Tada, M.; Onodera, T.; Furutake, N.; Shimura, K.; Saito, S.; Hayashi, Y. Highly-oriented PVD ruthenium liner for low-resistance direct-plated Cu interconnects. In Proceedings of the 2007 IEEE International Interconnect Technology Conference, Burlingame, CA, USA, 4–6 June 2007. [Google Scholar] [CrossRef]

- Mori, K.; Ohmori, K.; Torazawa, N.; Hirao, S.; Kaneyama, S.; Korogi, H.; Maekawa, K.; Fukui, S.; Tomita, K.; Inoue, M.; et al. Effects of Ru-Ta alloy barrier on Cu filling and reliability for Cu interconnects. In Proceedings of the 2008 International Interconnect Technology Conference, Burlingame, CA, USA, 1–4 June 2008. [Google Scholar] [CrossRef]

- Huang, H.Y.; Hsieh, C.H.; Jeng, S.M.; Tao, H.J.; Cao, M.; Mii, Y.J. A new enhancement layer to improve copper interconnect performance. In Proceedings of the 2010 IEEE International Interconnect Technology Conference, Burlingame, CA, USA, 6–9 June 2010. [Google Scholar] [CrossRef]

- Rullan, J.; Ishizaka, T.; Cerio, F.; Mizuno, S.; Mizusawa, Y.; Ponnuswamy, T.; Reid, J.; McKerrow, A.; Yang, C.-C. Low resistance wiring and 2Xnm void free fill with CVD Ruthenium liner and DirectSeed TM copper. In Proceedings of the 2010 IEEE International Interconnect Technology Conference, Burlingame, CA, USA, 6–9 June 2010. [Google Scholar] [CrossRef]

- Yang, C.-C.; Cohen, S.; Shaw, T.; Wang, P.-C.; Nogami, T.; Edelstein, D. Characterization of “Ultrathin-Cu”/Ru (Ta)/TaN liner stack for copper interconnects. IEEE Electron Device Lett. 2010, 31, 722–724. [Google Scholar] [CrossRef]

- Swerts, J.; Armini, S.; Carbonell, L.; Delabie, A.; Franquet, A.; Mertens, S.; Popovici, M.; Schaekers, M.; Witters, T.; Tökei, Z.; et al. Scalability of plasma enhanced atomic layer deposited ruthenium films for interconnect applications. J. Vac. Sci. Technol. A Vac. Surf. Film. 2012, 30, 01A103. [Google Scholar] [CrossRef]

- He, M.; Zhang, X.; Nogami, T.; Lin, X.; Kelly, J.; Kim, H.; Spooner, T.; Edelstein, D.; Zhao, L. Mechanism of Co liner as enhancement layer for Cu interconnect gap-fill. J. Electrochem. Soc. 2013, 160, D3040. [Google Scholar] [CrossRef]

- Wu, Z.; Chen, F.; Shen, G.; Hu, Y.; Pethe, S.; Lee, J.J.; Tseng, J.; Suen, W.; Vinnakota, R.; Kashefizadeh, K.; et al. Pathfinding of Ru-Liner/Cu-Reflow Interconnect Reliability Solution. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018. [Google Scholar] [CrossRef]

- Motoyama, K.; van der Straten, O.; Maniscalco, J.; Cheng, K.; DeVries, S.; Huang, H.; Shen, T.; Lanzillo, N.; Hosadurga, S.; Park, K.; et al. Co-doped Ru liners for highly reliable Cu interconnects with selective Co cap. In Proceedings of the 2020 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 5–8 October 2020. [Google Scholar] [CrossRef]

- Motoyama, K. EM performance improvements for Cu interconnects with Ru-based liner and Co cap in advanced nodes. In Proceedings of the 2021 IEEE International Interconnect Technology Conference (IITC), Kyoto, Japan, 6–9 July 2021. [Google Scholar] [CrossRef]

- Alers, G.; Rozbicki, R.T.; Harm, G.J.; Kailasam, S.; Ray, G.W.; Danek, M. Barrier-first integration for improved reliability in copper dual damascene interconnects. In Proceedings of the IEEE 2003 International Interconnect Technology Conference (Cat. No. 03TH8695), Burlingame, CA, USA, 4 June 2003. [Google Scholar] [CrossRef]

- You, S.; Ren, H.; Naik, M.; Chen, L.; Chen, F.; Cervantes, C.L.; Xie, X.; Kashefizadeh, K. Selective Barrier for Cu Interconnect Extension in 3nm Node and Beyond. In Proceedings of the 2021 IEEE International Interconnect Technology Conference (IITC), Kyoto, Japan, 6–9 July 2021. [Google Scholar] [CrossRef]

- Kawasaki, H.; Iwashita, M.; Warashina, H.; Nagai, H.; Iwai, K.; Komatsu, H.; Ozaki, Y.; Pattanaik, G. Advanced Damascene integration using selective deposition of barrier metal with Self Assemble Monolayer. In Proceedings of the 2021 IEEE International Interconnect Technology Conference (IITC), Kyoto, Japan, 6–9 July 2021. [Google Scholar] [CrossRef]

- Nogami, T.; Briggs, B.D.; Korkmaz, S.; Chae, M.; Penny, C.; Li, J.; Wang, W.; McLaughlin, P.S.; Kane, T.; Parks, C.; et al. Through-Cobalt Self Forming Barrier (tCoSFB) for Cu/ULK BEOL: A novel concept for advanced technology nodes. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015. [Google Scholar] [CrossRef]

- Koike, J.; Haneda, M.; Iijima, J.; Wada, M. Cu alloy metallization for self-forming barrier process. In Proceedings of the 2006 International Interconnect Technology Conference, Burlingame, CA, USA, 5–7 June 2006. [Google Scholar] [CrossRef]

- Siew, Y.K.; Jourdan, N.; Ciofi, I.; Croes, K.; Wilson, C.J.; Tang, B.J.; Demuynck, S.; Wu, Z.; Ai, H.; Cellier, D.; et al. Cu wire resistance improvement using mn-based self-formed barriers. In Proceedings of the IEEE International Interconnect Technology Conference, San Jose, CA, USA, 20–23 May 2014. [Google Scholar] [CrossRef]

- Nogami, T.; Zhang, X.; Kelly, J.; Briggs, B.; You, H.; Patlolla, R.; Huang, H.; McLaughlin, P.; Lee, J.; Shobha, H.; et al. Comparison of key fine-line BEOL metallization schemes for beyond 7 nm node. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017. [Google Scholar] [CrossRef]

- Usui, T.; Nasu, H.; Koike, J.; Wada, M.; Takahashi, S.; Shimizu, N.; Nishikawa, T.; Yoshimaru, A.; Shibata, H. Low resistive and highly reliable Cu dual-damascene interconnect technology using self-formed MnSi/sub x/O/sub y/barrier layer. In Proceedings of the IEEE 2005 International Interconnect Technology Conference, Burlingame, CA, USA, 6–8 June 2005. [Google Scholar] [CrossRef]

- Usui, T.; Tsumura, K.; Nasu, H.; Hayashi, Y.; Minamihaba, G.; Toyoda, H.; Sawada, H.; Ito, S.; Miyajima, H.; Watanabe, K.; et al. High performance ultra low-k (k = 2.0/keff = 2.4)/Cu dual-damascene interconnect technology with self-formed MnSixOy barrier layer for 32 nm-node. In Proceedings of the 2006 International Interconnect Technology Conference, Burlingame, CA, USA, 5–7 June 2006. [Google Scholar] [CrossRef]

- Nogami, T.; Chae, M.; Penny, C.; Shaw, T.; Shobha, H.; Li, J.; Cohen, S.; Hu, C.-K.; Zhang, X.; He, M.; et al. Performance of ultrathin alternative diffusion barrier metals for next-Generation BEOL technologies, and their effects on reliability. In Proceedings of the IEEE International Interconnect Technology Conference., San Jose, CA, USA, 20–23 May 2014. [Google Scholar] [CrossRef]

- Nogami, T.; Huang, H.; Shobha, H.; Patlolla, R.; Kelly, J.; Penny, C.; Hu, C.-K.; Sil, D.; Devries, S.; Lee, J.; et al. Technology challenges and enablers to extend Cu metallization to beyond 7 nm node. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019. [Google Scholar] [CrossRef]

- van der Veen, M.H.; Soethoudt, J.; Delabie, A.; Pedreira, O.V.; Gonzalez, V.V.; Lariviere, S.; Teugels, L.; Jourdan, N.; Decoster, S.; Struyf, H.; et al. Hybrid Metallization with Cu in sub 30nm Interconnects. In Proceedings of the 2020 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 5–8 October 2020. [Google Scholar] [CrossRef]

- van der Veen, M.H.; Vandersmissen, K.; Dictus, D.; Demuynck, S.; Liu, R.; Bin, X.; Nalla, P.; Lesniewska, A.; Hall, L.; Croes, K.; et al. Cobalt bottom-up contact and via prefill enabling advanced logic and DRAM technologies. In Proceedings of the 2015 IEEE International Interconnect Technology Conference and 2015 IEEE Materials for Advanced Metallization Conference (IITC/MAM), Grenoble, France, 18–21 May 2015. [Google Scholar] [CrossRef]

- Zheng, J.-F.; Chen, P.; Baum, T.H.; Lieten, R.R.; Hunks, W.; Lippy, S.; Frye, A.; Li, W.; O'Neill, J.; Xu, J.; et al. Selective Co growth on Cu for void-free via fill. In Proceedings of the 2015 IEEE International Interconnect Technology Conference and 2015 IEEE Materials for Advanced Metallization Conference (IITC/MAM), Grenoble, France, 18–21 May 2015. [Google Scholar] [CrossRef]

- Steinhögl, W.; Schindler, G.; Steinlesberger, G.; Traving, M.; Engelhardt, M. Comprehensive study of the resistivity of copper wires with lateral dimensions of 100 nm and smaller. J. Appl. Phys. 2005, 97, 023706. [Google Scholar] [CrossRef]

- Lanzillo, N.A.; Yang, C.-C.; Motoyama, K.; Huang, H.; Cheng, K.; Maniscalco, J.; Van Der Straten, O.; Penny, C.; Standaert, T.; Choi, K. Exploring the limits of cobalt liner thickness in advanced copper interconnects. IEEE Electron Device Lett. 2019, 40, 1804–1807. [Google Scholar] [CrossRef]

- Hu, C.-K.; Kelly, J.; Chen, J.H.-C.; Huang, H.; Ostrovski, Y.; Patlolla, R.; Peethala, B.; Adusumilli, P.; Spooner, T.; Gignac, L.M.; et al. Electromigration and resistivity in on-chip Cu, Co and Ru damascene nanowires. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017; pp. 1–3. [Google Scholar] [CrossRef]

- Bekiaris, N.; Wu, Z.; Ren, H.; Naik, M.; Park, J.H.; Lee, M.; Ha, T.H.; Hou, W.; Bakke, J.R.; Gage, M.; et al. Cobalt fill for advanced interconnects. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017. [Google Scholar] [CrossRef]

- Tierno, D.; Hosseini, M.; van der Veen, M.; Dangol, A.; Croes, K.; Demuynck, S.; Tokei, Z.; Litta, E.; Horiguchi, N. Reliability of Barrierless PVD Mo. In Proceedings of the 2021 IEEE International Interconnect Technology Conference (IITC), Kyoto, Japan, 6–9 July 2021. [Google Scholar] [CrossRef]

- Choi, D.; Barmak, K. On the potential of tungsten as next-generation semiconductor interconnects. Electron. Mater. Lett. 2017, 13, 449–456. [Google Scholar] [CrossRef]

- Wen, L.G.; Roussel, P.; Pedreira, O.V.; Briggs, B.; Groven, B.; Dutta, S.; Popovici, M.I.; Heylen, N.; Ciofi, I.; Vanstreels, K.; et al. Atomic layer deposition of ruthenium with TiN interface for sub-10 nm advanced interconnects beyond copper. ACS Appl. Mater. Interfaces 2016, 8, 26119–26125. [Google Scholar] [CrossRef] [PubMed]

- Zhang, X.; Huang, H.; Patlolla, R.; Wang, W.; Mont, F.W.; Li, J.; Hu, C.-K.; Liniger, E.G.; McLaughlin, P.S.; Labelle, C.; et al. Ruthenium interconnect resistivity and reliability at 48 nm pitch. In Proceedings of the 2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC). San Jose, CA, USA, 23–26 May 2016. [Google Scholar] [CrossRef]

- Nogami, T.; Patlolla, R.; Kelly, J.; Briggs, B.; Huang, H.; Demarest, J.; Li, J.; Hengstebeck, R.; Zhang, X.; Lian, G.; et al. Cobalt/copper composite interconnects for line resistance reduction in both fine and wide lines. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017. [Google Scholar] [CrossRef]

- Dutta, S.; Kundu, S.; Gupta, A.; Jamieson, G.; Granados, J.F.G.; Bommels, J.; Wilson, C.J.; Tokei, Z.; Adelmann, C. Highly scaled ruthenium interconnects. IEEE Electron Device Lett. 2017, 38, 949–951. [Google Scholar] [CrossRef]

- van der Veen, M.H.; Heyler, N.; Pedreira, O.V.; Ciofi, I.; Decoster, S.; Gonzalez, V.V.; Jourdan, N.; Struyf, H.; Croes, K.; Wilson, C.J.; et al. Damascene benchmark of Ru, Co and Cu in scaled dimensions. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018. [Google Scholar] [CrossRef]

- Wan, D.; Paolillo, S.; Rassoul, N.; Kotowska, B.K.; Blanco, V.; Adelmann, C.; Lazzarino, F.; Ercken, M.; Murdoch, G.; Bommels, J.; et al. Subtractive etch of ruthenium for sub-5nm interconnect. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018. [Google Scholar] [CrossRef]

- Murdoch, G.; Tokei, Z.; Paolillo, S.; Pedreira, O.V.; Vanstreels, K.; Wilson, C.J. Semidamascene Interconnects for 2nm node and Beyond. In Proceedings of the 2020 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 5–8 October 2020. [Google Scholar] [CrossRef]

- Lesniewska, A.; Roussel, P.; Tierno, D.; Gonzalez, V.V.; van der Veen, M.H.; Verdonck, P.; Jourdan, N.; Wilson, C.; Tokei, Z.; Croes, K. Dielectric reliability study of 21 nm pitch interconnects with barrierless Ru fill. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020. [Google Scholar] [CrossRef]

- Son, M.; Jang, J.; Lee, Y.; Nam, J.; Hwang, J.Y.; Kim, I.S.; Lee, B.H.; Ham, M.-H.; Chee, S.-S. Copper-graphene heterostructure for back-end-of-line compatible high-performance interconnects. NPJ 2D Mater. Appl. 2021, 5, 41. [Google Scholar] [CrossRef]

- Nogami, T.; Nguyen, S.; Huang, H.; Lanzillo, N.; Shobha, H.; Li, J.; Peethela, B.; Parbatani, A.; van Schravendijk, B.; Varadarajan, B.; et al. Electromigration and line R of graphene capped Cu dual Damascene interconnect. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021. [Google Scholar] [CrossRef]

- Lo, C.-L.; Zhang, K.; Smith, R.S.; Shah, K.; Robinson, J.A.; Chen, Z. Large-area, single-layer molybdenum disulfide synthesized at BEOL compatible temperature as Cu diffusion barrier. IEEE Electron Device Lett. 2018, 39, 873–876. [Google Scholar] [CrossRef]

- Yu, J.; Li, J.; Zhao, Y.; Lambertz, A.; Chen, T.; Duan, W.; Liu, W.; Yang, X.; Huang, Y.; Ding, K. Copper metallization of electrodes for silicon heterojunction solar cells: Process, reliability and challenges. Sol. Energy Mater. Sol. Cells 2021, 224, 110993. [Google Scholar] [CrossRef]

- Yang, L.; Zhong, S.; Zhang, W.; Li, X.; Li, Z.; Zhuang, Y.; Wang, X.; Zhao, L.; Cao, X.; Deng, X.; et al. Study and development of rear-emitter Si heterojunction solar cells and application of direct copper metallization. Prog. Photovolt. Res. Appl. 2018, 26, 385–396. [Google Scholar] [CrossRef]

- Blech, I.A.; Herring, C. Stress generation by electromigration. Appl. Phys. Lett. 1976, 29, 131–133. [Google Scholar] [CrossRef]

- Christiansen, C.; Li, B.; Gill, J. Blech effect and lifetime projection for cu/low-k interconnects. In Proceedings of the 2008 International Interconnect Technology Conference, Burlingame, CA, USA, 1–4 June 2008. [Google Scholar] [CrossRef]

- Cheng, Y.-L.; Lee, S.Y.; Chiu, C.; Wu, K. Back stress model on electromigration lifetime prediction in short length copper interconnects. In Proceedings of the 2008 IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 27 April–1 May 2008. [Google Scholar] [CrossRef]

- Zhao, W.-S.; Zhang, R.; Wang, D.-W. Recent Progress in Physics-Based Modeling of Electromigration in Integrated Circuit Interconnects. Micromachines 2022, 13, 883. [Google Scholar] [CrossRef]

- Lloyd, J.R. Black’s law revisited-Nucleation and growth in electromigration failure. Microelectron. Reliab. 2007, 47, 1468–1472. [Google Scholar] [CrossRef]

- Hu, C.-K.; Gignac, L.; Rosenberg, R.; Liniger, E.; Rubino, J.; Sambucetti, C.; Stamper, A.; Domenicucci, A.; Chen, X. Reduced Cu interface diffusion by CoWP surface coating. Microelectron. Eng. 2003, 70, 406–411. [Google Scholar] [CrossRef]

- Hu, C.-K.; Gignac, L.; Lian, G.; Cabral, C.; Motoyama, K.; Shobha, H.; Demarest, J.; Ostrovski, Y.; Breslin, C.M.; Ali, M.; et al. Mechanisms of electromigration damage in Cu interconnects. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018. [Google Scholar] [CrossRef]

- Kimura, M. Oxide breakdown mechanism and quantum physical chemistry for time-dependent dielectric breakdown. In Proceedings of the 1997 IEEE International Reliability Physics Symposium Proceedings. 35th Annual, Denver, CO, USA, 8–10 April 1997. [Google Scholar] [CrossRef]

- Ogawa, E.; Kim, J.; Haase, G.; Mogul, H.; McPherson, J. Leakage, breakdown, and TDDB characteristics of porous low-k silica-based interconnect dielectrics. In Proceedings of the 2003 IEEE International Reliability Physics Symposium Proceedings, 2003. 41st Annual, Dallas, TX, USA, 30 March–4 April 2003. [Google Scholar] [CrossRef]

- Oshida, D.; Takewaki, T.; Iguchi, M.; Taiji, T.; Morita, T.; Tsuchiya, Y.; Tsuchiya, H.; Yokogawa, S.; Kunishima, H.; Aizawa, H.; et al. Quantitative analysis of correlation between insulator surface copper contamination and TDDB lifetime based on actual measurement. In Proceedings of the 2008 International Interconnect Technology Conference, Burlingame, CA, USA, 1–4 June 2008. [Google Scholar] [CrossRef]

- Noguchi, J. Dominant factors in TDDB degradation of Cu interconnects. IEEE Trans. Electron Devices 2005, 52, 1743–1750. [Google Scholar] [CrossRef]

| Properties | SiO2 | FSG | Dense Low-k (Osg) | Porous Low-k |

|---|---|---|---|---|

| density (g/cm3) | 2.2 | 2.2 | 1.8~1.2 | 1.0~1.2 |

| dielectric constant (k) | 4 | 3.5~3.8 | 2.8~3.2 | 1.9~2.7 |

| modulus (gpa) | 55~70 | ~50 | 10~20 | 3~10 |

| hardness (gpa) | 3.5 | 3.36 | 1.2~2.5 | 0.3~1.0 |

| cte (ppm/k) | 0.6 | ~0.6 | 1~5 | 10~18 |

| thermal conductivity (w/mk) | 1.0 | 1.0 | ~0.8 | 0.26 |

| porosity (%) | NA | NA | <10 | 25~50 |

| average pore size (nm) | NA | NA | <1.0 | 2.0~10 |

| breakdown field (mv/cm) | >10 | >10 | 8~10 | <8 |

| Metal | Activation Energy for Different Diffusion Paths (Ev) | |||

|---|---|---|---|---|

| Bulk | Grain Boundary | Surface | Interface | |

| Al | 1.4 | 0.4~0.5 | NA | − |

| Al/Cu (Alloy) | 1.2 | 0.6~0.7 | NA | 0.9~1.1 |

| Cu | 2.1 | 1.1~1.2 | 0.6~0.7 | 0.8~1.3 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, H.-W. Recent Trends in Copper Metallization. Electronics 2022, 11, 2914. https://doi.org/10.3390/electronics11182914

Kim H-W. Recent Trends in Copper Metallization. Electronics. 2022; 11(18):2914. https://doi.org/10.3390/electronics11182914

Chicago/Turabian StyleKim, Hyung-Woo. 2022. "Recent Trends in Copper Metallization" Electronics 11, no. 18: 2914. https://doi.org/10.3390/electronics11182914

APA StyleKim, H.-W. (2022). Recent Trends in Copper Metallization. Electronics, 11(18), 2914. https://doi.org/10.3390/electronics11182914