A 16-Bit 120 MS/s Pipelined ADC Using a Multi-Level Dither Technique

Abstract

1. Introduction

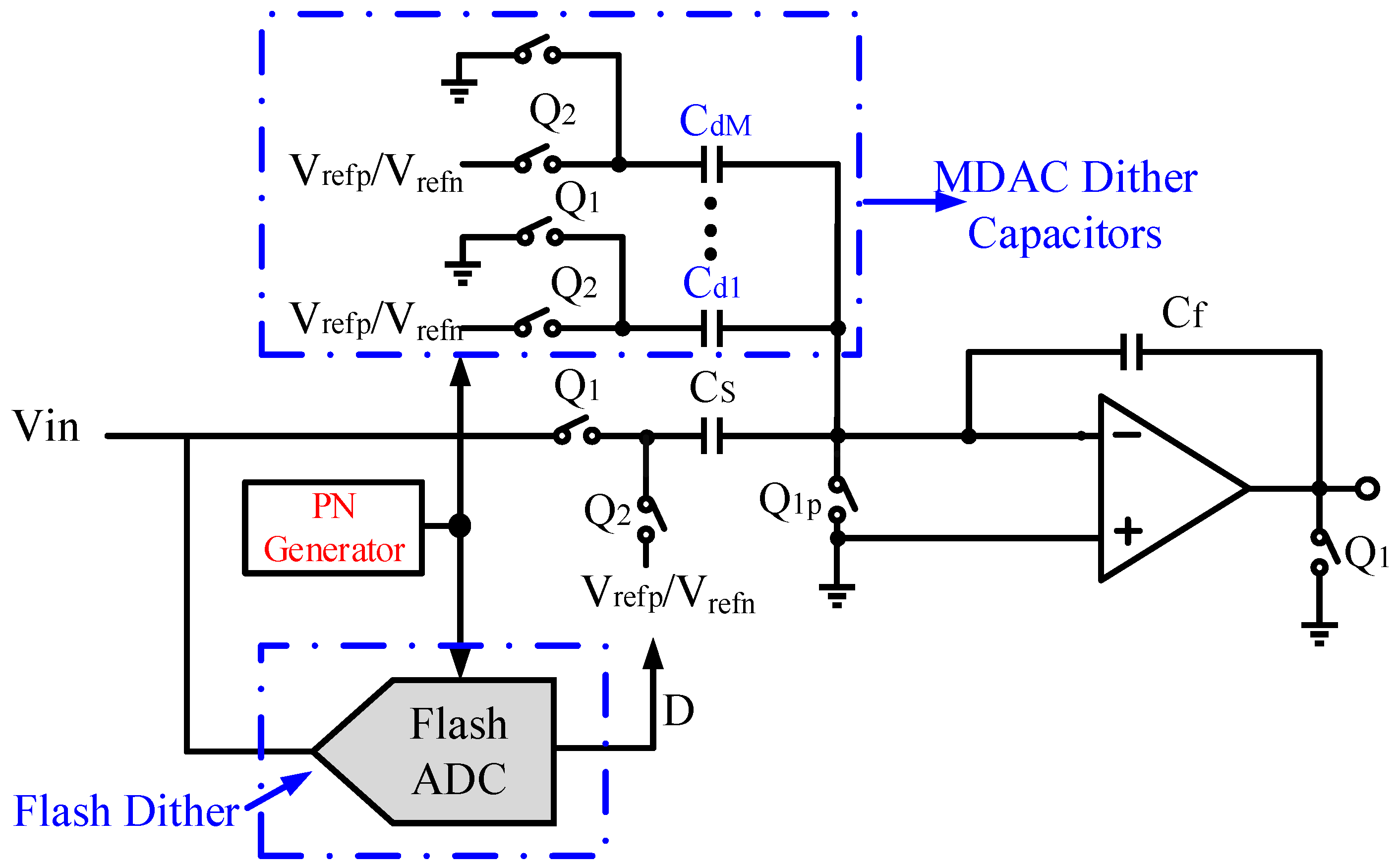

2. Architecture of the Proposed Dither Injection Scheme

3. Dither Injection Scheme and Its Circuit Implementation

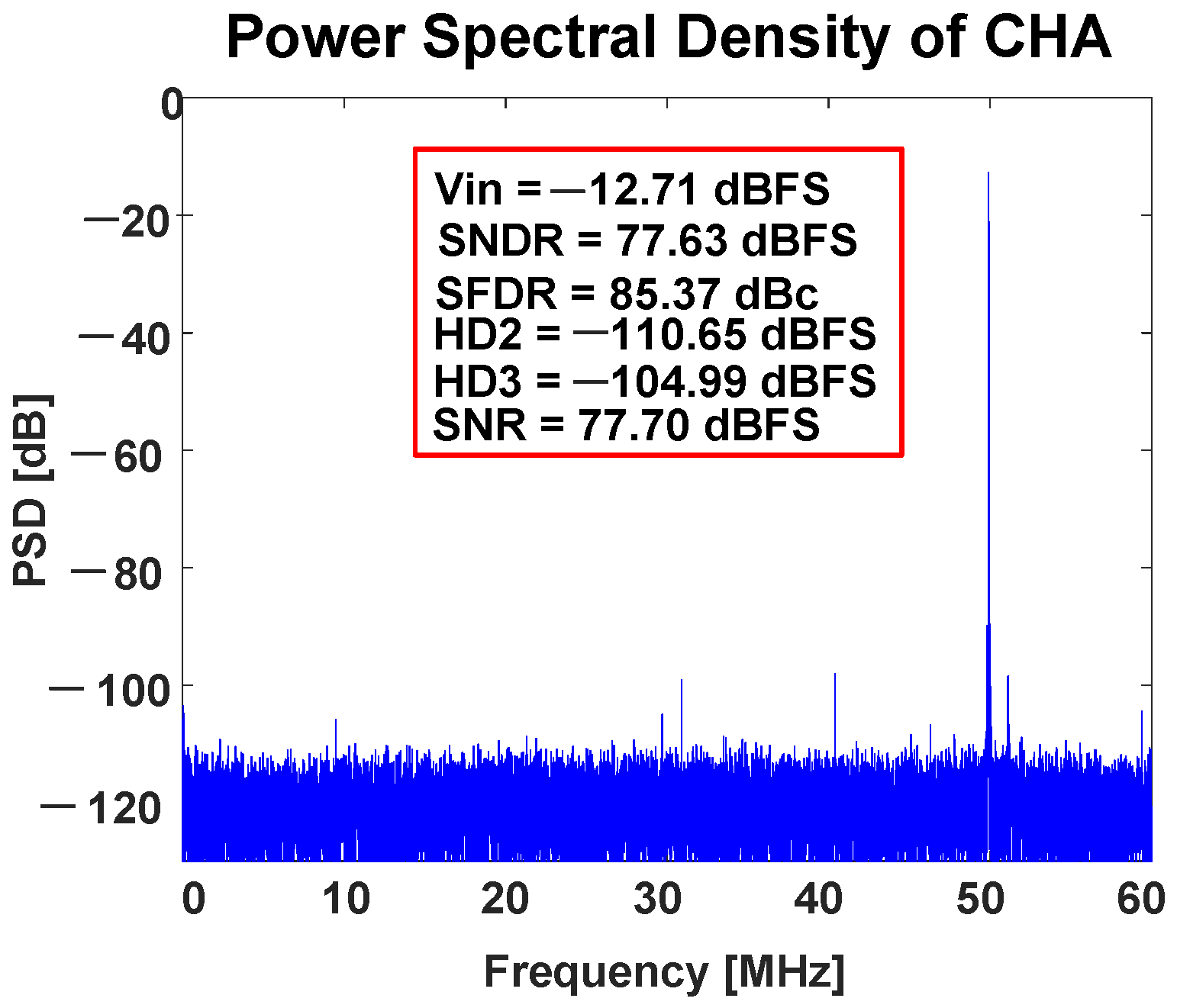

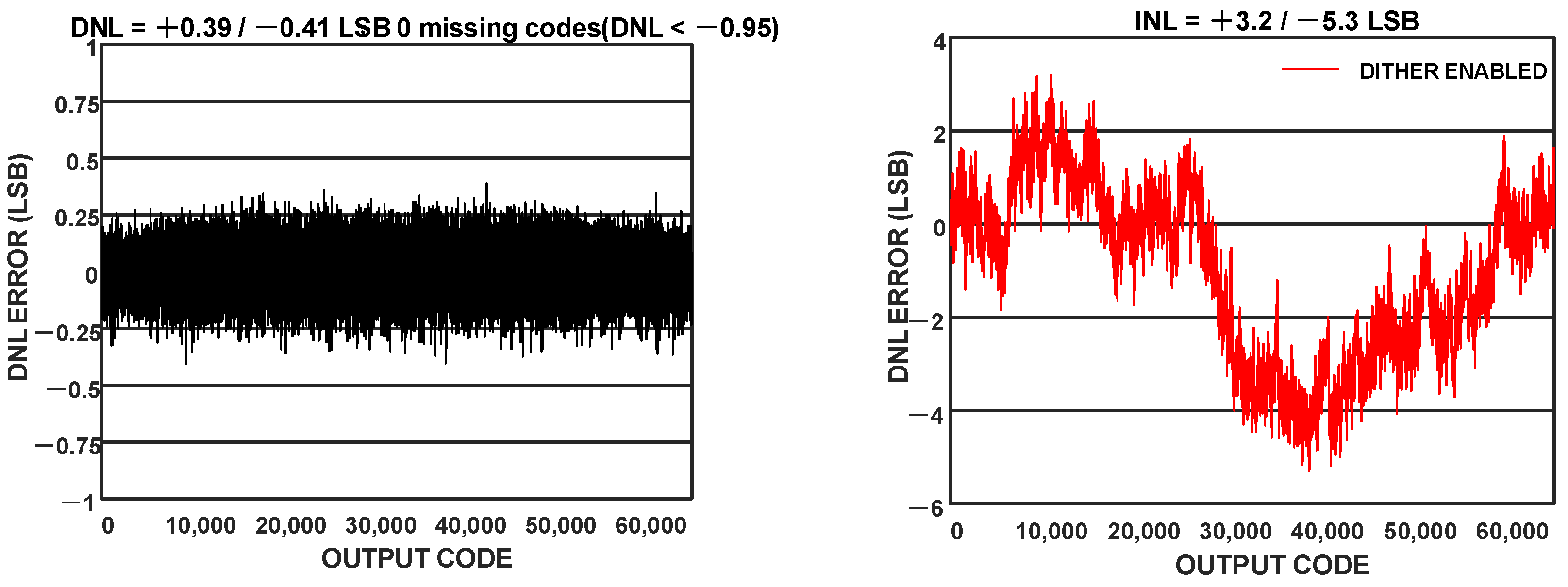

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Zheng, X.; Wang, Z.; Li, F.; Zhao, F.; Yue, S.; Zhang, C.; Wang, Z. A 14-bit 250 MS/s IF Sampling Pipelined ADC in 180 nm CMOS Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1381–1392. [Google Scholar] [CrossRef]

- Murmann, B.; Boser, B.E. A 12-bit 75-MS/s Pipelined ADC Using Open-Loop Residue Amplification. IEEE J. Solid-State Circuit 2003, 38, 2040–2050. [Google Scholar] [CrossRef]

- Liu, H.-C.; Lee, Z.-M.; Wu, J.-T. A 15-b 40-MS/s CMOS Pipelined Analog-to-Digital Converter with Digital Background Calibration. IEEE J. Solid-State Circuit 2005, 40, 1047–1056. [Google Scholar] [CrossRef]

- Fang, B.-N.; Wu, J.-T. A 10-Bit 300-MS/s Pipelined ADC with Digital Calibration and Digital Bias Generation. IEEE J. Solid-State Circuit 2013, 48, 670–683. [Google Scholar] [CrossRef]

- Wu, J.; Chen, C.-Y.; Li, T.; He, L.; Liu, W.; Shih, W.-T.; Tsai, S.S.; Chen, B.; Huang, C.-S.; Hung, B.J.-J.; et al. A 240-mW 2.1-GS/s 52-dB SNDR Pipeline ADC Using MDAC Equalization. IEEE J. Solid-State Circuit 2013, 48, 1818–1828. [Google Scholar]

- Brandolini, M.; Shin, Y.J.; Raviprakash, K.; Wang, T.; Wu, R.; Geddada, H.M.; Ko, Y.J.; Ding, Y.; Huang, C.S.; Shih, W.T.; et al. A 5 GS/s 150 mW 10 b SHA-Less Pipelined/SAR Hybrid ADC for Direct-Sampling Systems in 28 nm CMOS. IEEE J. Solid-State Circuit 2015, 50, 2922–2934. [Google Scholar] [CrossRef]

- Bogner, P.; Kuttner, F.; Kropf, C.; Hartig, T.; Burian, M.; Eul, H. A 14b 100 MS/s Digitally Self-Calibrated Pipelined ADC in 0.13 µm CMOS. IEEE J. Solid-State Circuit 2017, 53, 850–860. [Google Scholar]

- Ali, A.M.A.; Morgan, A.; Dillon, C.; Patterson, G.; Puckett, S.; Bhoraskar, P.; Dinc, H.; Hensley, M.; Stop, R.; Bardsley, S.; et al. A 16-bit 250-MS/s IF Sampling Pipelined ADC with Background Calibration. IEEE J. Solid-State Circuit 2010, 45, 2602–2612. [Google Scholar] [CrossRef]

- Ali, A.M.A.; Dinc, H.; Bhoraskar, P.; Dillon, C.; Puckett, S.; Gray, B.; Speir, C.; Lanford, J.; Brunsilius, J.; Derounian, P.R.; et al. A 14 Bit 1 GS/s RF Sampling Pipelined ADC with Background Calibration. IEEE J. Solid-State Circuit 2014, 49, 2857–2867. [Google Scholar] [CrossRef]

- Miyahara, Y.; Sano, M.; Koyama, K.; Suzuki, T.; Hamashita, K.; Song, B.-S. A 14b 60 MS/s Pipelined ADC Adaptively Cancelling Opamp Gain and Nonlinearity. IEEE J. Solid-State Circuit 2014, 49, 416–425. [Google Scholar] [CrossRef]

- Ali, A.M.A.; Dinc, H.; Bhoraskar, P.; Puckett, S.; Morgan, A.; Zhu, N.; Yu, Q.; Dillon, C.; Gray, B.; Lanford, J.; et al. A 14-bit 2.5 GS/s and 5 GS/s RF Sampling ADC with Background Calibration and Dither. In Proceedings of the 2016 Symposium on VLSI Circuits Digest of Technical Papers, Greensboro, NC, USA, 12–17 June 2016. [Google Scholar]

- Devarajan, S.; Singer, L.; Kelly, D.; Pan, T.; Silva, J.; Brunsilius, J.; Rey-Losada, D.; Murden, F.; Speir, C.; Bray, J.; et al. A 12-b 10-GS/s Interleaved Pipeline ADC in 28-nm CMOS Technology. IEEE J. Solid-State Circuit 2017, 52, 3204–3218. [Google Scholar] [CrossRef]

- Liu, H.; Sun, J.; Xu, H.; Zhang, L. A 16b 120MS/s Pipelined ADC Using an Auxiliary-Capacitor-Based Calibration Technique Achieving 90.5 dB SFDR in 0.18 μm CMOS. IEEE Trans. Circuits Syst.—II Express Briefs 2022, 69, 809–813. [Google Scholar] [CrossRef]

- Shu, Y.-S.; Song, B.-S. A 15-bit Linear 20-MS/s Pipelined ADC Digitally Calibrated with Signal-Dependent Dithering. IEEE J. Solid-State Circuit 2008, 43, 342–350. [Google Scholar] [CrossRef]

- Karanicolas, A.N.; Lee, H.-S.; Bacrania, K.L. A 15-b 1-Msample/s Digitally Self-calibrated Pipeline ADC. IEEE J. Solid-State Circuit 1993, 28, 1207–1215. [Google Scholar] [CrossRef]

- Chuang, S.-Y.; Sculley, T.L. A Digitally Self-Calibrating 14-bit 10-MHz CMOS Pipelined A/D Converter. IEEE J. Solid-State Circuit 2002, 37, 674–683. [Google Scholar] [CrossRef]

- Chiu, Y.; Gray, P.R.; Nikolic, B. A 14-b 12-MS/s CMOS Pipeline ADC with Over 100-dB SFDR. IEEE J. Solid-State Circuit 2004, 39, 2139–2151. [Google Scholar] [CrossRef]

- Peng, B.; Li, H.; Lin, P.; Chiu, Y. An Offset Double Conversion Technique for Digital Calibration of Pipelined ADCs. IEEE Trans. Circuits Syst.—II Express Briefs 2010, 57, 961–965. [Google Scholar] [CrossRef]

- Fan, J.-L.; Wang, C.-Y.; Wu, J.-T. A Robust and Fast Digital Background Calibration Technique for Pipelined ADCs. IEEE Trans. Circuits Syst.—I Regul. Pap. 2007, 54, 1213–1223. [Google Scholar] [CrossRef]

- McNeill, J.A.; Goluguri, S.; Nair, A. “Split-ADC” Digital Background Correction of Open-Loop Residue Amplifier Nonlinearity Errors in a 14b Pipeline ADC. In Proceedings of the 2007 IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007. [Google Scholar]

- Ahmed, I.; Johns, D.A. An 11-Bit 45 MS/s Pipelined ADC with Rapid Calibration of DAC Errors in a Multibit Pipeline Stage. IEEE J. Solid-State Circuit 2008, 43, 1626–1637. [Google Scholar] [CrossRef][Green Version]

- Panigada, A.; Galton, I. A 130 mW 100 MS/s Pipelined ADC with 69 dB SNDR Enabled by Digital Harmonic Distortion Correction. IEEE J. Solid-State Circuit 2009, 44, 3314–3328. [Google Scholar] [CrossRef]

- Sun, N. Exploiting Process Variation and Noise in Comparators to Calibrate Interstage Gain Nonlinearity in Pipelined ADCs. IEEE Trans. Circuits Syst.—I Regul. Pap. 2012, 59, 685–695. [Google Scholar] [CrossRef]

- Sarkar, S.; Zhou, Y.; Elies, B.; Chiu, Y. PN-Assisted Deterministic Digital Background Calibration of Multistage Split-Pipelined ADC. IEEE Trans. Circuits Syst.—I Regul. Pap. 2015, 62, 654–661. [Google Scholar] [CrossRef]

- Rakuljic, N.; Galton, I. Suppression of Quantization-Induced Convergence Error in Pipelined ADCs With Harmonic Distortion Correction. IEEE Trans. Circuits Syst.—I Regul. Pap 2013, 60, 593–602. [Google Scholar] [CrossRef]

- Fetterman, H.S.; Martin, D.G.; Rich, D.A. CMOS Pipelined ADC Employing Dither to Improve Linearity. In Proceedings of the IEEE 1999 Custom Integrated Circuits Conference, San Diego, CA, USA, 19 May 1999. [Google Scholar]

- Devarajan, S.; Singer, L.; Kelly, D.; Decker, S.; Kamath, A.; Wilkins, P. A 16-bit, 125 MS/s, 385 mW, 78.7 dB SNR CMOS Pipeline ADC. IEEE J. Solid-State Circuit 2009, 44, 3305–3313. [Google Scholar] [CrossRef]

- Pan, H.; Abidi, A.A. Spectral Spurs due to Quantization in Nyquist ADCs. IEEE Trans. Circuits Syst.—I Regul. Pap. 2004, 51, 1422–1439. [Google Scholar] [CrossRef]

- ElShater, A.; Venkatachala, P.K.; Lee, C.Y.; Muhlestein, J.; Leuenberger, S.; Sobue, K.; Hamashita, K.; Moon, U.K. A 10-mW 16-b 15-MS/s Two-Step SAR ADC with 95-dB DR Using Dual-Deadzone Ring Amplifier. IEEE J. Solid-State Circuit 2019, 54, 3410–3420. [Google Scholar] [CrossRef]

- Hu, G.; Sha, J.; Wang, Z. High-Speed Parallel LFSR Architectures Based on Improved State-Space Transformations. IEEE Trans. VLSI Syst. 2017, 25, 1159–1163. [Google Scholar] [CrossRef]

- Xu, H.; Abidi, A.A. Analysis and Design of Regenerative Comparators for Low Offset and Noise. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 2817–2830. [Google Scholar] [CrossRef]

- Shen, J.; Shikata, A.; Fernando, L.D.; Guthrie, N.; Chen, B.; Maddox, M.; Mascarenhas, N.; Kapusta, R.; Coln, M.C.W. A 16-bit 16-MS/s SAR ADC with On-Chip Calibration in 55-nm CMOS. IEEE J. Solid-State Circuit 2018, 53, 1149–1160. [Google Scholar] [CrossRef]

| Top | CM | Bot | Output |

|---|---|---|---|

| 1 | 1 | 0 | Vcm |

| 1 | 1 | 0 | Vcm |

| 1 | 0 | 1 | Vrefn |

| 0 | 0 | 0 | Vrefp |

| [1] | [27] | [13] | This Work | |

|---|---|---|---|---|

| Process (nm) | 180 | 180 | 180 | 180 |

| Supply (V) | 1.8 | 1.8 | 1.8 | 1.8 |

| Resolution (bits) | 14 | 16 | 16 | 16 |

| Power (mW) | 300 | 385 | 342 | 347 |

| Sampling rate (MHz) | 250 | 125 | 120 | 120 |

| SFDR (near full scale) | 87.9 | 92 | 91 | 90 |

| SNDR (near full scale) | 68.2 | 78.6 | 77 | 77 |

| SFDR (small signal) | N/A | 85 | N/A | 85 |

| SNDR (small signal) | N/A | 78.1 | N/A | 77 |

| FoM (fj/conv-step) | 570 | 462 | 410 | 416 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, J.; Xu, H.; Cao, X.; Liu, T. A 16-Bit 120 MS/s Pipelined ADC Using a Multi-Level Dither Technique. Electronics 2022, 11, 3979. https://doi.org/10.3390/electronics11233979

Wu J, Xu H, Cao X, Liu T. A 16-Bit 120 MS/s Pipelined ADC Using a Multi-Level Dither Technique. Electronics. 2022; 11(23):3979. https://doi.org/10.3390/electronics11233979

Chicago/Turabian StyleWu, Junjie, Honglin Xu, Xu Cao, and Tao Liu. 2022. "A 16-Bit 120 MS/s Pipelined ADC Using a Multi-Level Dither Technique" Electronics 11, no. 23: 3979. https://doi.org/10.3390/electronics11233979

APA StyleWu, J., Xu, H., Cao, X., & Liu, T. (2022). A 16-Bit 120 MS/s Pipelined ADC Using a Multi-Level Dither Technique. Electronics, 11(23), 3979. https://doi.org/10.3390/electronics11233979