A Wideband Reconfigurable CMOS VGA Based on an Asymmetric Capacitor Technique with a Low Phase Variation

Abstract

:1. Introduction

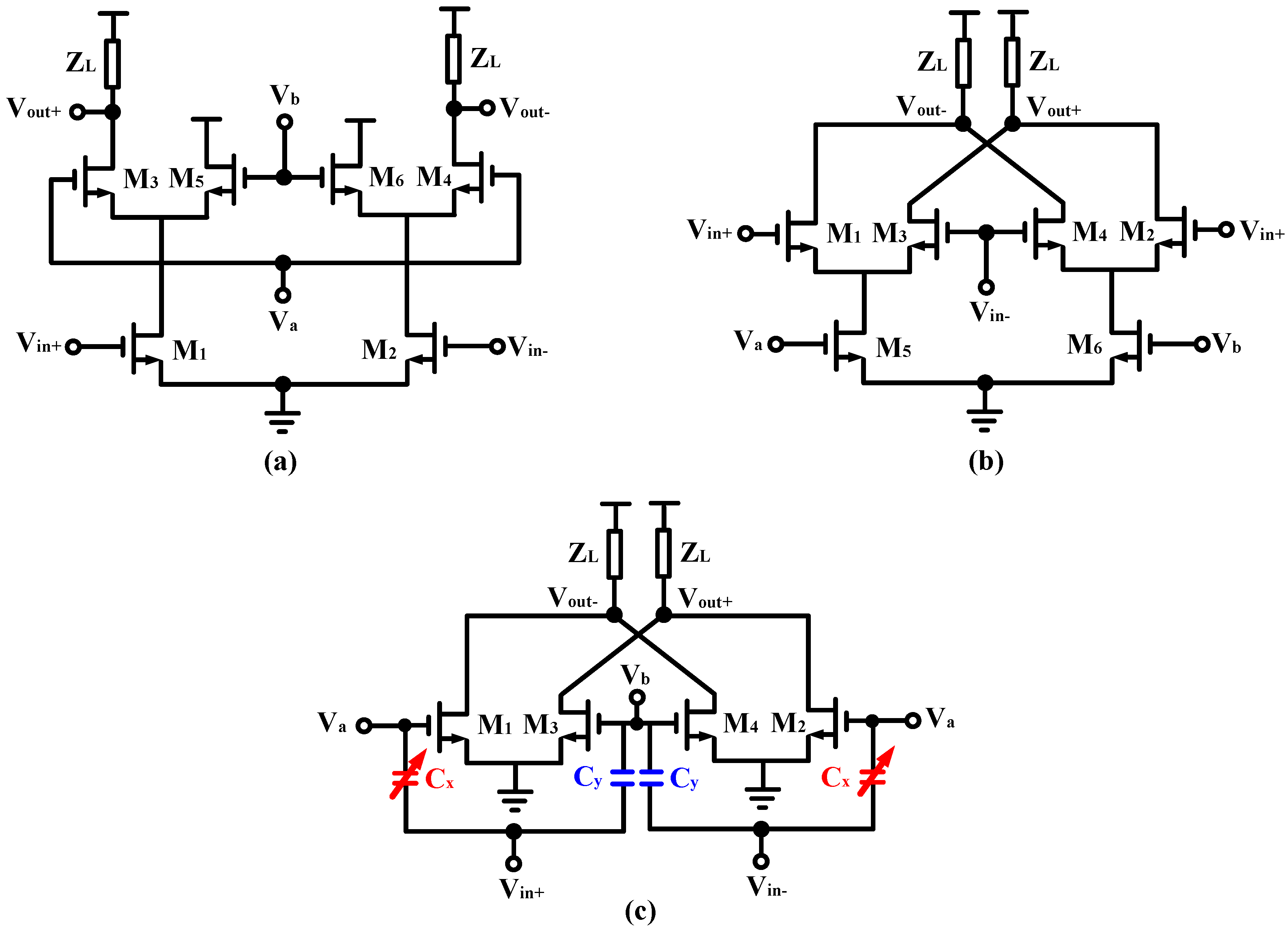

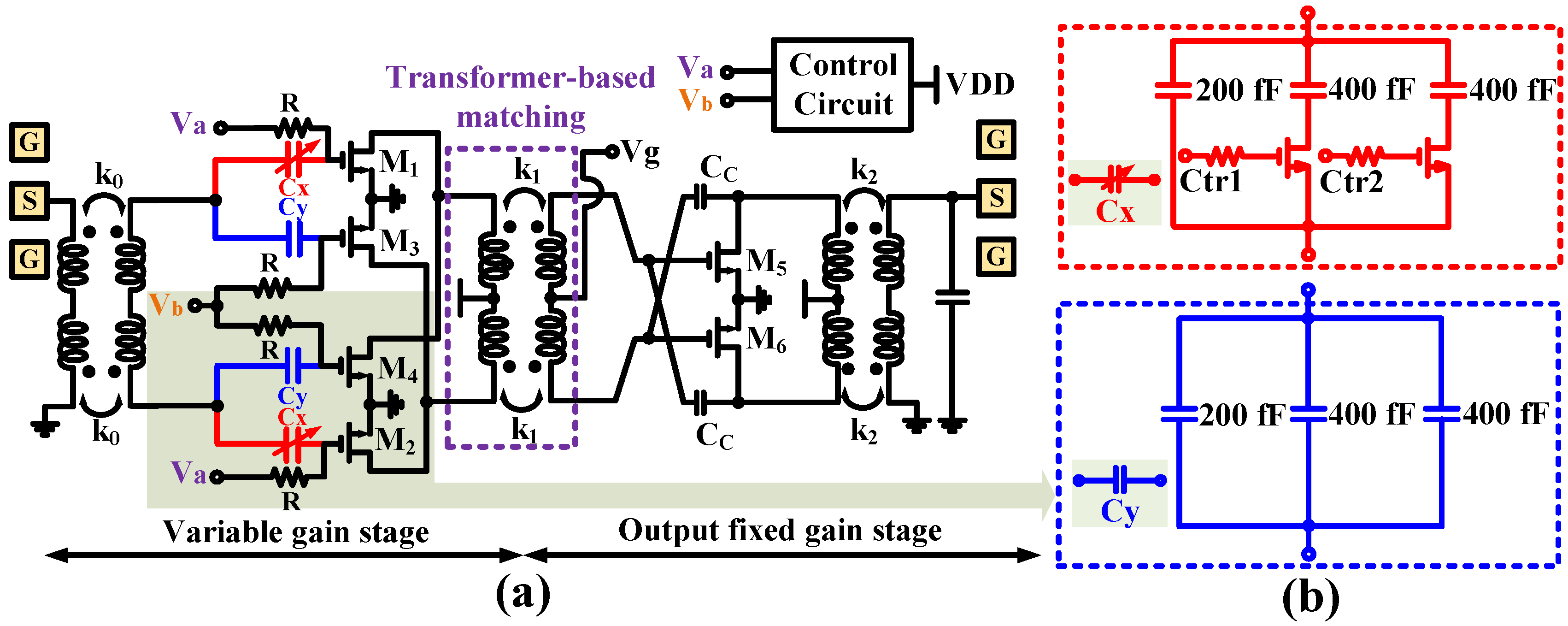

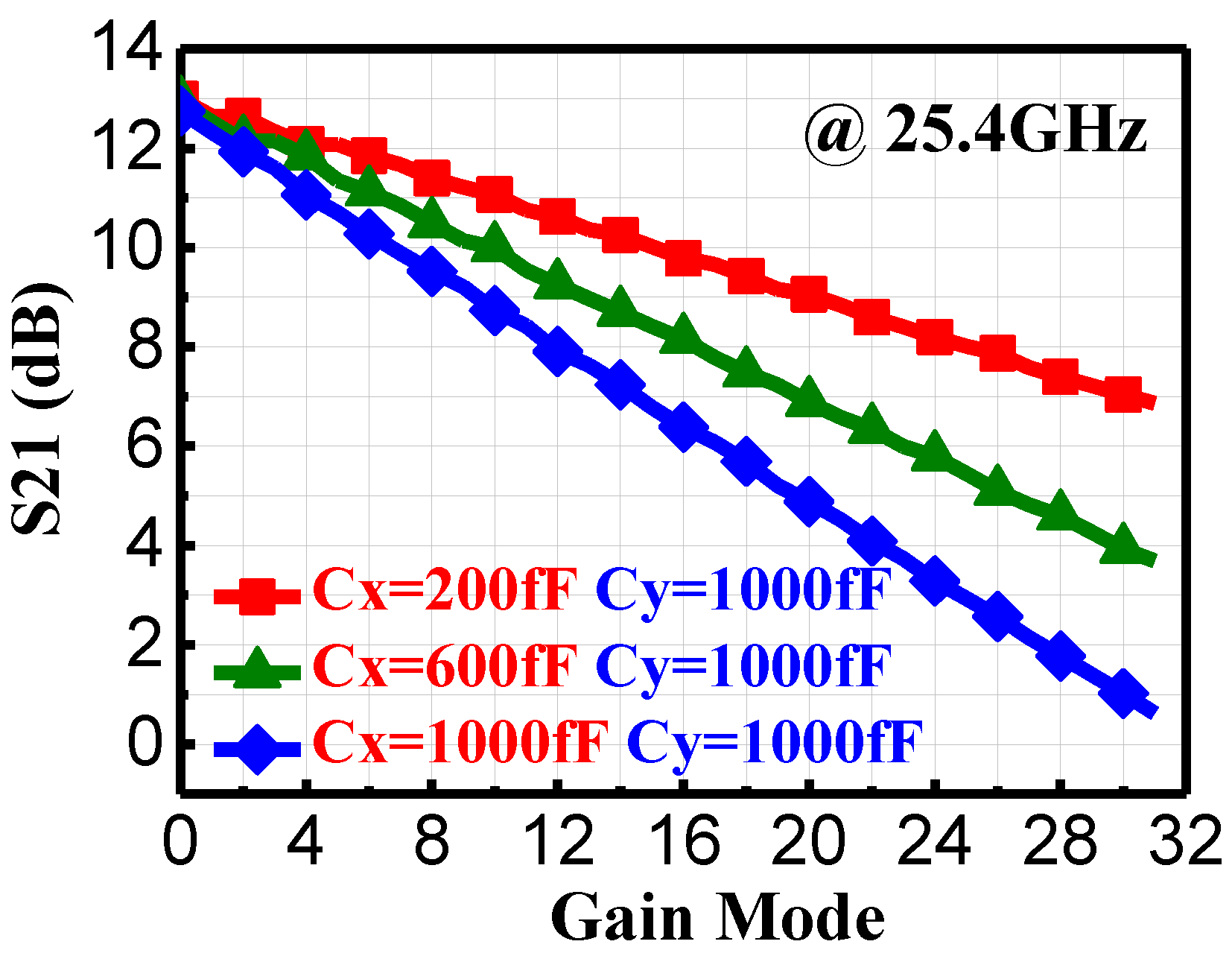

2. Design and Analysis of VGA

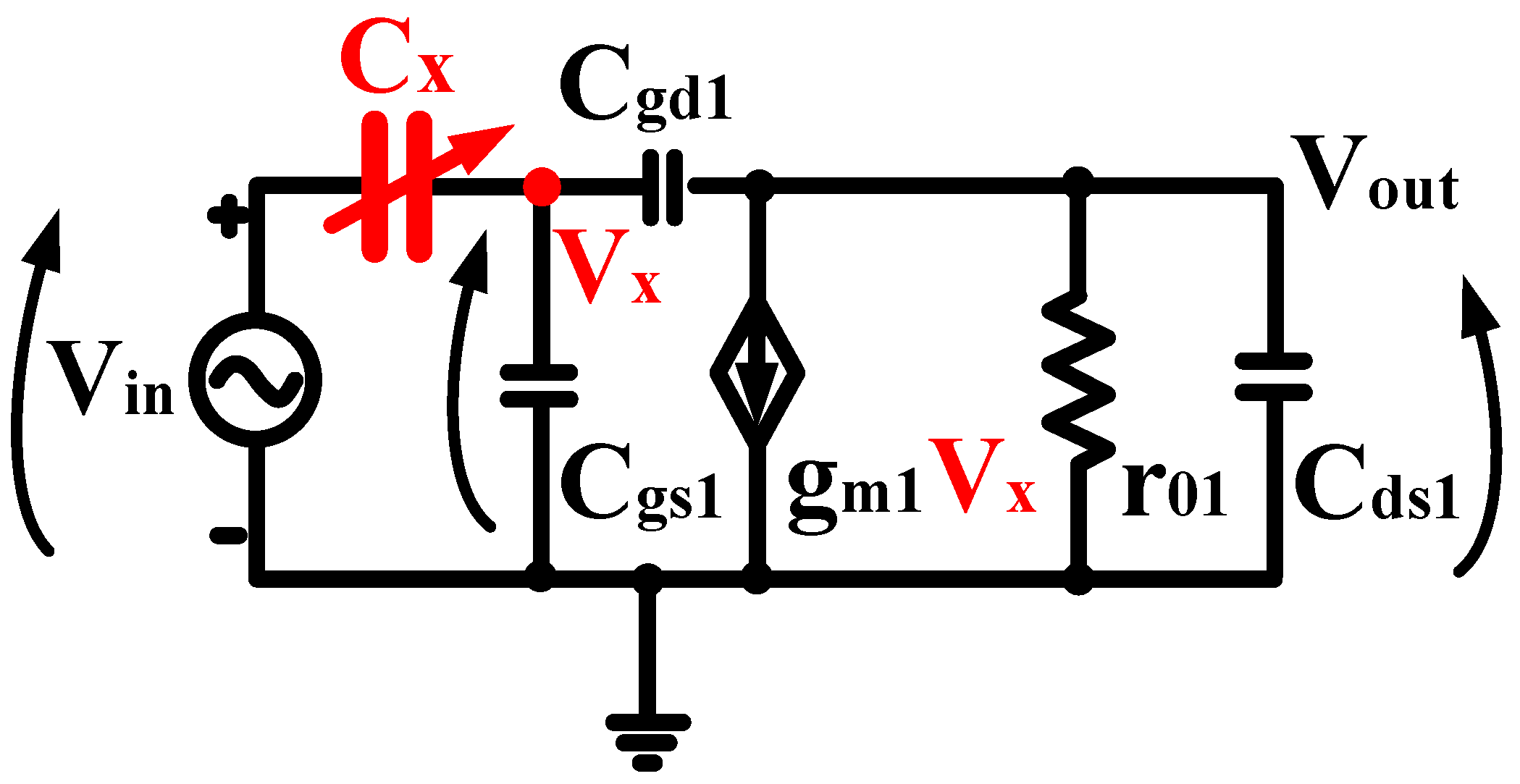

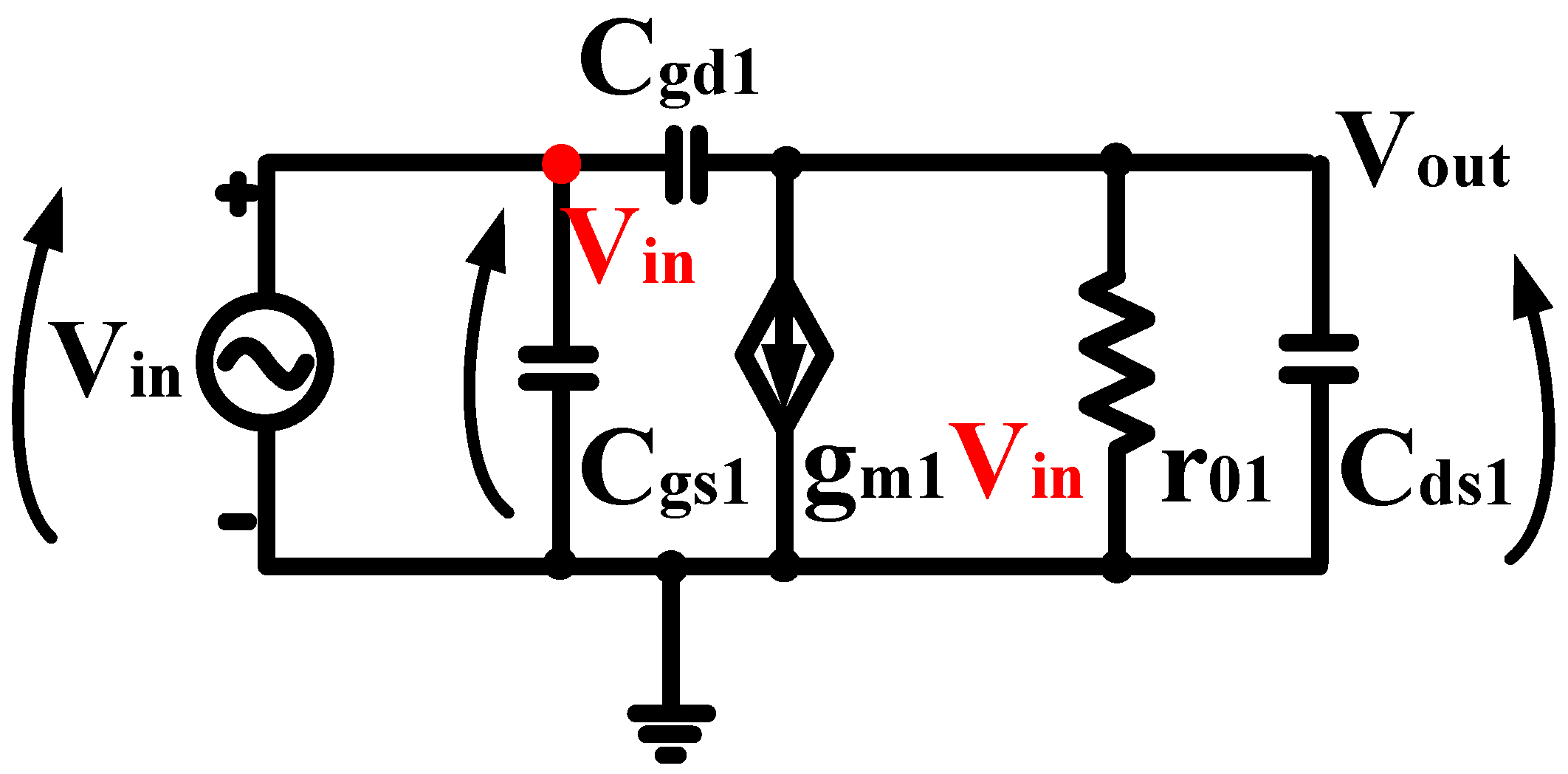

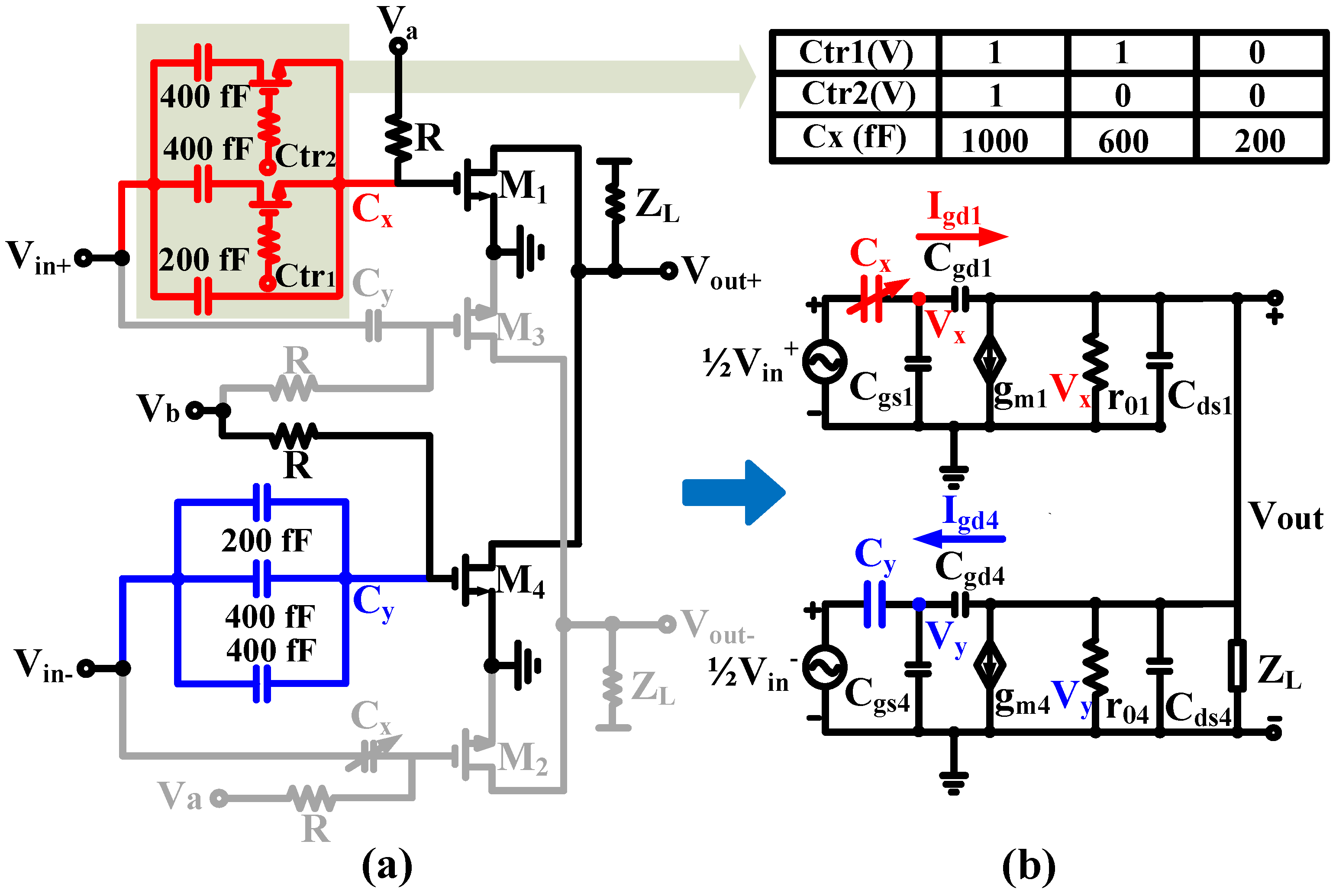

2.1. Asymmetric Capacitor-Based Reconfigurable Technique

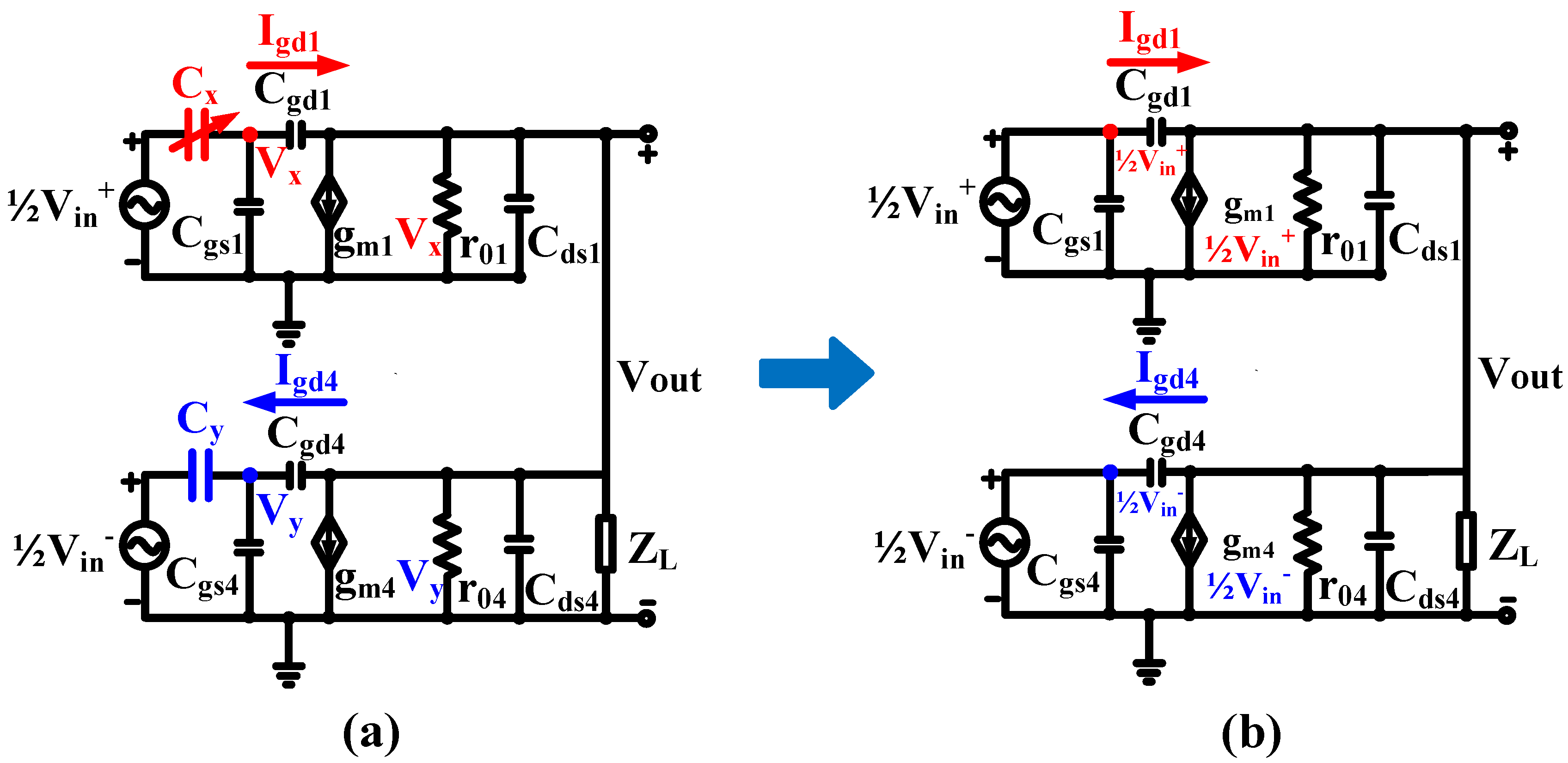

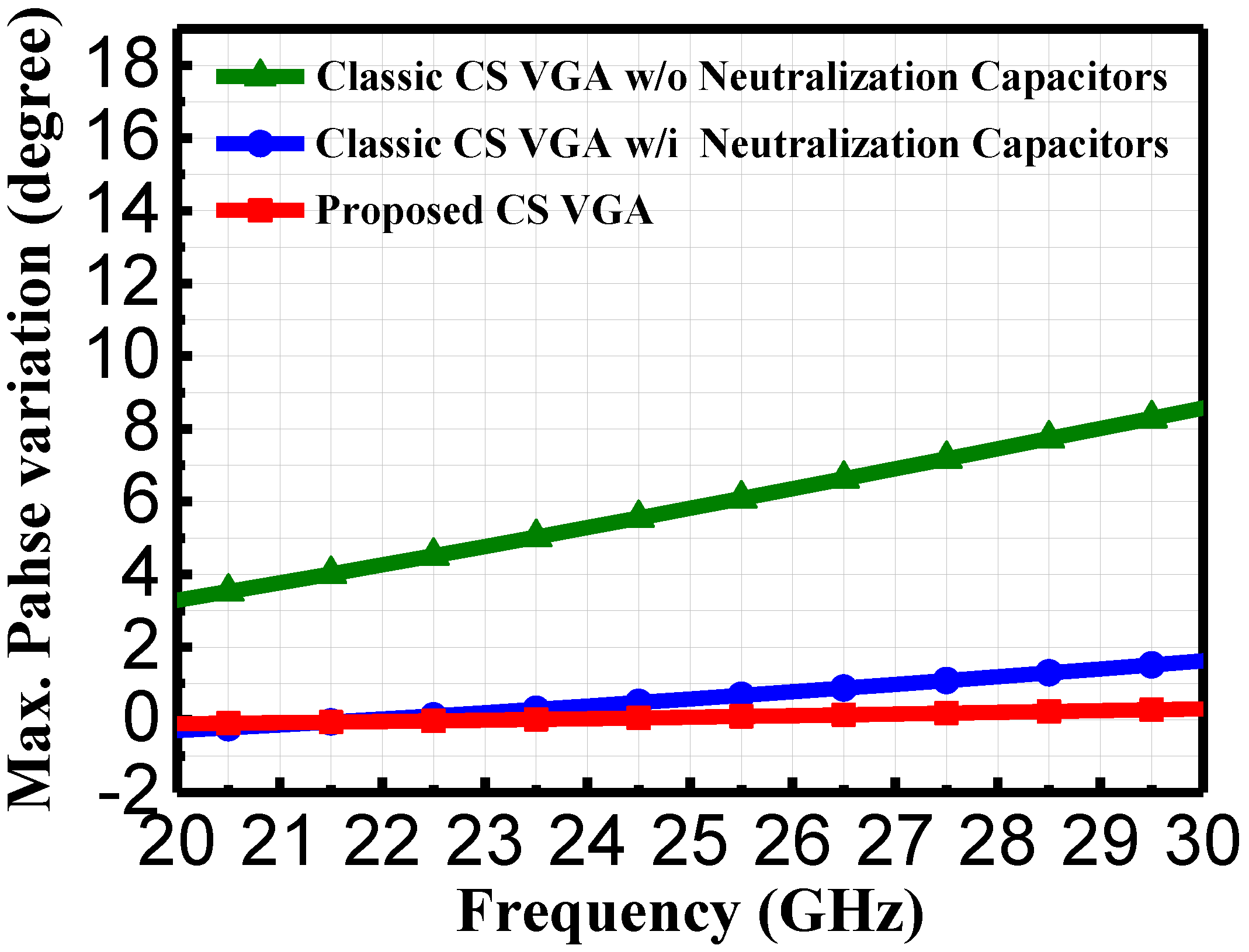

2.2. Phase Compensation Technique

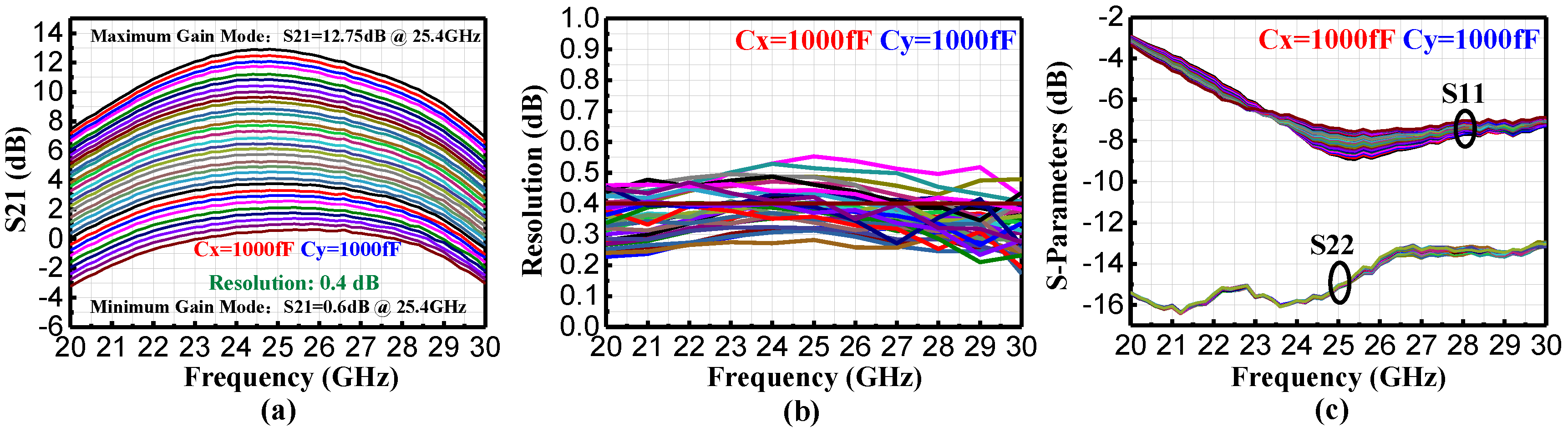

3. Measurement Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Appendix A

References

- Huang, D.; Zhang, L.; Li, D.; Zhang, L.; Wang, Y.; Yu, Z. A 60-GHz 360° 5-Bit Phase Shifter with Constant IL Compensation Followed by a Normal Amplifier with ±1 dB Gain Variation and 0.6-dBm OP-1dB. IEEE Trans. Circuits Syst. II Express Briefs 2016, 64, 1437–1441. [Google Scholar] [CrossRef]

- Li, W.-T.; Chiang, Y.-C.; Tsai, J.-H.; Yang, H.-Y.; Cheng, J.-H.; Huang, T.-W. 60-GHz 5-bit Phase Shifter with Integrated VGA Phase-Error Compensation. IEEE Trans. Microw. Theory Tech. 2013, 61, 1224–1235. [Google Scholar] [CrossRef]

- Roh, W.; Seol, J.-Y.; Park, J.; Lee, B.; Lee, J.; Kim, Y.; Cho, J.; Cheun, K.; Aryanfar, F. Millimeter-wave beamforming as an enabling technology for 5G cellular communications: Theoretical feasibility and prototype results. IEEE Commun. Mag. 2014, 52, 106–113. [Google Scholar] [CrossRef]

- Chen, Z.; Jiang, Z.; Liu, Z.; Cheng, Y.; Zhang, L.; Chen, D.; Zhang, J.; Sun, S.; Dong, J.; Liu, P.; et al. A 256-QAM 39 GHz Dual-Channel Transceiver Chipset with LTCC Package for 5G Communication in 65 nm CMOS. In Proceedings of the 2018 IEEE/MTT-S International Microwave Symposium—IMS, Philadelphia, PA, USA, 10–15 June 2018; pp. 1476–1479. [Google Scholar]

- Gao, L.; Ma, Q.; Rebeiz, G.M. A 20–44-GHz Image-Rejection Receiver With >75-dB Image-Rejection Ratio in 22-nm CMOS FD-SOI for 5G Applications. IEEE Trans. Microw. Theory Tech. 2020, 68, 2823–2832. [Google Scholar] [CrossRef]

- Kibaroglu, K.; Sayginer, M.; Phelps, T.; Rebeiz, G.M. A 64-Element 28-GHz Phased-Array Transceiver With 52-dBm EIRP and 8–12-Gb/s 5G Link at 300 Meters Without Any Calibration. IEEE Trans. Microw. Theory Tech. 2018, 66, 5796–5811. [Google Scholar] [CrossRef]

- Pang, J.; Wu, R.; Wang, Y.; Dome, M.; Kato, H.; Huang, H.; Narayanan, A.T.; Liu, H.; Liu, B.; Nakamura, T.; et al. A 28-GHz CMOS Phased-Array Transceiver Based on LO Phase-Shifting Architecture With Gain Invariant Phase Tuning for 5G New Radio. IEEE J. Solid-State Circuits 2019, 54, 1228–1242. [Google Scholar] [CrossRef]

- Huang, M.-Y.; Wang, H. A Mm-Wave Wideband MIMO RX With Instinctual Array-Based Blocker/Signal Management for Ultralow-Latency Communication. IEEE J. Solid-State Circuits 2019, 54, 3553–3564. [Google Scholar] [CrossRef]

- Wang, Y.; Wu, R.; Pang, J.; You, D.; Fadila, A.A.; Saengchan, R.; Fu, X.; Matsumoto, D.; Nakamura, T.; Kubozoe, R.; et al. A 39-GHz 64-Element Phased-Array Transceiver with Built-In Phase and Amplitude Calibrations for Large-Array 5G NR in 65-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 1249–1269. [Google Scholar] [CrossRef]

- Zhao, D.; Gu, P.; Zhong, J.; Peng, N.; Yang, M.; Yi, Y.; Zhang, J.; He, P.; Chai, Y.; Chen, Z.; et al. Millimeter-Wave Integrated Phased Arrays. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 3977–3990. [Google Scholar] [CrossRef]

- Shakib, S.; Elkholy, M.; Dunworth, J.; Aparin, V.; Entesari, K. 2.7 A wideband 28GHz power amplifier supporting 8 × 100 MHz carrier aggregation for 5G in 40 nm CMOS. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 44–45. [Google Scholar]

- Yi, Y.; Zhao, D.; You, X. A Ka-band CMOS Digital-Controlled Phase-Invariant Variable Gain Amplifier with 4-bit Tuning Range and 0.5-dB Resolution. In Proceedings of the 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Philadelphia, PA, USA, 10–12 June 2018; pp. 152–155. [Google Scholar]

- Shin, G.; Kim, K.; Lee, K.; Jeong, H.-H.; Song, H.-J. An E-Band 21-dB Variable-Gain Amplifier with 0.5-V Supply in 40-nm CMOS. Electronics 2021, 10, 804. [Google Scholar] [CrossRef]

- Lee, S.; Park, J.; Hong, S. A Ka-Band Phase-Compensated Variable-Gain CMOS Low-Noise Amplifier. IEEE Microw. Wirel. Components Lett. 2019, 29, 131–133. [Google Scholar] [CrossRef]

- Gao, H.; Li, N.; Li, M.; Wang, S.; Zhang, Z.; Kuan, Y.-C.; Song, C.; Yu, X.; Gu, Q.J.; Xu, Z. A 6.5–12-GHz Balanced Variable-Gain Low-Noise Amplifier With Frequency-Selective Gain Equalization Technique. IEEE Trans. Microw. Theory Tech. 2021, 69, 732–744. [Google Scholar] [CrossRef]

- Kuo, C.-C.; Tsai, Z.-M.; Tsai, J.-H.; Wang, H. A 71–76 GHz CMOS variable gain amplifier using current steering technique. In Proceedings of the 2008 IEEE Radio Frequency Integrated Circuits Symposium, Atlanta, GA, USA, 15–17 June 2008; pp. 609–612. [Google Scholar]

- Hsieh, C.-Y.; Kao, J.-C.; Kuo, J.-J.; Lin, K.-Y. A 57–64 GHz low-phase-variation variable-gain amplifier. In Proceedings of the 2012 IEEE/MTT-S International Microwave Symposium Digest, Montreal, QC, Canada, 17–22 June 2012; pp. 1–3. [Google Scholar]

- Siao, D.-S.; Kao, J.-C.; Wang, H. A 60 GHz Low Phase Variation Variable Gain Amplifier in 65 nm CMOS. IEEE Microw. Wirel. Components Lett. 2014, 24, 457–459. [Google Scholar] [CrossRef]

- Kong, L.; Chen, Y.; Boon, C.C.; Mak, P.; Martins, R.P. A Wideband Inductorless dB-Linear Automatic Gain Control Amplifier Using a Single-Branch Negative Exponential Generator for Wireline Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 3196–3206. [Google Scholar] [CrossRef]

- Huang, D.; Zhang, L.; Zhang, L.; Wang, Y. A 60-GHz, 15-dB Gain Range Digitally Controlled Phase-Inverting VGA With 0-dBm OP1 dB and 3° Phase Variation in 65-nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 819–821. [Google Scholar] [CrossRef]

- Kim, S.H.; Jang, T.H.; Kim, J.H.; Park, C.S. A Wideband 120-GHz Variable Gain Amplifier with Multistage Phase Compensation. IEEE Trans. Microw. Theory Tech. 2020, 68, 2419–2427. [Google Scholar] [CrossRef]

- Park, J.; Lee, S.; Lee, D.; Hong, S. 9.8 A 28GHz 20.3%-Transmitter-Efficiency 1.5°-Phase-Error Beamforming Front-End IC with Embedded Switches and Dual-Vector Variable-Gain Phase Shifters. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 176–178. [Google Scholar]

- Wu, T.; Zhao, C.; Liu, H.; Wu, Y.; Yu, Y.; Kang, K. A 20~43 GHz VGA with 21.5 dB Gain Tuning Range and Low Phase Variation for 5G Communications in 65-nm CMOS. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 71–74. [Google Scholar]

- Chan, W.L.; Long, J.R. A 58–65 GHz Neutralized CMOS Power Amplifier With PAE Above 10% at 1-V Supply. IEEE J. Solid-State Circuits 2010, 45, 554–564. [Google Scholar] [CrossRef]

- Li, C.-H.; Liu, Y.-L.; Kuo, C.-N. A 0.6-V 0.33-mW 5.5-GHz receiver front-end using resonator coupling technique. IEEE Trans. Microw. Theory Tech. 2011, 46, 1629–1638. [Google Scholar] [CrossRef]

| This Study | ISSCC 2017 [11] | RFIC 2018 [12] | MWCL 2019 [14] | TMTT 2021 [15] | |

|---|---|---|---|---|---|

| Technology | 65 nm CMOS | 40 nm CMOS | 65 nm CMOS | 65 nm CMOS | 55 nm CMOS |

| Topology | Stackless | Two-stack | Two-stack | Two-stack | Two-stack |

| Supply (V) | 1 | 1.1 | 1.2 | 1.2 | 1.3 |

| Freq (GHz) | 21.4–29 | 26–36 | 27–42 | 30–34.5 | 6.5–12 |

| S11 (dB) | −9~−5 | −20~−10 | −30~−4 | −28~−11 | −14~−36 |

| S22 (dB) | −17~−13 | −7~−6 | −50~−5 | −30~−10 | −14~−35 |

| Peak gain (dB) | 13 | 22.4 | 9.6 | 20.8 | 20.7 |

| ΔG (dB) | 12.2/9.2/6.1 | 8 | 7.5 | 10.6 | 18 |

| Gain resolution (dB) | 0.4/0.3/0.2 | 1 | 0.5 | 20.1 | N/A |

| RMS phase error (°) | <1.9/2.4/5.5 | <6 * | <3.5 | <8 ** | <4.5 |

| OP1 dB (dBm) | 8.6 | 13.7 | 2.5 | −0.6 # | 7.5 # |

| PDC (mW) | 98 | 30.3 | 15.6 | 26.7 | 75 |

| Core Area (mm2) | 0.174 | 0.23 | 0.083 | 0.2 | 0.98 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Q.; Zhao, C.; Kang, K. A Wideband Reconfigurable CMOS VGA Based on an Asymmetric Capacitor Technique with a Low Phase Variation. Electronics 2022, 11, 751. https://doi.org/10.3390/electronics11050751

Zhang Q, Zhao C, Kang K. A Wideband Reconfigurable CMOS VGA Based on an Asymmetric Capacitor Technique with a Low Phase Variation. Electronics. 2022; 11(5):751. https://doi.org/10.3390/electronics11050751

Chicago/Turabian StyleZhang, Qingfeng, Chenxi Zhao, and Kai Kang. 2022. "A Wideband Reconfigurable CMOS VGA Based on an Asymmetric Capacitor Technique with a Low Phase Variation" Electronics 11, no. 5: 751. https://doi.org/10.3390/electronics11050751