Indirect Matrix Converter Hardware-in-the-Loop Semi-Physical Simulation Based on Latency-Free Decoupling

Abstract

:1. Introduction

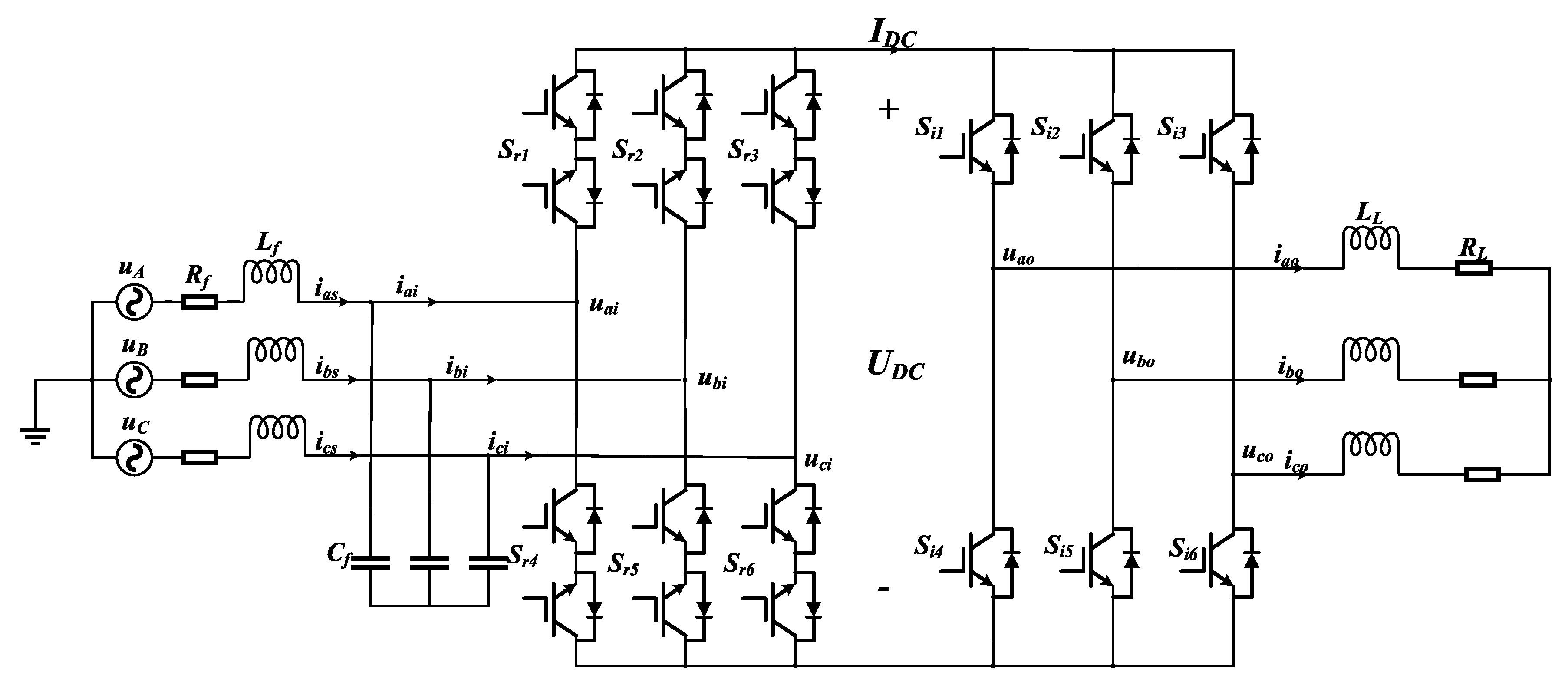

2. Circuit Topology of IMCs

2.1. IMC Mathematical Model

2.2. IMC Control

- (1)

- First, define the reference current and set the input reference power . It is necessary to measure the input voltage , the input current , the rectifier-side input voltage and the output current .

- (2)

- Predict the next occurrence of and from the switching state and measured values.

- (3)

- Finally, the predicted values are used to calculate the cost function k. The predicted values that minimize the cost are selected and the switching state is output. Since the predictive controller is formulated in discrete time, it is necessary to derive a discrete time model of the load converter system. The predictive variables at the input side are as follows:where and , with

3. Decoupled Modeling Analysis

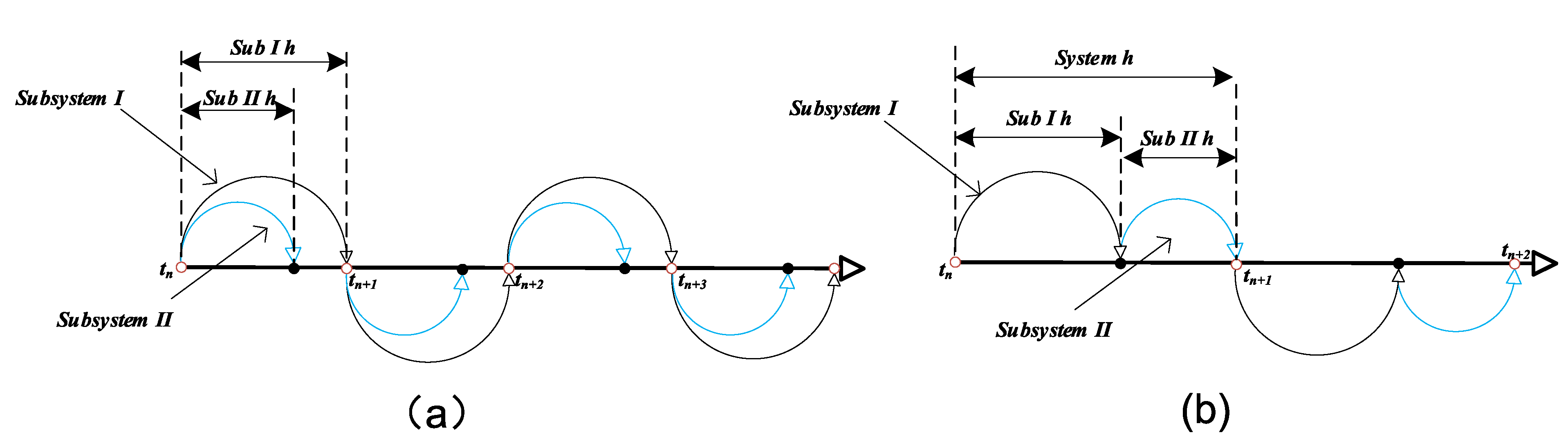

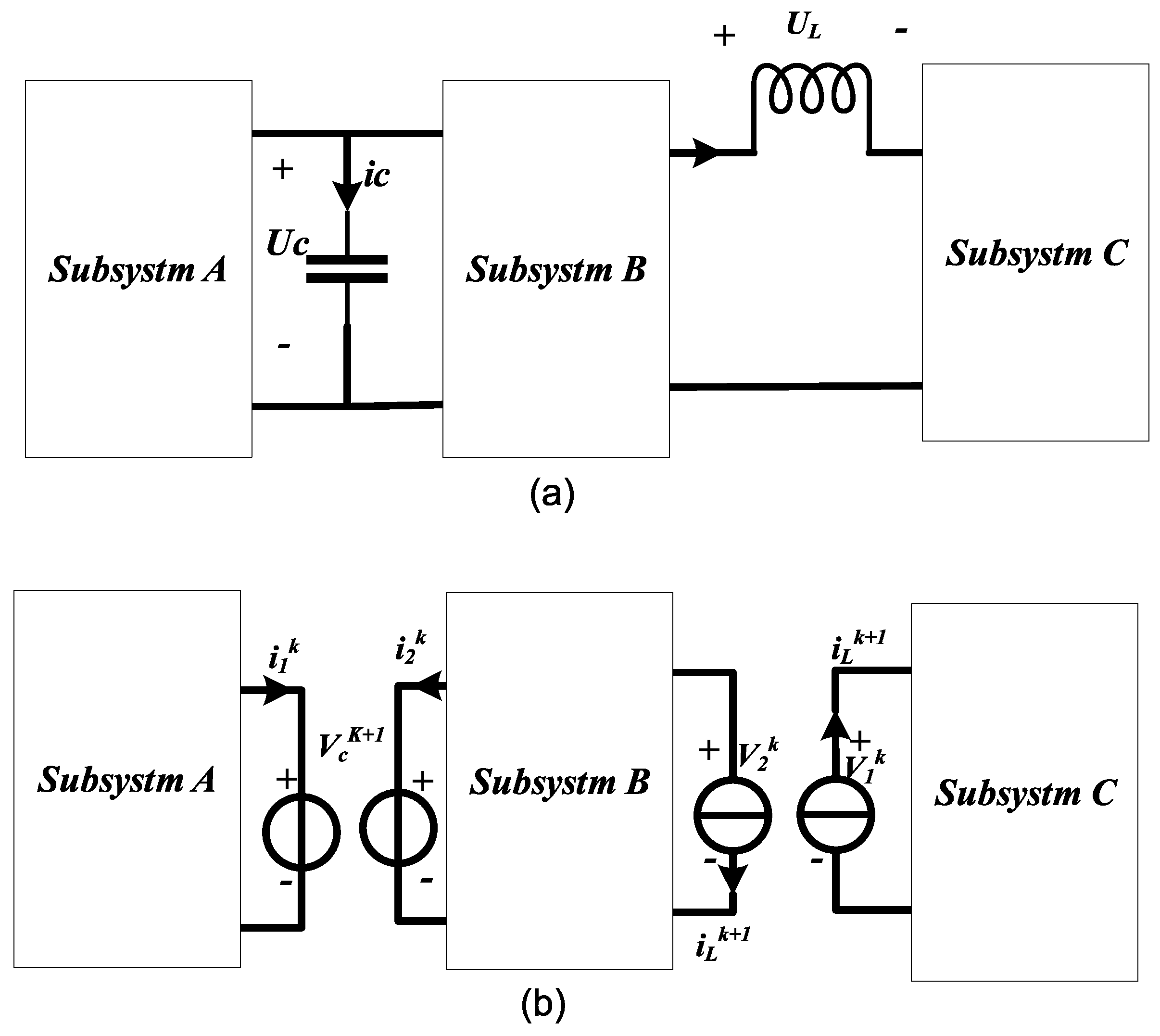

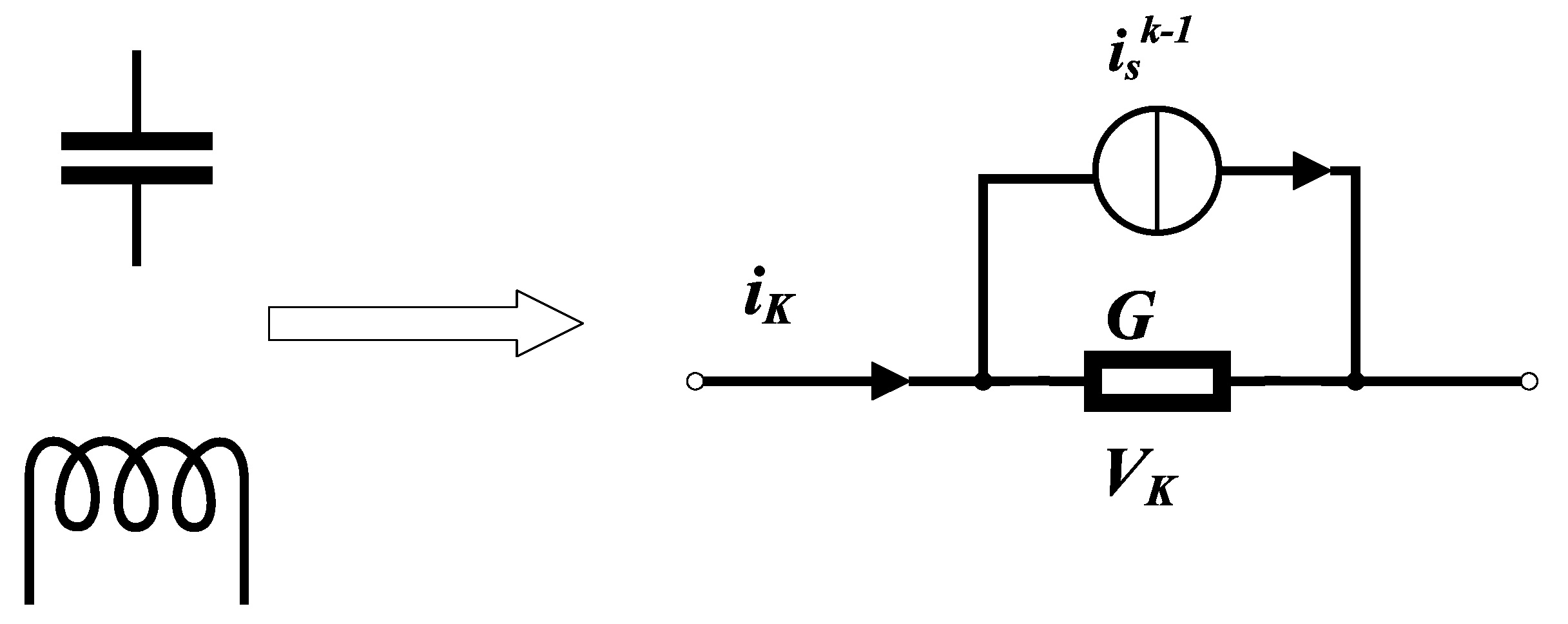

3.1. Latency-Free Decoupling Approach

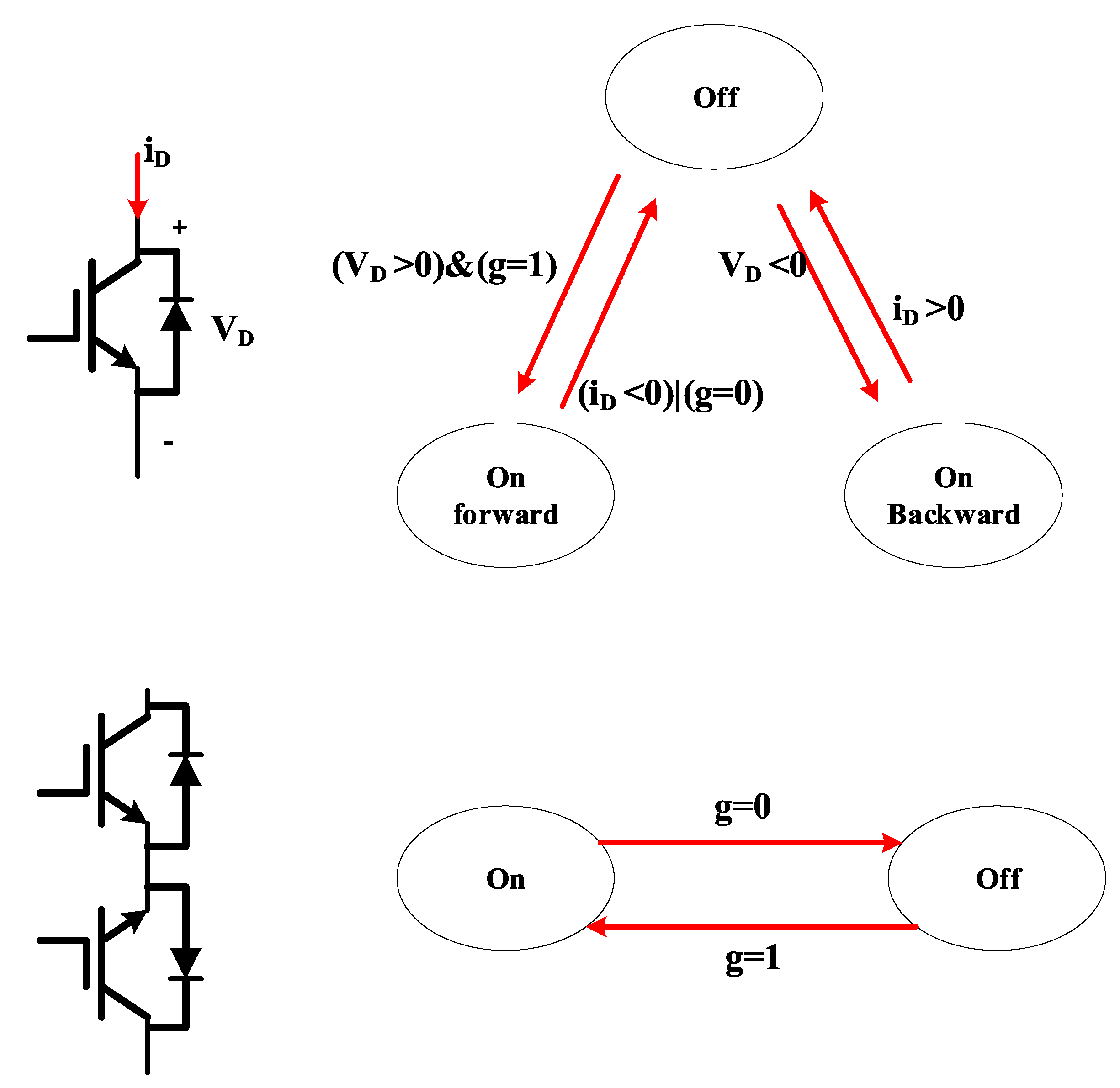

3.2. Switch Status Update

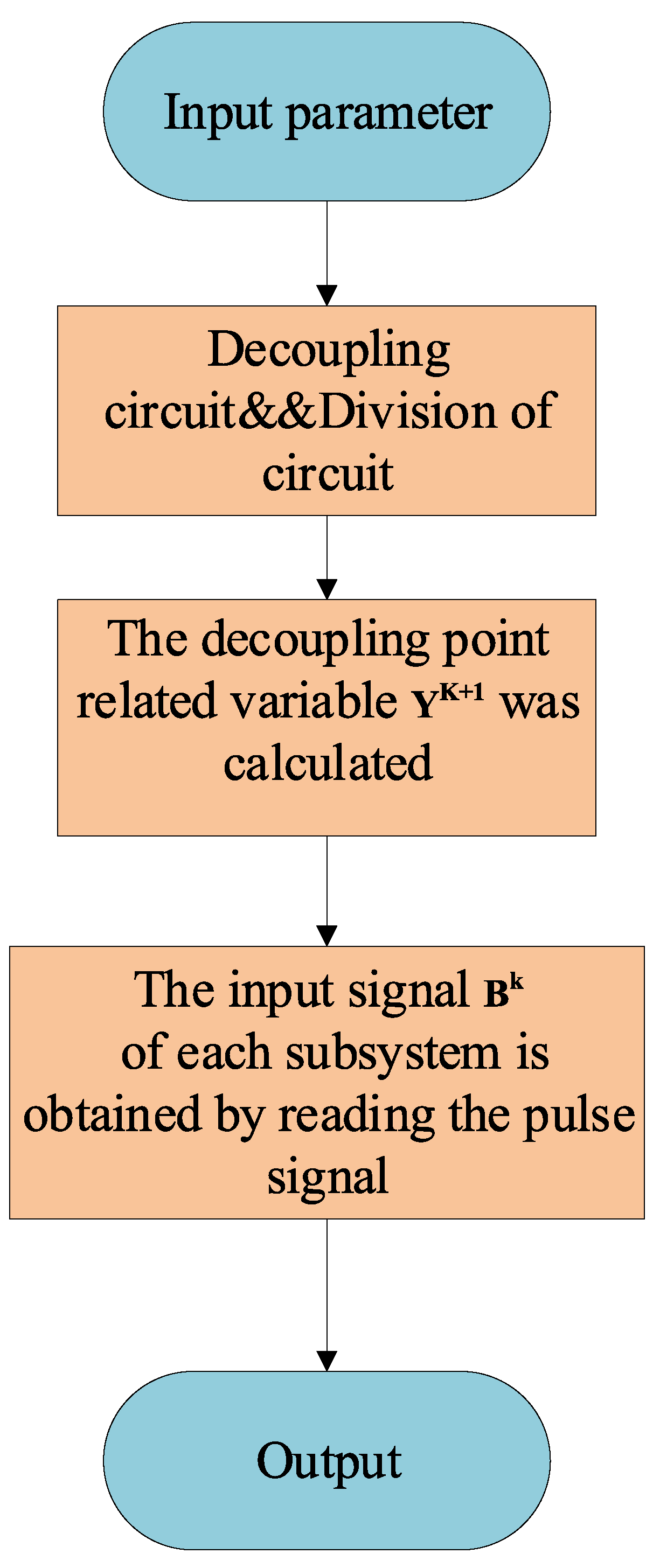

3.3. Modeling Analysis Steps

- (1)

- The circuit is first split using latency-free decoupling at the selected shunt inductor and series capacitor after forward Eulerian discretization to obtain the correlation variables , i.e., the capacitance voltage and the inductance current, at the decoupling.

- (2)

- The passive elements in the remaining circuit are then discretized and equated to a Norton-equivalent circuit, and then the state space equations are written according to Kirchhoff’s voltage–current law.

- (3)

- Then, according to the switch update rule, the switch update state is determined via the control signal, switch current, and voltage, and combined with the correlation variable in step (1). Each subsystem input is then reconstructed.

- (4)

- The state equations for each subsystem are computed in parallel, and the next step-length vector is output.

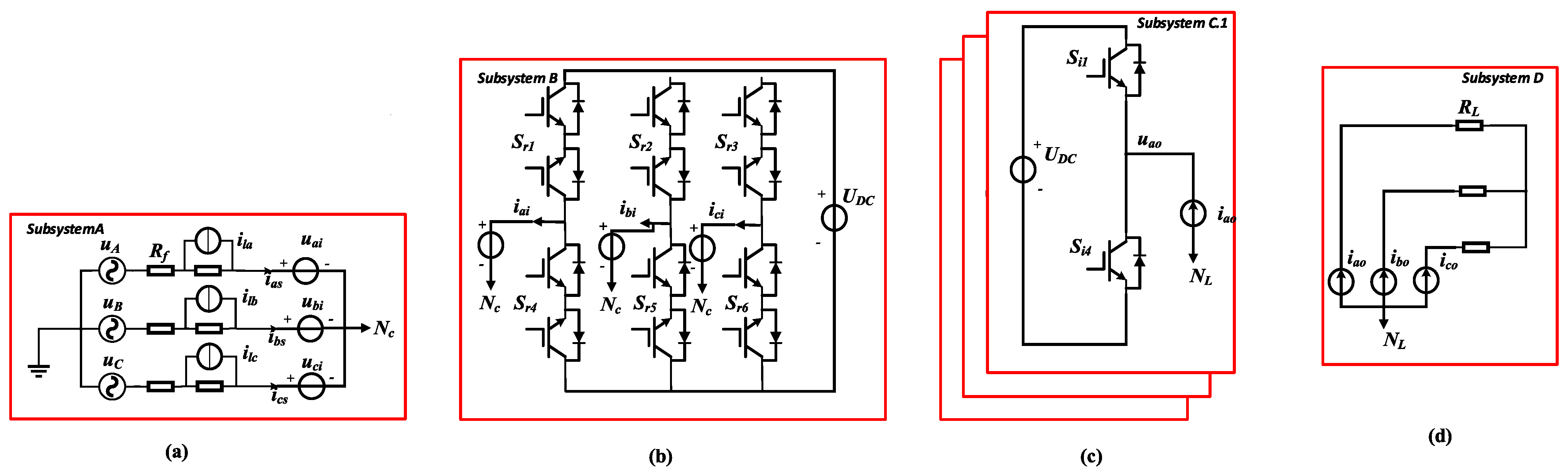

3.4. IMC Decoupled Modeling

4. Experiments

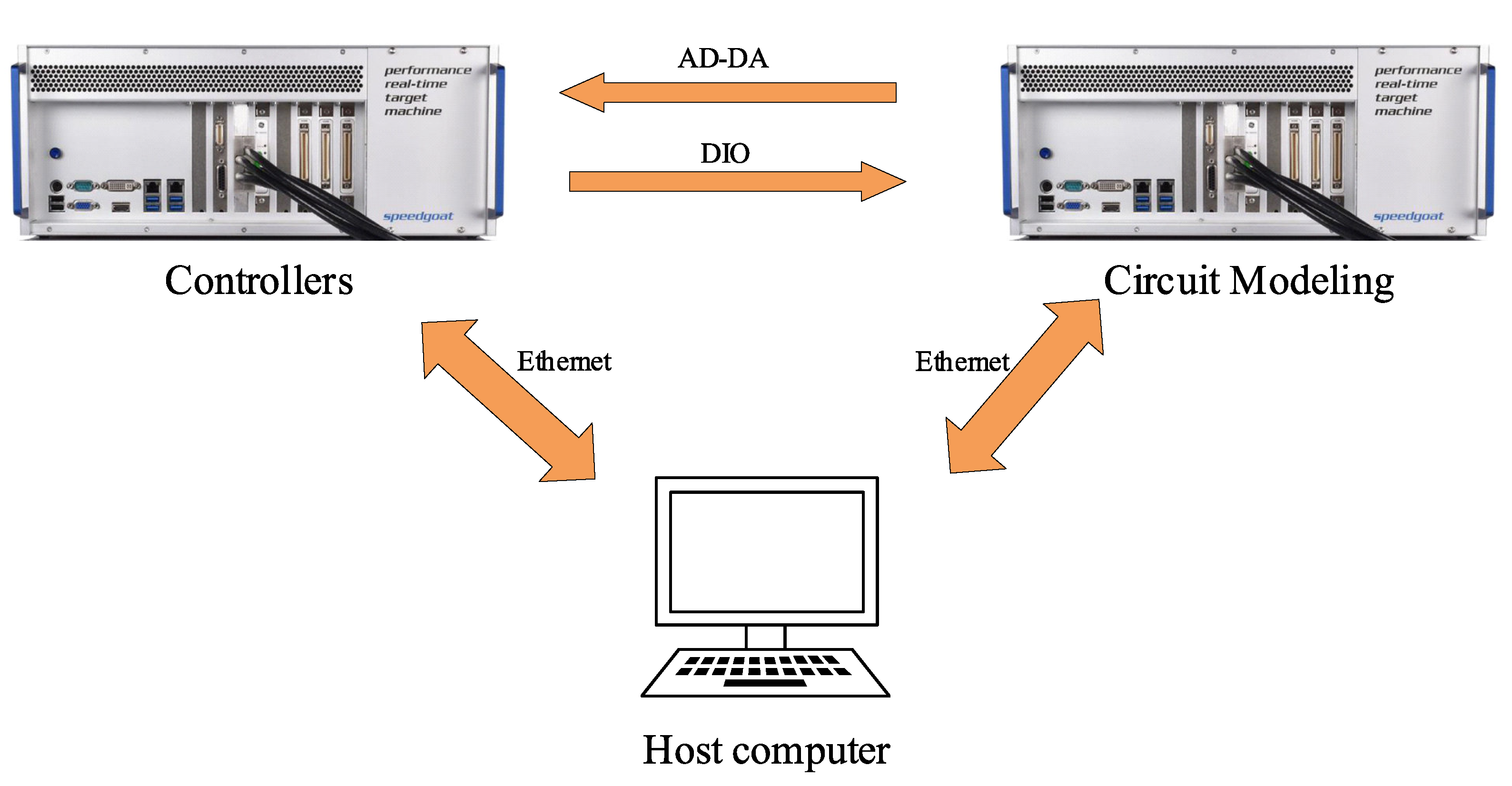

4.1. Experimental Environment

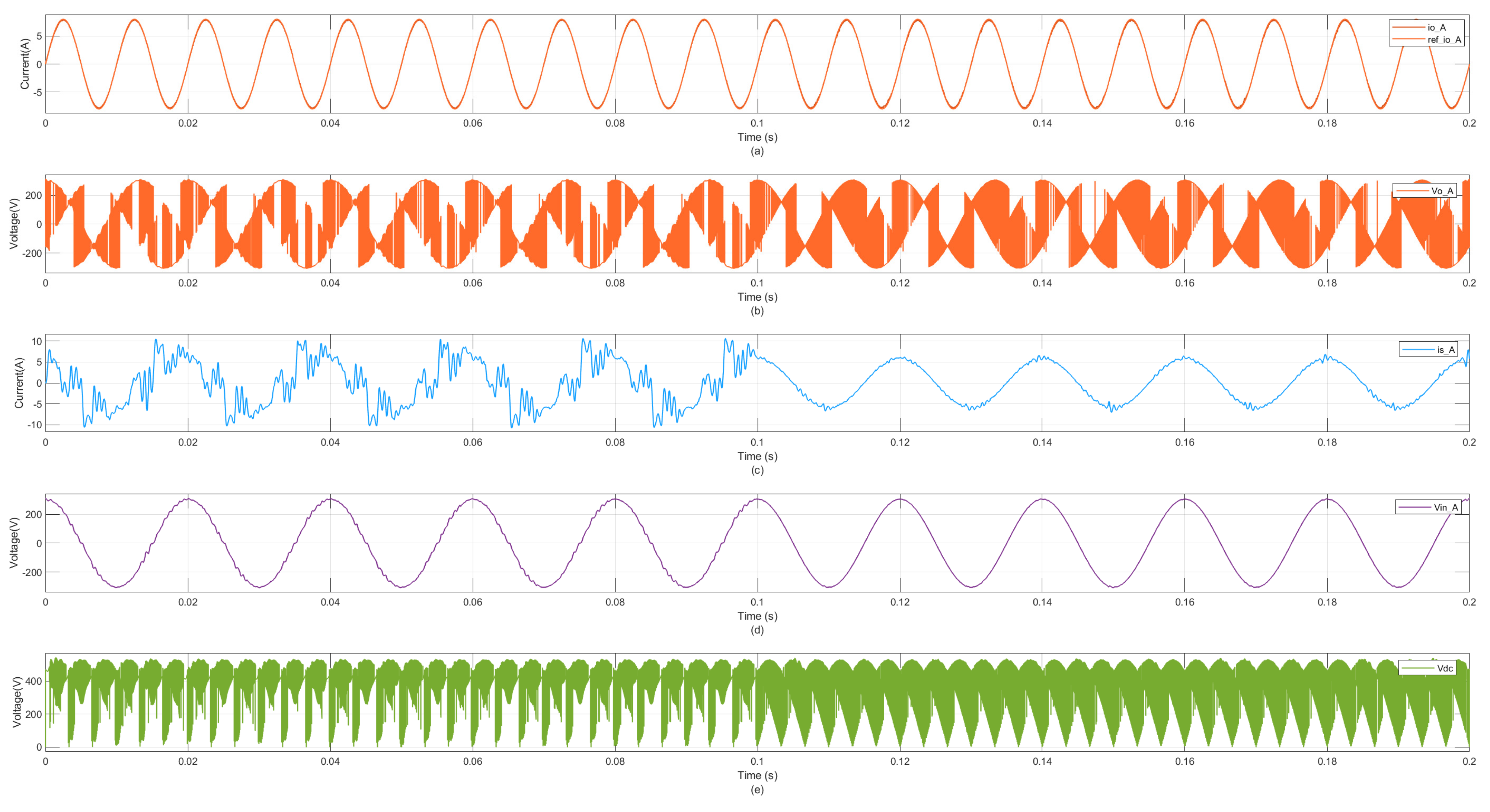

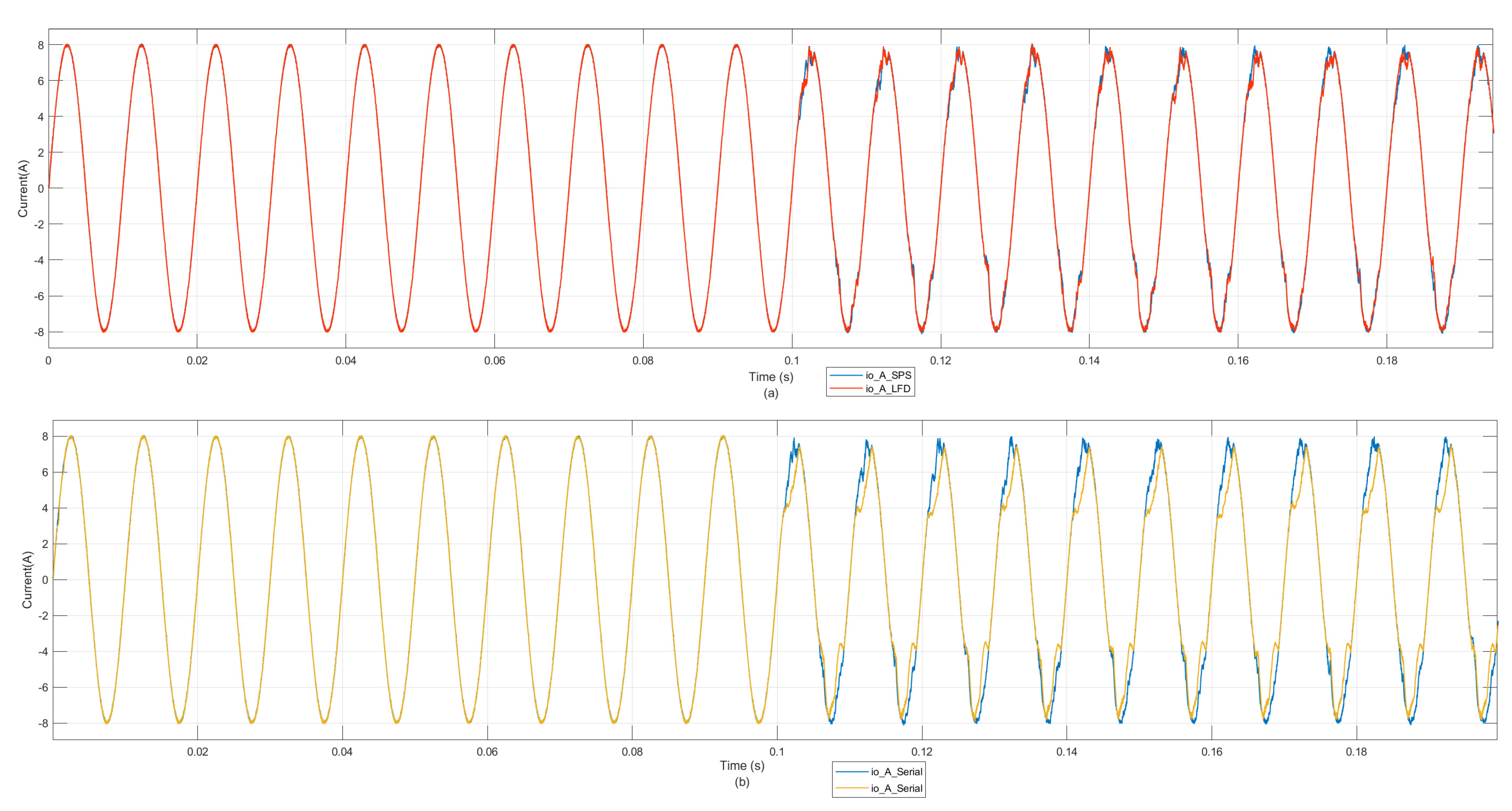

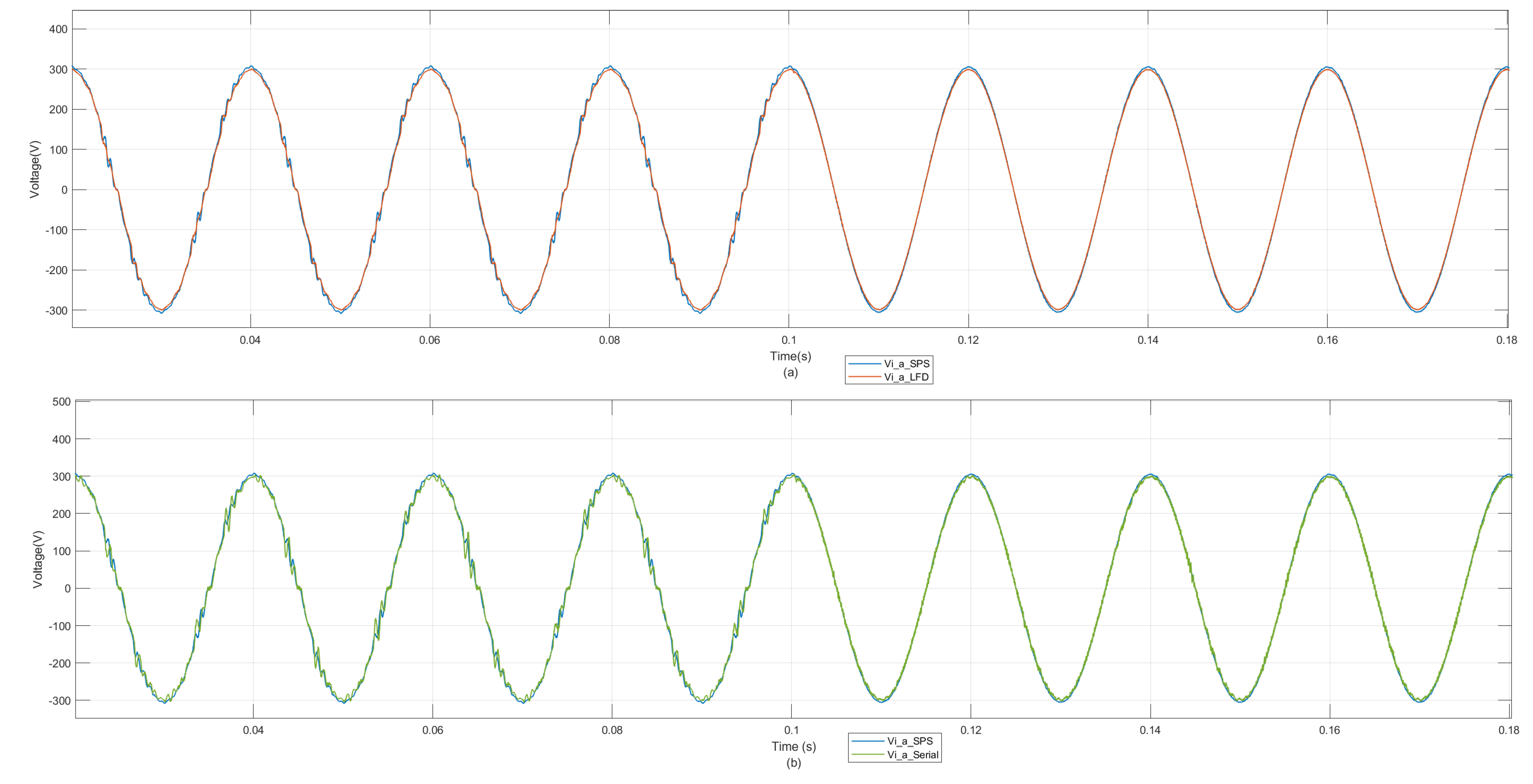

4.2. Real-Time Simulation Results

4.3. Resource Consumption and Time Step

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Di, Z.; Xu, D.; Zhang, K. Continuous Control Set Model Predictive Control for an Indirect Matrix Converter. Energies 2021, 14, 4114. [Google Scholar] [CrossRef]

- Tawfiq, K.B.; Ibrahim, M.N.; Rezk, H.; El-kholy, E.E.; Sergeant, P. Mathematical Modelling, Analysis and Control of a Three to Five-Phase Matrix Converter for Minimal Switching Losses. Mathematics 2021, 9, 96. [Google Scholar] [CrossRef]

- Ramalho, A.W.S.; Vitorino, M.A.; Corrêa, M.B.d.R.; Costa, L.A.L.d.A.C.; Braga-Filho, E.R. New Family of Two-to-Three-Phase AC–AC Indirect Matrix Converters with Open-End Rectifier Stage. IEEE Trans. Ind. Appl. 2022, 58, 517–530. [Google Scholar] [CrossRef]

- Garcia, C.F.; Rivera, M.E.; Rodríguez, J.R.; Wheeler, P.W.; Peña, R.S. Predictive Current Control with Instantaneous Reactive Power Minimization for a Four-Leg Indirect Matrix Converter. IEEE Trans. Ind. Electron. 2017, 64, 2. [Google Scholar] [CrossRef]

- Varajão, D.; Araújo, R.E. Modulation Methods for Direct and Indirect Matrix Converters: A Review. Electronics 2021, 10, 812. [Google Scholar] [CrossRef]

- Gong, Z.; Li, J.; Dai, P.; Su, D.; Wu, X. Design and Evaluation of a Virtual Vector Based Modulated Model Predictive Control for the Indirect Matrix Converters with Improved Performance. IEEE Trans. Ind. Electron. 2022, 69, 12019–12029. [Google Scholar] [CrossRef]

- Meddah, K.; Robert, T.; Rutovic, E.; Monthéard, R.; Ould-Bachir, T. Real-Time Simulation of a Neutral Point Clamped Dual Active Bridge Converter. In Proceedings of the 2022 IEEE 1st Industrial Electronics Society Annual On-Line Conference (ONCON), Kharagpur, India, 9–11 December 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Matar, M.; Iravani, R. FPGA Implementation of the Power Electronic Converter Model for Real-Time Simulation of Electromagnetic Transients. IEEE Trans. Power Deliv. 2010, 25, 2. [Google Scholar] [CrossRef]

- Rødal, G.L.; Peftitsis, D. Real-Time FPGA Simulation of High-Voltage Silicon Carbide MOSFETs. IEEE Trans. Power Electron. 2023, 38, 3213–3234. [Google Scholar] [CrossRef]

- Ebrahimi, S.; Amiri, N.; Jatskevich, J. Interfacing of Parametric Average-Value Models of LCR Systems in Fixed-Time-Step Real-Time EMT Simulations. IEEE Trans. Energy Convers. 2020, 35, 1985–1988. [Google Scholar] [CrossRef]

- Bieber, L.; Wang, L.; Jatskevich, J.; Li, W. Universal Equivalent Model for Real-Time CPU/FPGA Co-Simulation of Hybrid Cascaded Multilevel Converters. IEEE Access 2023, 11, 4228–4241. [Google Scholar] [CrossRef]

- Shin, D.-C.; Lee, D.-M. Development of Real-Time Implementation of a Wind Power Generation System with Modular Multilevel Converters for Hardware in the Loop Simulation Using MATLAB/Simulink. Electronics 2020, 9, 606. [Google Scholar] [CrossRef]

- Lee, J.; Kang, D.; Lee, J. A Study on the Improved Capacitor Voltage Balancing Method for Modular Multilevel Converter Based on Hardware-In-the-Loop Simulation. Electronics 2019, 8, 1070. [Google Scholar] [CrossRef]

- Kim, M.-n.; Yi, J.-s.; Won, C.-Y.; Lee, J.-H. Methods to Improve Dynamic System Response of Power Compensators Using Supercapacitors in Low-Voltage Ride-Through (LVRT) Conditions. Electronics 2022, 11, 1144. [Google Scholar] [CrossRef]

- Milton, M.; Benigni, A. Latency Insertion Method Based Real-Time Simulation of Power Electronic Systems. IEEE Trans. Power Electron. 2018, 33, 7166–7177. [Google Scholar] [CrossRef]

- Liu, C.; Ma, R.; Bai, H.; Gechter, F.; Gao, F. A new approach for FPGA-based real-time simulation of power electronic system with no simulation latency in subsystem partitioning. Int. J. Electr. Power Energy Syst. 2018, 99, 650–658. [Google Scholar] [CrossRef]

- Xu, J.; Wang, K.; Wu, P.; Li, Z.; Liu, Y.; Li, G.; Zheng, W. FPGA-Based Submicrosecond-Level Real-Time Simulation of Solid-State Transformer with a Switching Frequency of 50 kHz. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 4212–4224. [Google Scholar] [CrossRef]

- Grégoire, L.-A.; Blanchette, H.F.; Bélanger, J.; Al-Haddad, K. Real-Time Simulation-Based Multisolver Decoupling Technique for Complex Power-Electronics Circuits. IEEE Trans. Power Deliv. 2016, 31, 2313–2321. [Google Scholar] [CrossRef]

- Asai, H.; Tsuboi, N. Multi-Rate Latency Insertion Method with RLCG-MNA Formulation for Fast Transient Simulation of Large-Scale Interconnect and Plane Networks. In Proceedings of the 2007 Proceedings 57th Electronic Components and Technology Conference, Sparks, NV, USA, 29 May–1 June 2007. [Google Scholar] [CrossRef]

| Variables | Description | Value |

|---|---|---|

| Supply phase voltage | 311.1 V | |

| Supply frequency | 50 Hz | |

| Input filter inductance | 400 H | |

| Input filter capacitance | 30 F | |

| Input filter resistance | 1 | |

| Load resistance | 30 | |

| Load inductance | 10 mH |

| Latency-Free Decoupling | Serial | |

|---|---|---|

| Multipliers | 34 | 24 |

| Adders/Subtractors | 721 | 921 |

| Registers | 38 | 31 |

| Total 1-Bit Registers | 1104 | 592 |

| Multiplexers | 5971 | 7308 |

| I/O Bits | 954 | 388 |

| Static shift operators | 0 | 260 |

| Dynamic shift operators | 91 | 97 |

| Time step (minimum delay path) | 153.845 ns | 380.254 ns |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sang, Z.; Li, S.; Huang, Y.; Gao, X.; Qiao, R. Indirect Matrix Converter Hardware-in-the-Loop Semi-Physical Simulation Based on Latency-Free Decoupling. Electronics 2023, 12, 4802. https://doi.org/10.3390/electronics12234802

Sang Z, Li S, Huang Y, Gao X, Qiao R. Indirect Matrix Converter Hardware-in-the-Loop Semi-Physical Simulation Based on Latency-Free Decoupling. Electronics. 2023; 12(23):4802. https://doi.org/10.3390/electronics12234802

Chicago/Turabian StyleSang, Zhongqing, Shaojie Li, Yuanyuan Huang, Xin Gao, and Rui Qiao. 2023. "Indirect Matrix Converter Hardware-in-the-Loop Semi-Physical Simulation Based on Latency-Free Decoupling" Electronics 12, no. 23: 4802. https://doi.org/10.3390/electronics12234802

APA StyleSang, Z., Li, S., Huang, Y., Gao, X., & Qiao, R. (2023). Indirect Matrix Converter Hardware-in-the-Loop Semi-Physical Simulation Based on Latency-Free Decoupling. Electronics, 12(23), 4802. https://doi.org/10.3390/electronics12234802