Influence of JFET Width on Short-Circuit Robustness of 1200 V SiC Power MOSFETs

Abstract

:1. Introduction

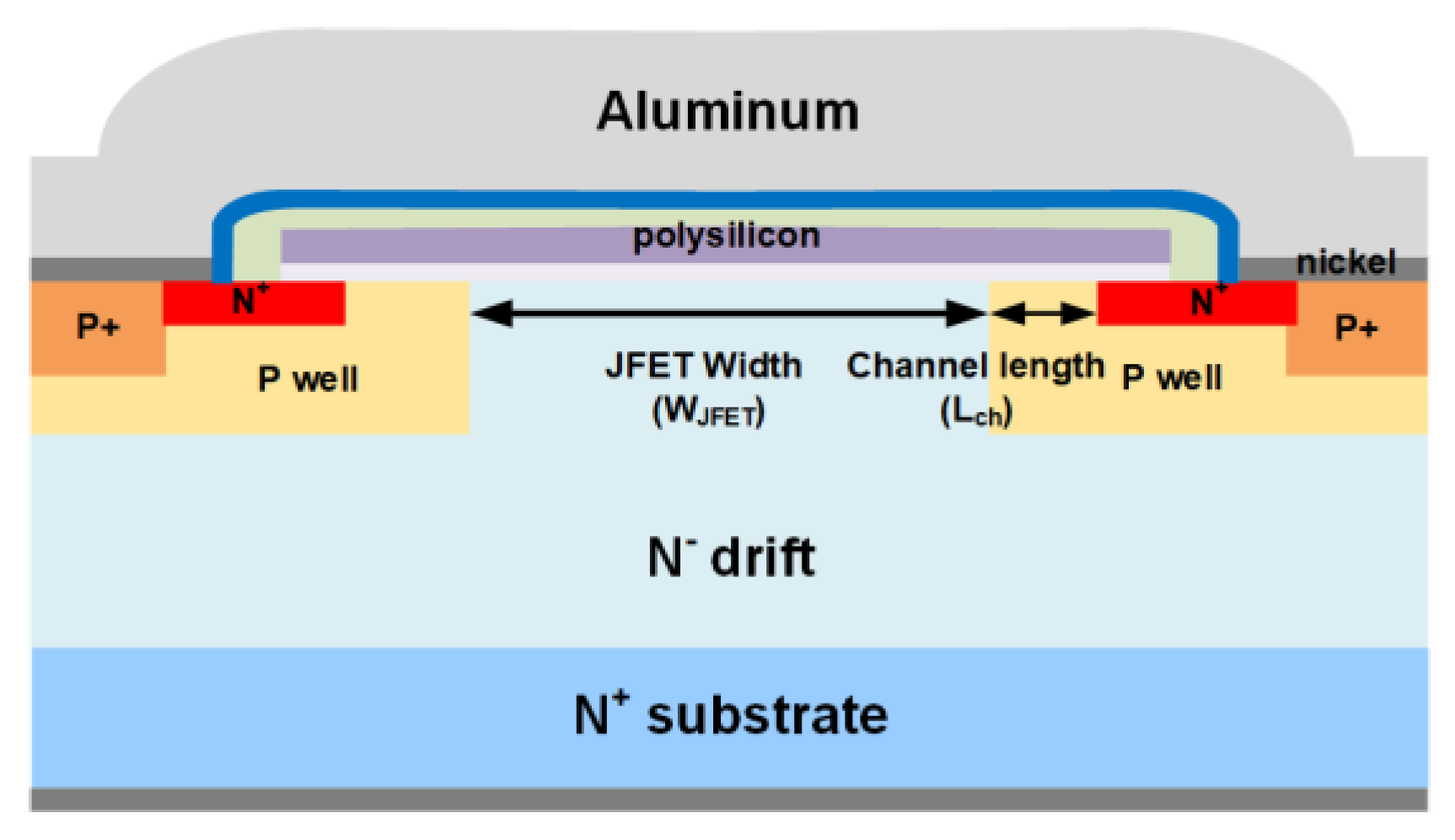

2. Materials and Methods

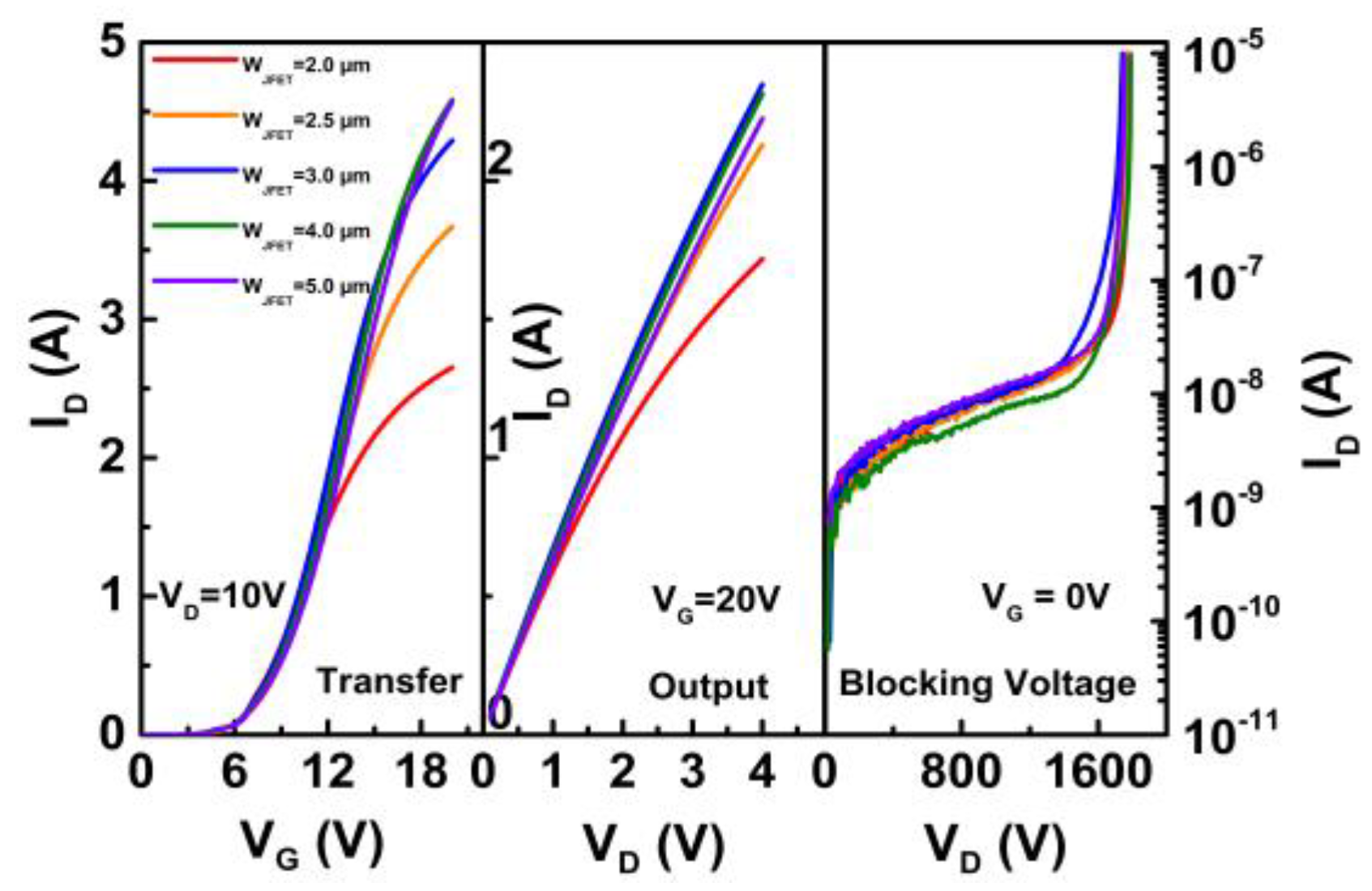

2.1. Static Characteristics of SiC MOSFETs with Different Structural Parameters

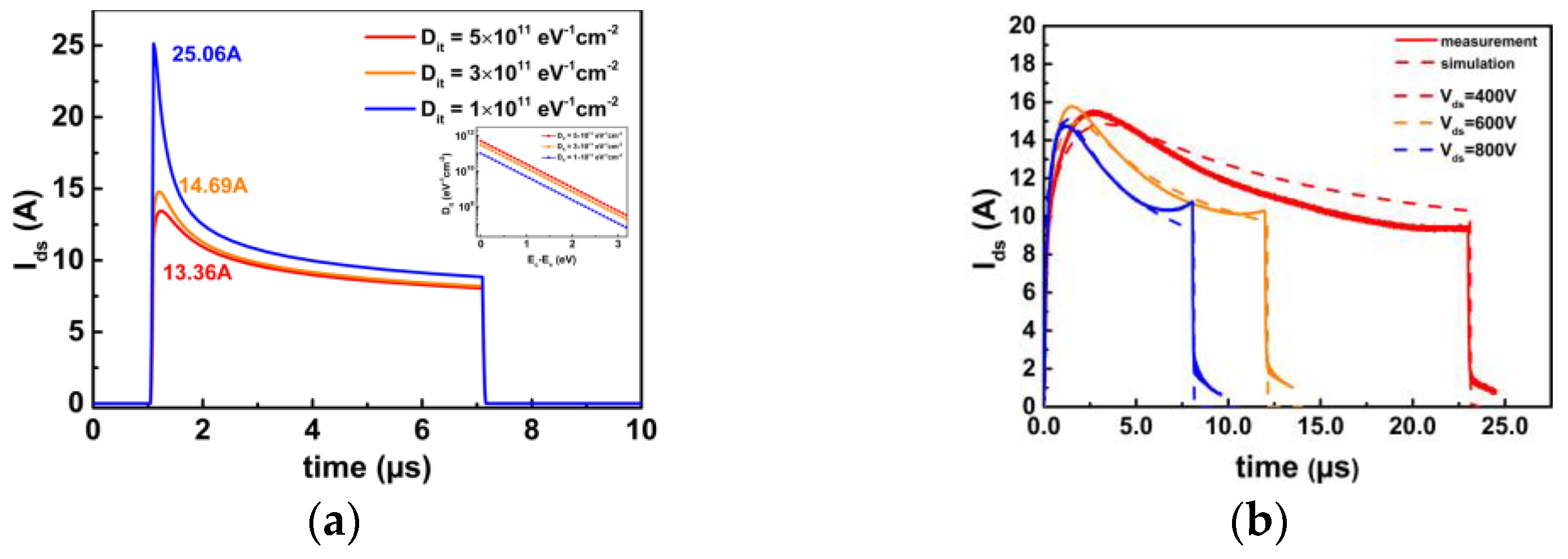

2.2. Short-Circuit Capability of SiC MOSFETs

3. Results

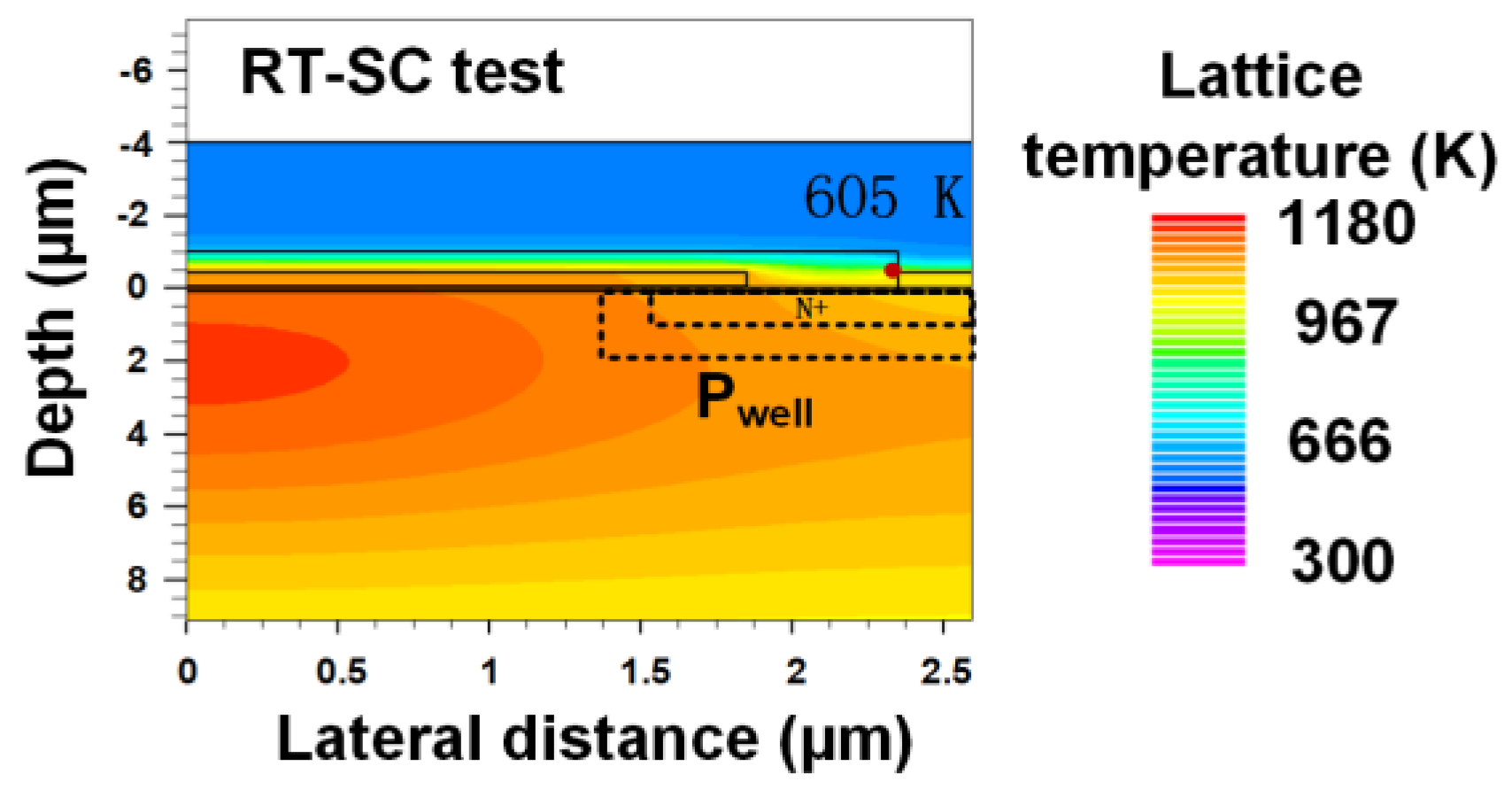

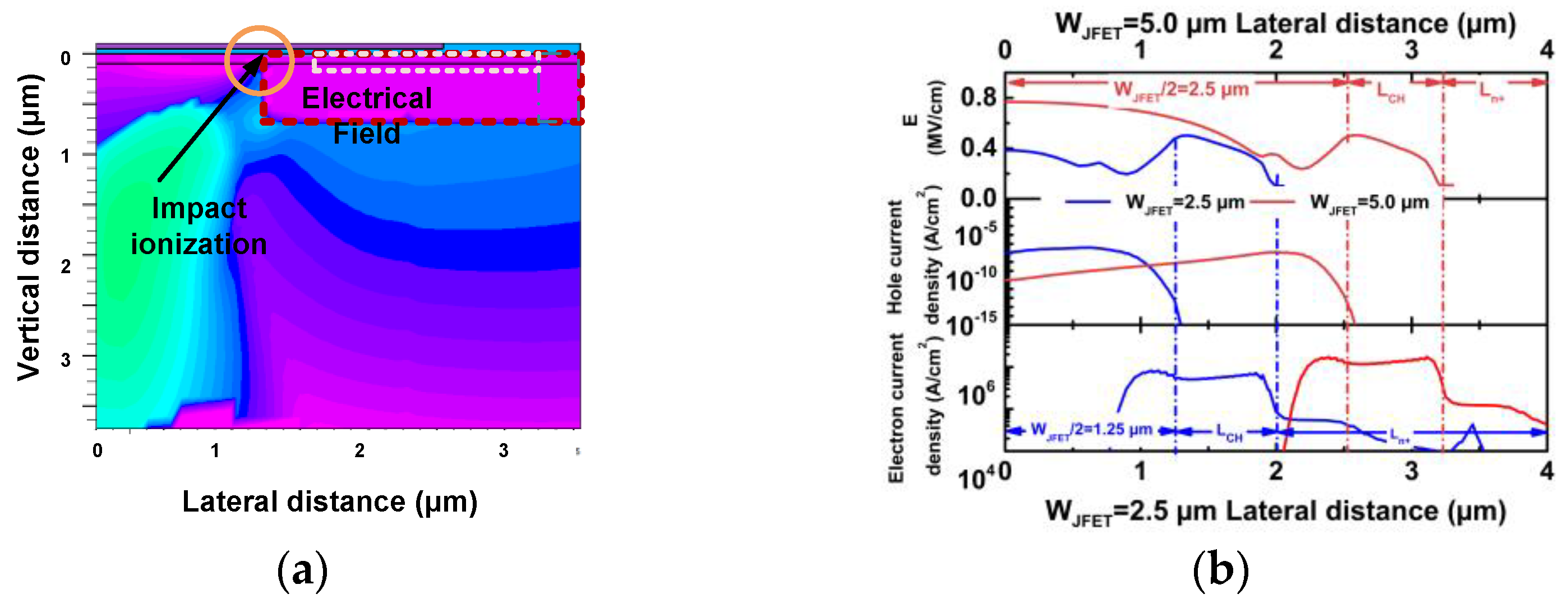

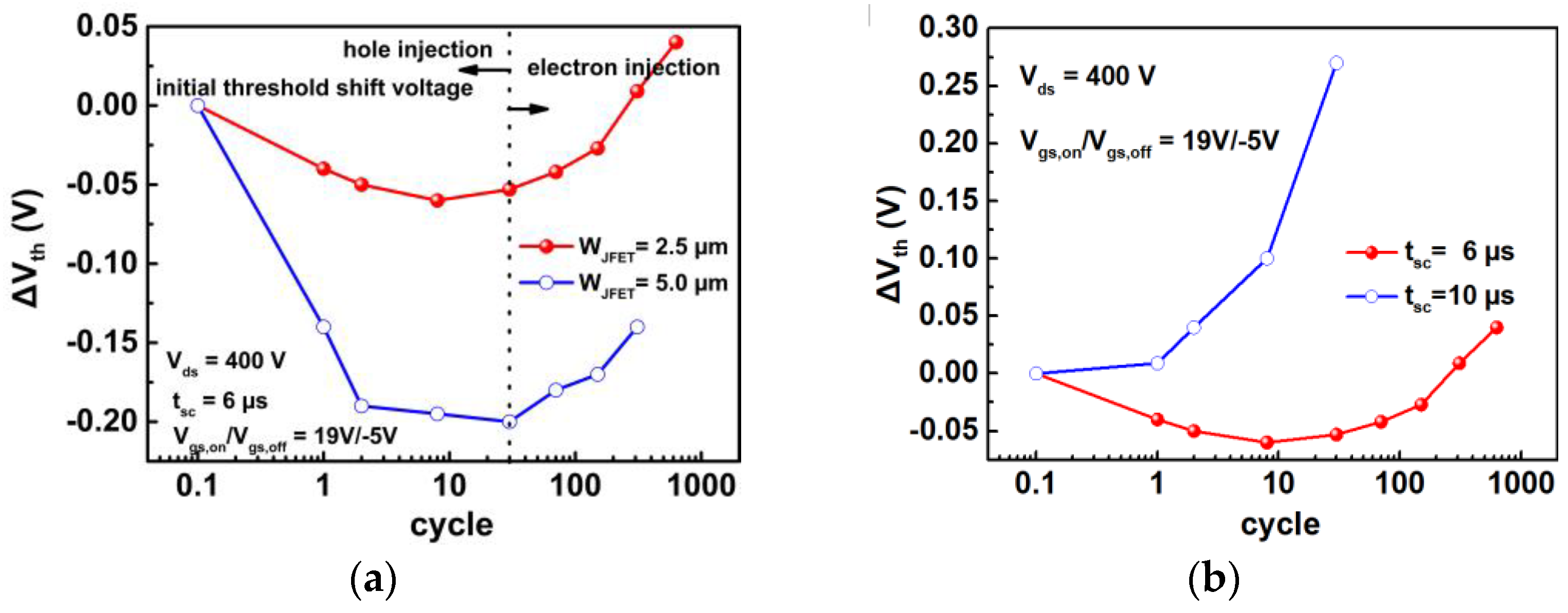

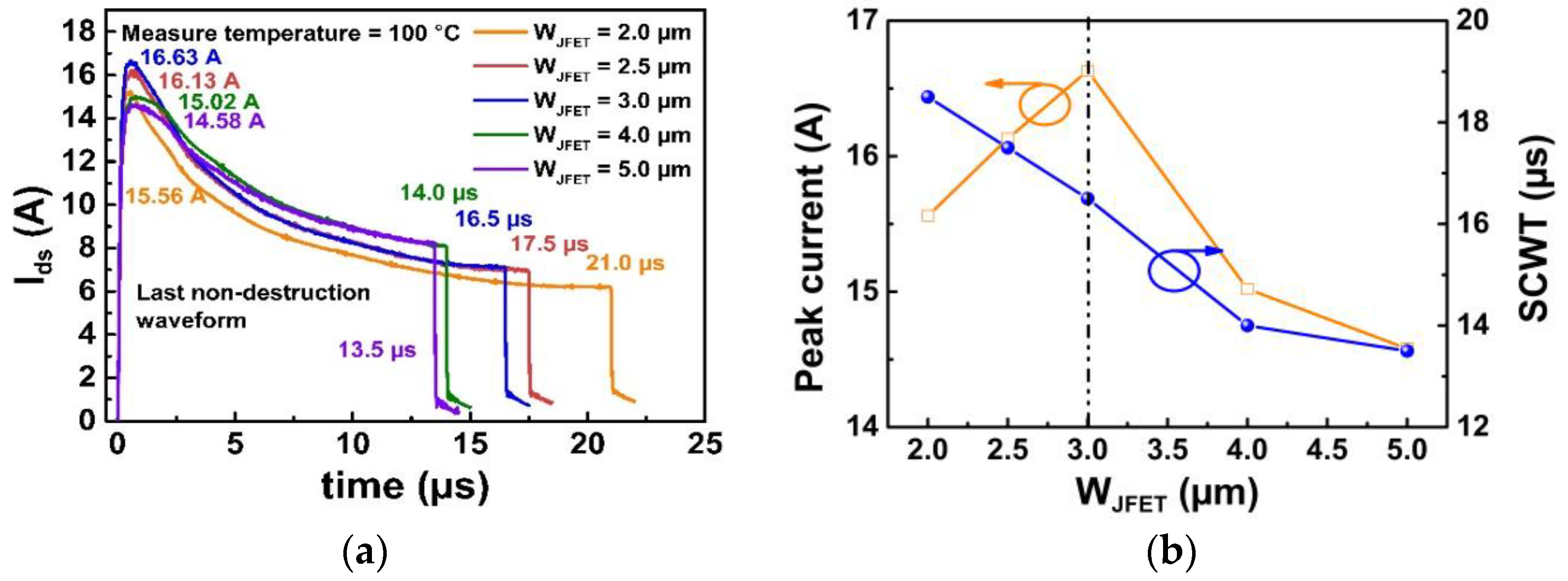

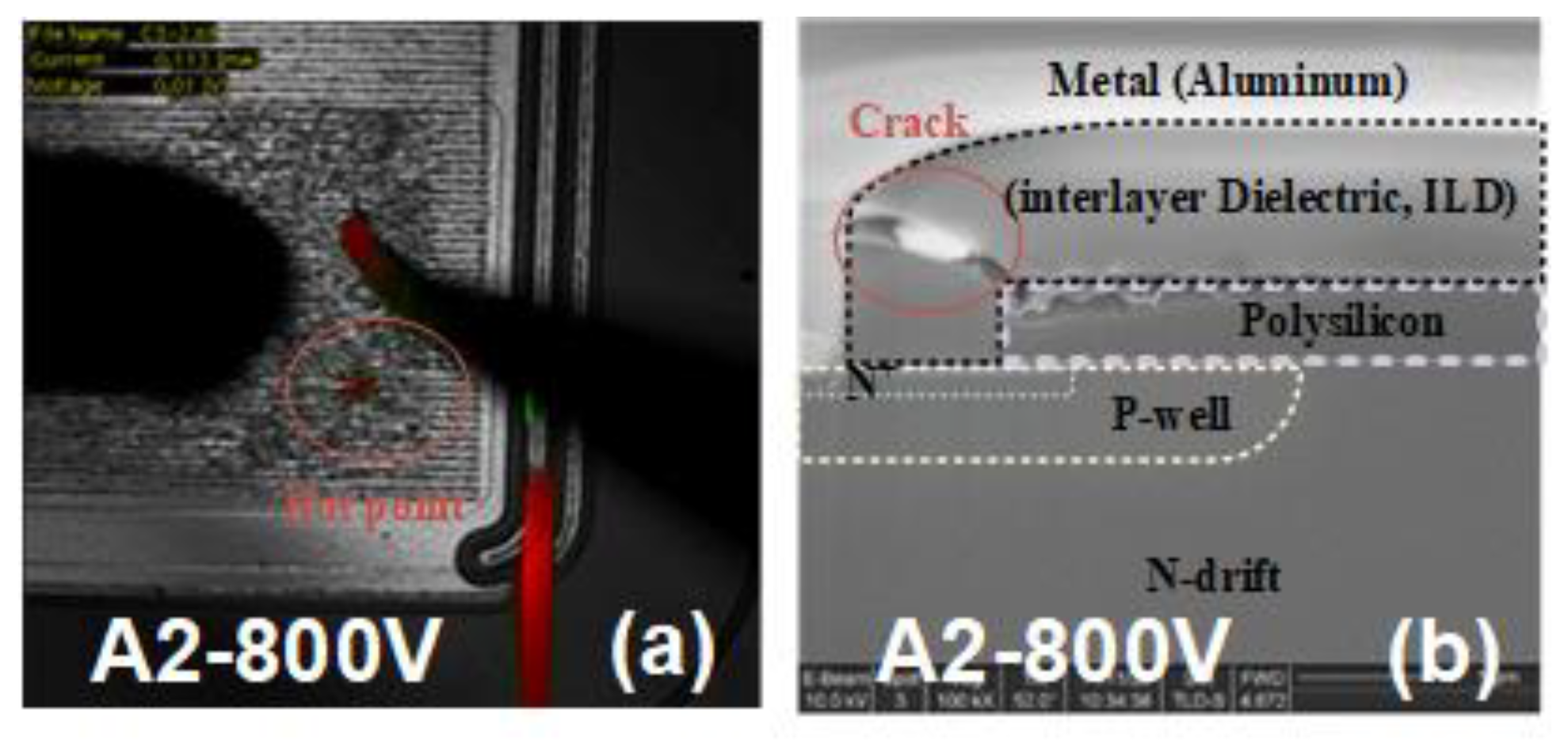

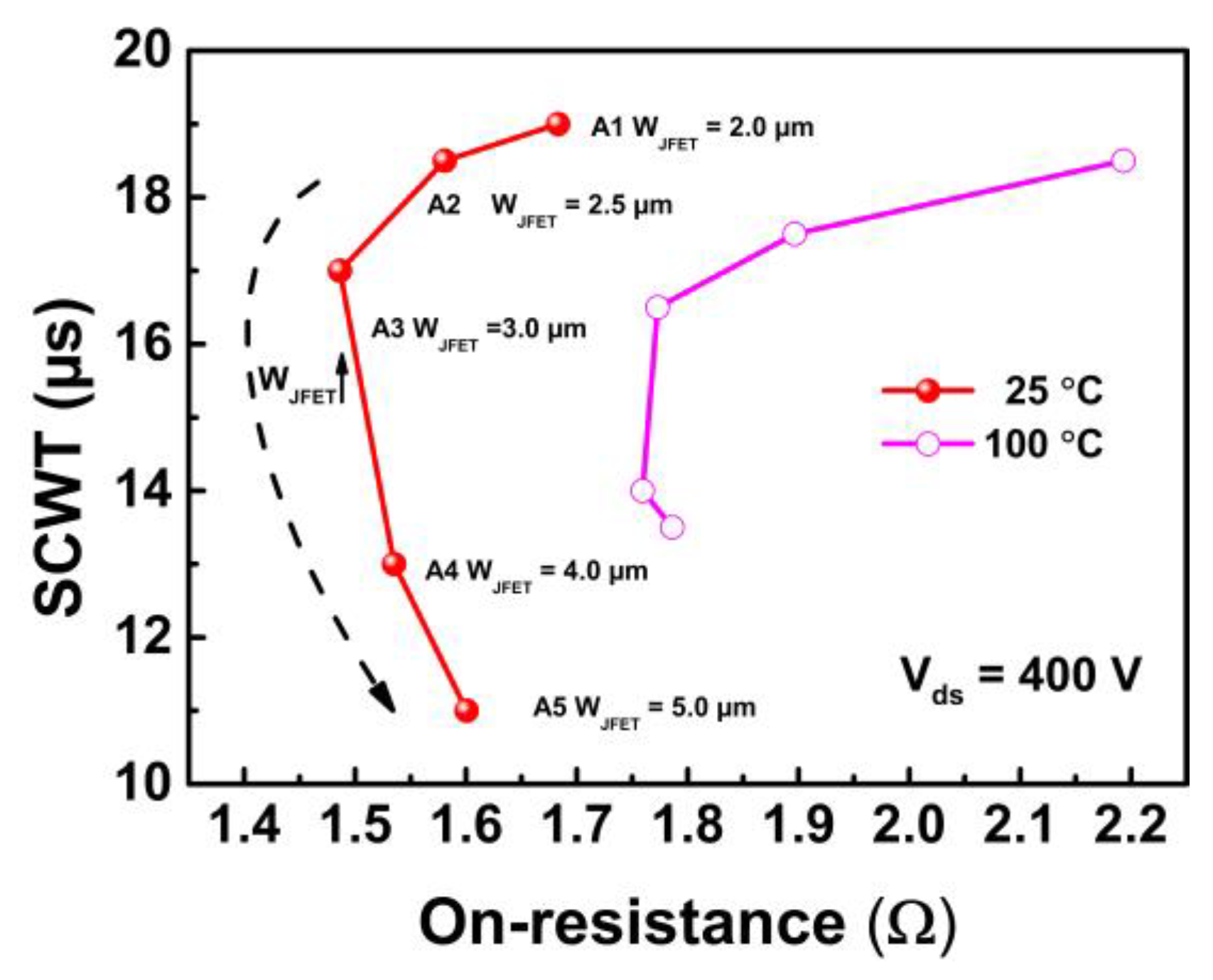

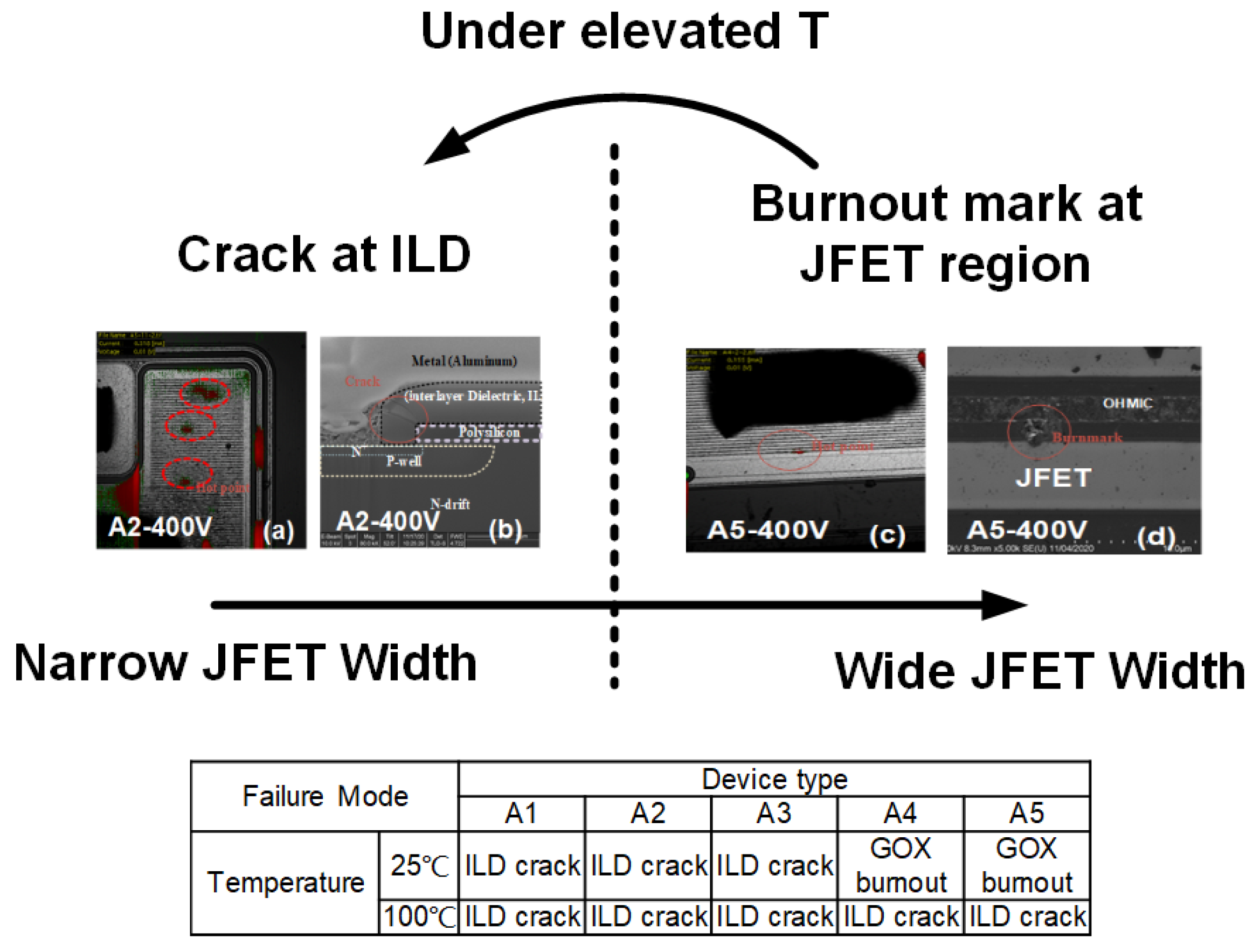

3.1. Short-Circuit Capability of SiC MOSFETs with Different JFET Widths at 400 V

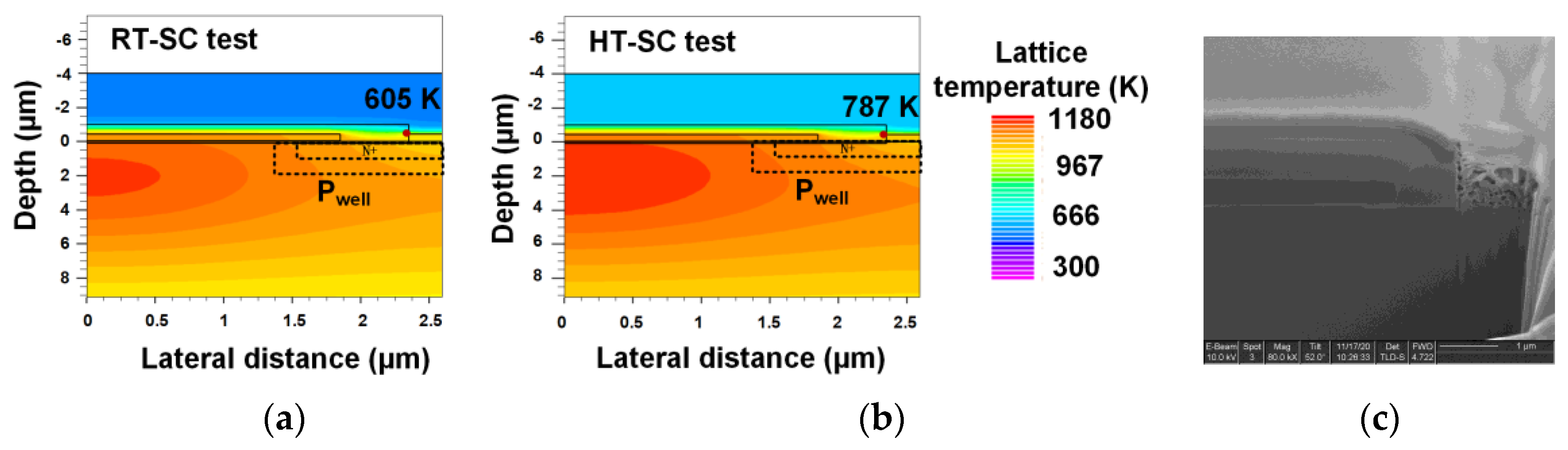

3.2. Short-Circuit Capability of SiC MOSFETs Measured at Elevated Temperature

3.3. Short-Circuit Capability of SiC MOSFETs with Different JFET Widths at Varied Vds Measured at Room Temperature

4. Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chen, Z.; Huang, A.Q. High Performance SiC Power Module Based on Repackaging of Discrete SiC Devices. IEEE Trans. Power Electron. 2023, 38, 9306–9310. [Google Scholar] [CrossRef]

- Fuchs, F. Some diagnosis methods for voltage source inverters in variable speed drives with induction machines a survey. In Proceedings of the IECON’03. 29th Annual Conference of the IEEE Industrial Electronics Society (IEEE Cat. No. 03CH37468), Roanoke, VA, USA, 2–6 November 2003. [Google Scholar] [CrossRef]

- Jiang, X.; Wang, J.; Lu, J.; Chen, J.; Yang, X.; Li, Z.; Tu, C.; Shen, Z.J. Failure modes and mechanism analysis of SiC MOSFET under short-circuit conditions. Microelectron. Reliab. 2018, 88–90, 593–597. [Google Scholar] [CrossRef]

- Wang, J.; Jiang, X.; Li, Z.; Shen, Z.J. Short-Circuit Ruggedness and Failure Mechanisms of Si/SiC Hybrid Switch. IEEE Trans. Power Electron. 2018, 34, 2771–2780. [Google Scholar] [CrossRef]

- Ahmed, M.T. Performance and Reliability Evaluation of SiC Power MOSFETs for Electric Vehicle Applications. IEEE Trans. Transp. Electrif. 2020, 6, 96–106. [Google Scholar]

- Kumar, A.; Losito, M.; Moradpour, M.; Gatto, G. Evaluation of Short-Circuit Capability of SiC MOSFET Power Modules. In Proceedings of the 2022 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), Sorrento, Italy, 22–24 June 2022; pp. 523–527. [Google Scholar] [CrossRef]

- Moradpour, M.; Pirino, P.; Losito, M.; Franke, W.-T.; Kumar, A.; Gatto, G. Multi-Objective Optimization of the Gate Driver Parameters in a SiC-Based DC-DC Converter for Electric Vehicles. Energies 2020, 13, 3720. [Google Scholar] [CrossRef]

- Zhang, S. Short-Circuit Failure Mechanism and Reliability Analysis of SiC MOSFETs. IEEE Trans. Device Mater. Reliab. 2022, 23, 581–589. [Google Scholar]

- Sun, J.; Yang, S.; Xu, H.; Zhang, L.; Wu, X.; Sheng, K.; Chen, K.J. High-Temperature Characterization of a 1.2-kV SiC MOSFET Using Dynamic Short-Circuit Measurement Technique. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 215–222. [Google Scholar] [CrossRef]

- Sun, J.; Wei, J.; Zheng, Z.; Wang, Y.; Chen, K.J. Short Circuit Capability and Short Circuit Induced VTH Instability of a 1.2-kV SiC Power MOSFET. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1539–1546. [Google Scholar] [CrossRef]

- Liu, J.; Zhang, G.; Wang, B.; Li, W.; Wang, J. Gate Failure Physics of SiC MOSFETs Under Short-Circuit Stress. IEEE Electron Device Lett. 2020, 41, 103–106. [Google Scholar] [CrossRef]

- Yao, K.; Yano, H.; Tadano, H.; Iwamuro, N. Investigations of SiC MOSFET Short-Circuit Failure Mechanisms Using Electrical, Thermal, and Mechanical Stress Analyses. IEEE Trans. Electron Devices 2020, 67, 4328–4334. [Google Scholar] [CrossRef]

- Agarwal, A.; Kanale, A.; Han, K.; Baliga, B.J.; Bhattacharya, S. Impact of Gate Oxide Thickness on Switching and Short Circuit Performance of 1200 V 4H-SiC Inversion-channel MOSFETs. In Proceedings of the 2019 IEEE 7th Workshop on Wide Bandgap Power De-vices and Applications (WiPDA), Raleigh, NC, USA, 29–31 October 2019; pp. 59–62. [Google Scholar] [CrossRef]

- Bencherif, H.; Dehimi, L.; Pezzimenti, F.; Yousfi, A.; De Martino, G.; Della Corte, F.G. Impact of a non-uniform p-base doping concentration on the electrical characteristics of a low power MOSFET in 4H-SiC. In Proceedings of the 2019 International Conference on Advanced Electrical Engineering (ICAEE), Algiers, Algeria, 19–21 November 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Chen, Y. Effect of Channel Structure on Short-Circuit Capability of SiC MOSFETs. IEEE Electron Device Lett. 2023, 44, 1166–1169. [Google Scholar]

- Zhang, M. Impact of Gate Structure on the Short-Circuit Performance of SiC MOSFETs. IEEE Trans. Electron Devices 2023, 70, 1380–1386. [Google Scholar]

- Romano, G.; Riccio, M.; Maresca, L.; Breglio, G.; Irace, A.; Fayyaz, A.; Castellazzi, A. Influence of design parameters on the short-circuit ruggedness of SiC power MOSFETs. In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 2–16 June 2016; pp. 47–50. [Google Scholar] [CrossRef]

- Tachiki, K.; Ono, T.; Kobayashi, T.; Tanaka, H.; Kimoto, T. Estimation of Threshold Voltage in SiC Short-Channel MOSFETs. IEEE Trans. Electron Devices 2018, 65, 3077–3080. [Google Scholar] [CrossRef]

- Baliga, B.J. Material properties and transport physics. In Fundamentals of Power Semiconductor Devices; Springer: Raleigh, NC, USA, 2008; pp. 23–28. [Google Scholar]

| Device | A1 | A2 | A3 | A4 | A5 |

|---|---|---|---|---|---|

| WJFET (μm) | 2.0 | 2.5 | 3.0 | 4.0 | 5.0 |

| Threshold Voltage (V) (Vd = 10 V, Vth @ Ids = 1 × 10−3 A) | 2.58 | 2.56 | 2.52 | 2.69 | 2.73 |

| On-resistance (Ω) | 1.68 | 1.58 | 1.48 | 1.53 | 1.60 |

| Transconductance (S) | 0.377 | 0.602 | 0.748 | 0.837 | 0.841 |

| Breakdown voltage (V) (Vds @ Ids = 1 × 10−6 A) | 1774 | 1725 | 1742 | 1706 | 1777 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, H.; Wang, B.; Ren, N.; Long, H.; Huang, K.; Sheng, K. Influence of JFET Width on Short-Circuit Robustness of 1200 V SiC Power MOSFETs. Electronics 2023, 12, 4849. https://doi.org/10.3390/electronics12234849

Xu H, Wang B, Ren N, Long H, Huang K, Sheng K. Influence of JFET Width on Short-Circuit Robustness of 1200 V SiC Power MOSFETs. Electronics. 2023; 12(23):4849. https://doi.org/10.3390/electronics12234849

Chicago/Turabian StyleXu, Hongyi, Baozhu Wang, Na Ren, Hu Long, Kai Huang, and Kuang Sheng. 2023. "Influence of JFET Width on Short-Circuit Robustness of 1200 V SiC Power MOSFETs" Electronics 12, no. 23: 4849. https://doi.org/10.3390/electronics12234849

APA StyleXu, H., Wang, B., Ren, N., Long, H., Huang, K., & Sheng, K. (2023). Influence of JFET Width on Short-Circuit Robustness of 1200 V SiC Power MOSFETs. Electronics, 12(23), 4849. https://doi.org/10.3390/electronics12234849