Impact of the Noise on the Emulated Grid Voltage Signal in Hardware-in-the-Loop Used in Power Converters

Abstract

:1. Introduction

2. Error Source Affecting a HIL

- Errors in the implementation of the model [19,20], such as the omission of specific physical effects in the model, such as losses, or the oversimplification of some aspects of the system [21], errors in the mathematical formulation of the model, or errors due to the chosen numerical format. Omitting certain physical effects can also affect accuracy. For example, if the model does not account for electrical resistance in a circuit, it can produce inaccurate results for the voltage drop in the circuit. On the other hand, errors in the mathematical formulation of the model may include errors in the definition of the equations or constants, which are used to describe the behavior of the system or mistakes in the implementation of these equations in the code.

- Errors measuring the input and output signals of the model [22], such as calibration, data acquisition, or sampling errors. If a poorly calibrated sensor is used to measure an input signal, it can produce an inaccurate input signal that affects model accuracy. Whereas, in the case of data acquisition, if a low sampling rate is used to capture all the variations in a signal, it can result in an inaccurate input or output signal affecting the accuracy of the model [23].

- Synchronization errors [26]. The latency between the model and the hardware can cause timing, communication, and test accuracy errors.

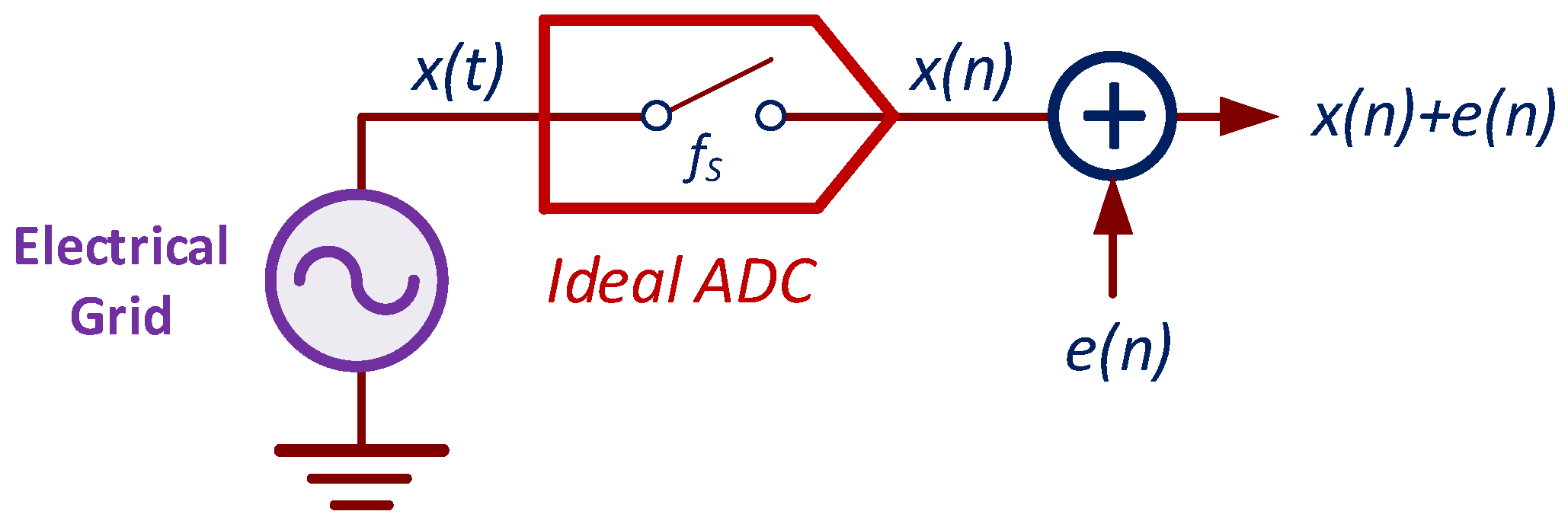

- Inaccurate or noisy input data [30]. Noise in an electrical signal is defined as an unwanted disturbance deviating from the signal, typically random. Its origins are diverse, but can be classified into noise inherent to the system and external noise, in this case, AC-input noise. The total inherent noise in an ADC is mainly due to uncorrelated quantization and thermal noises. Quantization noise is due to mapping the input signal to a finite set of digital codes, and oscillates at a known threshold, depending on two fundamental factors: the number of bits in the ADC and the input signal range. On the other hand, thermal noise is inherent in all electrical components because of the temperature effects on the physical movement of electrical charges. It is dependent on the ADC design and manufacturing processes. It typically exhibits a Gaussian distribution in the time domain, and it is broadband. The user cannot modify the ADC thermal noise. Furthermore, the predominance of one type of noise or another in the ADC depends on its resolution; thus, in a low-resolution ADC, quantization errors will predominate, while in a high-resolution ADC, thermal noise will predominate. In this sense, the ADC is not trivial [31,32]. Different types of ADC can be used in building a HIL. Although all of them can be affected by noise due to random jitter in the signal during digital conversion, each is affected by other types of noise based on its characteristics. So, for example, successive approximation register (SAR) ADCs tend to be more prone to sampling noise, and counter ADCs tend to be more prone to counter noise, while sigma-delta ADCs avoid these errors by using a modulation technique that allows high-frequency noise to be removed.

2.1. Noise in the Input Data Effects

- Signal distortion: Including noise in the signal can distort the latter, making it deviate from the ideal signal.

- Difficulty in interpreting the signal: The level of noise present can make it challenging to analyze the signal and obtain information from it, especially around zero values or in quasi-stationary conditions.

- Reduction of the signal to noise: If the noise signal is excessively high, the signal can be reduced to noise only, and practically useless for the system.

- Loss of information: Noise can hide valuable information in the signal. This unwanted phenomenon can negatively affect the precision, stability, and even processing time of the model used.

2.2. Measurement of the Noise Introduced in the Input Signals

- Noise sensors and/or meters [37]: These components or pieces of equipment measure the noise in the input signal of the HIL system.

- Sinewave-input and DC-input tests: The sinewave-input test assesses the performance of the ADC when faced with a known sinusoidal signal of a certain amplitude and frequency, in order to evaluate the manner in which the ADC converts the signal. The DC-input test measures the DC noise of the signal by using histograms [40,41], which are graphs that show the probability density function (PDF). Noise level measurements are acquired over a specific period. They are grouped in intervals and displayed in a bar graph to show the number of measurements falling within a specific range of noise levels, and to detect abnormal noise levels or patterns in the noise distribution. The histogram shows whether most of the noise is allocated in a specific frequency range, or distributed more uniformly throughout the intervals.

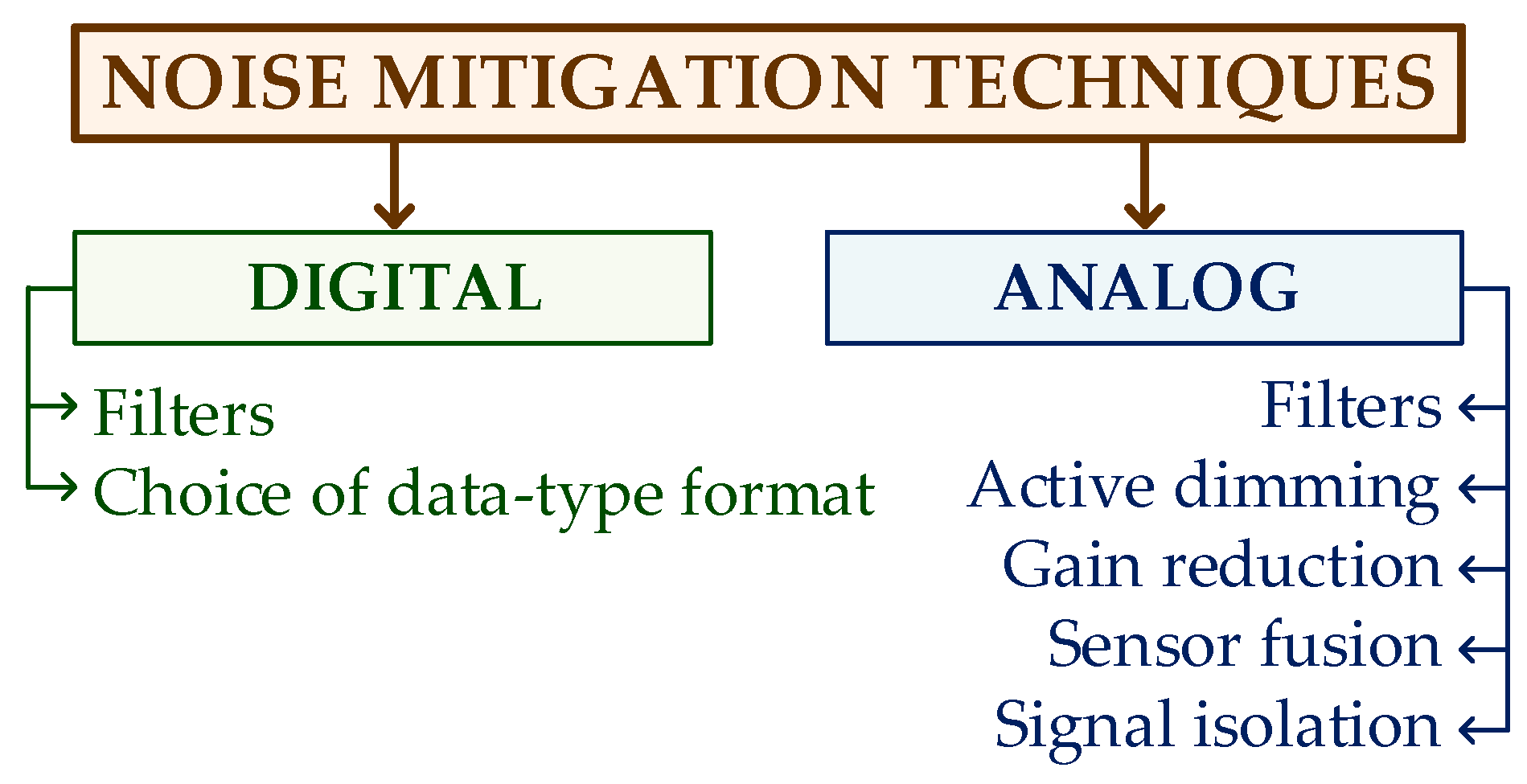

2.3. Noise Mitigation Techniques

- Filters [45]: Filters are circuits or algorithms that allow noise to be removed or attenuated from an input signal. The type of filter, moving average [46], interpolation [47], or downsampling, is selected upon the characteristics of the noise, the frequency of the input signal, and the disturbance.

- Choice of model data-type format [13]: Data-type format refers to how numbers are represented in a system. Although its design affects accuracy and therefore noise, it does not necessarily reduce it. However, it enables the definition of the system’s precision and simultaneously sets a range of allowed values. A good design reduces the rounding and truncation effects.

- Gain reduction [50]: The gain reduction technique decreases the amplification of the input signal to reduce signal noise.

- Sensor fusion [51]: This process combines data from several sensors to obtain a more accurate and complete representation of a specific variable or condition. The sensors do not need to be the same.

- Signal isolation: Signal isolation consists of isolating the input signal from external noise using techniques such as galvanic isolation or electrical isolation.

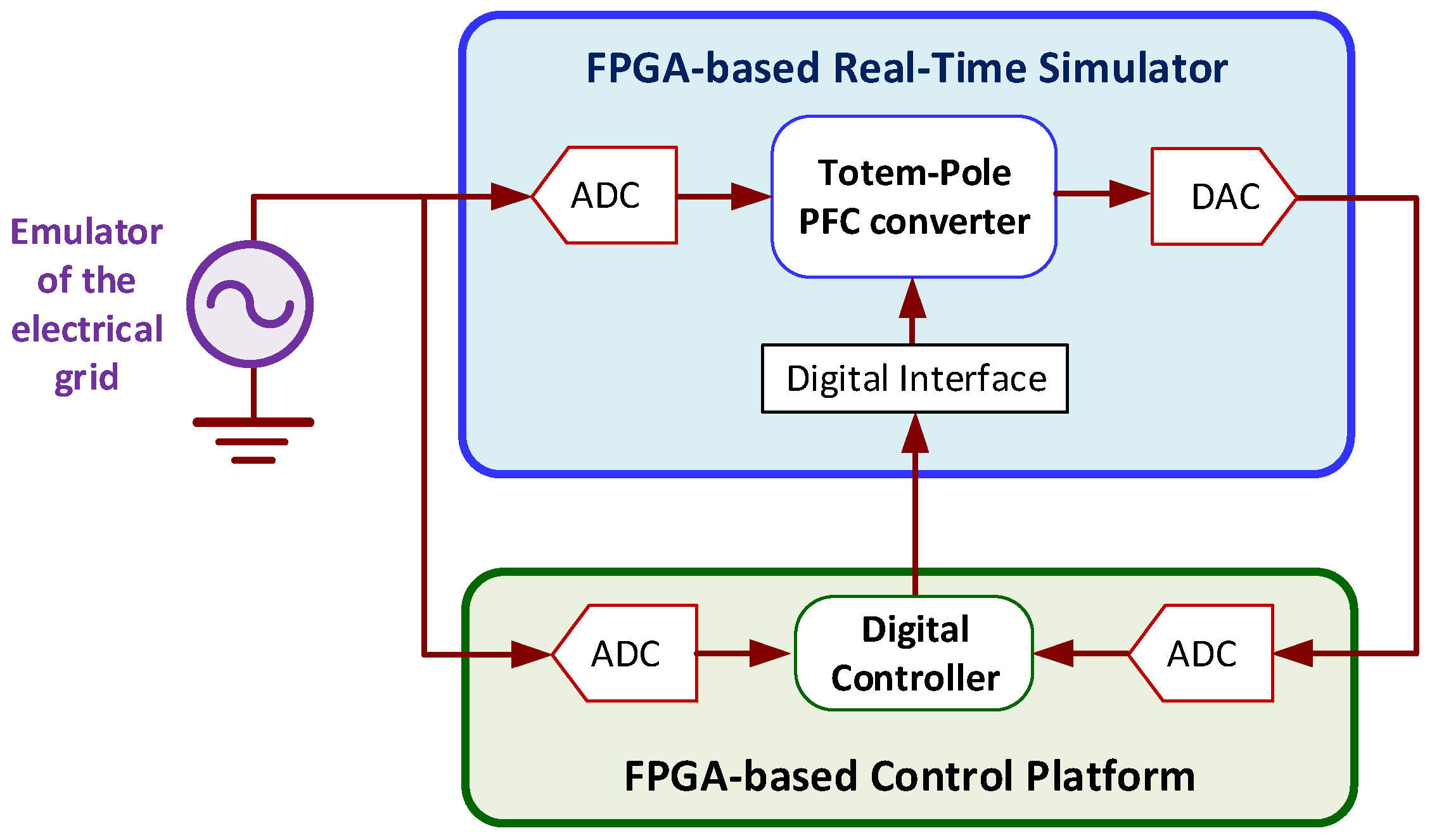

3. Case Study of Noise Implications

3.1. Characterization of the ADC Noise

3.2. Relevance of the Model Data-Type Format

3.3. Effects of Noise on the Mathematical Model and the Hardware Implementation

4. Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Bai, H.; Liu, C.; Breaz, E.; Al-Haddad, K.; Gao, F. A Review on the Device-Level Real-Time Simulation of Power Electronic Converters: Motivations for Improving Performance. IEEE Ind. Electron. Mag. 2021, 15, 12–27. [Google Scholar] [CrossRef]

- Zamiri, E.; Sanchez, A.; Martínez-García, M.S.; de Castro, A. Sub-Harmonic Oscillations Attenuation in Hardware-in-the-Loop Models Using the Integration Oversampling Method. Int. J. Electr. Power Energy Syst. 2023, 144, 108568. [Google Scholar] [CrossRef]

- Mihalič, F.; Truntič, M.; Hren, A. Hardware-in-the-Loop Simulations: A Historical Overview of Engineering Challenges. Electronics 2022, 11, 2462. [Google Scholar] [CrossRef]

- Dufour, C.; Bélanger, J. On the Use of Real-Time Simulation Technology in Smart Grid Research and Development. IEEE Trans. Ind. Appl. 2014, 50, 3963–3970. [Google Scholar] [CrossRef]

- Sámano-Ortega, V.; Méndez-Guzmán, H.M.-G.; Padilla-Medina, J.; Aguilera-álvarez, J.; Martínez-Nolasco, C.; Martínez-Nolasco, J. Control Hardware in the Loop and IoT Integration: A Testbed for Residential Photovoltaic System Evaluation. IEEE Access 2022, 10, 71814–71829. [Google Scholar] [CrossRef]

- Bruno, S.; Giannoccaro, G.; Iurlaro, C.; Scala, M.L.; Menga, M.; Rodio, C.; Sbrizzai, R. Fast Frequency Support Through LED Street Lighting in Small Non-Synchronous Power Systems. In IEEE Transactions on Industry Applications; IEEE: Piscataway Township, NJ, USA, 2022; pp. 1–11. [Google Scholar] [CrossRef]

- Sattar, A.; Al-Durra, A.; Caruana, C.; Debouza, M.; Muyeen, S.M. Testing the Performance of Battery Energy Storage in a Wind Energy Conversion System. IEEE Trans. Ind. Appl. 2020, 56, 3196–3206. [Google Scholar] [CrossRef]

- Saralegui, R.; Sanchez, A.; Martínez-García, M.S.; Novo, J.; de Castro, A. Comparison of Numerical Methods for Hardware-In-the-Loop Simulation of Switched-Mode Power Supplies. In Proceedings of the 2018 IEEE 19th Workshop on Control and Modeling for Power Electronics (COMPEL), Padua, Italy, 25–28 June 2018; pp. 1–6. [Google Scholar]

- Saralegui, R.; Sanchez, A.; de Castro, A. Modeling of Deadtime Events in Power Converters with Half-Bridge Modules for a Highly Accurate Hardware-in-the-Loop Fixed Point Implementation in FPGA. Appl. Sci. 2021, 11, 6490. [Google Scholar] [CrossRef]

- Zamiri, E.; Sanchez, A.; Martínez-García, M.S.; de Castro, A. Analysis of the Aliasing Effect Caused in Hardware-in-the-Loop When Reading PWM Inputs of Power Converters. Int. J. Electr. Power Energy Syst. 2022, 136, 107678. [Google Scholar] [CrossRef]

- Goñi, O.; Sanchez, A.; Todorovich, E.; Castro, A. de Resolution Analysis of Switching Converter Models for Hardware-in-the-Loop. IEEE Trans. Ind. Inform. 2014, 10, 1162–1170. [Google Scholar] [CrossRef] [Green Version]

- Zamiri, E.; Sanchez, A.; de Castro, A.; Martínez-García, M.S. Comparison of Power Converter Models with Losses for Hardware-in-the-Loop Using Different Numerical Formats. Electronics 2019, 8, 1255. [Google Scholar] [CrossRef]

- Cirugeda-Roldán, E.M.; Martínez-García, M.S.; Sanchez, A.; de Castro, A. Evaluation of the Different Numerical Formats for HIL Models of Power Converters after the Adoption of VHDL-2008 by Xilinx. Electronics 2021, 10, 1952. [Google Scholar] [CrossRef]

- Lin, N.; Dinavahi, V. Detailed Device-Level Electrothermal Modeling of the Proactive Hybrid HVDC Breaker for Real-Time Hardware-in-the-Loop Simulation of DC Grids. IEEE Trans. Power Electron. 2018, 33, 1118–1134. [Google Scholar] [CrossRef]

- Domanska, A. Evaluating the Measurement Uncertainty in an A/D Converter with Non Optimal Dither. In Proceedings of the 5th IEE International Conference on ADDA 2005. Advanced A/D and D/A Conversion Techniques and their Applications, Limerick, Ireland, 25–27 July 2005; pp. 331–334. [Google Scholar] [CrossRef]

- The ABCs of Analog to Digital Converters: How ADC Errors Affect System Performance|Analog Devices. Available online: https://www.analog.com/en/technical-articles/the-abcs-of-analog-to-digital-converters-how-adc-errors-affect-system-performance.html (accessed on 28 December 2022).

- Error Sources. Available online: https://training.ti.com/node/1139104 (accessed on 28 December 2022).

- ADC Noise. Available online: https://training.ti.com/adc-noise (accessed on 28 December 2022).

- Dai, X.; Ke, C.; Quan, Q.; Cai, K.-Y. Simulation Credibility Assessment Methodology With FPGA-Based Hardware-in-the-Loop Platform. IEEE Trans. Ind. Electron. 2021, 68, 3282–3291. [Google Scholar] [CrossRef]

- Chakraborty, S.; Mazuela, M.; Tran, D.-D.; Corea-Araujo, J.A.; Lan, Y.; Loiti, A.A.; Garmier, P.; Aizpuru, I.; Hegazy, O. Scalable Modeling Approach and Robust Hardware-in-the-Loop Testing of an Optimized Interleaved Bidirectional HV DC/DC Converter for Electric Vehicle Drivetrains. IEEE Access 2020, 8, 115515–115536. [Google Scholar] [CrossRef]

- Kim, M.; Kwak, S.-K.; Kim, K.A.; Jung, J.-H. Enhanced Computation Performance of Photovoltaic Models for Power Hardware-in-the-Loop Simulation. IEEE Trans. Ind. Electron. 2021, 68, 6952–6961. [Google Scholar] [CrossRef]

- Trinh, Q.N.; Wang, P.; Tang, Y.; Koh, L.H.; Choo, F.H. Compensation of DC Offset and Scaling Errors in Voltage and Current Measurements of Three-Phase AC/DC Converters. IEEE Trans. Power Electron. 2018, 33, 5401–5414. [Google Scholar] [CrossRef]

- Juárez-Abad, J.A.; Sandoval-García, A.P.; Linares-Flores, J.; Guerrero-Castellanos, J.F.; Bañuelos-Sánchez, P.; Contreras-Ordaz, M.A. FPGA Implementation of Passivity-Based Control and Output Load Algebraic Estimation for Transformerless Multilevel Active Rectifier. IEEE Trans. Ind. Inform. 2019, 15, 1877–1889. [Google Scholar] [CrossRef]

- Paim, G.; Amrouch, H.; Rocha, L.M.G.; Abreu, B.; César da Costa, E.A.; Bampi, S.; Henkel, J. A Framework for Crossing Temperature-Induced Timing Errors Underlying Hardware Accelerators to the Algorithm and Application Layers. IEEE Trans. Comput. 2022, 71, 349–363. [Google Scholar] [CrossRef]

- Duan, T.; Dinavahi, V. Adaptive Time-Stepping Universal Line and Machine Models for Real Time and Faster-Than-Real-Time Hardware Emulation. IEEE Trans. Ind. Electron. 2020, 67, 6173–6182. [Google Scholar] [CrossRef]

- Cale, J.L.; Johnson, B.B.; Dall’Anese, E.; Young, P.M.; Duggan, G.; Bedge, P.A.; Zimmerle, D.; Holton, L. Mitigating Communication Delays in Remotely Connected Hardware-in-the-Loop Experiments. IEEE Trans. Ind. Electron. 2018, 65, 9739–9748. [Google Scholar] [CrossRef]

- Peng, B.; Gu, N.; Wang, D.; Peng, Z. Model-Free Adaptive Disturbance Rejection Control of a Robotic Surface Vehicle With Hardware-in-The-Loop Experiments. In IEEE Transactions on Industrial Electronics; IEEE: Piscataway Township, NJ, USA, 2022; pp. 1–3. [Google Scholar] [CrossRef]

- Jin, H.; Liu, G.; Li, H.; Zhang, H. Closed-Loop Compensation Strategy of Commutation Error for Sensorless Brushless DC Motors With Nonideal Asymmetric Back-EMFs. IEEE Trans. Power Electron. 2021, 36, 11835–11846. [Google Scholar] [CrossRef]

- Guo, S.; Wang, Y.; Liu, R.; Gao, Y. Multi-Dimensional and Complicated Electromagnetic Interference Hardware-in-the-Loop Simulation Method. J. Syst. Eng. Electron. 2015, 26, 1142–1148. [Google Scholar] [CrossRef]

- Ren, W.; Steurer, M.; Baldwin, T.L. An Effective Method for Evaluating the Accuracy of Power Hardware-in-the-Loop Simulations. IEEE Trans. Ind. Appl. 2009, 45, 1484–1490. [Google Scholar] [CrossRef]

- Beev, N. Analog-to-Digital Conversion beyond 20 Bits. In Proceedings of the 2018 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Houston, TX, USA, 14–17 May 2018; pp. 1–6. [Google Scholar]

- Lizon, B. Fundamentals of Precision ADC Noise Analysis; Texas Instruments: Dallas, TX, USA, 2020. [Google Scholar]

- Wang, Q.; Ju, B.; Lei, Y.; Zhou, D.; Yin, S.; Li, D. Design and Hardware-in-the-Loop Validation: A Fractional Full Feed-Forward Method of Grid Voltage in LCL Grid-Connected Inverter System. In CSEE Journal of Power and Energy Systems; CSEE: Beijing, China, 2022; pp. 1–12. [Google Scholar] [CrossRef]

- Kardan, M.A.; Asemani, M.H.; Khayatian, A.; Vafamand, N.; Khooban, M.H.; Dragičević, T.; Blaabjerg, F. Improved Stabilization of Nonlinear DC Microgrids: Cubature Kalman Filter Approach. IEEE Trans. Ind. Appl. 2018, 54, 5104–5112. [Google Scholar] [CrossRef]

- Midya, P.; Krein, P.T. Noise Properties of Pulse-Width Modulated Power Converters: Open-Loop Effects. IEEE Trans. Power Electron 2000, 15, 1134–1143. [Google Scholar] [CrossRef]

- Sepehr, A.; Gomis-Bellmunt, O.; Pouresmaeil, E. Employing Machine Learning for Enhancing Transient Stability of Power Synchronization Control During Fault Conditions in Weak Grids. IEEE Trans. Smart Grid 2022, 13, 2121–2131. [Google Scholar] [CrossRef]

- Lauss, G.; Feng, Z.; Syed, M.H.; Kontou, A.; Paola, A.D.; Paspatis, A.; Kotsampopoulos, P. A Framework for Sensitivity Analysis of Real-Time Power Hardware-in-the-Loop (PHIL) Systems. IEEE Access 2022, 10, 101305–101318. [Google Scholar] [CrossRef]

- Maeda, T.; Tokairin, T. Analytical Expression of Quantization Noise in Time-to-Digital Converter Based on the Fourier Series Analysis. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 1538–1548. [Google Scholar] [CrossRef]

- Alam, A.; Mukul, M.K.; Thakura, P. Wavelet Transform-Based EMI Noise Mitigation in Power Converter Topologies. IEEE Trans. Electromagn. Compat. 2016, 58, 1662–1673. [Google Scholar] [CrossRef]

- Using Histogram Techniques to Measure A/D Converter Noise|Analog Devices. Available online: https://www.analog.com/en/analog-dialogue/articles/histogram-techniques-measure-adc-noise.html (accessed on 21 December 2022).

- Carbone, P.; Petri, D. Noise Sensitivity of the ADC Histogram Test. IEEE Trans. Instrum. Meas. 1998, 47, 1001–1004. [Google Scholar] [CrossRef]

- Lamo, P.; de Castro, A.; Sanchez, A.; Ruiz, G.A.; Azcondo, F.J.; Pigazo, A. Hardware-in-the-Loop and Digital Control Techniques Applied to Single-Phase PFC Converters. Electronics 2021, 10, 1563. [Google Scholar] [CrossRef]

- Dwiza, B.; Kalaiselvi, J. Analytical Approach for Common Mode EMI Noise Analysis in Dual Active Bridge Converter. In Proceedings of the IECON 2020 The 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 18–21 October 2020; pp. 1279–1284. [Google Scholar]

- Lamo, P.; Azcondo, F.J.; Pigazo, A. Academic Use of Rapid Prototyping in Digitally Controlled Power Factor Correctors. Electronics 2022, 11, 3600. [Google Scholar] [CrossRef]

- Lokin, C.E.; Schinkel, D.; Van Der Zee, R.A.R.; Nauta, B. Compensating Processing Delay in Excess of One Clock Cycle in Noise Shaping Loops Without Altering the Filter Topology. IEEE Access 2021, 9, 108101–108111. [Google Scholar] [CrossRef]

- Lu, S.; Chon, K.H. Nonlinear Autoregressive and Nonlinear Autoregressive Moving Average Model Parameter Estimation by Minimizing Hypersurface Distance. IEEE Trans. Signal Process. 2003, 51, 3020–3026. [Google Scholar] [CrossRef]

- Nguyen, T.-T.; Cheng, C.-H.; Liu, D.-G.; Le, M.-H. A Fast Cross-Correlation Combined with Interpolation Algorithms for the LiDAR Working in the High Background Noise. Electronics 2022, 11, 985. [Google Scholar] [CrossRef]

- Ren, W.; Steurer, M.; Baldwin, T.L. Improve the Stability and the Accuracy of Power Hardware-in-the-Loop Simulation by Selecting Appropriate Interface Algorithms. IEEE Trans. Ind. Appl. 2008, 44, 1286–1294. [Google Scholar] [CrossRef]

- Böhler, J.; Huber, J.; Wurz, J.; Stransky, M.; Uvaidov, N.; Srdic, S.; Kolar, J.W. Ultra-High-Bandwidth Power Amplifiers: A Technology Overview and Future Prospects. IEEE Access 2022, 10, 54613–54633. [Google Scholar] [CrossRef]

- Sharpin, D.L.; Tsui, J.B.Y. Analysis of the Linear Amplifier/Analog-Digital Converter Interface in a Digital Microwave Receiver. IEEE Trans. Aerosp. Electron. Syst. 1995, 31, 248–256. [Google Scholar] [CrossRef]

- Ayoubi, R.; Kaboli, S. A Robust Short-Circuit Fault Diagnosis for High Voltage DC Power Supply Based on Multisensor Data Fusion. In Proceedings of the 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), Iran, Islamic Republic, 12–14 February 2019; pp. 659–664. [Google Scholar]

- Ashrafidehkordi, F.; De Carne, G. Improved Accuracy of the Power Hardware-in-the-Loop Modeling Using Multirate Discrete Domain. In Proceedings of the 2022 IEEE 13th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Kiel, Germany, 26–29 June 2022; pp. 1–5. [Google Scholar]

- Zhang, Z.; Fickert, L.; Zhang, Y. Power Hardware-in-the-Loop Test for Cyber Physical Renewable Energy Infeed: Retroactive Effects and an Optimized Power Hardware-in-the-Loop Interface Algorithm. In Proceedings of the 17th International Scientific Conference on Electric Power Engineering (EPE), Prague, Czech Republic, 16–18 May 2016; pp. 1–6. [Google Scholar]

- Lamo, P.; Azcondo, F.J.; Pigazo, A. Improved Noise Immunity for Two-Sample PLL Applicable to Single-Phase PFCs. In Proceedings of the 2021 IEEE 22nd Workshop on Control and Modelling of Power Electronics (COMPEL), online, 2–5 November 2021; pp. 1–6. [Google Scholar]

- Oppenheim, A.V.; Schafer, R.W. Digital Signal Processing; Prentice-Hall: Hoboken, NJ, USA, 1975. [Google Scholar]

- Martínez-García, M.S.; de Castro, A.; Sanchez, A.; Garrido, J. Analysis of Resolution in Feedback Signals for Hardware-in-the-Loop Models of Power Converters. Electronics 2019, 8, 1527. [Google Scholar] [CrossRef]

- Smith, L.M.; Bormar, B.W.; Joseph, R.D.; Yang, G.C.-J. Floating-Point Roundoff Noise Analysis of Second-Order State-Space Digital Filter Structures. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 1992, 39, 90–98. [Google Scholar] [CrossRef]

- Bomar, B.W.; Smith, L.M.; Joseph, R.D. Roundoff Noise Analysis of State-Space Digital Filters Implemented on Floating-Point Digital Signal Processors. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 1997, 44, 952–955. [Google Scholar] [CrossRef]

- Gaffar, A.A.; Mencer, O.; Luk, W. Unifying Bit-Width Optimisation for Fixed-Point and Floating-Point Designs. In Proceedings of the 12th Annual IEEE Symposium on Field-Programmable Custom Computing Machines, Napa, CA, USA, 20–23 April 2004; pp. 79–88. [Google Scholar]

- Wadekar, S.A.; Parker, A.C. Accuracy Sensitive Word-Length Selection for Algorithm Optimization. In Proceedings of the International Conference on Computer Design. VLSI in Computers and Processors (Cat. No.98CB36273), Austin, TX, USA, 5–7 October 1998; pp. 54–61. [Google Scholar]

- Barnes, C.; Tran, B.; Leung, S. On the Statistics of Fixed-Point Roundoff Error. IEEE Trans. Acoust. Speech Signal Process. 1985, 33, 595–606. [Google Scholar] [CrossRef]

- Nehmeh, R. Quality Evaluation in Fixed-Point Systems with Selective Simulation. Ph.D. Thesis, Loire Bretagne University, Rennes, France, 2017. [Google Scholar]

| Data Type | Standard Deviation (σ) | FPGA Implementation | ||||

|---|---|---|---|---|---|---|

| iL (mA) | v0(mV) | DSP | FF | LUT | Latency | |

| Float (32-bits) | 28.2 | 194.1 | 10 | 851 | 1313 | 3 |

| Fixed point (32-bits) | 8.0 | 106.9 | 8 | 214 | 5552 | 1 |

| Fixed point (28-bits) | 8.3 | 106.9 | 7 | 190 | 6292 | 1 |

| Fixed point (24-bits) | 50.5 | 189.9 | 4 | 205 | 5917 | 1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lamo, P.; Ruiz, G.A.; Azcondo, F.J.; Pigazo, A.; Brañas, C. Impact of the Noise on the Emulated Grid Voltage Signal in Hardware-in-the-Loop Used in Power Converters. Electronics 2023, 12, 787. https://doi.org/10.3390/electronics12040787

Lamo P, Ruiz GA, Azcondo FJ, Pigazo A, Brañas C. Impact of the Noise on the Emulated Grid Voltage Signal in Hardware-in-the-Loop Used in Power Converters. Electronics. 2023; 12(4):787. https://doi.org/10.3390/electronics12040787

Chicago/Turabian StyleLamo, Paula, Gustavo A. Ruiz, Francisco J. Azcondo, Alberto Pigazo, and Christian Brañas. 2023. "Impact of the Noise on the Emulated Grid Voltage Signal in Hardware-in-the-Loop Used in Power Converters" Electronics 12, no. 4: 787. https://doi.org/10.3390/electronics12040787

APA StyleLamo, P., Ruiz, G. A., Azcondo, F. J., Pigazo, A., & Brañas, C. (2023). Impact of the Noise on the Emulated Grid Voltage Signal in Hardware-in-the-Loop Used in Power Converters. Electronics, 12(4), 787. https://doi.org/10.3390/electronics12040787