A Simple Scan Driver Circuit Suitable for Depletion-Mode Metal-Oxide Thin-Film Transistors in Active-Matrix Displays

Abstract

:1. Introduction

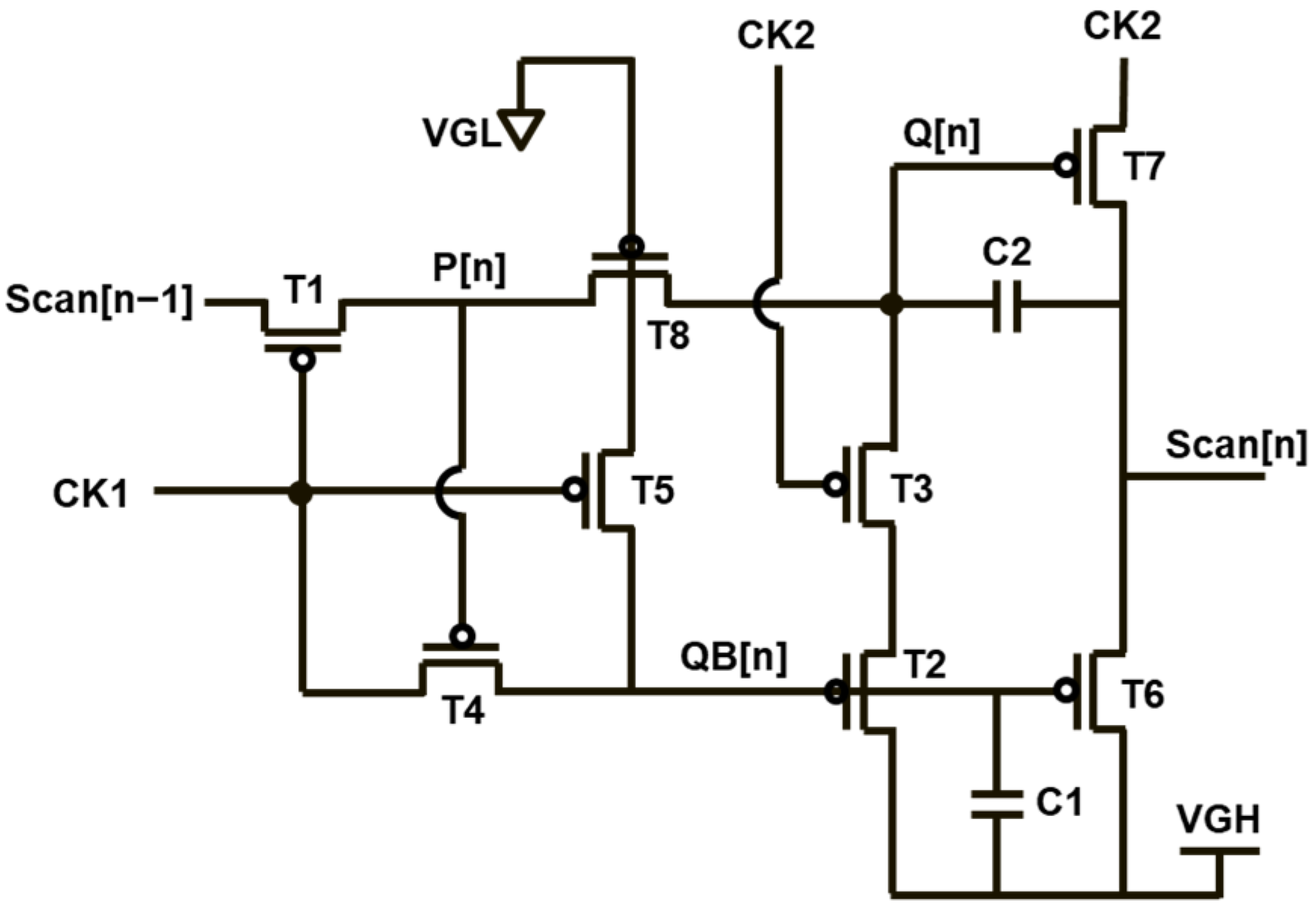

2. Conventional Scan Driver Circuit

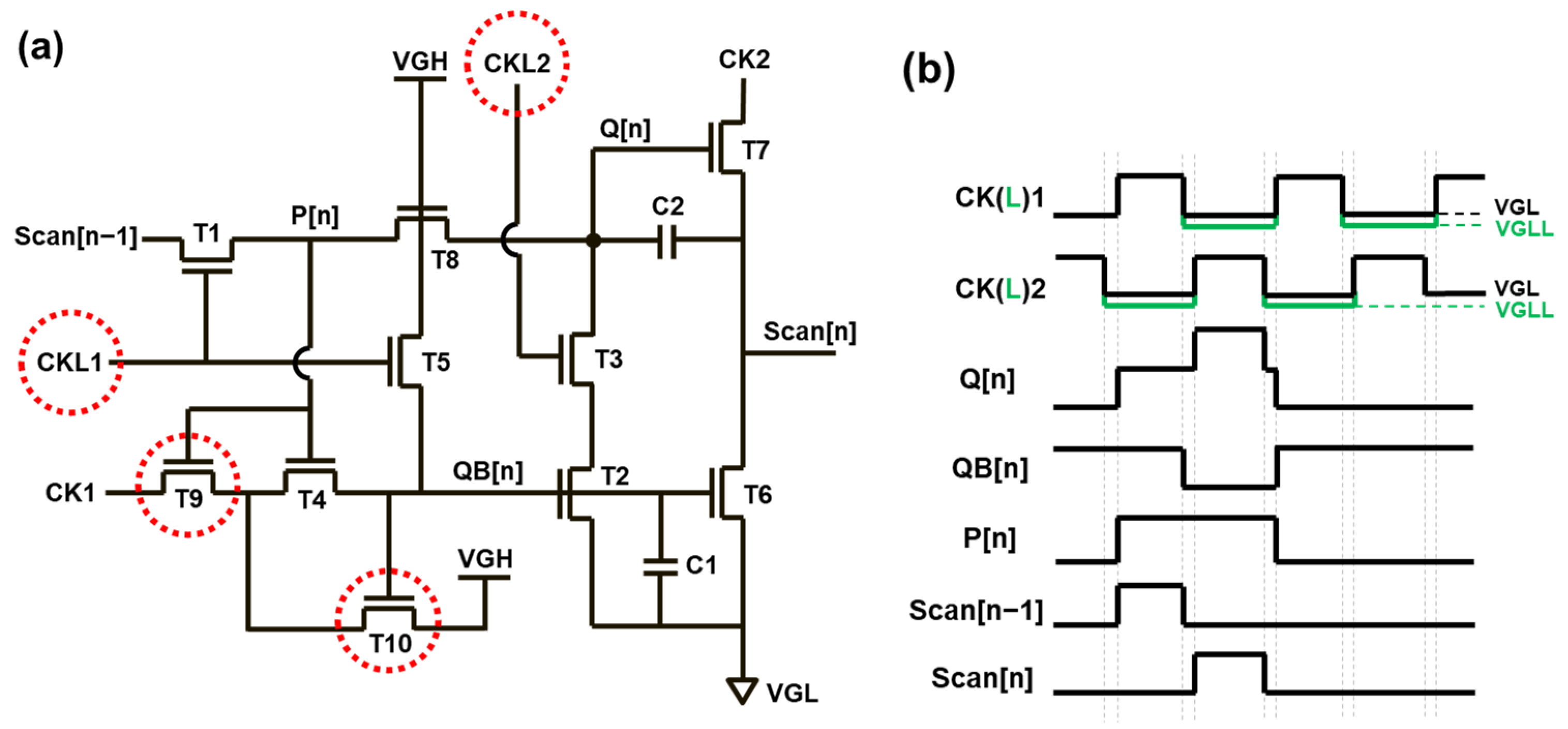

3. Proposed Scan Driver Circuit

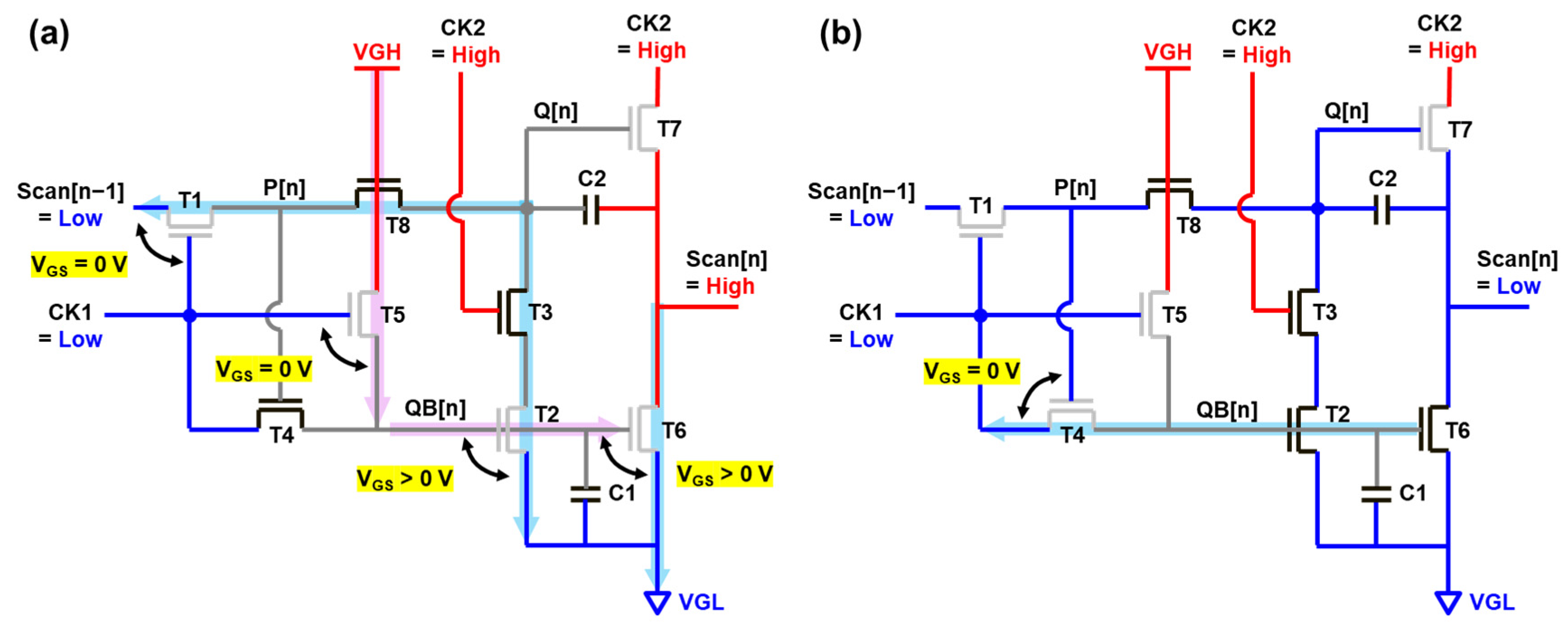

3.1. Pre-Charging

3.2. Output Pull-Up and Pull-Down

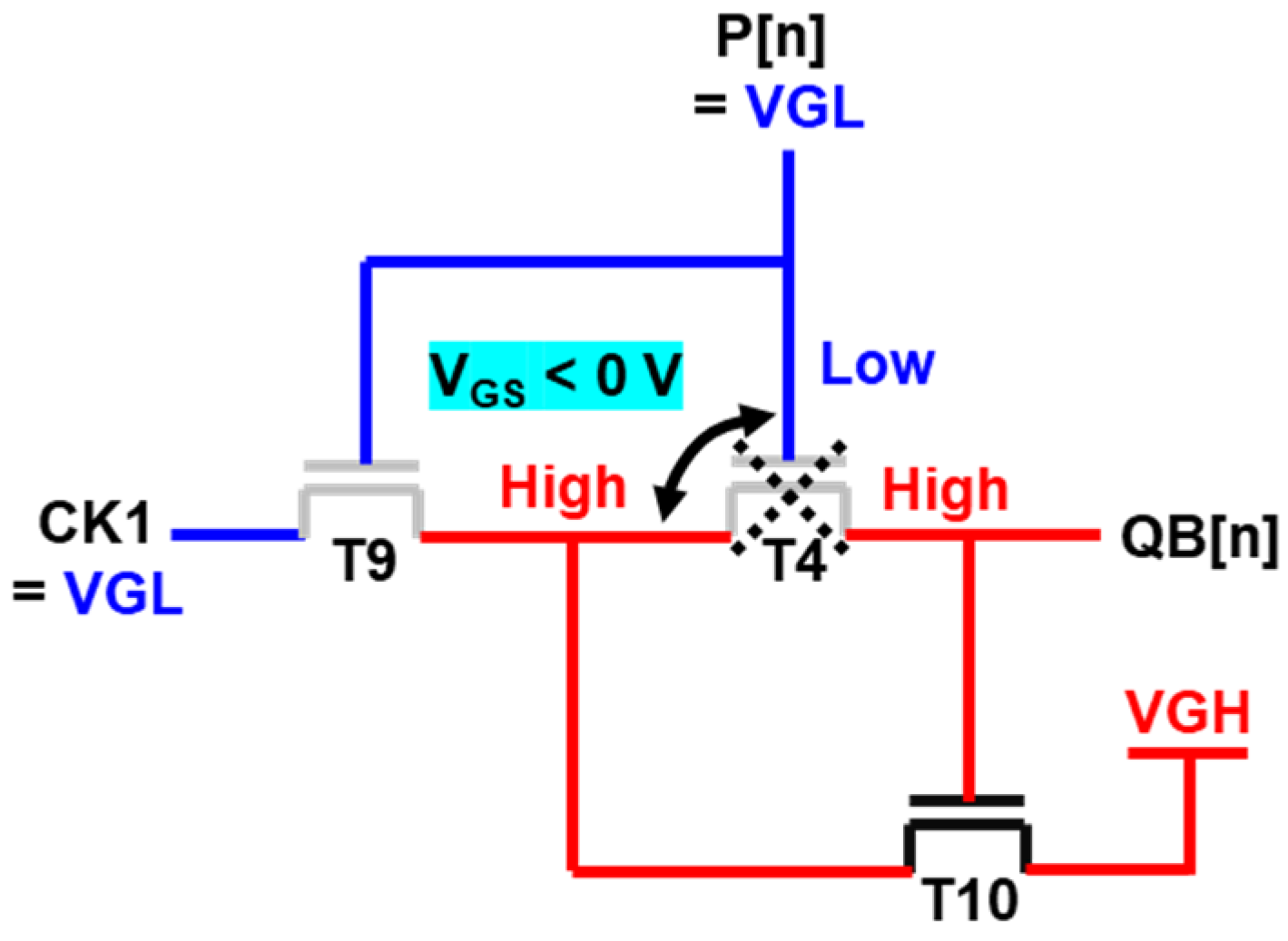

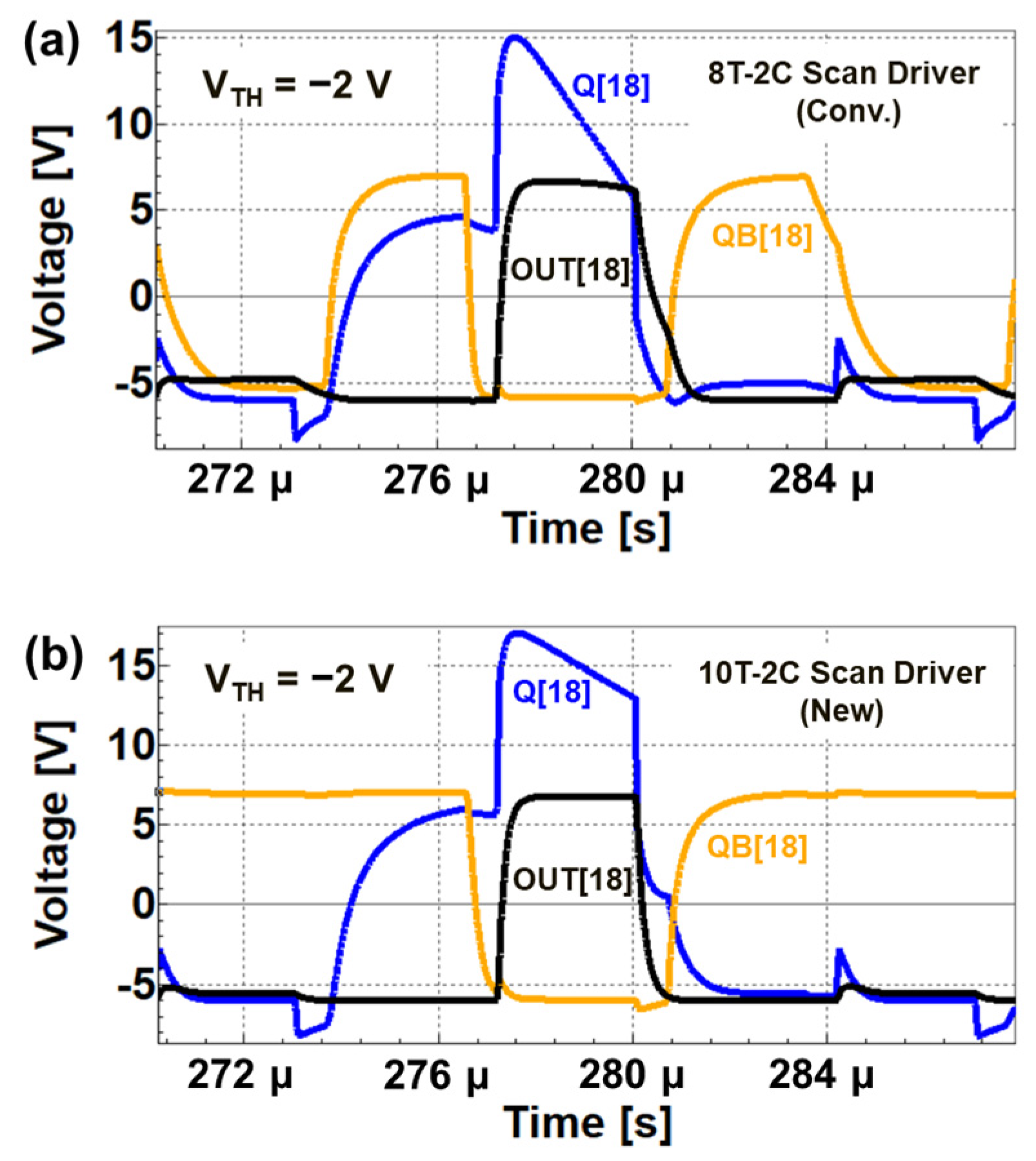

3.3. Output Hold-Down

4. Results and Discussions

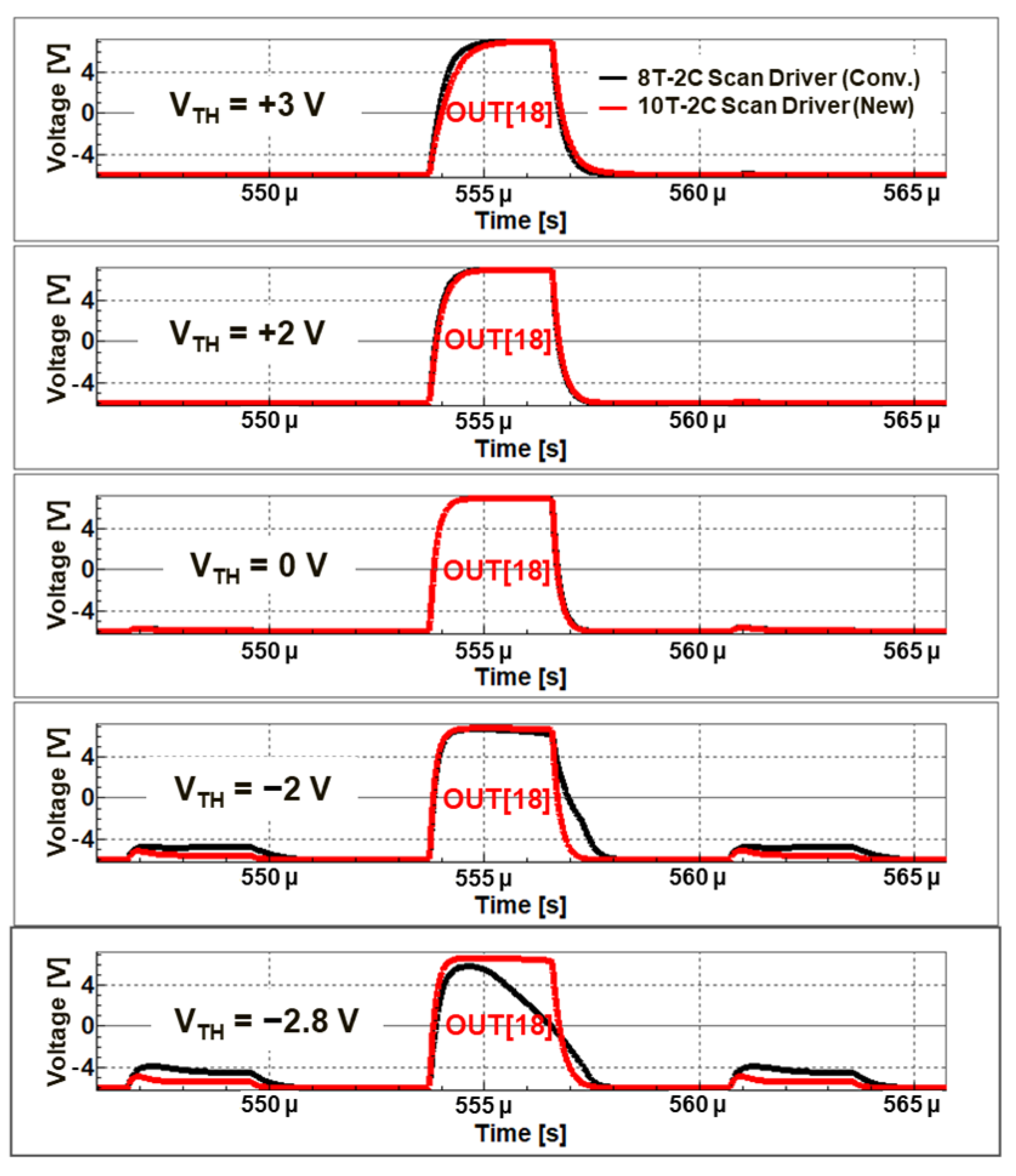

4.1. SPICE Simulation

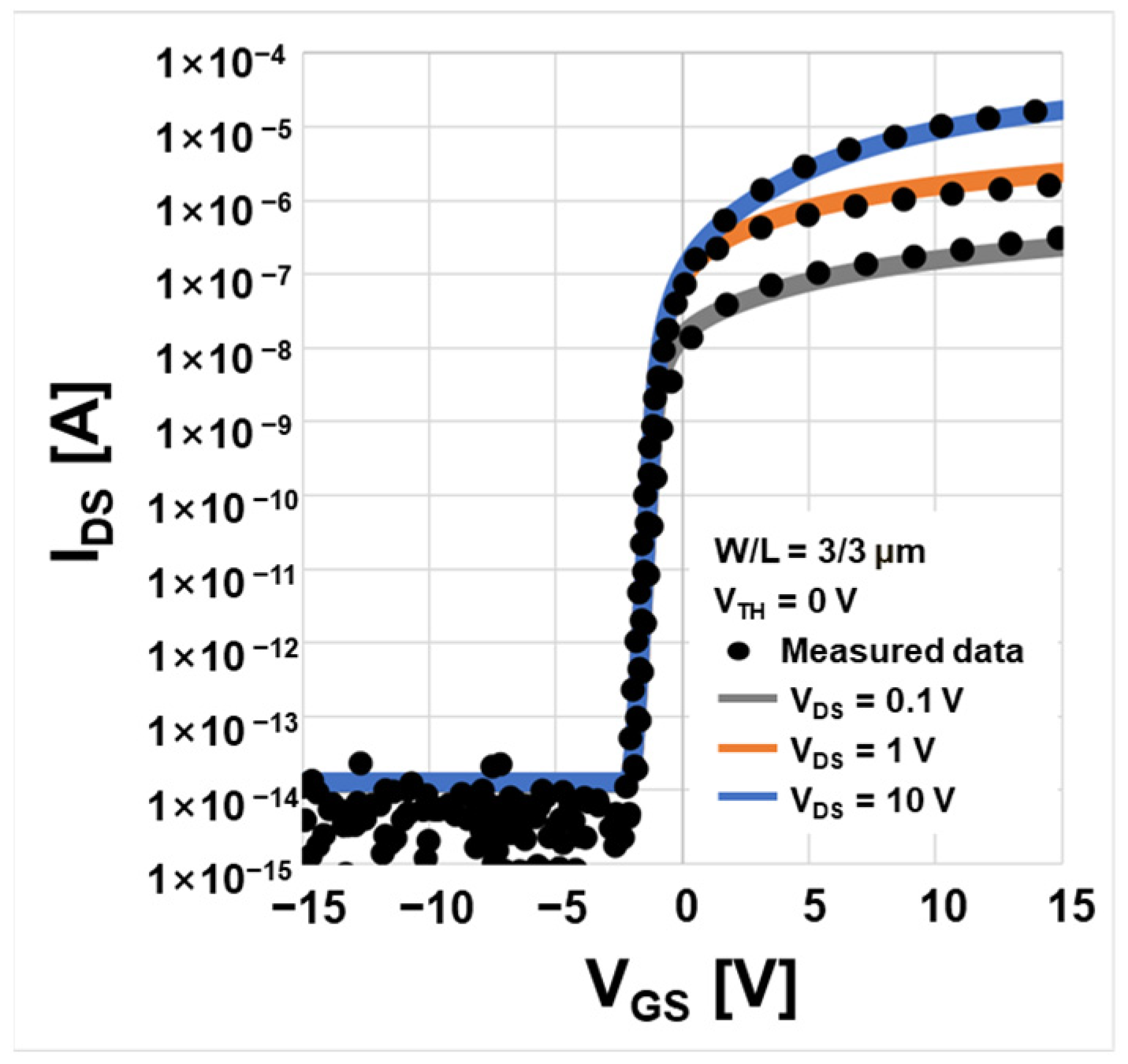

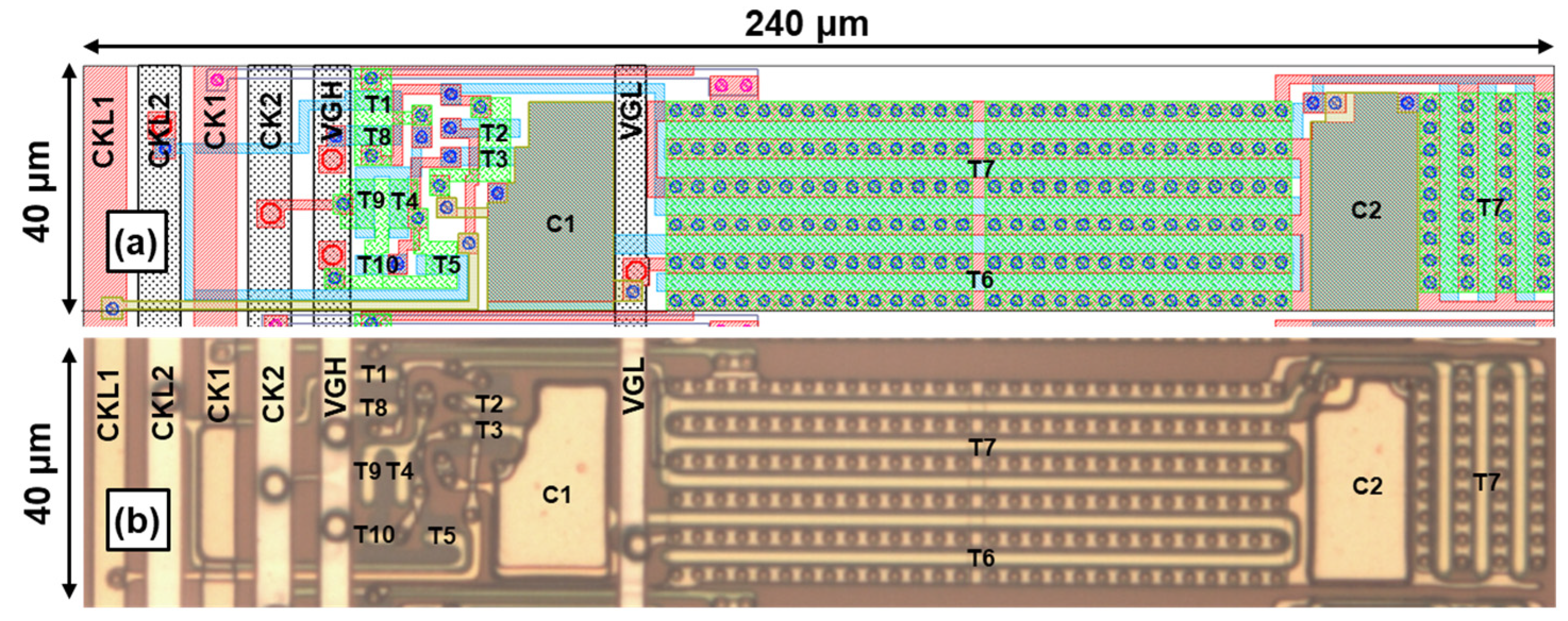

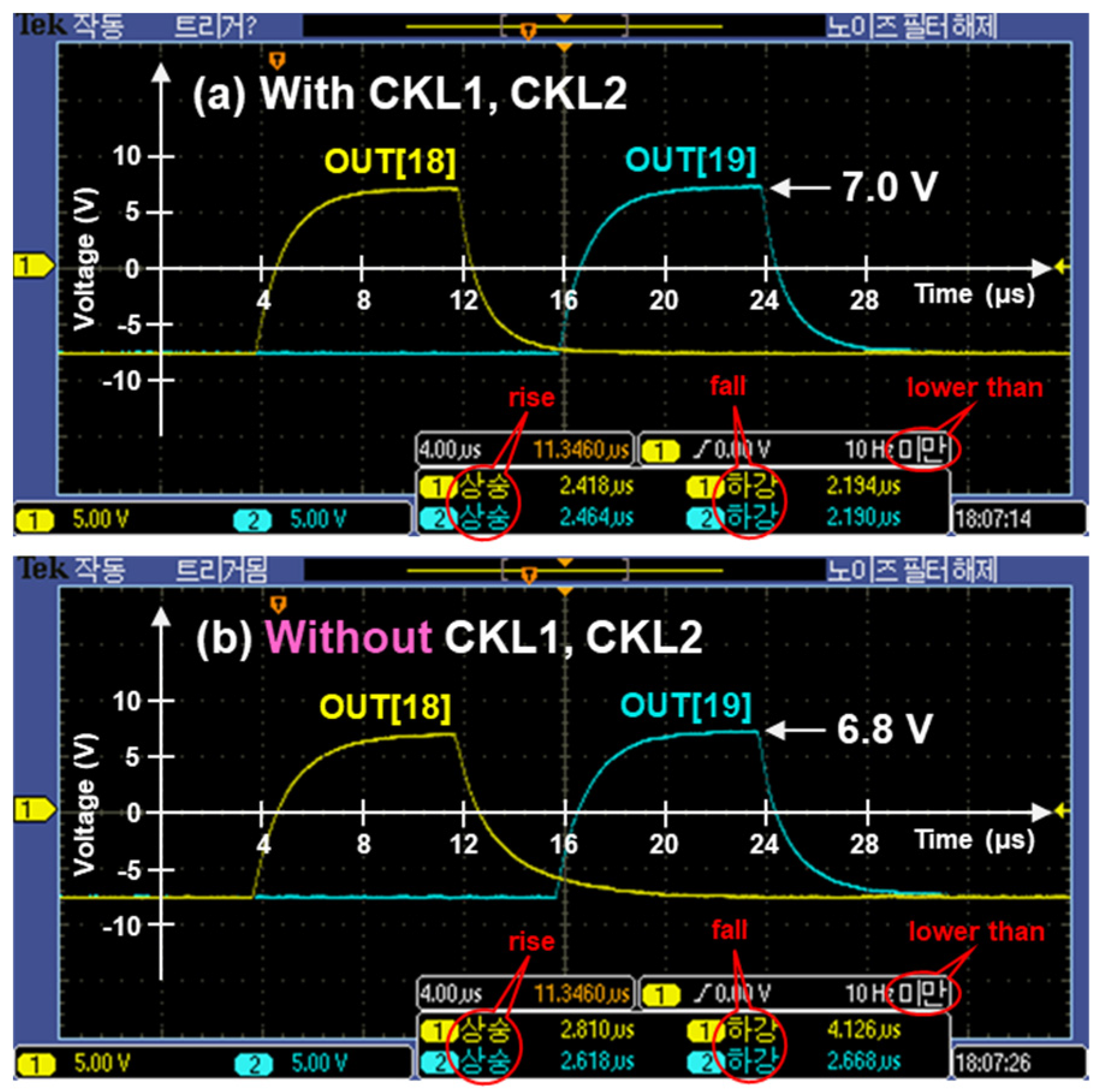

4.2. Fabrication and Measurement

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kunic, S.; Sego, Z. OLED Technology and Displays. In Proceedings of the 54th International Symposium ELMAR-2012, Zadar, Croatia, 12–14 September 2012; pp. 31–35. [Google Scholar]

- Chaji, R.; Nathan, A. Invited Paper: LTPS vs Oxide Backplanes for AMOLED Displays: System Design Considerations and Compensation Techniques. SID Int. Symp. Dig. Tech. Pap. 2014, 45, 153–156. [Google Scholar] [CrossRef]

- Park, K.-S.; Oh, S.; Yun, P.; Bae, J.U.; Kang, I.B. Invited Paper: Prospects of Oxide TFTs approaching LTPS. In Proceedings of the 2015 22nd International Workshop on Active-Matrix Flatpanel Displays and Devices (AM-FPD), Kyoto, Japan, 1–4 July 2015; pp. 241–244. [Google Scholar] [CrossRef]

- Ji, D.; Jang, J.; Park, J.H.; Kim, D.; Rim, Y.S.; Hwang, D.K.; Noh, Y.-Y. Recent progress in the development of backplane thin film transistors for information displays. J. Inf. Disp. 2021, 22, 1–11. [Google Scholar] [CrossRef]

- Kang, S.J.; Lee, H.S.; Woo, J.G.; Yu, E.S.; Lee, J.M.; Bae, B.S. Decoder-Type Scan Driver Suitable for Flexible and Stretchable Displays. Electronics 2022, 11, 519. [Google Scholar] [CrossRef]

- Lin, C.-L.; Lai, P.-C.; Chang, J.-H.; Chen, Y.-C.; Lai, P.-C.; Shih, L.-W. Reducing Leakage Current Using LTPS-TFT Pixel Circuit in AMOLED Smartwatch Displays. IEEE Trans. Ind. Electron. 2023, 70, 8588–8597. [Google Scholar] [CrossRef]

- Ke, J.; Deng, L.; Zhen, L.; Wu, Q.; Liao, C.; Luo, H.; Huang, S. An AMOLED Pixel Circuit Based on LTPS Thin-film Transistors with Mono-Type Scanning Driving. Electronics 2020, 9, 574. [Google Scholar] [CrossRef]

- Kim, K.-N.; Kang, J.-S.; Ahn, S.-J.; Lee, J.S.; Lee, D.H.; Kim, C.W.; Kwon, O.-K. A single-clock-driven gate driver using p-type, low-temperature polycrystalline silicon thin-film transistors. J. Inf. Disp. 2011, 12, 61–67. [Google Scholar] [CrossRef]

- Wu, Z.; Duan, L.; Yuan, G.; Jiang, C.; Li, Y.; Yan, L.; Cheng, J.; Wang, G.; Jin, S. An Integrated Gate Driver Circuit Employing Depletion-Mode IGZO TFTs. SID Int. Symp. Dig. Tech. Pap. 2012, 43, 5–7. [Google Scholar] [CrossRef]

- Han, I.; Song, E.; Kang, B.; Oh, K.; Kim, B.; Oh, C.; Ahn, B.; Nam, H. Depletion-Mode Oxide-TFT Shift Register with Wide Operating Frequency Range for AMOLED Displays. SID Int. Symp. Dig. Tech. Pap. 2015, 46, 61–63. [Google Scholar] [CrossRef]

- Song, R.; Wu, Y.; Lin, C.; Liu, K.; Qing, Z.; Li, Y.; Xue, Y. High-Speed Shift Register with Dual-Gated Thin-Film Transistors for a 31-Inch 4K AMOLED Display. Micromachines 2022, 13, 1696. [Google Scholar] [CrossRef] [PubMed]

- Kim, B.; Choi, S.C.; Lee, S.-Y.; Kuk, S.-H.; Jang, Y.H.; Kim, C.-D.; Han, M.-K. A Depletion-Mode a-IGZO TFT Shift Register With a Single Low-Voltage-Level Power Signal. IEEE Electron Device Lett. 2011, 32, 1092–1094. [Google Scholar] [CrossRef]

- Iwase, Y.; Tagawa, A.; Takeuchi, Y.; Watanabe, T.; Horiuchi, S.; Asai, Y.; Yamamoto, K.; Daitoh, T.; Matsuo, T. A novel low-power gate driver architecture for large 8 K 120 Hz liquid crystal display employing IGZO technology. J. Soc. Inf. Disp. 2018, 26, 304–313. [Google Scholar] [CrossRef]

- Tu, C.-D.; Tsao, S.-W.; Huang, C.-H.; Yu, W.-S.; Chen, Y.-C.; Lee, M.-H.; Hong, K.-W.; Chang, H.-S.; Lee, S.-C.; Kuo, C.-H. A Gate Driver Circuit with a-IGZO TFTs for 8-inch QXGA TFT-LED Panel. J. Soc. Inf. Disp. 2017, 48, 1416–1418. [Google Scholar] [CrossRef]

- Xu, P.; Han, Y.; Zhang, H.; Liu, F.; Yan, G.; Zhu, M.; Wang, L.; Zhao, D.; Zhang, X.; Luo, C.; et al. Development of Internal Compensation Technology for Medium Size OLED Display based on Oxide TFTs. SID Int. Symp. Dig. Tech. Pap. 2024, 37–40. [Google Scholar]

- Yan, G.; Wang, D.; Ding, L.; Xu, L.; Sun, X.; Chen, F.-H.; Xing, R.; Li, J. Development of High Mobility and Reliability Metal Oxide TFT for 13.2 inch AMOLED Display. SID Int. Symp. Dig. Tech. Pap. 2024, 154–157. [Google Scholar]

- Ning, C.; Wang, D.; Yuan, G.; Wang, L.; Liu, F.; Sun, H.; Lu, Y.; He, J.; Ma, Y.; Lin, Y. Ultra-low power consumption notebook LCD with high on-state current metal oxide device. SID Int. Symp. Dig. Tech. Pap. 2024, 1448–1451. [Google Scholar]

| Parameter | Value |

|---|---|

| VGH | 7 V |

| VGL | −6 V |

| VGLL | −9 V |

| CK1, CK2 | 7 V/−6 V |

| CKL1, CKL2 | 7 V/−9 V |

| W/L of T6 | 200/3 μm |

| W/L of T7 | 400/3 μm |

| W/L of T1, T8 | 6/3 μm |

| W/L of T2, T3, T5 | 5/3 μm |

| W/L of T4, T9 | 8/3 μm |

| W/L of T10 | 2/3 μm |

| C1, C2 | 190 fF |

| CLOAD | 25 pF |

| RLOAD | 2 kΩ |

| Reference | TFT Type | Structure | Width of Scan Driver Circuit | Negative Limit of TFT VTH |

|---|---|---|---|---|

| [9] | n-type a-IGZO | 15T-1C | 1200 μm | −2.1 V |

| [13] | n-type a-IGZO | 11T-1C | 3500 μm | −0.9 V |

| [14] | n-type a-IGZO | 15T-1C | 1000 μm | −0.4 V |

| This work | n-type a-IGZO | 10T-2C | 240 μm | −2.8 V |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

You, Y.; Lim, J.; Son, K.; Kim, J.; Kim, Y.; Lee, K.; Chung, K.; Park, K. A Simple Scan Driver Circuit Suitable for Depletion-Mode Metal-Oxide Thin-Film Transistors in Active-Matrix Displays. Electronics 2024, 13, 2254. https://doi.org/10.3390/electronics13122254

You Y, Lim J, Son K, Kim J, Kim Y, Lee K, Chung K, Park K. A Simple Scan Driver Circuit Suitable for Depletion-Mode Metal-Oxide Thin-Film Transistors in Active-Matrix Displays. Electronics. 2024; 13(12):2254. https://doi.org/10.3390/electronics13122254

Chicago/Turabian StyleYou, Yikyoung, Junhyung Lim, Kyoungseok Son, Jaybum Kim, Youngoo Kim, Kyunghoe Lee, Kyunghoon Chung, and Keechan Park. 2024. "A Simple Scan Driver Circuit Suitable for Depletion-Mode Metal-Oxide Thin-Film Transistors in Active-Matrix Displays" Electronics 13, no. 12: 2254. https://doi.org/10.3390/electronics13122254