Innovative Programming Approaches to Address Z-Interference in High-Density 3D NAND Flash Memory

Abstract

:1. Introduction

2. Simulation Set Up

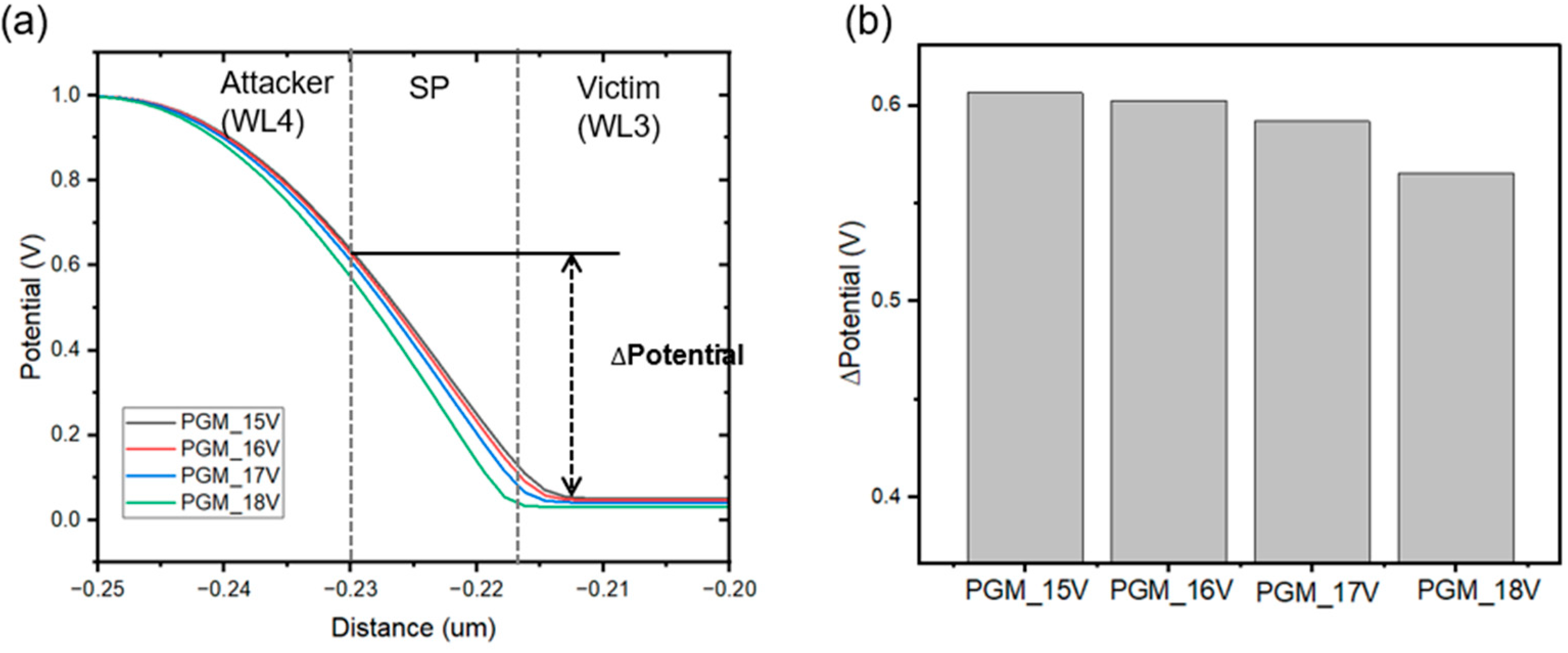

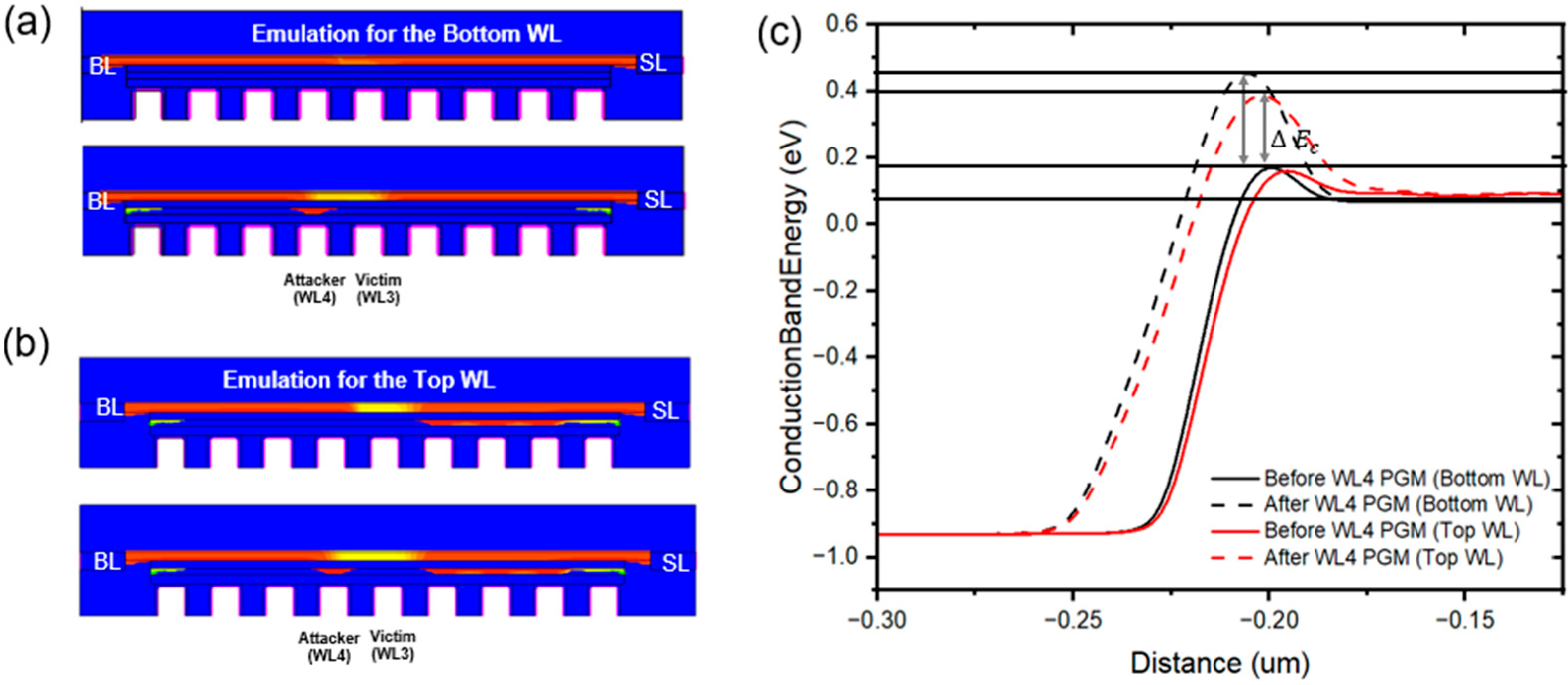

3. Asymmetric Z-Interference Analysis

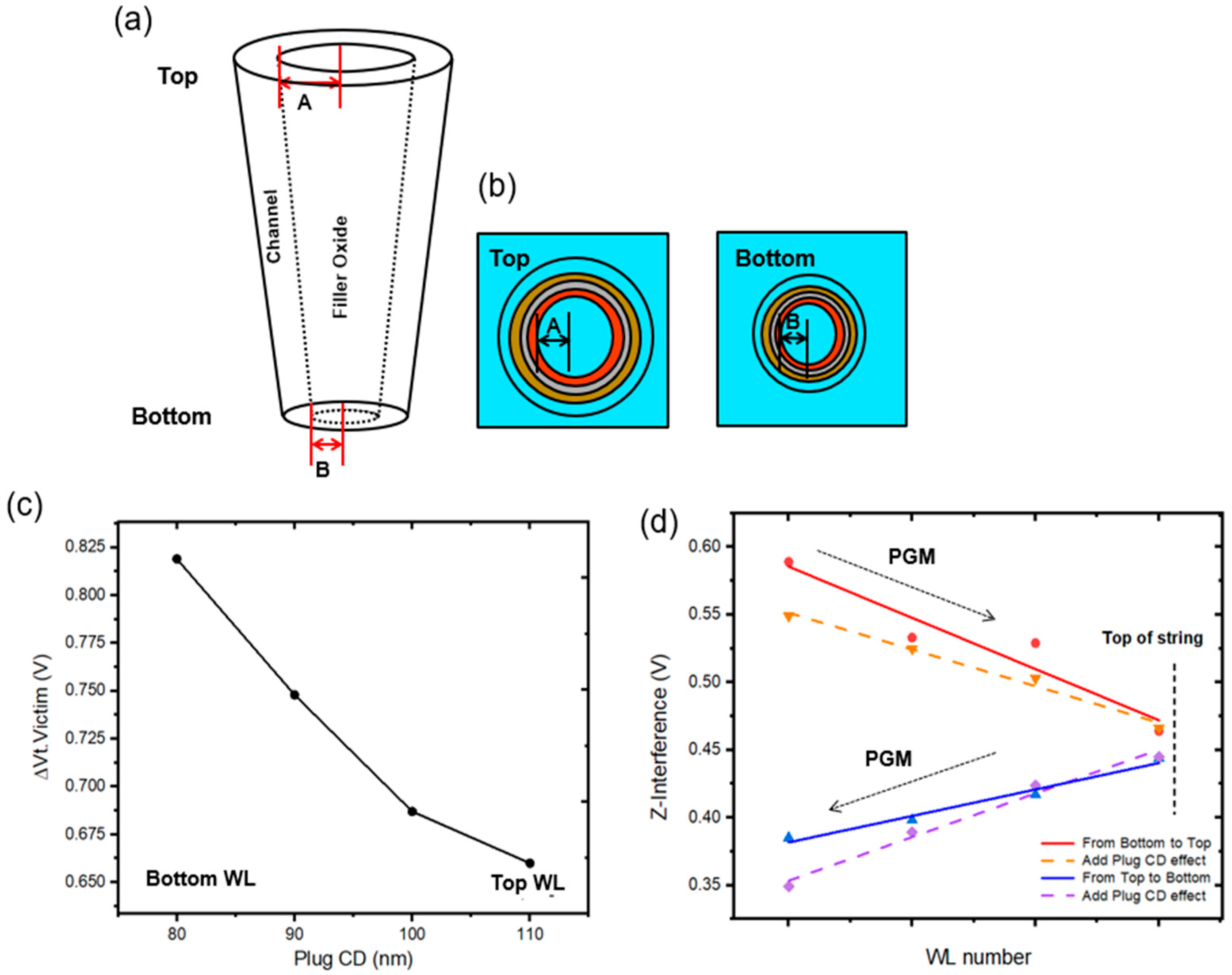

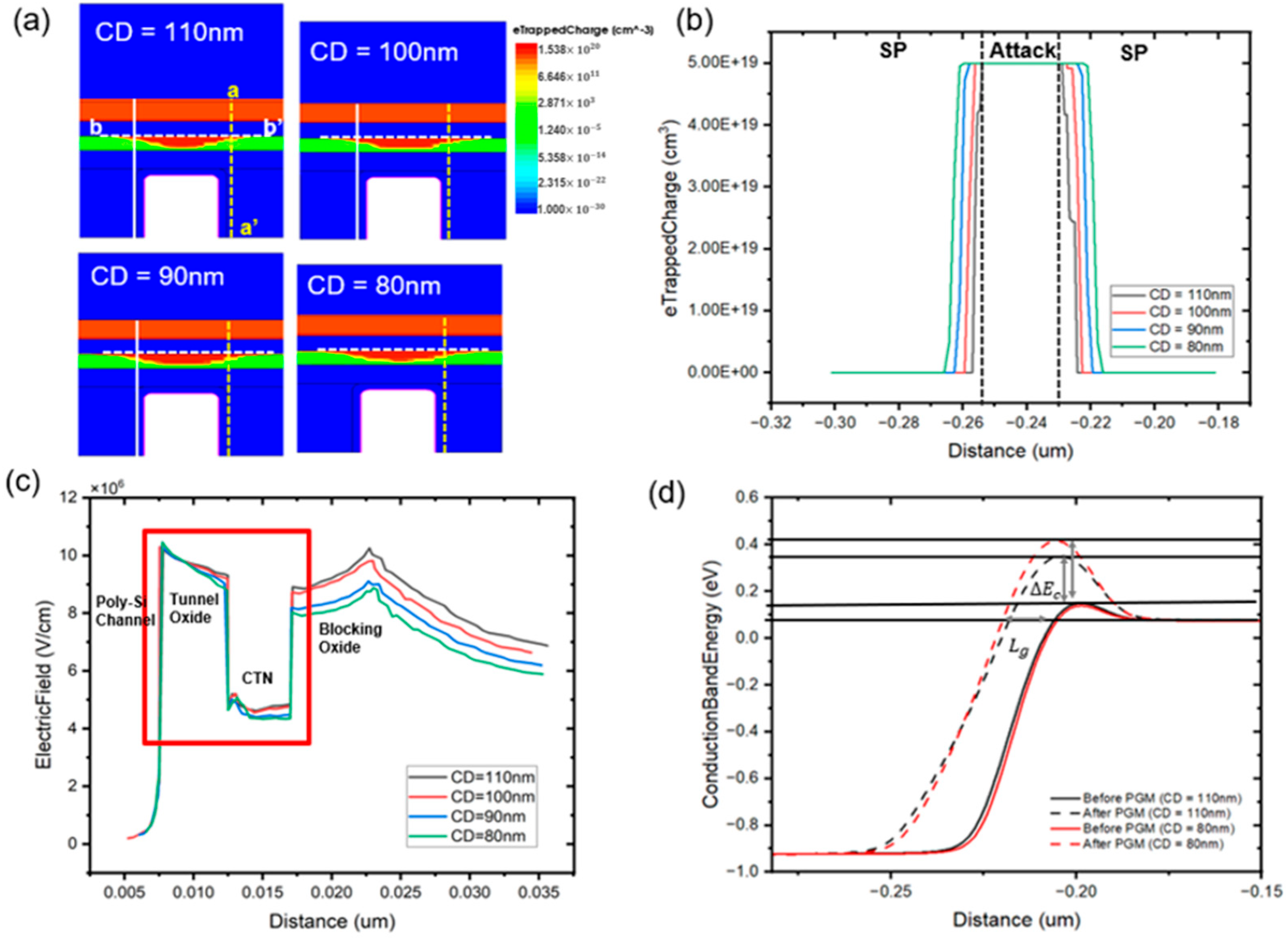

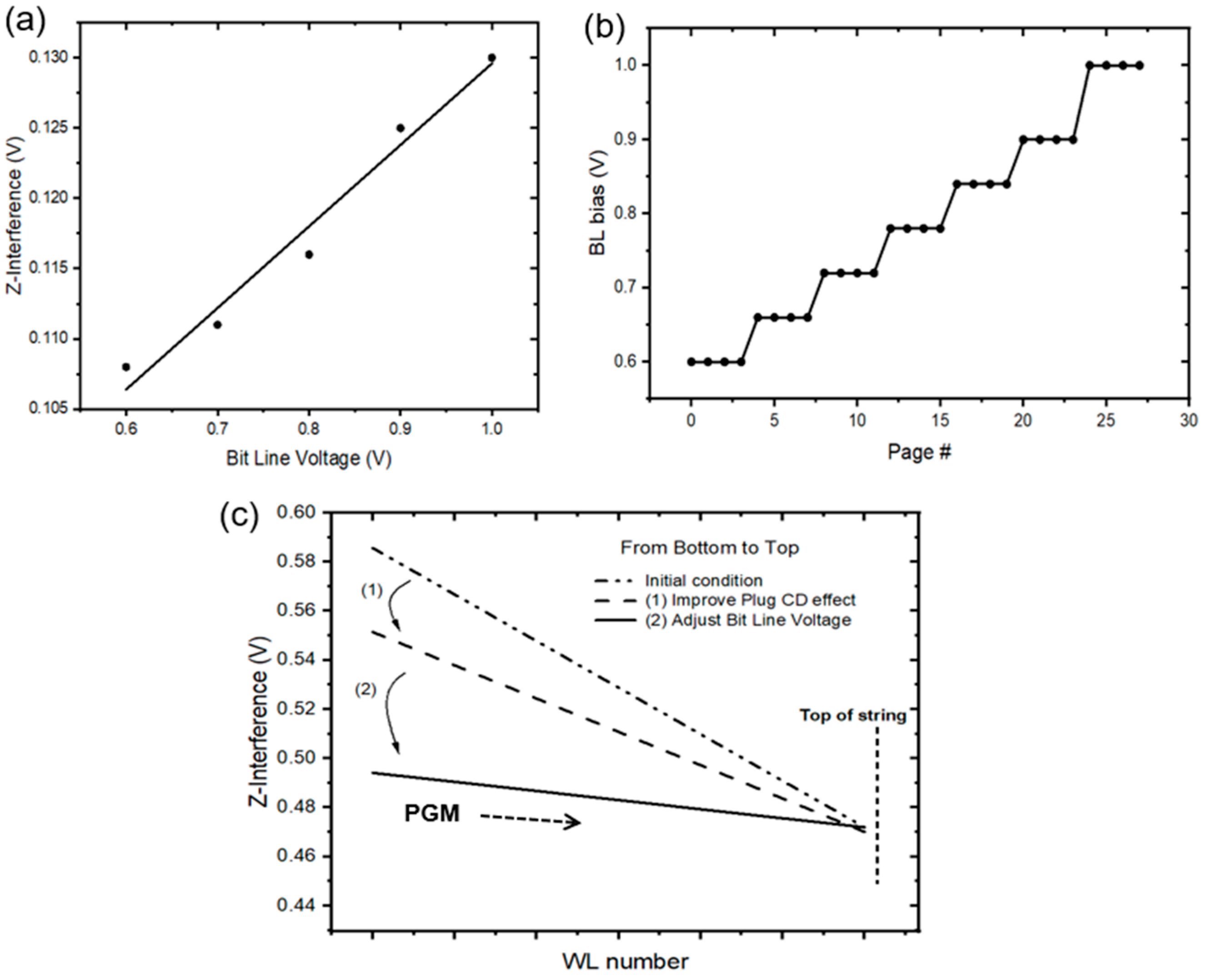

4. Effects of Tapered Shape of the Channel Hole

5. Improving Z-Interference by Adjusting Bitline Voltage

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Heineck, L.; Liu, J. 3D NAND flash status and trends. In Proceedings of the 2022 IEEE International Memory Workshop (IMW), Dresden, Germany, 15–18 May 2022; pp. 1–4. [Google Scholar]

- Goda, A. 3-D NAND technology achievements and future scaling perspectives. IEEE Trans. Electron Devices 2020, 67, 1373–1381. [Google Scholar] [CrossRef]

- Chandrasekaran, N.; Ramaswamy, N.; Mouli, C. Memory technology: Innovations needed for continued technology scaling and enabling advanced computing systems. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020. [Google Scholar]

- Yang, L.; Wang, Q.; Li, Q.; Yu, X.; He, J.; Huo, Z. Efficient data recovery technique for 3D TLC NAND flash memory based on WL interference. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021. [Google Scholar]

- Liu, W.; Wu, F.; Chen, X.; Zhang, M.; Wang, Y.; Lu, X.; Xie, C. Characterization summary of performance, reliability, and threshold voltage distribution of 3D charge-trap NAND flash memory. ACM Trans. Storage (TOS) 2022, 18, 1–25. [Google Scholar] [CrossRef]

- Chang, Y.-W.; Wu, G.-W.; Yang, I.-C.; Huang, Y.-H.; Lee, Y.-J.; Lee, C.-H.; Chen, K.-F.; Lu, T.-C.; Chen, K.-C.; Lu, C.-Y. Asymmetric interference behavior in 3D NAND cell and the reverse trend induced by undercut of sacrificial nitride film. IEEE Electron Device Lett. 2022, 43, 2077–2080. [Google Scholar] [CrossRef]

- Kim, Y.; Hong, S.K.; Park, J.K. Optimizing Confined Nitride Trap Layers for Improved Z-Interference in 3D NAND Flash Memory. Electronics 2024, 13, 1020. [Google Scholar] [CrossRef]

- Chen, W.-C.; Lue, H.-T.; Hsieh, C.-C.; Wang, K.-C.; Lu, C.-Y. Performance enhancement of 3-D NAND flash featuring a two-step dummy wordline program waveform and pair-bitline program scheme. IEEE Trans. Electron Devices 2019, 67, 99–104. [Google Scholar] [CrossRef]

- Sim, J.-M.; Kang, M.; Song, Y.-H. A new read scheme for alleviating cell-to-cell interference in scaled-down 3D NAND flash memory. Electronics 2020, 9, 1775. [Google Scholar] [CrossRef]

- Yi, S.-i.; Kim, J. Novel program scheme of vertical NAND flash memory for reduction of Z-interference. Micromachines 2021, 12, 584. [Google Scholar] [CrossRef] [PubMed]

- Jo, H.; Ahn, S.; Shin, H. Investigation and modeling of Z-interference in poly-Si channel-based 3-D NAND flash memories. IEEE Trans. Electron Devices 2022, 69, 543–548. [Google Scholar] [CrossRef]

- Chen, W.-C.; Lue, H.-T.; Chang, K.-P.; Hsiao, Y.-H.; Hsieh, C.-C.; Shih, Y.-H.; Lu, C.-Y. Study of the programming sequence induced back-pattern effect in split-page 3D vertical-gate (VG) NAND flash. In Proceedings of the Technical Program—2014 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), Hsinchu, Taiwan, 28–30 April 2014; pp. 1–2. [Google Scholar]

- Fan, H.; Tian, X.; Peng, H.; Shen, Y.; Li, L.; Li, M.; Gao, L. Adaptive Bitline Voltage Countermeasure for Neighbor Wordline Interference in 3D NAND Flash Memory-Based Sensors. Sensors 2023, 23, 3212. [Google Scholar] [CrossRef] [PubMed]

- Goda, A. Recent progress on 3D NAND flash technologies. Electronics 2021, 10, 3156. [Google Scholar] [CrossRef]

- Lee, D.; Shin, C. Impact of Stacking-Up and Scaling-Down Bit Cells in 3D NAND on Their Threshold Voltages. Micromachines 2022, 13, 1139. [Google Scholar] [CrossRef] [PubMed]

- Wu, C.-J.; Lue, H.-T.; Hsu, T.-H.; Hsieh, C.-C.; Chen, W.-C.; Du, P.-Y.; Chiu, C.-J.; Lu, C.-Y. Device characteristics of single-gate vertical channel (SGVC) 3D NAND flash architecture. In Proceedings of the 2016 IEEE 8th International Memory Workshop (IMW), Paris, France, 15–18 May 2016. [Google Scholar]

- Yoon, D.; Sim, J.; Song, Y. Mechanical stress in a tapered channel hole of 3D NAND flash memory. Microelectron. Reliab. 2023, 143, 114941. [Google Scholar] [CrossRef]

- Lee, J.G.; Jung, W.J.; Park, J.H.; Yoo, K.-H.; Kim, T.W. Effect of the blocking oxide layer with asymmetric taper angles in 3-D NAND flash memories. IEEE J. Electron Devices Soc. 2021, 9, 774–777. [Google Scholar] [CrossRef]

- Kim, S.S.; Yong, S.K.; Kim, W.; Kang, S.; Park, H.W.; Yoon, K.J.; Sheen, D.S.; Lee, S.; Hwang, C.S. Review of semiconductor flash memory devices for material and process issues. Adv. Mater. 2023, 35, 2200659. [Google Scholar] [CrossRef] [PubMed]

- Bhatt, U.M.; Manhas, S.K.; Kumar, A.; Pakala, M.; Yieh, E. Mitigating the impact of channel tapering in vertical channel 3-D NAND. IEEE Trans. Electron Devices 2020, 67, 929–936. [Google Scholar] [CrossRef]

- Yoon, C.-W. The Fundamentals of NAND Flash Memory: Technology for tomorrow’s fourth industrial revolution. IEEE Solid-State Circuits Mag. 2022, 14, 56–65. [Google Scholar] [CrossRef]

- Shim, S.I.; Jang, J.; Song, J. Trends and future challenges of 3D NAND flash memory. In Proceedings of the 2023 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 21–24 May 2023. [Google Scholar]

| Program | Erase | Read | |

|---|---|---|---|

| Selected cell | 15 V~18 V | 0 V | −6 V~5 V |

| Unselected cell | 8.5 V | 0 V | 7 V |

| BL | 0 V | 22 V | 1 V |

| DSL | 8.5 V | Floating | 7 V |

| SSL | 0 V | Floating | 7 V |

| SL | 2 V | 22 V | 0 V |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, Y.J.; Hong, S.K.; Park, J.K. Innovative Programming Approaches to Address Z-Interference in High-Density 3D NAND Flash Memory. Electronics 2024, 13, 3123. https://doi.org/10.3390/electronics13163123

Choi YJ, Hong SK, Park JK. Innovative Programming Approaches to Address Z-Interference in High-Density 3D NAND Flash Memory. Electronics. 2024; 13(16):3123. https://doi.org/10.3390/electronics13163123

Chicago/Turabian StyleChoi, Yu Jin, Seul Ki Hong, and Jong Kyung Park. 2024. "Innovative Programming Approaches to Address Z-Interference in High-Density 3D NAND Flash Memory" Electronics 13, no. 16: 3123. https://doi.org/10.3390/electronics13163123