Study on the Single-Event Burnout Effect Mechanism of SiC MOSFETs Induced by Heavy Ions

Abstract

:1. Introduction

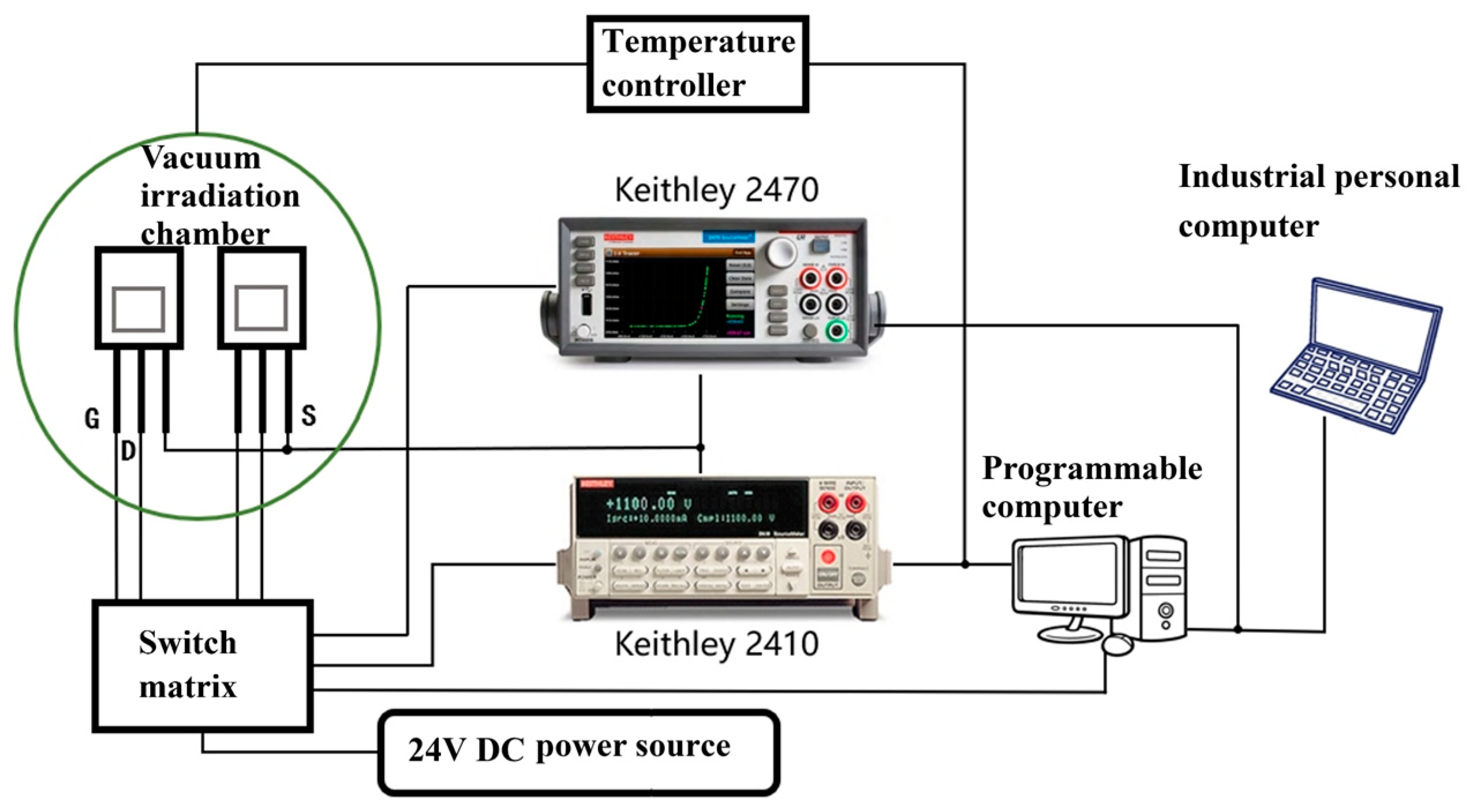

2. Experimental Setup

3. Results and Discussion

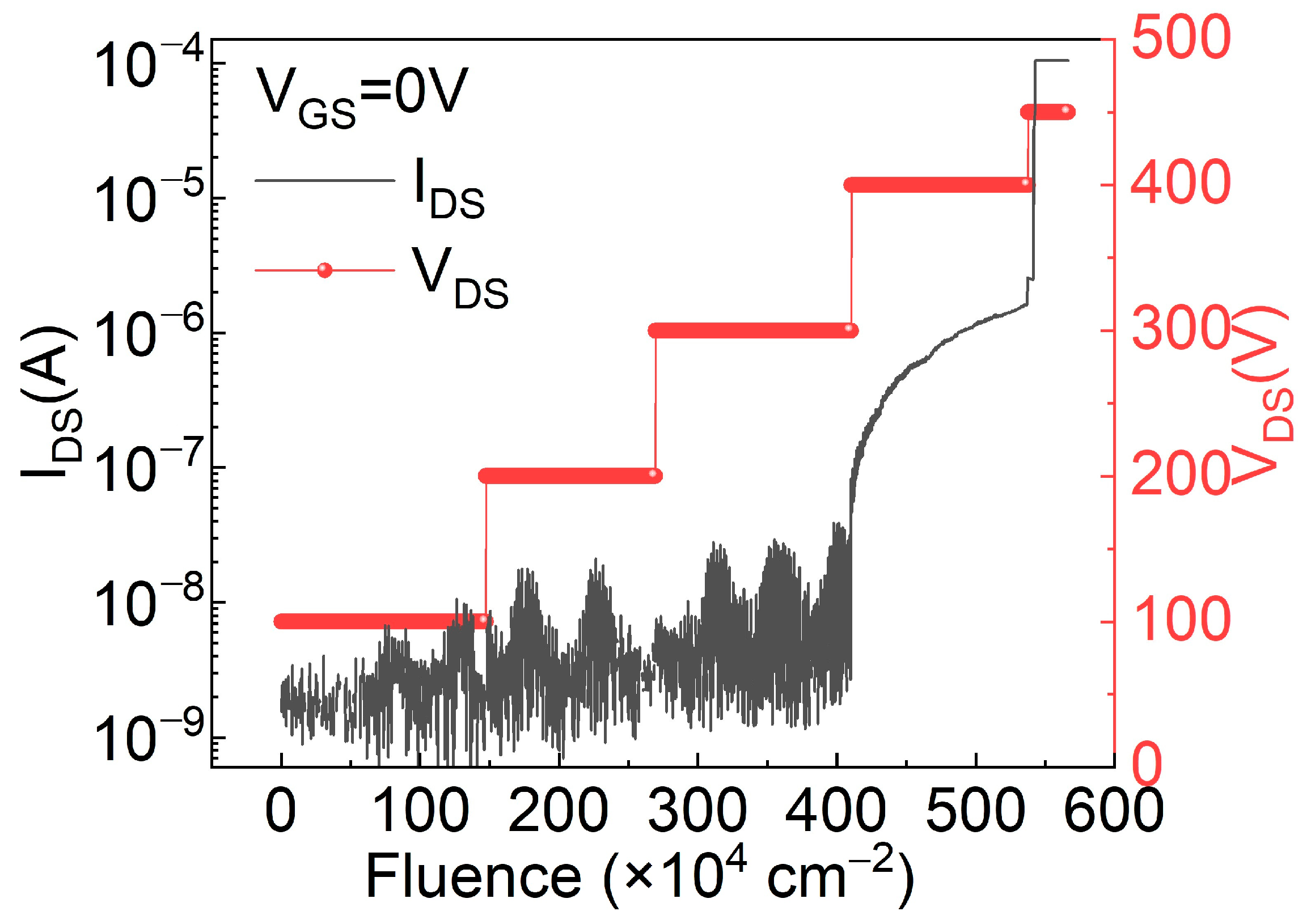

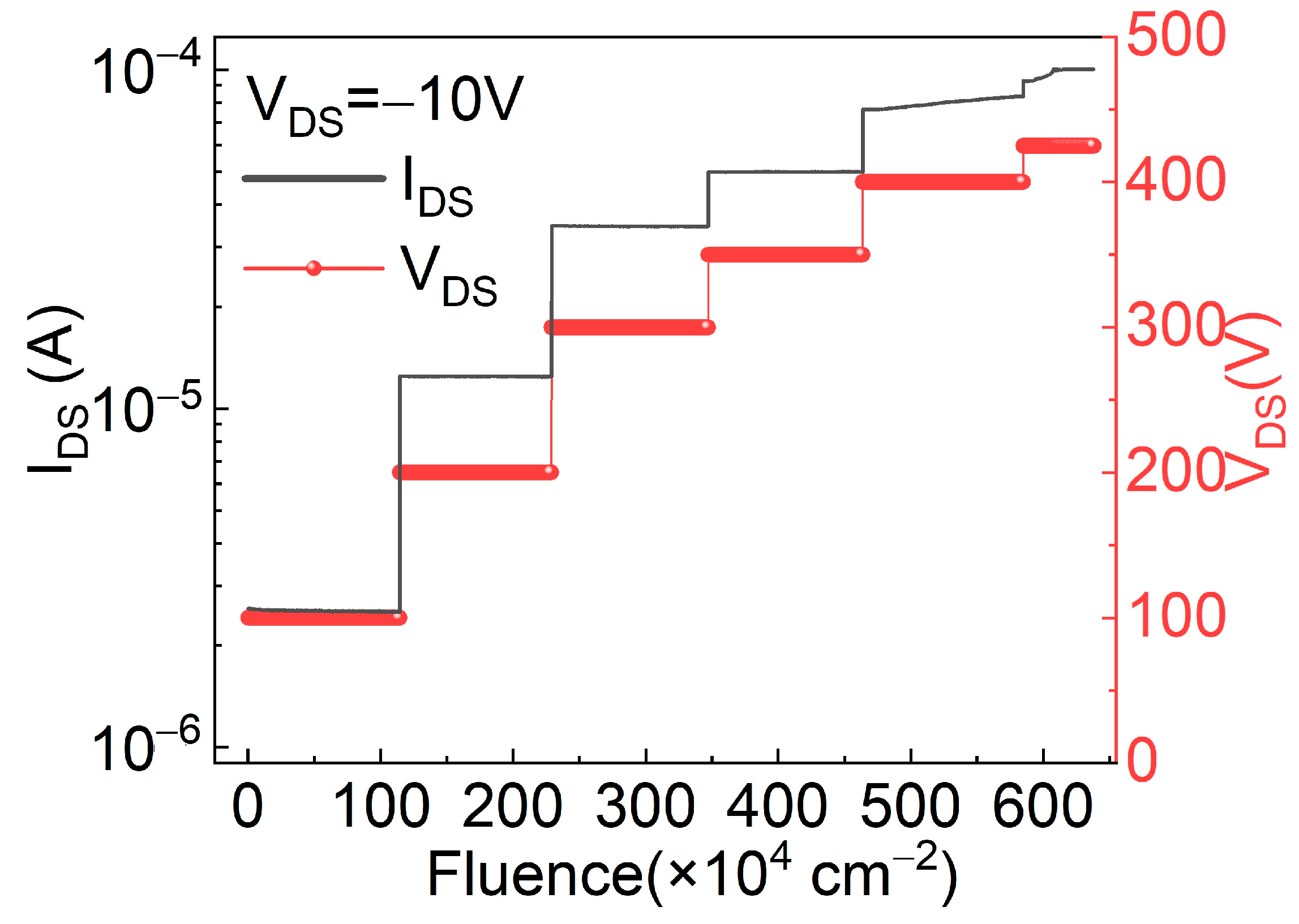

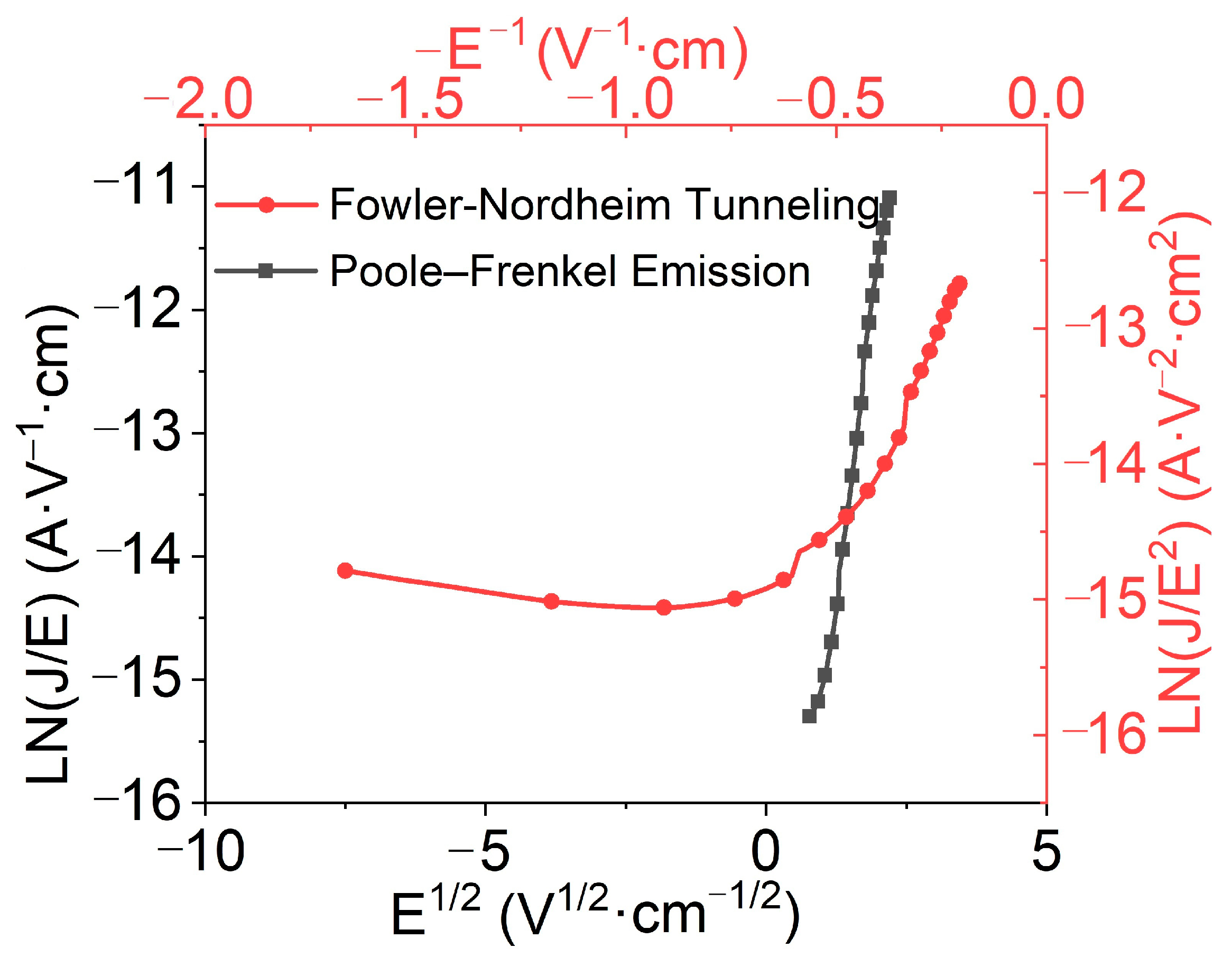

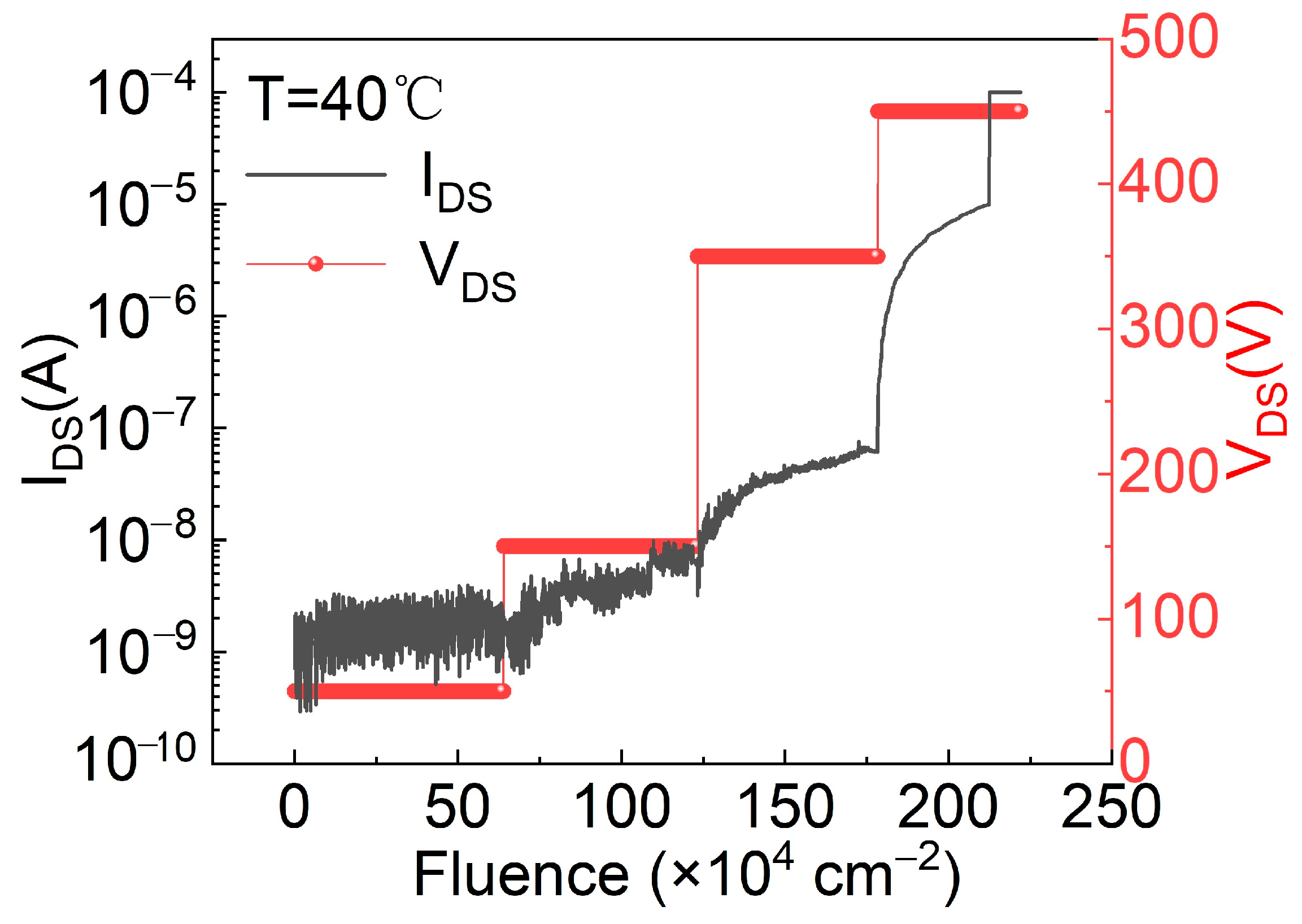

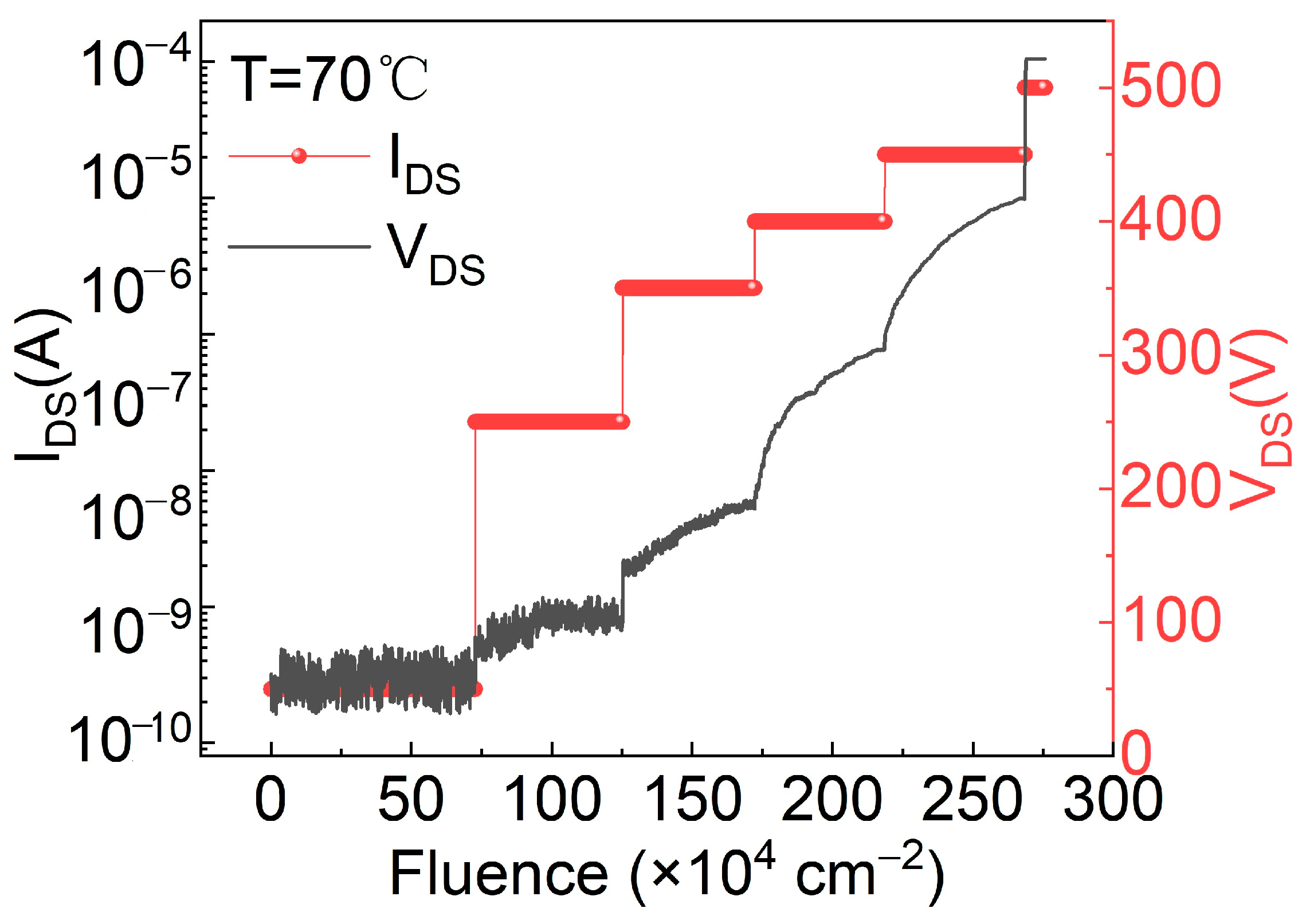

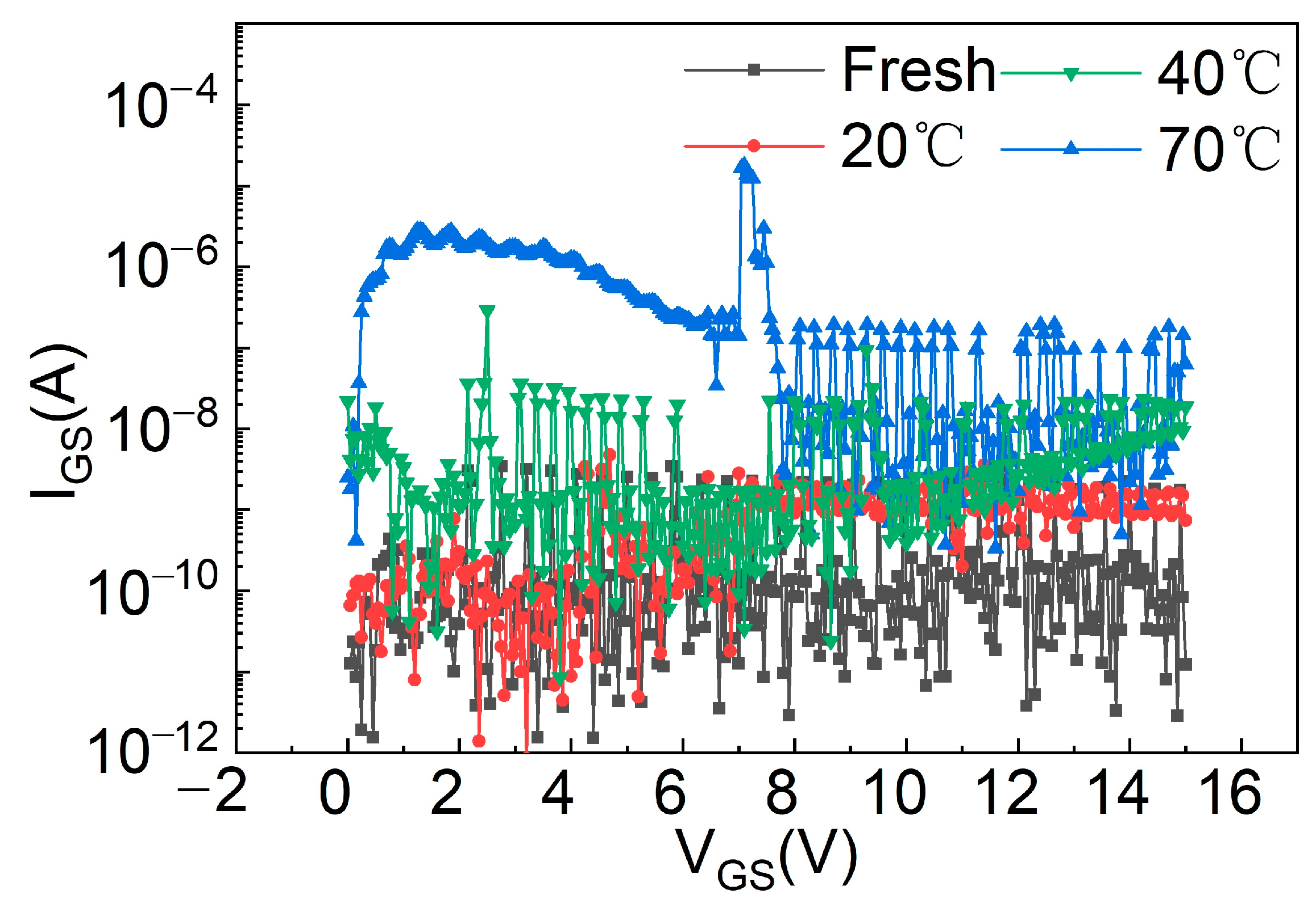

3.1. Degradation Characteristics of SiC MOSFET under Heavy Ion Irradiation

- Atomic displacement: defects introduced by atomic displacement in SiO2 caused by irradiation.

- Chemical bond breakage: defects introduced by chemical bond breakage in SiO2 caused by electrical stress.

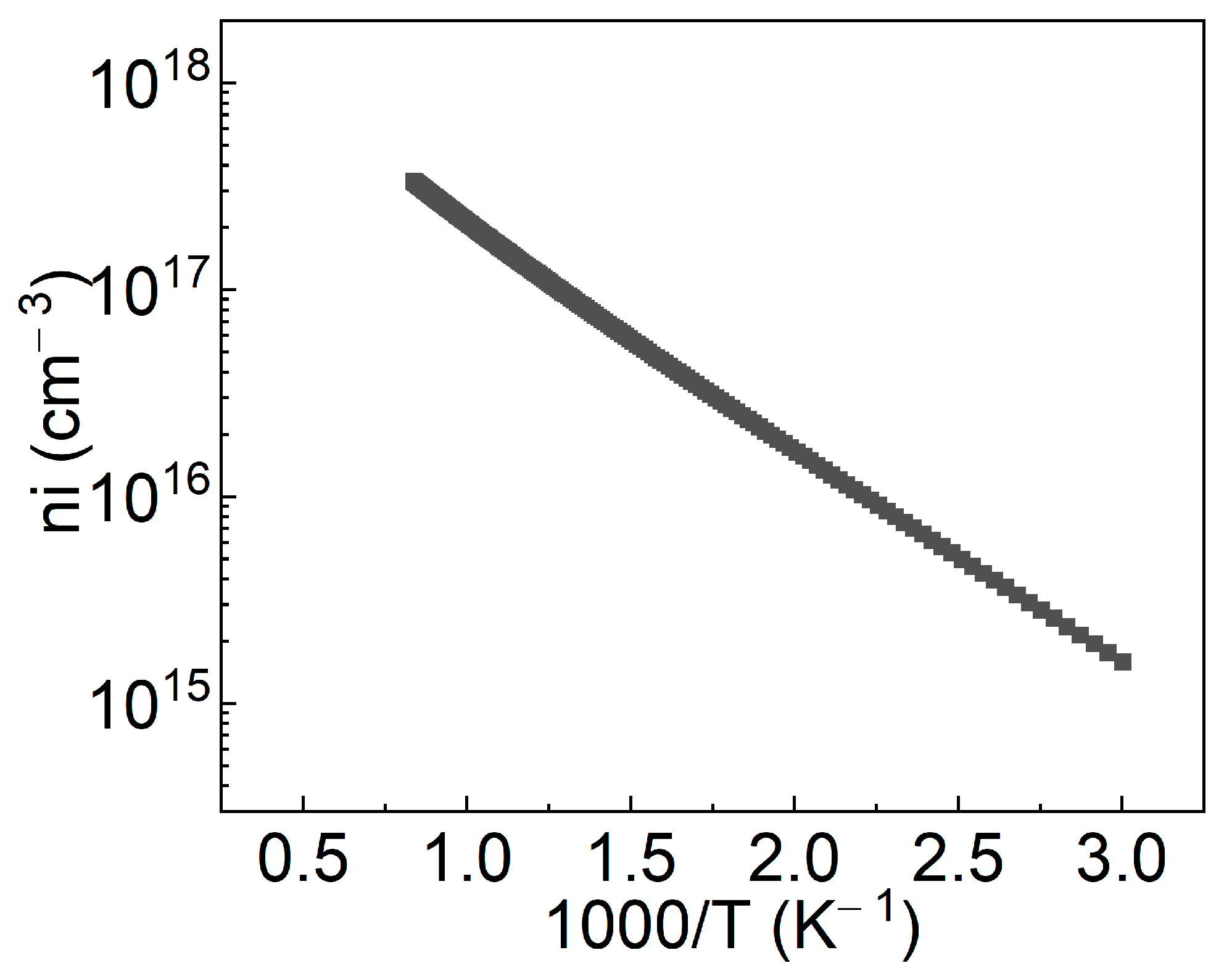

3.2. Temperature Synergy Effect

- Voltage drop on the gate oxide layer, caused by the charge that generates the strong inversion layer.

- Flat band voltages. The second and third terms are the flat band voltages of the MOSFET device.

- The surface potential is ϕs = 2ϕfp, where a strong inversion layer begins to form at the interface. The ϕfp formula can be expressed as follows:

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Grome, C.A.; Ji, W. A Brief Review of Single-Event Burnout Failure Mechanisms and Design Tolerances of Silicon Carbide Power MOSFETs. Electronics 2024, 13, 1414. [Google Scholar] [CrossRef]

- Zhang, H.; Guo, H.; Lei, Z.; Peng, C.; Zhang, Z.; Chen, Z.; Sun, C.; He, Y.; Zhang, F.; Pan, X.; et al. Experiment and Simulation on Degradation and Burnout Mechanisms of SiC MOSFET under Heavy Ion Irradiation. Chin. Phys. B 2023, 32, 028504. [Google Scholar]

- Peng, C.; Lei, Z.; Chen, Z.; Yue, S.; Zhang, Z.; He, Y.; Huang, Y. Experimental and Simulation Studies of Radiation-Induced Single Event Burnout in SiC-Based Power MOSFETs. IET Power Electron. 2021, 14, 1700–1712. [Google Scholar]

- Martinella, C.; Ziemann, T.; Stark, R.; Tsibizov, A.; Voss, K.O.; Alia, R.G.; Kadi, Y.; Grossner, U.; Javanainen, A. Heavy-Ion Microbeam Studies of Single-Event Leakage Current Mechanism in SiC VD-MOSFETs. IEEE Trans. Nucl. Sci. 2020, 67, 1381–1389. [Google Scholar]

- Martinella, C.; Natzke, P.; Alia, R.G.; Kadi, Y.; Niskanen, K.; Rossi, M.; Jaatinen, J.; Kettunen, H.; Tsibizov, A.; Grossner, U.; et al. Heavy-Ion Induced Single Event Effects and Latent Damages in SiC Power MOSFETs. Microelectron. Reliab. 2022, 128, 114423. [Google Scholar]

- Kim, C.; Yoon, H.; Kim, D.-S.; Seok, O. Comparison Analysis of Radiation Effects on 1.2 kV SiC Metal-Oxide-Semiconductor Field-Effect Transistors with Gamma-Ray and Proton Irradiation. Electronics 2024, 13, 1352. [Google Scholar] [CrossRef]

- Johnson, R.A.; Witulski, A.F.; Ball, D.R.; Galloway, K.F.; Sternberg, A.L.; Reed, R.A.; Schrimpf, R.D.; Alles, M.L.; Lauenstein, J.M.; Hutson, J.M. Analysis of Heavy-Ion-Induced Leakage Current in SiC Power Devices. IEEE Trans. Nucl. Sci. 2022, 69, 248–253. [Google Scholar]

- Johnson, R.A.; Witulski, A.F.; Sierawski, B.D.; Ball, D.B.; Galloway, K.F.; Sternberg, A.L.; Reed, R.A.; Schrimpf, R.D.; Alles, M.L.; Lauenstein, J.M.; et al. Influence of Radiation Environment Variability on Cumulative Heavy-Ion-Induced Leakage Current in SiC Power Devices. IEEE Trans. Nucl. Sci. 2023, 70, 322–327. [Google Scholar]

- Martinella, C.; Stark, R.; Ziemann, T.; Alia, R.G.; Kadi, Y.; Grossner, U.; Javanainen, A. Current Transport Mechanism for Heavy-Ion Degraded SiC MOSFETs. IEEE Trans. Nucl. Sci. 2019, 66, 1702–1709. [Google Scholar]

- Witulski, A.F.; Arslanbekov, R.; Raman, A.; Schrimpf, R.D.; Sternberg, A.L.; Galloway, K.F.; Javanainen, A.; Grider, D.; Lichtenwalner, D.J.; Hull, B. Single-Event Burnout of SiC Junction Barrier Schottky Diode High-Voltage Power Devices. IEEE Trans. Nucl. Sci. 2018, 65, 256–261. [Google Scholar]

- Cao, S.; Yu, Q.; Wang, Q.; Wang, H.; Sun, Y.; Lv, H.; Mei, B.; Mo, R.; Li, P.; Zhang, H. Failure Analysis of Heavy Ion-Irradiated Silicon Carbide Junction Barrier Schottky Diodes. Microelectron. Reliab. 2024, 157, 115401-1–115401-5. [Google Scholar]

- Pintacuda, F.; Massett, S.; Vitanza, E.; Muschitiello, M.; Cantarella, V. SEGR and PIGS Failure Analysis of SiC Mosfet. In Proceedings of the 2019 European Space Power Conference (ESPC), Juan-les-Pins, France, 30 September–4 October 2019. [Google Scholar]

- Rafí, J.M.; Campabadal, F.; Ohyama, H.; Takakura, K.; Tsunoda, I.; Zabala, M.; Beldarrain, O.; González, M.B.; García, H.; Castán, H.; et al. 2 MeV Electron Irradiation Effects on the Electrical Characteristics of Metal-Oxide-Silicon Capacitors with Atomic Layer Deposited Al2IO3, HfO2 and Nanolaminated Dielectrics. Solid State Electron. 2013, 79, 65–74. [Google Scholar]

- Lim, E.W.; Ismail, R. Conduction Mechanism of Valence Change Resistive Switching Memory: A Survey. Electronics 2015, 4, 586–613. [Google Scholar] [CrossRef]

- Yang, W.L.; Marino, J.; Monson, A.; Wolden, C.A. An Investigation of Annealing on the Dielectric Performance of TiO2 Thin Films. Semicond. Sci. Technol. 2006, 21, 1573–1579. [Google Scholar]

- Zhou, X.; Pang, H.; Jia, y.; Hu, D.; Wu, Y.; Zhang, S.; Li, Y.; Li, X.; Wang, L.; Fang, X.; et al. Gate Oxide Damage of SiC MOSFETs Induced by Heavy-Ion Strike. IEEE Trans. Electron Devices 2021, 68, 4010–4015. [Google Scholar]

- Chen, X.; Zhang, Q.; Chen, Y. Microelectronic Devices, 4th ed.; Publishing House of Electronics Industry: Beijing, China, 2011; pp. 208–212. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, C.; Guo, G.; Shi, H.; Zhang, Z.; Li, F.; Zhang, Y.; Han, J. Study on the Single-Event Burnout Effect Mechanism of SiC MOSFETs Induced by Heavy Ions. Electronics 2024, 13, 3402. https://doi.org/10.3390/electronics13173402

Liu C, Guo G, Shi H, Zhang Z, Li F, Zhang Y, Han J. Study on the Single-Event Burnout Effect Mechanism of SiC MOSFETs Induced by Heavy Ions. Electronics. 2024; 13(17):3402. https://doi.org/10.3390/electronics13173402

Chicago/Turabian StyleLiu, Cuicui, Gang Guo, Huilin Shi, Zheng Zhang, Futang Li, Yanwen Zhang, and Jinhua Han. 2024. "Study on the Single-Event Burnout Effect Mechanism of SiC MOSFETs Induced by Heavy Ions" Electronics 13, no. 17: 3402. https://doi.org/10.3390/electronics13173402

APA StyleLiu, C., Guo, G., Shi, H., Zhang, Z., Li, F., Zhang, Y., & Han, J. (2024). Study on the Single-Event Burnout Effect Mechanism of SiC MOSFETs Induced by Heavy Ions. Electronics, 13(17), 3402. https://doi.org/10.3390/electronics13173402