High Quality Factor Miniaturized CMOS Transmission Lines Using Cascaded T-Networks for 60 GHz Millimeter Wave Applications

Abstract

:1. Introduction

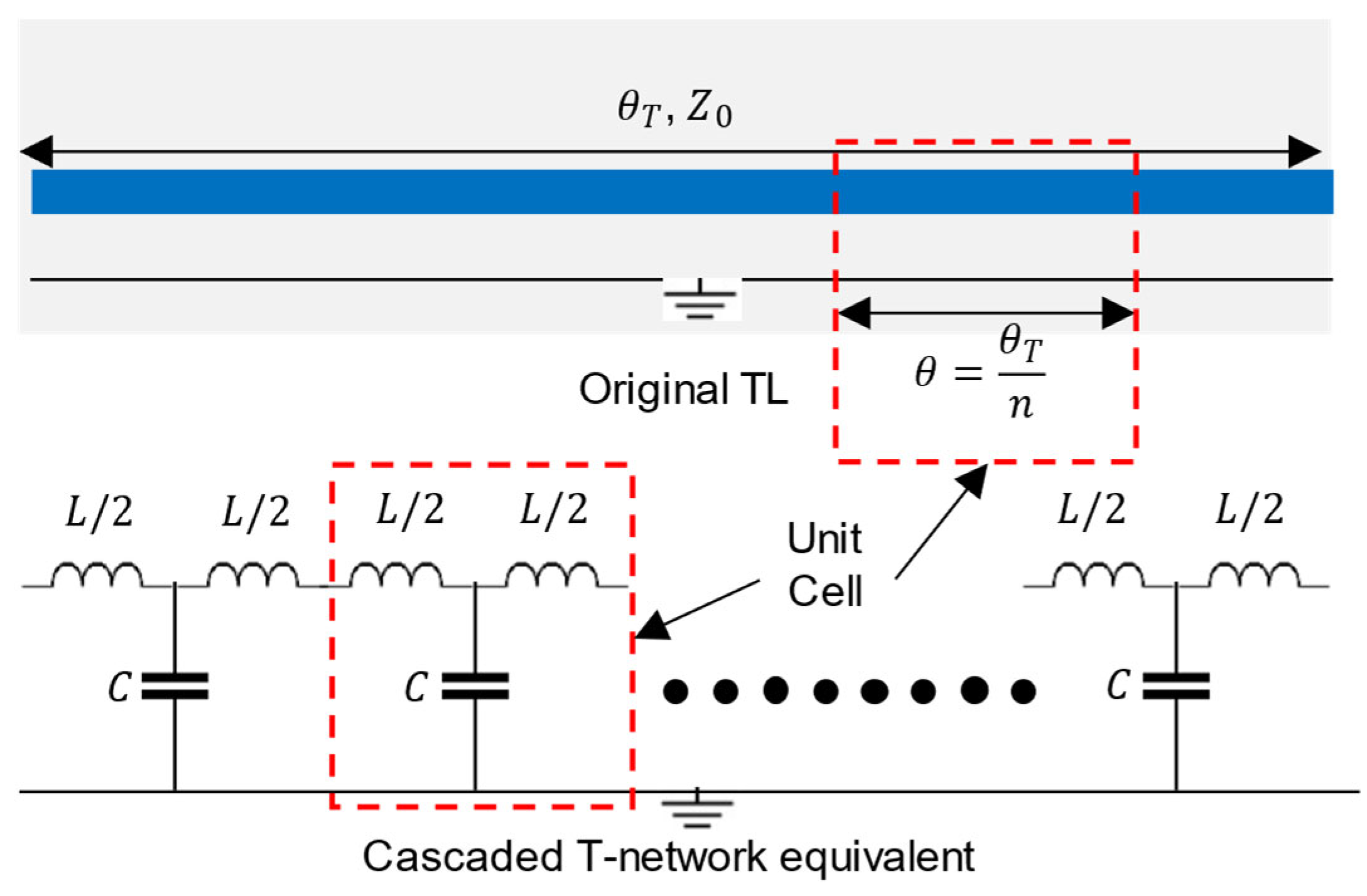

2. Proposed Lumped Element TL Design

2.1. Unit Cell Design

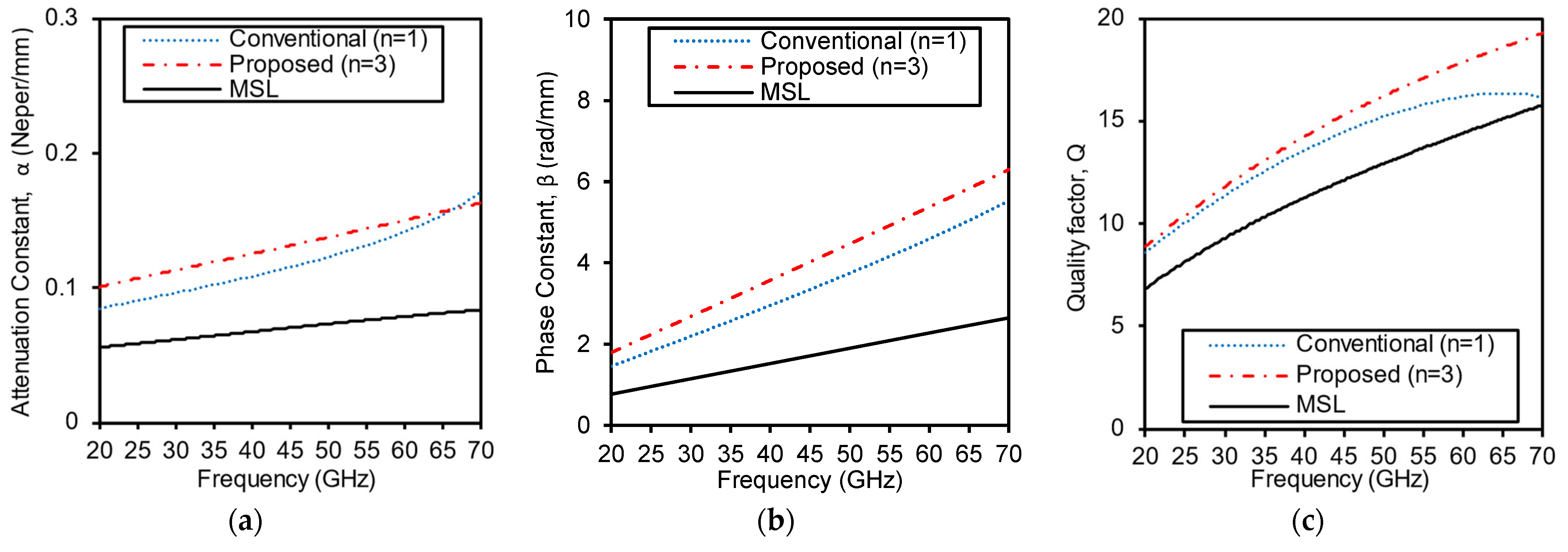

2.2. Optimum Number of Unit T-Networks

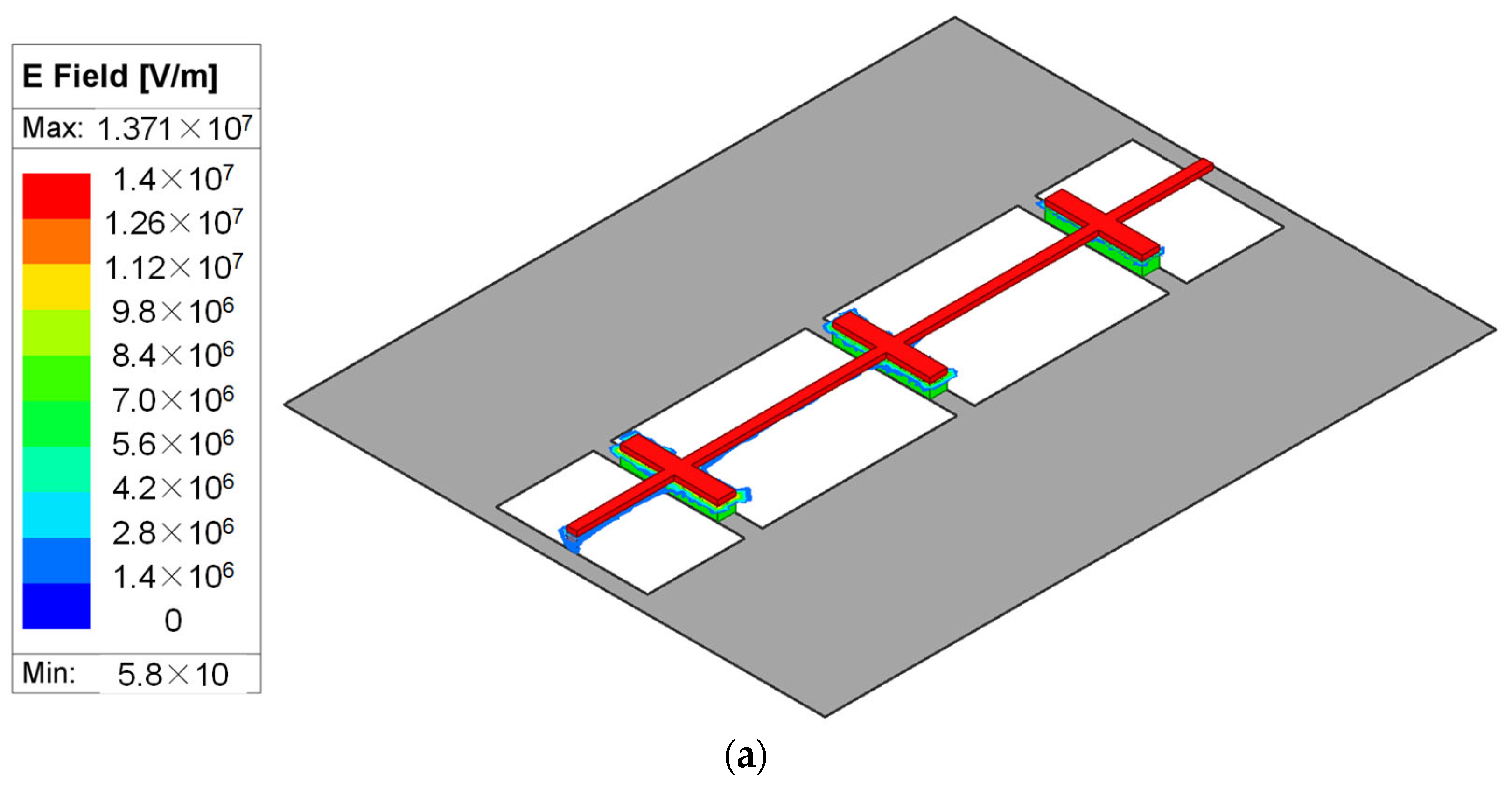

3. EM Model and Simulation Results of a Quarter Wavelength TL

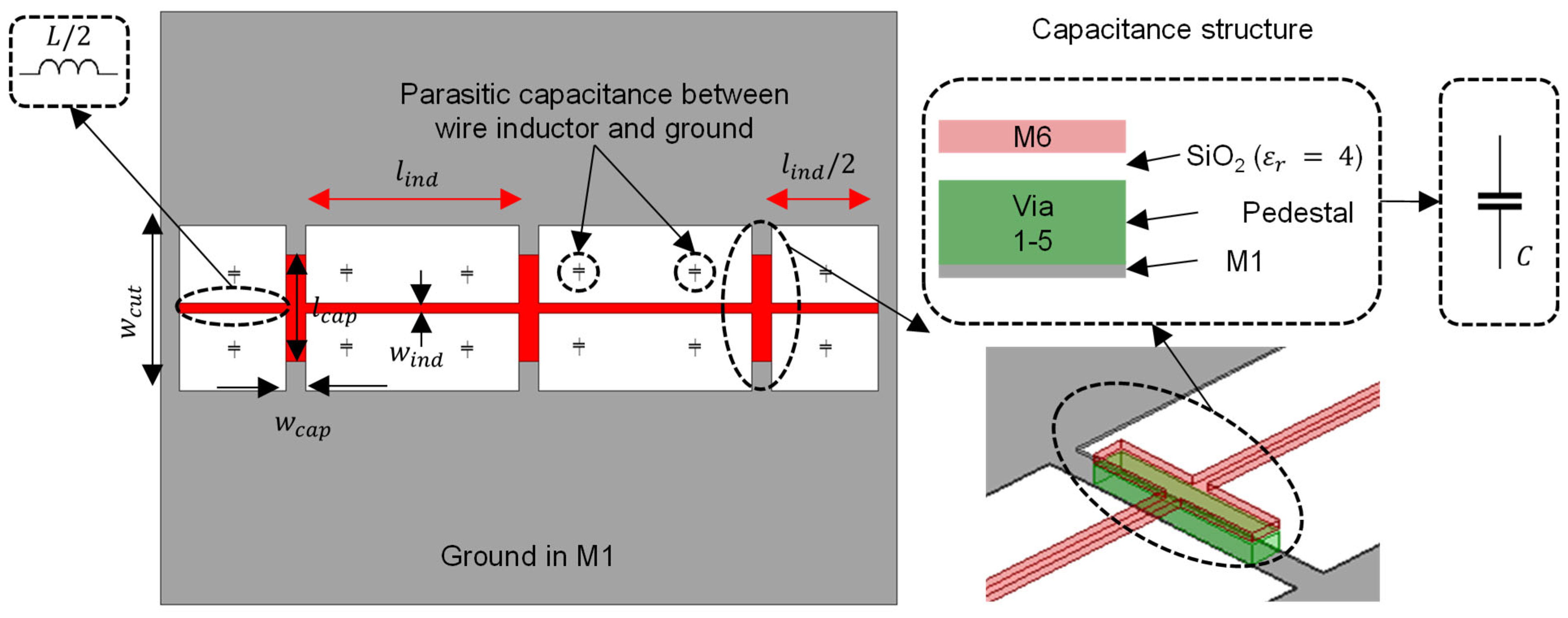

3.1. Practical TL Parameters

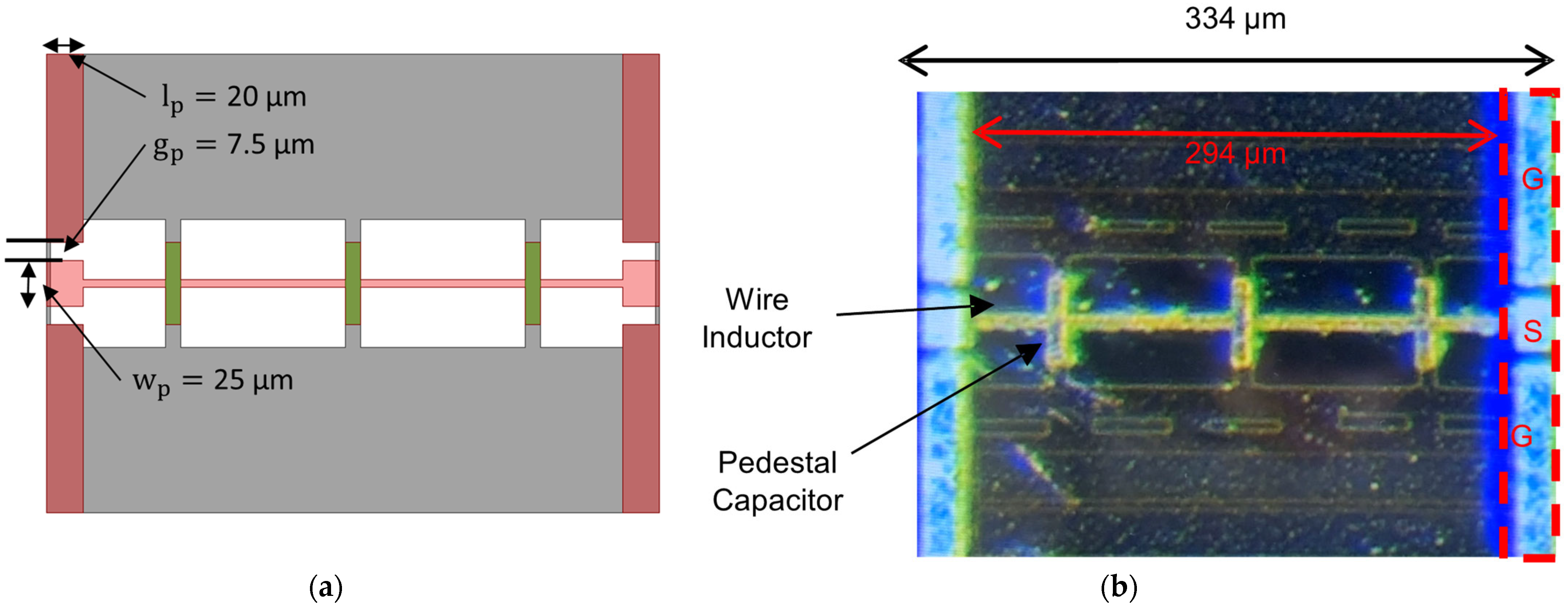

3.2. Unit Capacitance Implementation

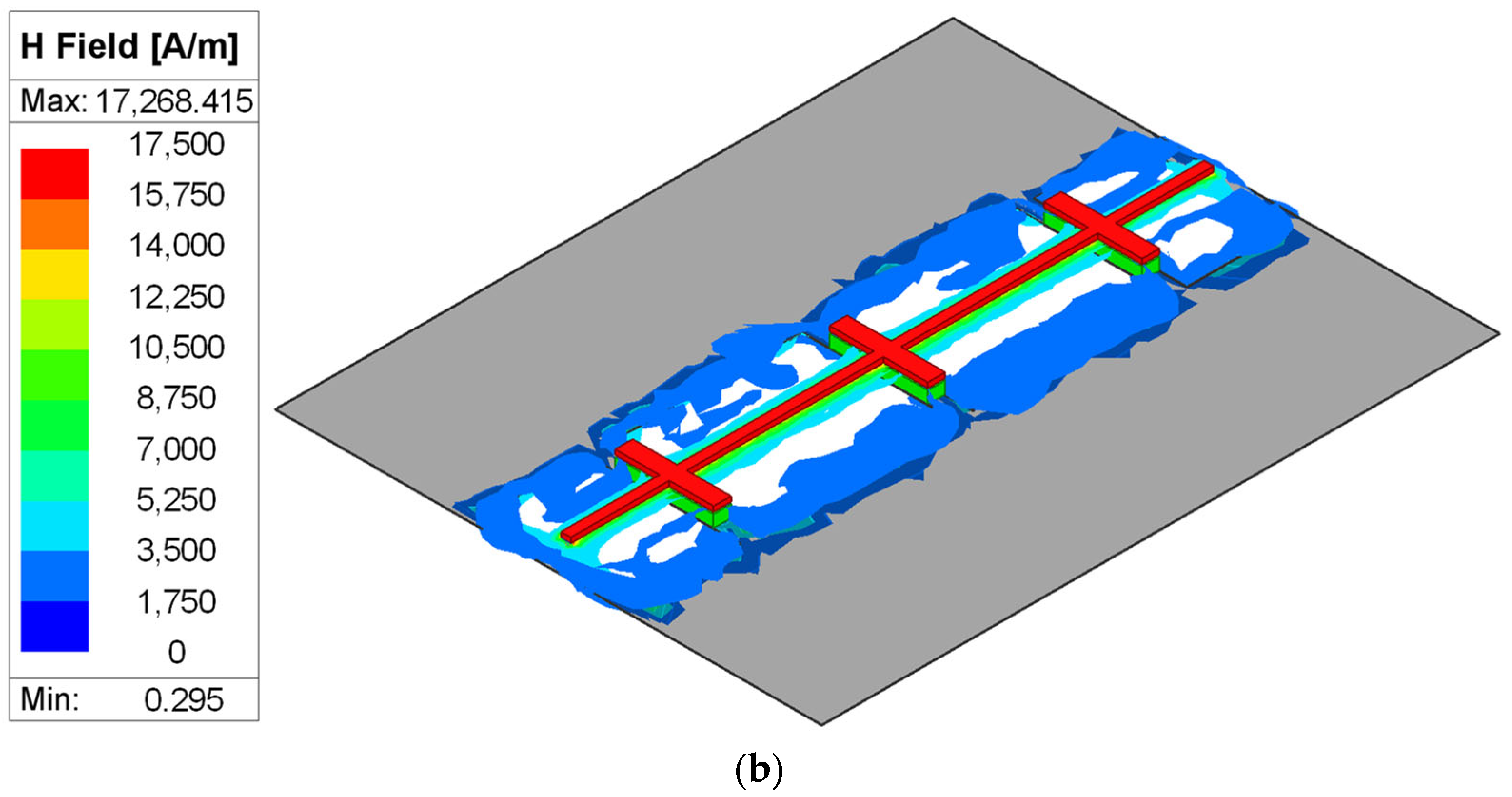

3.3. Unit Inductance Implementation

3.4. Example Designs with Different n T-Networks

4. Measurements

4.1. Measurement Setup

4.2. Measurement Results

4.3. Results Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Pakasiri, C.; Xu, J.-L.; Wang, S. A 10 GHz Compact Balun with Common Inductor on CMOS Process. Electronics 2023, 12, 468. [Google Scholar] [CrossRef]

- Ahn, H.-R. Chapter 3.3.5 Conventional Lumped-Element Ring Hybrids. In Asymmetric Passive Components in Microwave Integrated Circuits; John Wiley & Sons: Hoboken, NJ, USA, 2006. [Google Scholar]

- Byeon, C.W.; Park, C.S. Low-Loss Compact Millimeter-Wave Power Divider/Combiner for Phased Array Systems. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 312–314. [Google Scholar] [CrossRef]

- Abdel Hameed, A.S.; Barakat, A.; Abdel-Rahman, A.B.; Allam, A.; Pokharel, R.K. Design of Low-Loss Coplanar Transmission Lines Using Distributed Loading for Millimeter-Wave Power Divider/Combiner Applications in 0.18-μm CMOS Technology. IEEE Trans. Microw. Theory Tech. 2018, 66, 5221–5229. [Google Scholar] [CrossRef]

- Park, S.; Hong, S. Miniaturized Stepped Impedance Transmission Lines for D-Band Wideband Power Divider with Isolation Capacitor. IEEE Solid-State Circuits Lett. 2024, 7, 78–81. [Google Scholar] [CrossRef]

- Hettak, K.; Verver, C.J.; Stubbs, M.G.; Morin, G.A. A novel compact uniplanar MMIC Wilkinson power divider with ACPS series stubs. In Proceedings of the IEEE MTT-S International Microwave Symposium, Philadelphia, PA, USA, 8–13 June 2003; pp. 59–62. [Google Scholar]

- Elsbury, M.M.; Dresselhaus, P.D.; Benz, S.P.; Popovic, Z. Broadband Lumped-Element Integrated N-way Power Dividers for Voltage Standards. IEEE Trans. Microw. Theory Tech. 2009, 57, 2055–2063. [Google Scholar] [CrossRef]

- Zhang, T.; Che, W.; Chen, H. Miniaturized Multiway Unequal Power Divider with Controllable Characteristic Impedances. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 1062–1064. [Google Scholar] [CrossRef]

- Lin, Y.-S.; Lan, K.-S.; Chen, B.-S. Wideband Millimeter-Wave Power Divider and SPDT Switch Using Inverting Spiral-Coupled-Line. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 1575–1579. [Google Scholar] [CrossRef]

- Park, S.; Hong, S. Millimeter-Wave Wideband Differential Four-Way Wilkinson Power Divider with 90° Rotational Symmetric Layout. IEEE Microw. Wirel. Compon. Lett. 2022, 32, 1163–1166. [Google Scholar] [CrossRef]

- Chirala, M.K.; Floyd, B.A. Millimeter-wave Lange and ring-hybrid couplers in a silicon technology for E-band applications. In Proceedings of the 2006 IEEE MTT-S International Microwave Symposium Digest, San Francisco, CA, USA, 11–16 June 2006; pp. 1547–1550. [Google Scholar]

- Elsaidy, E.; Barakat, A.; Abdel-Rahman, A.B.; Allam, A.; Pokharel, R.K. Ultracompact CMOS 60-GHz Tapped-Line Combline BPF with Two Transmission Zeros Using Defected Ground Structures. IEEE Trans. Compon. Packag. Manuf. Technol. 2018, 8, 1642–1649. [Google Scholar] [CrossRef]

- Mahmoud, N.; Barakat, A.; Abdel-Rahman, A.B.; Allam, A.; Pokharel, R.K. Compact Size On-Chip 60 GHz H-Shaped Resonator BPF. IEEE Microw. Compon. Lett. 2016, 26, 681–683. [Google Scholar] [CrossRef]

- Barakat, A.; Pokharel, R.; Kaho, T. 60 GHz on-chip mixed coupled BPF with H-shaped defected ground structures. Electron. Lett. 2016, 52, 533–535. [Google Scholar] [CrossRef]

- Xiao, Y.; Shan, P.; Zhao, Y.; Sun, H.; Yang, F. Design of a W-Band GaAs-Based SIW Chip Filter Using Higher Order Mode Resonances. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 104–106. [Google Scholar] [CrossRef]

- Barakat, A.; Pokharel, R.K. Low-Pass Filtering Admittance Inverter for High Out-of-Band Rejection Millimeter-Wave On-Chip BPF. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 3963–3967. [Google Scholar] [CrossRef]

- Parisi, A.; Papotto, G.; Ragonese, E.; Palmisano, G. A 1-V 7th-Order SC Low-Pass Filter for 77-GHz Automotive Radar in 28-nm FD-SOI CMOS. Electronics 2021, 10, 1466. [Google Scholar] [CrossRef]

- Men, K.; Liu, H.; Yeo, K.S. Design of a Ka-Band U-Shaped Bandpass Filter with 20-GHz Bandwidth in 0.13-μm BiCMOS Technology. Electronics 2020, 9, 1608. [Google Scholar] [CrossRef]

- Paudel, B.; Li, X.J.; Seet, B.-C. Design and Modeling of a Terahertz Transceiver for Intra- and Inter-Chip Communications in Wireless Network-on-Chip Architectures. Sensors 2024, 24, 3220. [Google Scholar] [CrossRef] [PubMed]

- Chung, M.-A.; Huang, S.-R.; Huang, P.-R. Designed on 0.18 μm CMOS Process Small Size Broadband Millimeter Wave Chip Antenna. Inventions 2023, 8, 64. [Google Scholar] [CrossRef]

- Vendelin, G.D.; Pavio, A.M.; Rohde, U.L. Chapter 1.3 Transmission Lines. In Microwave Circuit Design; Wiley: New York, NY, USA, 1990. [Google Scholar]

- Grover, F.W. Inductance Calculations: Working Formulas and Tables; Courier Corporation: New York, NY, USA, 2004. [Google Scholar]

- Eisenstadt, W.R.; Eo, Y. S-parameter-based IC interconnect transmission line characterization. IEEE Trans. Compon. Hybrids Manuf. Technol. 1992, 15, 483–490. [Google Scholar] [CrossRef]

| Line Type | n | Q @ 60 GHz | (Miniaturization Ratio) | (mm−1) @ 60 GHz | |||||

|---|---|---|---|---|---|---|---|---|---|

| Microstrip | N/A | 14.4 | 700 (N/A) | N/A | 20.6 | ||||

| Proposed cascaded T-networks | 1 | 16.2 | 344 (50.8%) | 90 | 8 | 336 | 4.5 | 70 | 47.1 |

| 2 | 18 | 306 (56.3%) | 63.5 | 8 | 145 | 4.5 | 70 | 58.8 | |

| 3 | 17.9 | 294 (58%) | 45 | 8 | 90 | 4.5 | 70 | 60.9 | |

| 4 | 17.9 | 294 (58%) | 34.5 | 8 | 65.5 | 4.5 | 70 | 60.9 | |

| 5 | 17.8 | 300 (57.15%) | 27.5 | 8 | 52 | 4.5 | 70 | 59.3 | |

| 6 | 17.4 | 300 (57.15%) | 23 | 8 | 42 | 4.5 | 70 | 58 | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Barakat, A.; Pokharel, R.K. High Quality Factor Miniaturized CMOS Transmission Lines Using Cascaded T-Networks for 60 GHz Millimeter Wave Applications. Electronics 2024, 13, 3748. https://doi.org/10.3390/electronics13183748

Barakat A, Pokharel RK. High Quality Factor Miniaturized CMOS Transmission Lines Using Cascaded T-Networks for 60 GHz Millimeter Wave Applications. Electronics. 2024; 13(18):3748. https://doi.org/10.3390/electronics13183748

Chicago/Turabian StyleBarakat, Adel, and Ramesh K. Pokharel. 2024. "High Quality Factor Miniaturized CMOS Transmission Lines Using Cascaded T-Networks for 60 GHz Millimeter Wave Applications" Electronics 13, no. 18: 3748. https://doi.org/10.3390/electronics13183748